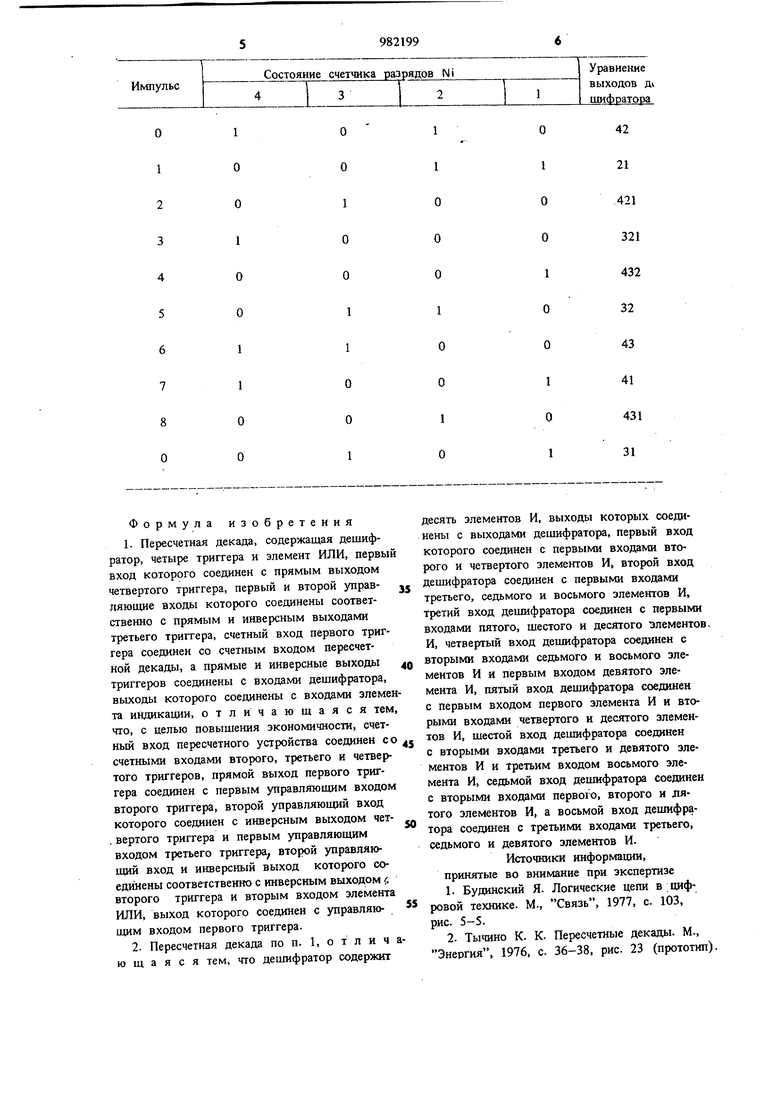

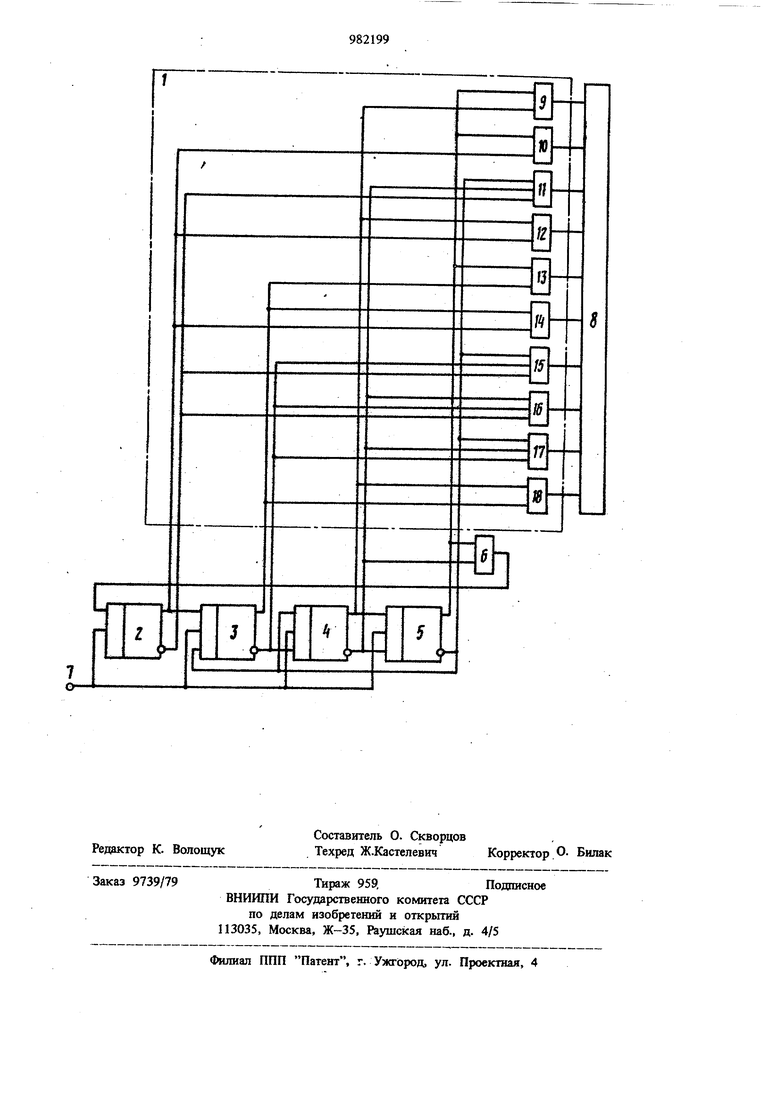

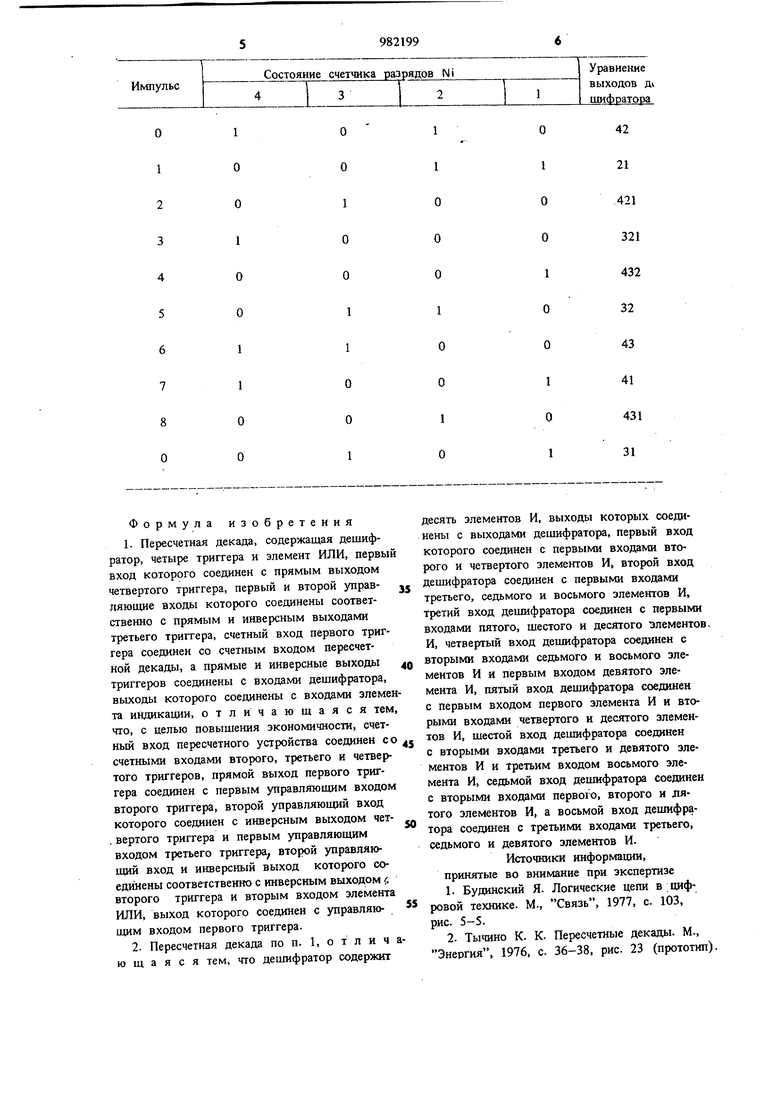

Изобретение относится к устройствам подсчета импульсных сигналов и может быть использовано в измерительных и вычислительных системах с индикацией результатов. Известны пересчетные декады, содержащие счетчик на четырех триггерах и дешифратор, требующий для своего построения десяти логических элементов с общим числом входов не менее тридцати 1. Недостатком этих пересчетных декад является необходимость относительно больщих затрат оборудования для их реализации. Известна также пересчетная декада, содерж щая дешифратор, четыре триггера и элемент ИЛИ, первый вход которого соединен с прямым выходом четвертого триггера, первый и второй управляющие входы которого соединены соответственно с прямым и инверснь5 выходами третьего триггера, счетный вход пе вого триггера соединен со счетным входом пересчетной декады, а прямые и инверсные выходы триггеров соединены с входами дешифратора, выходы которого соединены с входами элемента индикации 2. Недостатком этой пересчетной декада является относительно низкай экономичность, что связано с необходимостью использовашея сравнительно сложного дешифратора. Цель изобретения - повышение экономичности пересчетиой декады. Поставленная цель достигается тем, что в пересчетной декаде, содержащей дешифратор, четыре триггера и элемент ИЛИ, первый вход которого соединен с прямым выходом четвертого триггера, первый и второй управляющий входы которого соединены соответственно с прямым и инверсным выходами третьего триггера, счетный вход первого триггера соединен со счетным входом пересчетной декады, а пряко 1е и инверсные выходы триггеров соединены с входами дешифратора, выходы которого соединены с входами элемента индикации, счетный вход пересчетного устройства соединен со счетными входами второго третьего и четвертого триггеров, прямой выход первого триггера соединен с первым управляющим входом второго триггера, второк управляющий вход которого соединен с инверсным выходом четвертого триггера и пер вым управляющим входом третьего триггера второй управляющий вход и инверсный выход которого соединены соответствешю с инверсным выходом второго триггера и вторым входом элемента ИЛИ, выход которого соединен с управляющим входом первого триггера. Кроме того, деишфратор содержит десять элементов И, выходы которых соединены с выходами дешифратора, первый вход которо го соединен с первыми входами второго и четвертого элементов И, второй вход дещифратора соединен с первыми входами третье седьмогр и восьмого элементов И, третий вх дешифратора соединен с первыми входами п того, шестого и десятого элемеетов И, четве тый вход дешифратора соединен с вторыми входами седьмого и восьмого элементов И и первым входом девятого элемента И, пятый вход дешифратора соединен с первым входом первого элемента И и вторыми входами четвертого и десятого элементов И, шестой вход дешифратора соединен с вторыми входами третьего и девятого элементов И и третьим входом восьмого элемента И, седьмой вход дешифратора соединен с вторыми входами первого, второго и пятого эле ментов И, а восьмой вход дешифратора соединен с третьими входами третьего, седьмого и девятого элементов И. На чертеже показана структурная схема пе счетной декады. Пересчетная декада содержит дешифратор 1 четыре триггера 2-5 и элемент ИЛИ 6, первьш вход которого соединен с прямым выходом четвертого триггера 5, первый и второй управляющие входы которого соединены соответственно с прямым и инверсным выходами третьего триггера 4, счетный вход первого триггера 2 соединен со счетным входом 7 пересчетной декады, а прямые и инверсные выходы триггеров 2-5 соединены с входами дешифратора 1, выходы которого соеди11ены с входами элемента индикации 8. Счетный вход 7 пересчетного устройства соединен со счетными входами второго 3, третьего 4 и четвертого 5 триггеров, прямой выход первого триггера 2 соединен с первым управляющим входом второго триггера 3, второй управляющий вход которого соединен с инверсным выходом четвертого триггера 5 и первым управляющим входом третьего триггера 4, второй управляющий вход и инверсный выход которого соединен соответственно с инверсным выходом второго триггера 3 и вторым входом элемента ИЛИ, 6, выход которого соединен с управляющим входом первого триггера 2. Дещифратор 1 содержит десять элементов И 9-12, выходы которых соединены с выходами дешифратора 1, первый вход которого соединен с первыми входами второго 10 и четвертого 12 элементов И, второй вход депшфратора 1 соединен с первыми входами третьего И, седьмого 15 и восьмого 16 элементов И, третий вход де)лифратора 1 соедийен с первыми входами пятого 13, шестого 14 и десятого 18 элементов И, четвертый выход дешифратора 1 соединен с вторыми входами седьмого 15 и восьмого 16 элементов И и первым входом девятого элемента И 17, пятый вход дешифратора 1: соединен с первым входом первого элемента И 9 и вторыми входами четвертого 12 и десятого 18 элементов И, шестой вход дешифратора I соединен с входами третьего 11 и девятого 17 элементов И и третьим входом восьмого элемента И 16, седьмой вход дешифратора 1 соединен с вторыми входами первого 9, второго 10 и пятого 13 элементов И, а восьмой вход дешифратора 1 соеди 1ен с третьими входами третьего 11, седьмого 15 и девятого 17 элементов И. Пересчетиая декада работает следующим образом. При поступлении входных импульсов на вход 7 счетчик, образованный триггерами, пере 01ючается в соответствии с таблицей. Правее каждого значения состояний счетчика приведены значения функций выходов дешифратора, преобразующего код счетчика в унитарный десятичный, что приводит к зажиганию соответствующей цифры шздикатора. Синхронность работы всех разрядив счетчика и одноступенчатость дешифратора обеспечивает при высоком быстродействии декады исключение ложных сигналов на выходе дешифратора. Использование счетчика, работающего в выбранном коде и имеющего структурную схему, показанную на чертеже, позволяет использовать дешифратор с общим числом входов, равным двадцати четырем, что обеспечивает не только большую экономичность, но и снижение нагрузки на триггеры. Формула изобретения 1. Пересчетная декада, содержащая дешифратор, четыре триггера и элемент ИЛИ, первый вход которого соединен с прямым выходом четвертого триггера, первый и второй управляющие входы которого соединены соответственно с прямым и инверсным выходами третьего триггера, счетный вход первого триггера соединен со счетным входом пересчетной декады, а прямые и инверсные выходы триггеров соединены с входами дешифратора, выходы которого соединены с входами элемен та индикации, отличающаяся тем что, с целью повышения экономичности, счетный вход пересчетного устройства соединен со счетными входами второго, третьего и четвертого триггеров, прямой выход первого триггера соединен с первым управляющим входом второго триггера, второй управляющий вход которого соединен с инверсным выходом четвертого триггера и первым управляющим входом третьего триггера, второй управляющий вход и инверсный выход которого соединены соответственно с инверсным выходом с. второго триггера и вторым входом элемента ИЛИ, выход которого соединен с управляю- . щим входом первого триггера. 2. Пересчетная декада по п. 1, о т л и ч ю щ а я с я тем, что дешифратор содержит десять элементов И, выходы которых соеданены с выходами дешифратора, первый вход которого соединен с первыми входами второго и четвертого элементов И, второй вход дешифратора соединен с первыми входами третьего, седьмого и восьмого элементов И, третий вход дешифратора соединен с первыми входами пятого, шестого и десятого элементов. И, четвертый вход дешифратора соединен с вторыми входами седьмого и восьмого элементов И и первым входом девятого элемента И, пятый вход дешифратора соединен с первым входом первого элемента И и вторыми входами четвертого и десятого элементов И, шестой вход дешифратора соединен с вторыми входами третьего и девятого элементов И и третьим входом восьмого элемента И, седьмой вход дешифратора соединен с вторыми входами первою, второго и лятого элементов И, а восьмой вход дешифратора соединен с третьими входами третьего, седьмого и девятого элементов И. Источники информации, принятые во внимание при экспертизе 1.Будинский Я. Логические цепи в ; цифровой технике. М., Связь, 1977, с. 103, рис. 5-5. 2.Тычино К. К. Пересчетные декады. М., Энергия, 1976, с. 36-38, рис. 23 (прототип).

5

Ю

ми

п

Ml

г fj п

| название | год | авторы | номер документа |

|---|---|---|---|

| Пересчетная декада | 1982 |

|

SU1022311A1 |

| Пересчетная декада | 1983 |

|

SU1112574A1 |

| Пересчетная декада | 1982 |

|

SU1064478A1 |

| Десятичное счетно-индикаторное устройство | 1982 |

|

SU1078628A1 |

| Счетчик импульсов с цифровой индикацией | 1984 |

|

SU1231602A1 |

| Счетчик импульсов с цифровой индикацией | 1987 |

|

SU1478325A1 |

| Счетчик импульсов с цифровой индикацией | 1986 |

|

SU1336230A1 |

| Реверсивная счетная декада | 1988 |

|

SU1554141A1 |

| Десятичный счетчик с индикацией | 1983 |

|

SU1156254A1 |

| Десятичный реверсивный счетчик с цифровой индикацией | 1985 |

|

SU1279062A1 |

Авторы

Даты

1982-12-15—Публикация

1981-05-25—Подача