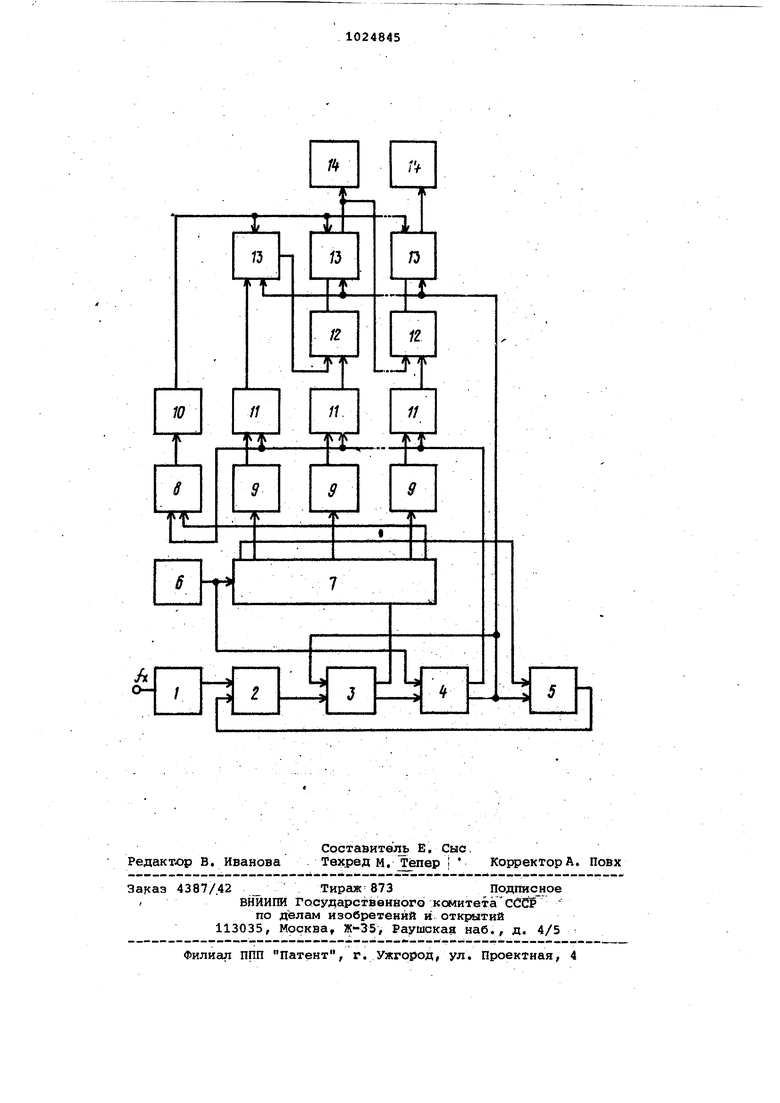

Изобретение относится к измерительной технике и может быть исполь эовано для контроля угловой скорости вращения различных механизмов- и В(системах диагностики. Известно устройство контроля угл вой скорости, содержащее датчик, измерительную схему C DОднако это устройство не обладает- достаточным быстродействием и помехоустойчивостью как полный цикл измерения осуществляется в теч ние нескольких периодов частоты дат чика и в нем не предусмотрена защит от ложных срабатываний. Наиболее близким по технической сущности к изобретению является уст ройство для контроля частоты вращения, содержащее датчик с формирователем, счетчик, соединенный с дешиф раторами, -выходы которых подключены соответственно к входам регистров, запоминающие элементы, выходы которых присоединены к исполнительйым органам, генератор стандартной частоты, схему И, интегратор 2. Однако известное устройство обла дает рядом недостатков. Во-первых, состояние элементов устройства в момент включения питакия и отсутствии входного сигнала Я ляется неопределенным, поэтому возможно ложное срабатывание исполнительного органа. Во-вторых, независимость отдельных каналов многоточе ного контроля дает возможность ложного срабатывания одновременно всех исполнительных органов. В-третьих, при Пт 1 In число интегрируемых импульсов повышение помехоустойчивости достигается за счет интегрирО вания входного сигнала, что снижает быстродействие и при поступлении на вход помехи уменьшается точность контроля. , . Целью изобретения является повышение помехоустойчивости и быстроде ствия устройства для контроля частоты вращения. ДЛЯдостижения поставленной цели устройство для контроля частоты вращения,.содержащее датчик с форми рователетл, счетчик, соединенный с дешифраторами, выходы которых подключены соответственно к входам регистров, Запоми{дающие элементы, выходы которых V присоединены к исполнительным органам, генератор стандартной частоты, схему И, интегратор снабжено регистром перелолнения, двумя дополнительными схемами И исоединенными последовательно формирователем строба, формирователем так тов, регибтром блокировки, первый вход которого соединен с первУм выходом счетчика, а второй вход с первым выходом формирователя тактов вторым входом формирователя стрЬба. и вторыми входами запоминающих элементов , выход регистра блокировки подключен к второму входу схемы И,включенной между формирователем датчика и формирователем строба, при этом второй вход формирователя , строба присоединен к выходу генератора стандартной частоты, а второй выход формирователя строба - к вторым входам регистров, к первому входу регистра переполнения, который через интегратор подключен к третьим входам запоминающих элементов, кроме того, выходы первого и второго запоминающих элементов подключены к первым входам второго и третьего запоминающих элементов через две дополнительные схемы И,вторые входы которых соединены с выходами второго и третьего регистров, причем первый вход счетчик подключен к второму выходу формирователя строба, второй вход счетчика - к генератору стан- дартной частоты, а пятый выход счетчика - к второму входу регистра переполнения . На чертеже представлена структурная- схема устройства. Устройство содержит формирователь 1, первую схему И 2, формирователь 3 строба, формирователь 4 тактов, регистр,5 блокировки, генератор б стандартной частоты, счетчик 7, регистр 8 переполнения, дешифраторы 9, интегратор 10, регистры 11, вторые схемы R 12, запоминающие элементы 13, исполнительные органы 14. Устройство для контроля частоты вращения работает следующим образом. Сигнал с датчика через формирователь., и открытую первую схему И 2 поступает на вход формирователя 3 строба, изменяя его состояние таким образом, что с его первого выхода поступает сигнал установки в ноль счетчика 7, а с второго - сигнал запуска формирователя .4 тактов, который из последовательности импульсов генератора 6 Стандартной частоты формирует два сдвинутых по времени тактовых импульса; При этом первым из них осуществляется возврат в исходное состояние формирователя 3 стрбба., установка в нуль регистра 5 блокировки, перепись результата предыдущего измерения из первого регистра 11 в первый запоминающий элемент 13, остальных регистров 11 чеpgs дополни т ель вые-две схемл И в остальные запоминающие .элементы 13. Вторым тактовым импульсом осущест вляется установка в исходное состояние регистра 8 переполнения и регистр.а 11.-После установки в -ноль дче тчика 7 начинается его заполнение импульсаMH генератора 6 и продолжается до при хода следующего импульса на вход уст-, ройства;Лнксирующвго конец периода и начало,следующего цикла. Через время, равное половине перио-. да максимальной входной частоты диа пазона изме1 ений, с-первого выхода счетчика 7 на регистр 5 блокировки поступает сигнал установки его в единицу, в результате чего снимаeTdH запрет на прохождение входных импульсов. Таким образом, введение второго регистра 5 блокировки защищает устройотвр от импульсных помех на входе. По мере заполнения счетчика 7 происходит срабатывание второго и третьего, дешифраторов 9 с одновременной установкой в ноль второго и третьего регистров 11.- В последнюю очередь сработает первый дешифратор 9, код которого устанавливается бол ше кода второго и третьего дешифраторов 9 нижней контролируемой точки диапазона на величину максимального приращения кода за период входной частоты. Если входной импульс приде раньше, чем сработает какой-либо дешифратор, то соответствующий р6 гистр останется в состоянии единицы По окончании цикла единица с регистров переписывается в запоминшощие элементы 13. Причем логика рабо ты устройства организована таким об разом, что в каждом цикле BOSMdkHa перепись единицы только в запоминающий элниент одного канала, если на втором входе дополнительной схемы И 12 его.есть сигнал единицы. В результате чего исключается возможность ложного срабатывания как в каждом канале, так .как необходимо подтверждение о срабатывании в предыдущем, так и всех вместе от одной помехи. Для защиты первого канала;i к«1нтро: 1ирукяцего самую низшуюточку диапазона, служит канал, образованный первым дешифратором 9, первым регистром 11 и первым запоминающим элементом 13. Для предотвращения ложного срабатывания исполнительных органов 14 Вмомент включения устройства введен интегратор 10, блокирующий выходы запоминающих элементов 13 на время приведения схемы в ис- , ходное состояние. Заряд-разряд ем- кости интегратора 10 осуществляется через цепь выхода регистра 8 переполнения, устанавливающего в нулевое состояние интегратор при переполнении .счетчика 7j либо при выключении питания. При отсутствии переполнения счетчика 7 регистр 8 переполнения находится в состоянии единицы, емкостт интегратора заряжена и выходы запоминающих элементов 13 разблокированы. Изобретение позволяет в три раза пбвысить быстродействие прибора за . счет контроля каждого периода входной ч-астоты значительно улучшить .помехозащищенность прибора, за счет: вЁсдения режима блокировки.входа на время, равное примерно половине периода максимальной входной частоты (;для защиты от высокочастотных п мех типа отебезг j введение реАима блокировки выхода для защиты от ложного срабатывания исполнительных устройств из-за неопределённого состояния элементов схемы в момент включения прибора и при отсутствии . импульсов- входной частотыf введения режима блокировки выхода данного канала при отсутствии подтверждения о предыдущем срабатывании в,младших каналах, для защиты от ложного срабатывания одновременно всех исполнительных элементов от одного сигнала помехи, т.е. вводится обязательная очередность выдачи команд защиты по каналам и при нарушении ее иЗ-за сбоя по питанию или помехи выходы внеочередных каналов блокируются.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля частоты вращения | 1981 |

|

SU980002A2 |

| Двухканальное устройство для акустико-эмиссионного контроля | 1988 |

|

SU1508140A1 |

| Ультразвуковой дефектоскоп | 1986 |

|

SU1385064A1 |

| Устройство для измерения плотности распределения экстремумов | 1983 |

|

SU1101840A1 |

| Система для проведения испытаний турбины | 1989 |

|

SU1636706A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1983 |

|

SU1141439A2 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| ПРИЕМОИНДИКАТОР | 1990 |

|

SU1814387A1 |

| Программно-временное устройство для автоматического управления и контроля системы смазки | 1986 |

|

SU1374180A1 |

| Измеритель времени установления выходного напряжения цифроаналоговых преобразователей | 1984 |

|

SU1236612A1 |

УСТРОЙСТВО ДЛЯ KOHTPCjfe ЧАСТОТЫ ВРАЩЕНИЯ, содержащее Датчик с формирователем, счетчик, соединенг ный с, дешифраторами, выходы которых подключеюа соответственно к входам регистров, запоминающие элементы, выходы которых подключены к исполнительным opraHctM, генератор стандартной- частоты схему И, интегратор, отличающееся тем, что, с целью повшаения помехоустойчивости и быстродействия, оно снабжено регистром переполнения, двумя дополнит ьными схемами И и соединенными последовательно формирователем строба, формирователем тактов, регистром блокировки, первый вход которого соединен с первым выходов счетчика, а второй вход .- с первым выходом формирователя тактов, вторым входом формирователя строба и вторыми входами запоминающих элементов, выход регистра блокировки подключен к второму входу первой схемы И, включенной между формирователем датчика и формирователем строба, при этом второй вход формирователя строба присоединен К выходу генератора стандартной частоты, а второй выход формирователя строба - к .вторым входам регистров, к первому входу регистра переполнения, который через интегратор подключен к третьим входам запоминающих элементов, кроме того, вы ходы первого и второго запоминающих элементов подключены к первым вхо(Л С дам второго и третьего запоминающих элементов через две дополнительные схемн И, вторые входы которых соединены с выходами второго и третьего регистров, причем первый.вход счетчика подключении второму йыходу формирователя строба, второй вход счетчика- к генератору стандартной частоты, а пятый выход счетчика - к ВТОРОМУвходу регистра переполнения.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля частоты вращения | 1977 |

|

SU678416A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-06-23—Публикация

1982-02-26—Подача