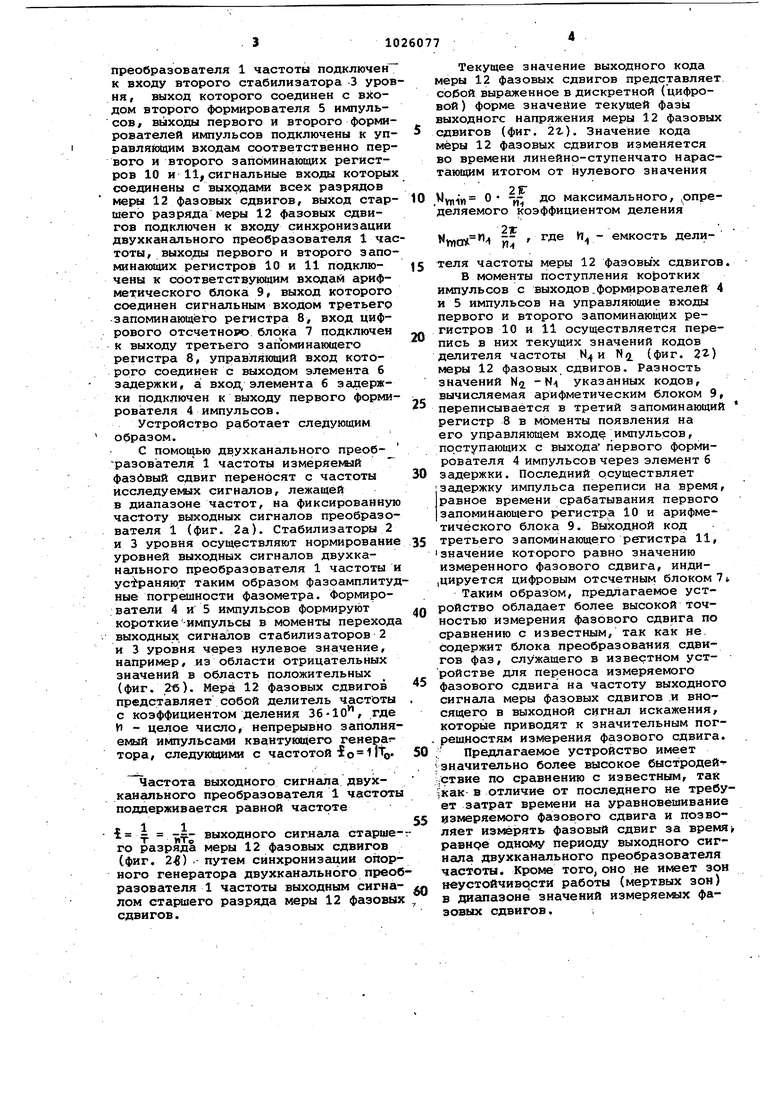

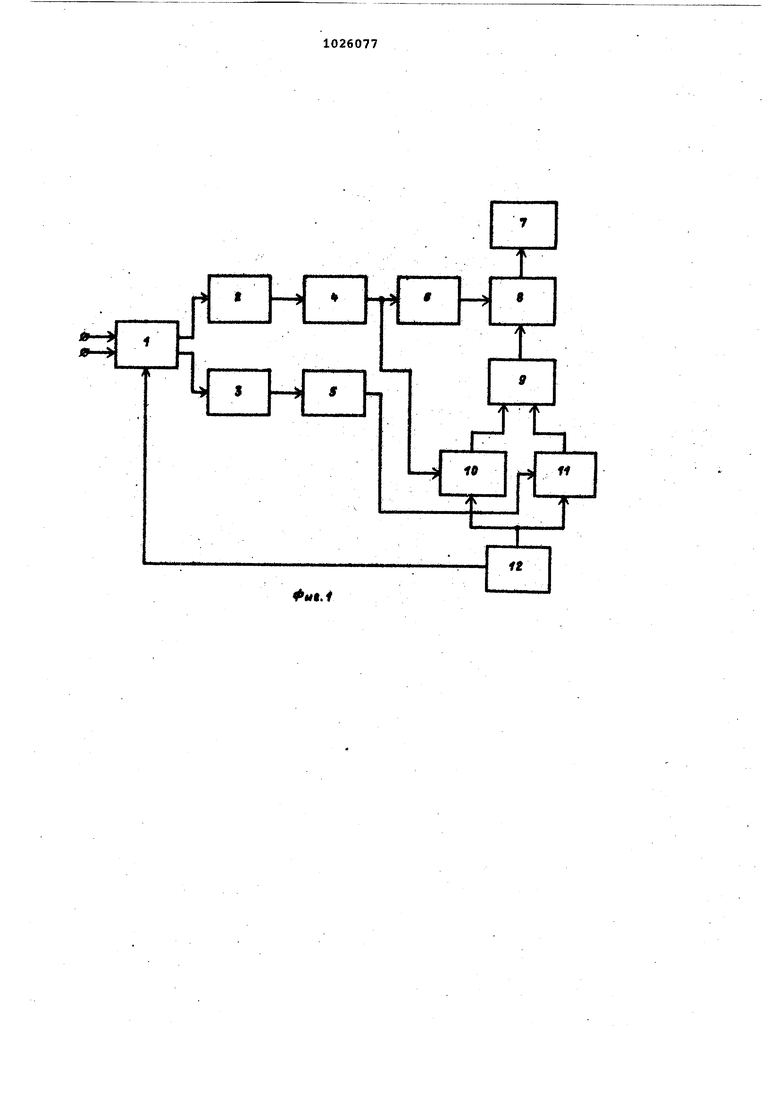

Изобретение относится к измерительной технике и может быть исполь зовано для измерения фазового сдвига непрерывных сигналов. Известны цифровые фазометры с пе рекрытием, а также триггерные цифро вые фазометры, содержащие усилители ограничители, элементы совпадений, триггер, счетчики импульсов, квантуклций генератор 1. Указанные фазометры имеют недостаточно высокую точность измерения из-за значительных погрешностей от нелинейных искажений входных сигналов и наличия зон неустойчивой рабо ты (мертвых зон) в диапазоне значен Измеряемой величины. Наиболее близким по технической сущности к предлагаемому является цифровой фазометр, содержащий двухканальный преобразователь частоты, первый и второй стабилизаторы уровня, блок преобразования сдвигов фаз нуль-индикатор, меру фазовых сдвигов блок управления мерой, блок управления и цифровой отсчетный блок, причем входы двухканального преобразователя частоты соединены с входами опорного и измерительного сигналов, S а выхрды - с входами первого и второго стабилизаторов уровня, выходы стабилизаторов уровня соединены с первым.и вторым, входами бло.ка преоб разования сдвигов фаз, третий вхол которого связан с первым выходом меры фазовых сдвигов, выход блока преобразования сдвигов фаз подключен к первому входу нуль-индикатора выход Которого соединен с входом блокауправления мерой, выход блока управления мерой подключен к первому входу меры фазовых сдвигов, второй вход которой соединен с блоком управ ления, второй вход нуль-индикатора . связан с вторым выходом меры фазовых сдвигов, третий выход которой подклю чен к входу цифрового отсчетного блока Г 2. Однако такое устройство характери зуется недостаточно высокой точность измерения фазового сдвига сигналов и низким быстродействием. Это объясняет ся тем, что в состав устройства входит : блок преобразования сдвигов фаз , который осуществляет перенос измеряемого фазового сдвига на частоту выходного сигнала мери фазовых сдвигов путем двойного преобразования частоты сигналов и является источником значител ных погрешностей измерения фазовых сдвигов сигналов. Низкое быстродействие обусловлено реализуемым в нем алгоритмом уравновешивания измеряемого фазового сдвига калиброванным фазовым сдвигом меры фазовых сдвигов при помощи нуль-индикатора и блока управления мерой. Процесс уравновешивания фазового сдвига требует значительных затрат времени. Цель изобретения т повышение быстродействия и точности измерения фазовых сдвигов сигналов. Поставленная цель достигается тем, что в цифровой фазометр, содержащий меру фазовых сдвигов, цифровой отсчетный блок, двухканальный преоб-. разователь частоты, первый и второй входы которого подключены к входам соответственно опорного и измерительного сигналов, а первый и второй выходы соединены с входами соответственно первого и второго стабилизаторов уровня, введены первый, второй и третий запоминающие регистры, арифметический блок, первый и второй формирователи импульсов и элемент задержки, причем выходы первого и второго стабилизаторов уровней соединены с входами соответствен.но первого и второго формирователей импульсов, выходы которых подключены к управляющим входам соответственно первого и второго запоминающих регистров, вход синхронизации двухканйльного преобразователя частоты соединен с выходом старшего разряда меры фазовых сдвигов, выходы всех разрядов которой подключены к сигнешьным входам первого и второго запоминающих регистров, выходы первого и второго запоминающих регистров соединены с соответствующими входами арифметического блока, выход арифметического блока соединен с сигнальным-входом третьего запоминающего регистра, выход которого- подключен к входу цифрового отсчетного блока, управляющий вход третьего запоминающего регистра соединен с выходом элемента задержки вход которого подключен квыходу первого формирователя импульсов. На фиг. 1 показана структурная схема устройства; на фиг. 2 - эпюры напряжений и кодов устройства. Устройство содержит двухканальный преобразователь 1 частоты, первый стабилизатор 2 уровня, второй стабилизатор 3 уровня, первый формирователь 4 импульсов, второй формирователь 5 импульсов, элемент б задержки, цифровой отсчетный блок 7, третий запоминающий регистр 8, арифметический блок 9, первый 10 и второй 11 запоминающие регистры и меру 12 фазовых сдвигов, причем первый и второй входы двухканального преобразователя 1 частоты соединены с входами соответственно опорного и измерительного сигналов, первый выход двухканального преобразователя 1 частоты подключен к входу первого стабилизатора 2 уровня, выход которого соединен с первым формирователем 4 импульсов, второй выход двухканального преобразователя 1 частоты подключен к входу второго стабилизатора 3 уров ня , выход которого соединен с входом второго формирователя 5 импульсов, выходы первого и второго формирователей импульсов подключены к упI равляющим входам соответственно первого и второго запоминающих регистров 10 и 11, сигнальные входы которых соединены с выходами всех разрядов меры 12 фазовых сдвигов, выход старшего разряда меры 12 фазовых сдвигов подключен к входу синхронизации двухканального преобразователя 1 час тоты, выходы первого и второго запоминающих регистров 10 и 11 подключены к соответствующим входай арифметического блока 9, выход которого соединен сигнальным входом третьего запоминающего регистра 8, вход цифрового отсчетноро блока 7 подключен к выходу третьего запЪминаюадего регистра 8, управляющий вход которого соединен- с выходом элемента б задержки, ai вход, элемента 6 задержки подключен к выходу первого формирователя 4 импульсов. Устройство работает следующим образом. С помощью двухканального преобразователя 1 частоты измеряекый фаздвый сдвиг переносят с частоты исследуемлх сигналов, лежащей в диапазоне частот, на фиксированную часчготу выходных сигналов преоб1 азователя 1 (фиг. 2а). Стабилизаторы 2 и 3 уровня осуществляют нормирование уровней выходных сигналов двухканального преобразователя 1 частоты и устраняют таким образом фазоамплитуд ные погрешности фазометра. Формирователи 4 и 5 импульсов формируют короткие-импульсы в моменты перехода выходных сигна юв стабилизаторов 2 и 3 уровня через нулевое значение, например, из области отрицательных значений в область положительных (фиг. 2б). Мера 12 фазовых сдвигов представляет собой делитель частоты с коэффициентом деления 36 Ю , где И целое число, непрерывно заполняемый импульсами квантукмдего генера тора, следующими с частотой So . Частота выходного сигнала двухканального преобразователя 1 частоты поддерживается равной частоте i :р hf-e выходного сигнала старщего разряда меры 12 фазовых сдвигов (фиг. 2.в) - путем синхронизации опорного генератора двухканального преоб разователя 1 частоты выходным сигналом старшего разряда меры 12 фазовых сдвигов. Текущее значение выходного кода меры 12 фазовых сдвигов представляет собой выраженное в дискретной (цифровой ) форме значейие текущей фазы выходного напряжения меры 12 фазовых сдвигов (фиг. 2г). Значение кода меры 12 фазовых сдвигов изменяется во времени линейно-ступенчато нарастающим итогом от нулевого значения vnin- о -fTi до максимального, ,рпределяемого коэффициентом деления та й7 -t емкость делителя частоты меры 12 фазовых сдвигов. В моменты поступления коротких импульсов с выходов.формирователеи 4 и 5 импульсов на управляющие входы первого и второго запоминающих регистров 10 и 11 осуществляется перепись в них текущих значений кодов делителя частоты N и NQ. (фиг. 2) меры 12 фазовых сдвигов. Разность значений Niji - NI указанных кодов, вычисляемая арифметическим блоком 9, переписывается в третий запоминающий регистр В в моменты появления на его управляющем входе импульсов, поступающих с выхода первого формирователя 4 импульсов через элемент б задержки. Последний осуществляет задержку импульса переписи на время, равное времени срабатывания первого запоминающего регистра 10 и арифметического блока 9. Выход,ной код третьего запоминающего регистра 11, значение которого равно значению измеренного фазового сдвига, инди|ЦИруется цифровым отсчетным блоком 71 Таким образом, предлагаемое устройство обладает более высокой точностью измерения фазового сдвига по сравнению с известным, так как не содержит блока преобразования сдвигов фаз, служащего в известном устройстве для переноса измеряемого фазового сдвига на частоту выходного сигнала меры фазовых сдвигов и вносящего в выходной сигнал искажения, которые приводят к значительным погрешностям измерения фазового сдвига. Предлагаемое устройство имеет значительно более высокое быстродей;Ствие по сравнению с известным, так как в отличие от последнего не требует затрат времени на уравновешивание измеряемого фазового сдвига и позволяет измерять фазовый сдвиг за время равнре одному периоду выходного сигнала двухканального преобразователя частоты Кроме того, оно не имеет зон неустойчивости работы (мертвых зон) в диапазоне значений измеряемых фазовых сдвигов.

Ж

ГЧ

-

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1985 |

|

SU1262412A1 |

| Цифровой фазометр | 1984 |

|

SU1176264A1 |

| Цифровой фазометр | 1982 |

|

SU1064226A1 |

| Цифровой фазометр | 1976 |

|

SU664120A1 |

| Радиоимпульсный фазометр | 1985 |

|

SU1257558A1 |

| Цифровой фазометр | 1982 |

|

SU1075187A1 |

| Устройство для определения фазоамплитудной погрешности фазометров | 1988 |

|

SU1597764A1 |

| Цифровой компенсационный фазометр | 1980 |

|

SU920563A1 |

| Анализатор частотного спектра | 1980 |

|

SU900209A1 |

| Цифровой фазометр | 1986 |

|

SU1348744A1 |

ЦИФРОВОЙ ФАЗОШ:ТР, содержащий меру фазовых сдвигов, цифровой отсчетный блок, двухканальный преобразователь частоты, первый и второй входы которого подключены к входам соответственно опорного я измерительного сигналов, а первый и второй выходы соединены с входами соответственно первого и второго стабилизаторов уровня, отличающий с я тем, что, с целью повЕшеаия .быстродействия и точности измерения фазового сдвига сигналов, в него :введены первый, второй и третий -Запоминающие регистры, арифметический блок, первый и второй формирова.тели импульсов и злемент задержки, причем выходы первого и второго стабилизаторов уровней соединены с входами соответственно первого и второго формирователей импульсов, выходы которых подключены к управляющим входам соответственно первого и второго запоминающих регистров, вход синхронизации двухканального преобразователя частоты соединен с выходом старшего разряда меры фазовых сдвигов, выхода всех разрядов которой подключены к сигнальным входам первого к второго запоминающих регистров, выходы первого и второго запоми-Ё наювдих регистров соединены с соответ(Л ствующими входами арифметического блока, выход арифметического блока соединен с сигнальным входом третьего запоминающего регистра, выход которого подключен к входу цифрового отсчетного блока, управляюпдай вход третьего запоминающего регистра соединен с выходом элемента з-адержки, вход Которого подключен-к- выходу э. формирователя импульсов. д 3d Э Ч ч

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Смирнов П.Т | |||

| Цифровые фазометры | |||

| Л., Энергия, 1974, с | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цилиндр для двухтактного двигателя внутреннего горения | 1926 |

|

SU5126A1 |

| Техническое описание и инструкция по эксплуатации. | |||

Авторы

Даты

1983-06-30—Публикация

1981-12-10—Подача