Изобретение относится к информационно-измерительной технике и может быть использовано в устройствах .для змерения неэлектрических величин, например силы, крутящего момента и т.д.

Известен преобразователь параметров мостового датчика с переключением направления интегрирования pj.

Недостатком этого устройства является ограниченный диапазон выход- ных частот, обусловленный влиянием распределенных параметров датчика.

Известен также преобразователь электрического сигнала мостового датчика в частоту, срдержащий мостовой датчик, измерительная диагональ которого подключена к входу -масштабного усилителя, интегратор, к выходу которого подключен первый вход компаратора , первый вход которого подключен к выходу интегратора, формирователь импульсов, вход которого соединен с выходом компаратора, и делитель частоты, первый выход которого подключен через источник знакопеременного напряжения к диагонали питания мостового датчика ..

Недостаток данного преобразова- . теля - ограниченный диапазон выходных частот, обусловленный ограниченным динамическим диапазоном цифроаналогового преобразователя.

Цель изобретения расширение диапазона выходных частот в сторону высоких частот.

Поставленная цель достигае1;ся тем, что в преобразователь электрического сигнала мостового датчика в часто ту, содержащий мостовой датчик, измерительная диагональ которого подключена к входу масштабного усилителя, интегратор, к выходу которого подключен первый вход компаратора, формирователь импульсов, вход которого соединен с выходом компаратора, и делитель частоты, первый выход которого подключен через источник знакопеременного напряжения к диагонали питания мостового датчика, введены первый и второй модуляторы, триггер и блок фазирования, причем вход первого модулятора подключен к выходу масштабного усилителя, а выход к входу интегратора, вход второго модулятора подключен к выходу источника знакопеременного напряжения, а выход - к второму входу компаратора, первый и второй входи блока фазирования подключены соответственно к первому и второму выходам делителя частоты, а первый и второй выходы блока фазирования подключены соответственно к входам установки нуля и единицы триггера, причем тактовый вход триггера подключен к выходу формирователя импульсов, инверсный и прямой выходы триггера подключены соответственно к управляющим входам первого и второго модуляторов, а вход делителя подключен к выходу формирователя импульсов.

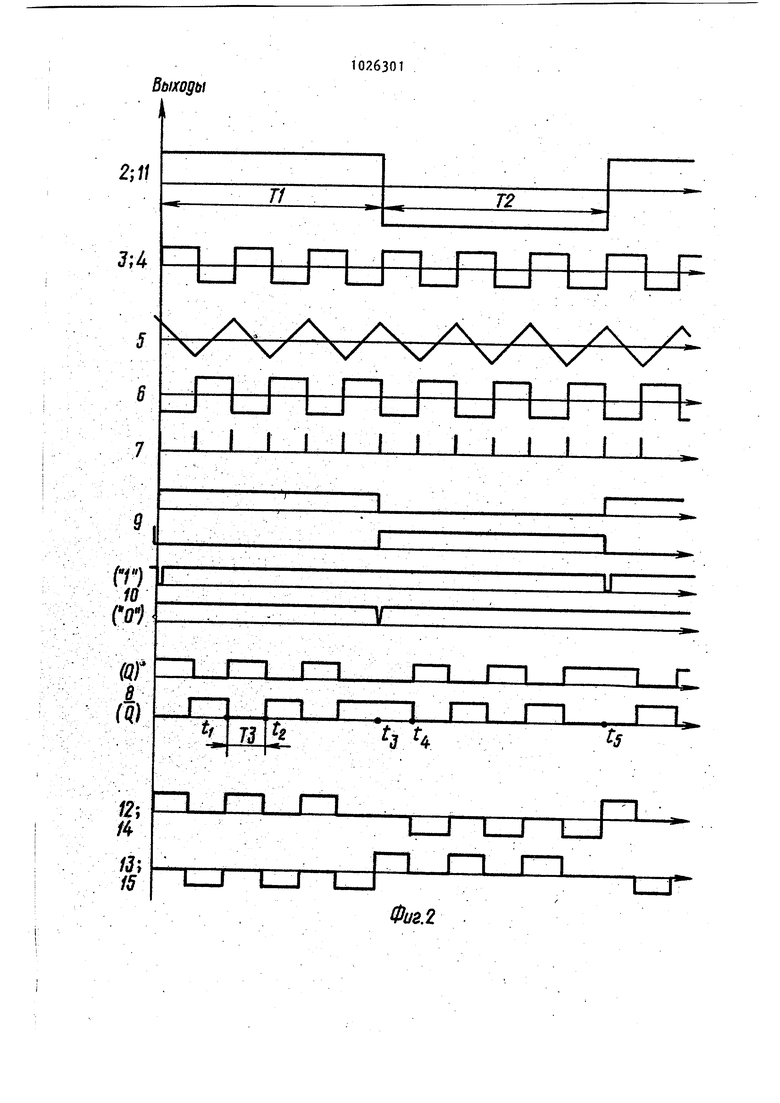

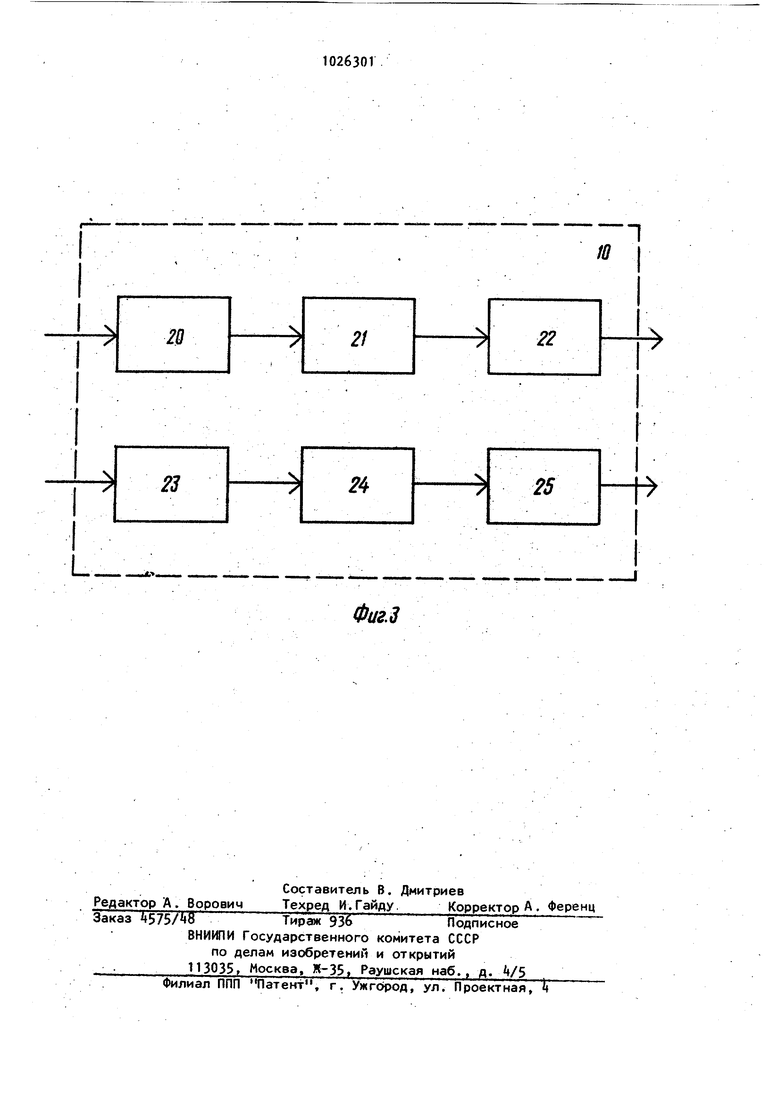

Кроме того, блок фазирования выполнен Двухканальным, при этом каждый из каналов выполнен на последовательно соединенных дифференцирующей цепочке, ограничителе и инвер;торе, причем входы дифференцирующих цепочек подключены cootBeTCTBeHino к первому и второму входам блока фазирования, первый и второй выходы которого подключены соответственно ,к выходам инверторов.

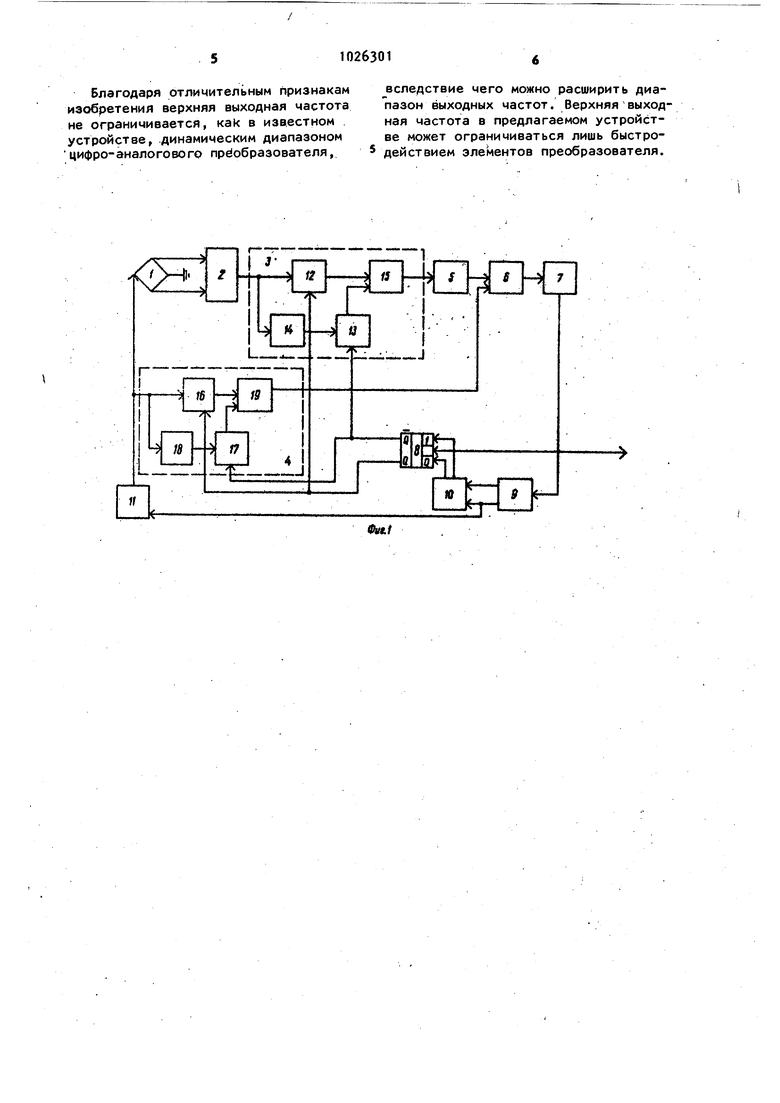

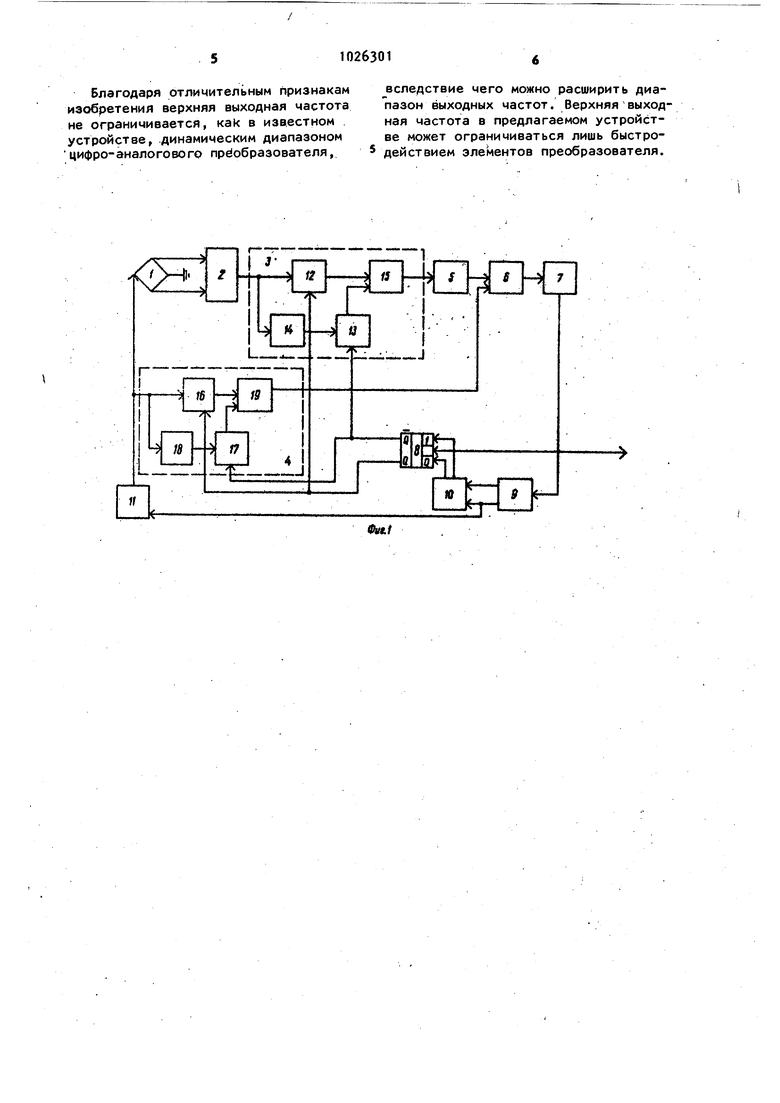

На фиг. 1 представлена функциональная схема преобразователя; на фиг. 2 - временные диаграммы работы элементов устройства; на фиг. 3

0 функциональная схема блока фазирования.

Преобразователь содержит мостовой датчик 1, к выходу которого подключен вход масштабного усилителя 2, модулятор 3, вход которого подключен к выходу масштабного усилителя, модулятор 4, интегратор 5, вход которого подключен к выходу модулятора 3, а выход - к первому входу компаратора

0 6, формирователь 7 импульсов, вход которого подключен к выходу компаратора 6, а выход - к тактовому входу триггера 8, делитель 9 частоты, вход которого подключен к выходу формирователя 7, а выходы - к входам блока 10 фазирования. Выходы блока 10 фазирования подключены к входам устанрвки нуля и единицы триггера 8, выходы которого подключены к управляющим входам модуляторов 3 и 4. Первый выход делителя 9 частоты подключен к входу источника, 11 знакопеременного напряжения, выход которого соединен с диагональю питания мостового датчика 1 и с входом модулятора 4. Выход модулятора подключен к второму входу компаратора 6.

Модулятор 3 выполнен на ключах 12 и 13, инверторе И и сумматоре 15, 3 а модулятор А - на ключах 16 и 17, инверторе 18 и сумматоре 19. Блок 10 фазирования (фиг, 3) содержит два идентичных канала, первый из которых выполнен на последователь но соединенных дифференцирующей цепочке 20, ограничителе 21 и инверторе 22, а второй - на последовательно соединенных дифференцирующей цепочке 23, ограничителе 2k и инверторе 25. Преобразователь работает следующим образом. Пусть положение делителя 9 частоты соответствует интервалу, преобразования Ti , при котором источник 11 д.. , при котором источник знакопеременного напряжения и масштабный усилитель 2 выдают положитель ное напряжение (фиг. 2). Пусть также в момент t после очередного срабатывания компаратора 6 импульс с формирователя 7 импульсов перебросил по тактовому входу триггер 8 в положение, соответствующее положительному уровню напряжения на прямом выходе Q триггера 8 и нулевому уровню на инверсном выходе триггера 8. Блок фазирования по обоим выходам выдает положительное напряжение, сигнал с выхода Q триггера открывает ключ 12 модулятора 3 и ключ 16 модулятора k, при этом ключи 13 и 17 модуляторов закрыты. На выходах сумматоров 15, 19 и,- следовательно, на выходах модуляторов 3 и появляется положительное напряжение. Выходное напряжение интегратора 5 начинает линейно изменяться в сторону отрицательных значений. При равенстве в момент tf абсолютных значений напряжений на входах компаратора 6 последний перекидывается, а формирователь 7 импульсов перебрасывает триггер 8 в нулевое положение по первому выходу Q, при этом на втором выходе Q триг.гера появляется положительное напряжение. Импульс с выхода формирователя 7 импульсов проходит на выходную шину и на делитель 9 частоты. Выходные потенциалы триггера 8 открывают, ключи 13 и 17 и закрывают ключи 12 и 16. Отрицательные сигналы с выходо инверторов проходят соответственно через открытые ключи 13 и 17. Отрицательный- сигнал, появляющийся на входе интегратора 5, интегрируется, пока выходное напряжение интегратора, подаваемое на первый вход компардтора 6, не будет равно по модулю 01 напряжению, подаваемому с выхода модулятора Ц. При равенстве сигналов на входах компаратора, последний перекидывается, формирователь 7 выдает импульс, который снова перебрасывает триггер 8, выходные потенциалы триггера открывают ключи 12 и 16 и закрывают ключи 13 и 17. Процесс повторяется, пока не появится импульс на выходе делителя 9 частоты, который установит на выходе источника 11 знакопеременного напряжения отрицательное напряжение, т.е. в момент tj начнется интервал Т (фиг. 2). В момент изменения полярности на выходах делителя 9 частоты происходит изменение потенциала: на одном из выходов изменяется от нулевого уровня до положительного уровня, на другом - от положительного уровня до нулевого. Эти изменения потенциалов поступают на дифференцирующие цепочки 20, 23 (фиг. 2) блока 10 фазирования. Так как изменение уровней на входах дифференцирующих цепей происходит при смене полярности в противоположные стороны, на вход ограничителей 21 и 2k уровня поступают сигналы противоположной полярности. Ограничители пропускают только положительные импульсы, поэтому при смене полярности импульс поступает только на один из инверторов 22 или 25. Импульс, прошедший на инвертор, открывает его, и происходит формирование импульса на одном из выходов блока 10 фазирования. Импульсы с выходов блока 10 фазирования поступают на первый вход Ч и на второй вход О триггера 8. Если на первый вход 1 триггера 8 приходит импульс, то триггер по выходу Q остается в поло- жении единица, несмотря на приход импульса на тактовый вход триггера. Если импульс поступает на второй вход О триггера, то триггер по выходу Q остается в положении ноль. Таким образом, при каждой смене полярности импульс с одного из выходов блока 10 фазирования запрещает очередной переброс триггера импульсом с формирователя 7, т.е. триггер остается в положении, предшествующем моменту сменыполярности, происходит тем самым изменение очередности работы ключей (фиг. 2). Затем на интервале Т работа схемы происходит так же, как на интервале Т.

Благодаря отличительным признакам изобретения верхняя выходная частота не ограничивается, как в известном устройстве, динамическим диапазоном цифро-аналогового преобразователя,

вследствие чего можно расширить диапазон выходных частот. Верхняя выходная частота в предлагаемом устройстве может ограничиваться лишь быстродействием элементов преобразователя.

Выходы

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь неэлектрических величин | 1985 |

|

SU1403374A1 |

| Устройство для преобразования сигнала мостового датчика в частоту | 1978 |

|

SU782150A1 |

| ТЕРМОИНВАРИАНТНЫЙ ИЗМЕРИТЕЛЬ ЛИНЕЙНОГО УСКОРЕНИЯ | 2012 |

|

RU2528119C2 |

| Преобразователь электрических сиг-НАлОВ МОСТОВыХ дАТчиКОВ B чАСТОТу | 1978 |

|

SU813773A1 |

| ПРЕОБРАЗОВАТЕЛЬ НЕЭЛЕКТРИЧЕСКИХ ВЕЛИЧИН В ЦИФРОВОЙ КОД | 1991 |

|

RU2020745C1 |

| ШИРОКОДИАПАЗОННЫЙ ВОЛОКОННО-ОПТИЧЕСКИЙ ИЗМЕРИТЕЛЬ УГЛОВОЙ СКОРОСТИ | 2002 |

|

RU2227272C2 |

| Устройство для управления регулируемым мостовым инвертором | 1988 |

|

SU1548830A1 |

| Устройство для управления автономным инвертором | 1980 |

|

SU936363A1 |

| Измерительный преобразователь активной мощности | 1989 |

|

SU1659890A1 |

| Устройство для измерения динамических параметров вращающихся валов | 1983 |

|

SU1176187A1 |

1. ПРЕОБРАЗОВАТЕ/Ь ЭЛЕКТРИЧЕСКОГО СИГНАт МОСТОВОГО ДАТЧИКА В ЧАСТОТУ, содержащий мостовой датчик, измерительная диагональ которого подключена к входу масштабного Усилителя, интегратор, к выходу которого подключен первый вход компаратора, формирователь импульсов, вход ко торого соединен с выходом компаратора, и делитель частоты, первый выход которого подключен через источник знакопеременного напряжения к диагонали питания мостового датчика, о тличающийся тем, что, с целью расширения диапазона выходных частот в сторону высоких частот, в него введены первый и второй модуляторы, триггер и блок фазирования, причем вход первого:модулятора под- . ключен к выходу масштабного усилителя, а выход - к входу интегратора., вход второго модулятора подключен к. выходу источника знакопеременного напряжения, а выход - к второму входу компаратора, первый и второй входы блока фазирования подключены соответственно к первому и второму выходам делителя частоты, а первый и второй выходы блока фазирования подключены соответственно к входам установки нуля и единицы триггера, причем а € тактовый вход триггера подключен к выходу формирователя импульсов, ин(Л версный и прямой выходы триггера подключены соответственно к управляющим входам первого и второго модуляторов, а вход делителя подключен к выходу формирователя импульсов. 2. Преобразователь по п. 1, о тл и ч а ю щ и и с я тем, что блок фазирования выполнен двухканальным, при этом каждый из каналов выполнен на последовательно соединенных дифференцирующей цепочке, ограничителе и инверторе, причем входы дифференцирующих цепочек подключены соответственно к первому и второму входам блока фазирования, первый и второй выходы которого подключены соответственно к выходам инверторов.

2, 11

П V У У /Ч У / / лл / /

II I II I I 1 I 1 1 I 1

f2

п

ГП

Т2

IL

С

Г 1I1

i

S

3 4

:Г

Й/г2 У УЧ Л / /

1

10

Фиг.З

Авторы

Даты

1983-06-30—Публикация

1982-01-21—Подача