(Л

с:

Изобретение относится к электроизмерительной и вычислительной технике и предназначено для преобразования широкополосных аналоговых электрических сигналов в цифровой двоичный код.

Известное устройство для аналогоцифрового преобразования содержит усилитель с переменным коэффициентом усиления, первый вход которого подключен к входу устройства, второй вход - к выходу первого цифро-аналогового преобразователя, выход соединен с первым входом аналого-цифрового преобразователя, первый и второй входы сумматора-вычитателя соответственно соединены с выходами первого и второго цифро-аналоговых преобразователей, а первый и второй выходы соединены соответственно с первыми в; ;одами первого и второго компараторов, вторые входы которых подключены к входу устройства, а выходы подсоединены к первому и второму входам блока устройства, выход которого соединен с входом блока памяти, с третьим входом усилителя с переменны коэффициентом усиления, вторым входо аналого-цифрового преобразователя и с первым входом сумматора, второй вход .которого соединен с выходом аналого-цифрового преобразователя, первый выход соединен,с входом первого цифро-аналогового преобразователя, третий вход соединен с выходом блока памяти и с входом второго цифро-аналогового преобразователя, а второй выход соединен с выходом устройства 1 ..

К недостаткам известного устройства следует отнести ограниченные функциональные возможности, а именно невозможность aвтoмatичecкoгo выбора интервала дискретизации в условиях недостатка априорных данных о корреляционных свойствах преобразуемого сигнала и определения интервала корреляции.

Цель изобретения - расширение функциональных возможностей устройства.

Поставленная цель достигается тем, что в устройство для аналогоцифрового преобразования введены блок сравнения, блок вым итания, пер вый и второй усреднители, причём вход первого усреднителя и первый вход блока вычитания соединены с ВТО рым выходом сумматора, второй вход

блока вычитания соединен с первым выходом первого усреднителя, а выход подключен к входу второго усреднителя, выход которого соединен с первым входом блока сравнения, второй вход которого подключен к второму выходу первого усреднителя, а выход соединен с дополнительным входом блока управления.

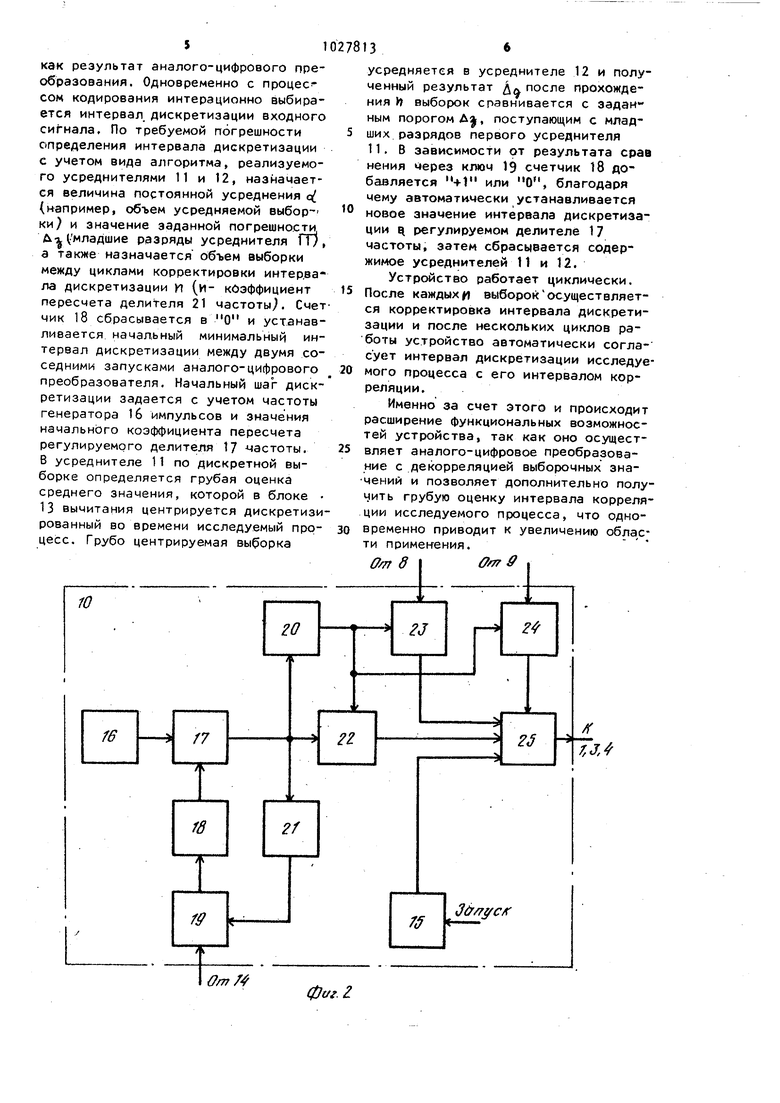

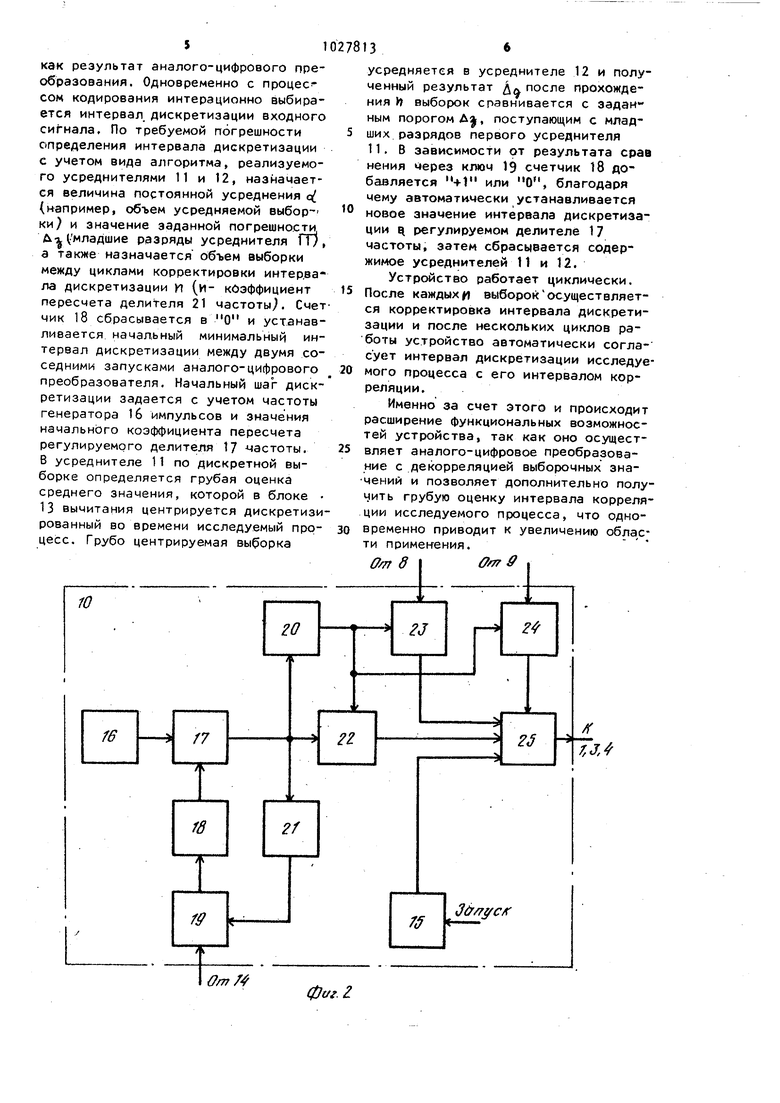

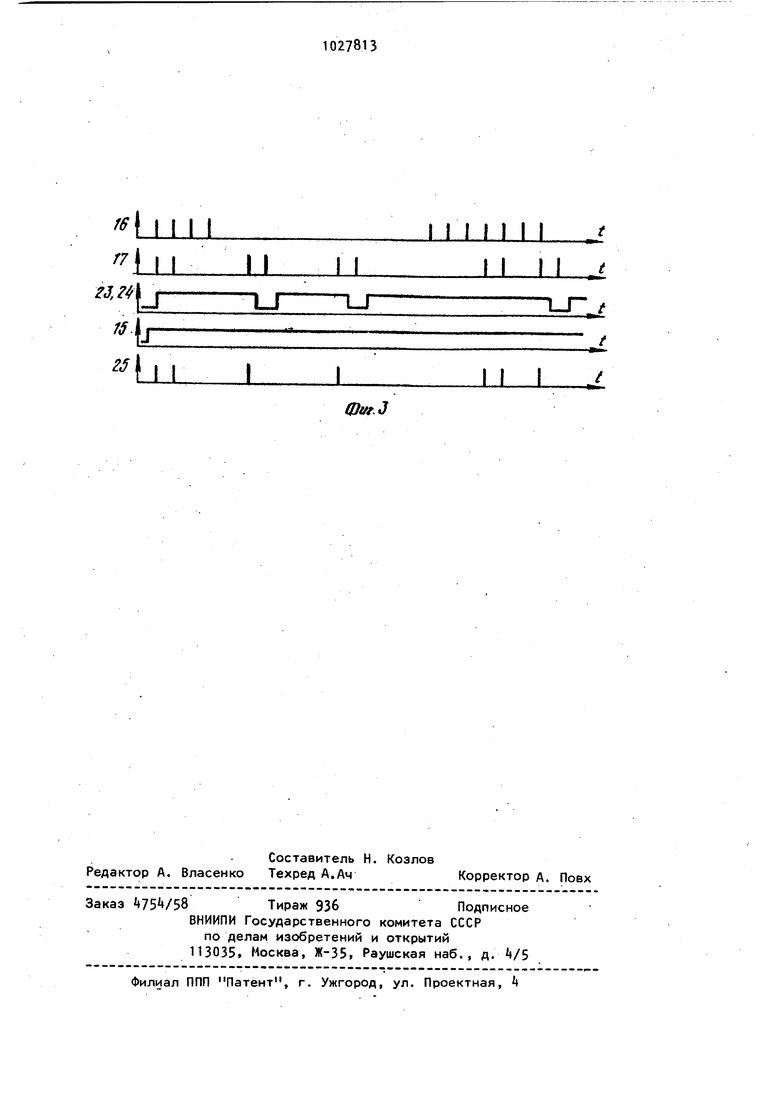

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 пример выполнения блока управления; на фиг. 3 - диаграмма работы устройства.

Устройство для аналого-цифрового преобразования содержит усилитель 1, первый цифро-аналоговый преобразователь 2, аналого-цифровой преобразова тель 3, сумматор 4, блок 5 памяти, второй цифро-аналоговый преобразователь 6, сумматор-вычитатель 7, первы и второй компараторы 8 и 9 блок 10 управления, первый и второй усред- нители 11 и 12, блок 13 вычитания, блок И сравнения. Первый вход усилителя 1 соединен с входом устройства, второй вход подключен к выходу первого цифро-аналогового преобразовтеля 2, выход соединен с первым входом аналого-цифрового преобразователя 3) первый и второй входы сумматора-вычитателя 7 соответственно соединены с выходами первого и второго соответственно соединены с выходами первого и второго цифро-аналоговых преобразователей 2 и б, а : первый и второй выходы соединены соответственно с первыми входами первого и второго компараторов 8 и 9, вторые входы которых подключены к входу устройства, а выходы подсоединены соответственно к первому и второму входам блока 10 управления, выход которого соединен с входом блока 5 памяти, с третьим входом усилителя 1, вторым входом аналого-цифрового преобразователя 3 и с первым входом сумматора 4, второй вход которого соединен с выходом аналого-цифрового преобразователя 3, первый выход соединен с входом первого цифро-аналогового преобразователя 2, третий вход соединен с выходом блока 5 памяти и с входо| 1 второго цифро-аналогового, преобразователя 6, а второй выход соединен с выходом устройства {и с первыми входами первого усреднителя 11 и блока 13 вь1читания, второй вход которого соединен с первым выходом первого усреднителя 11, авыход подключен к входу второго усреднителя 12, выход которого сое динен с первым входом блока 14 сравнения, второй вход которого подключен к второму выходу первого усредни теля 11, а выход сЪединен с третьим входом блока 10 управления. Блок 10 управления соде|эжит триггер 15 генератор 16 импульсов, регулируемый делитель 1/ частоты, -счет чик 18, первый ключ 19 элемент 20 задержки, делитель 21 частоты, элемент ИЛИ 22,.второй и третий ключи 23 и 2k, элемент И 25. На вход триггера 15 поступает сигнал запуска устройства, выход триггера 15 подклю чен к первому входу элемента И 25, выход которого является выходом блок 10 управления. Выход генератора 16 импульсов соединен с первым входом регулируемого делителя 17 частоты, второй вход которого соединен с выходом счетчика 18, а выход подключен к входу-элемента 20 задержки, к первому входу элмента ИЛИ 22 и к входу делителя 21 частоты, выход которого соединен с первым входом ключа 19 второй вход которого является третьим входом блока 10 управления, а вы ход соединен с входом счетчика t8. Выход элемента 20 соединен с первыми входами ключей 2 и 24 и с вторым входом элемента И 25, трети и четвертый входы которого соединены с выходами ключей 23 и 24, вторые входы которых являются соответственно первым и.вторым входами блока 10 управления. Устройство работает следующим образом, Цикл преобразования входного сигнала разделен в зависимости от ско-. рости его изменения на К тактов. За один такт работы устройства происходит определение Ы разрядов двоичного кода Длительность одного такта преобразования определяется временем работы аналого-цифрового преобразователя З(Ьпр) и временем слежения за изменением входного сигнала (. В блок.5 памяти записаны коды устано вок, соответствующие приращению входного сигнала за время при раз личных скоростях изменения входного сигнала. В начале работы импульсом Запуск триггер 15 (фиг. 2 ) открывает эле-, мент И 25- Для примера на элементе 20 задержки и элемента ИЛИ 22 формируются два такта преобразования. Первым импульсом из блока 10 в усили теле 1 устанавливается коэффициент передачи, равный 1, регистры сумматора 4 сбрасываются в О в блоке 5памяти устанавливается код, соответствующий приращению входного сигнала за время- к Ри максимальной частоте входного сигнала. Затем запускается аналого-цифровой преобразователь 3, который кодирует входной сигнал с числом разрядов Н. Этот код записывается в сумматор 4 и подает,ся ма цифро-аналоговый преобразова- . тель 2. С его выхода аналоговый сигнал, соответствующий коду Ny , пода:ется на второй вход усилителя 1 и на вход сумматора-вычйтателя 7, на другой вход которого с выхода второго цифро-аналогового преобразователя 6подается напряжение уставки CSJvcT-t)- соответствующее коду первой уставки, записанному в блоке 5 памяти. С выходов сумматора-вычитателя 7на входы первого и второго компараторов 8 и 9 подается напряжение UNTH VCTH На другие входы компараторов 8 и подается входное напряжение Ux Если за время ;-Ь,(диаграмма, фиг. 3 изменение входного напряжения не. пре восходит заданной уставки, то вторым импульсом с элемента 20 задержки через элемент ИЛИ 22 и элемент И 25 приходящим через время -fcj после первого импульса, в усилителе 1 устанавЛЙвается коэффициент передачи К - 2 и запускается аналого-цифровой преобразователь, который кодирует усиленную в К раз разность Ux Оцу. Полученный код сдвигается на vj разряда, т.е. делится на 2, записывается в сумматор 4 и суммируется с записанным в нем кодом N.. Если за время -fc изменение входного напряжения превзойдет заданную уставку(и-чц.Т1) сработает один из . компараторов 8 или 9, и в момент стробировайия через один из кгвочей 23 или 24 произойдет запрет на прохождение второго импульса в блоке 17 на второй цикл преобразования. Код соответстввющей уставки перепи сывается в сумматор 4, суммируется с хранящ.имся там кодом первого результата преобразования Кч( и выдается из сумматора 4 на выход устройства

как результат аналого-цифрового преобразования. Одновременно с процес сом кодирования интерационно выбирается интервад дискретизации входного сигнала. По требуемой погрешности определения интервала дискретизации с учетом вида алгоритма, реализуемого усреднителями 11 и 12, назначается величина постоянной усреднения о (например, объем усредняемой выборки и значение заданной погрешности Ла -млаДшие разряды усреднителя ГТ) , а также назначается объем выборки между циклами корректировки интервала дискретизации Ц (и- коэффициент пересчета делителя 21 частоты. Счет чик 18 сбрасывается в О и устанавливается начальный минимальный интервал дискретизации между двумя соседними запусками аналого-цифрового преобразователя. Начальный шаг дискретизации задается с учетом частоты генератора 16 импульсов и значения начального коэффициента пересчета регулируемого делителя 17 частоты. В усреднителе 11 по дискретной выборке определяется грубая оценка среднего значения, которой в блоке 13 вычитания центрируется дискретизированный во времени исследуемый процесс. Грубо центрируемая выборка О/п7 фаг. I

усредняется в усреднителе 12 и полученный результат Дл после прохождения выборок сравнивается с задан ным порогом А|, поступающим с младших разрядов первого усреднителя 11. В зависимости от результата срав нения мерез ключ 19 счетчик 18 добавляется или О, благодаря чему автоматически устанавливается новое значение интервала дискретизации регулируемом делителе 17 частоты, затем сбрасывается содержимое усреднителей 11 и 12.

Устройство работает циклически. После каждыхц выборойосуществляется корректировка интервала дискретизации и после нескольких циклов работы устройство автоматически согласует интервал дискретизации исследуемого процесса с его интервалом корреляции.

Именно за счет этого и происходит расширение функциональных возможностей устройства, так как оно осуществляет аналого-цифровое преобразование с декорреляцией выборочных значений и позволяет дополнительно получить грубую оценку интервала корреляции исследуемого процесса, что одновременно приводит к увеличению облакети применения. ffm ffm 8 ff t I И I 1 гJ,г Л II (Dtffd Ml II I I M M M I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобразования | 1980 |

|

SU949806A1 |

| Устройство для сжатия информации | 1979 |

|

SU809297A1 |

| Анализатор спектра | 1977 |

|

SU732759A1 |

| Устройство для сжатия информации | 1980 |

|

SU930333A1 |

| Адаптивный коррелометр | 1977 |

|

SU696478A2 |

| Устройство для определения временного шага дискретизации случайного сигнала | 1977 |

|

SU656047A1 |

| Устройство для аналого-цифровогопРЕОбРАзОВАНия | 1979 |

|

SU815898A1 |

| Измеритель коэффициента гар-МОНиК | 1979 |

|

SU819737A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU873405A1 |

| Адаптивный статистический анализатор | 1987 |

|

SU1434453A1 |

УСТРОЙСТВО ДЛЯ АНАЛОГО-ЦИФ-. РОВОГО ПРЕОБРАЗОВАНИЯ по авт. св. Vf 815898, отличающееся тем, что, с целью расширения функ-ч циональных возможностей, в него введены блок сравнения, блок вычитания, певый и второй усреднители, причем вход первого усреднителя и первый вход блока вычитания соединены с вторым выходом сумматора, второй вход блока вычитания соединен с пер вым выходом первого усреднителя, а выход подключен к выходу второго усреднителя, выход которюго соединен с первым входом блока сравнения, второй вход которого подключен к второму й 1ходу первого усреднителя, а выход соединен с дополнительным входом блока управления.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для аналого-цифровогопРЕОбРАзОВАНия | 1979 |

|

SU815898A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-07-07—Публикация

1982-03-23—Подача