1

Изобретение относится к области вычислительной техники для измерения вероятностных характеристик случайных сигналов и предназначено для определения временного шага выробки сигнала при измерении ординат функции и плотности распределения, математического ожидания, моментов высших порядков.

Известно устройство, в котором для повышения точности измерения нормированной корреляционной функции входного случайного сигнала сохраняется относительная ошибка восстановления. Устройство содержит сравниваю щее устройство, устройство управления, логическое устройство, счетчик, реверсивный счетчик, цифро-аналоговый преобразователь, состоящий из регистра памяти, двух разнополярных источников образцовых напряжений, измерительных ключей и дискретного делителя, источник дополнительных образцовых напряжений, состоящий из дискретного делителя, дополнительных измерительных ключей и двух резкополярных источников образцовых напряжений, масштабирующего делителя и схем совпадений 1.

Недостатком этого устройства является сложность схемного решения, в частности наличие двух цифро-аналоговых преобразователей с управлением.

Наиболее близким техническим решением к предлагаемому является устройство, содержащее счетчик, входы счета и сброса которого соединены соответственно с первым и вторым выходами блока управления, первый вход которого соединен с управляющим выходом компаратора, первая группа входов которого подключена к разрядным выходам счетчика, а вторая группа входов - к разрядным выходам реверсивного счетчика, входы сложения и вычитания которого подключены к выходам логического блока, первый вход которого, соединен с выходом первого

9 блока сравнения, управляющий вход которого соединен с третьим выходом блока управления, а первый вход - с первым выходом блока памяти, вход которого является входом устройства

5 и подключен ко второму входу блока управления, второй выход блока памяти соединен с входом блока деления 2j

Устройство позволяет автоматически определять оптимальный интервал

0 дуборки случайного сигнала в зависимости от скорости изменения сигнала. Недостатком известного устройства является также сложность схемного

решения.

Целью предлагаемого изобретения является повышение быстродействия пр упрощении устройства определения временного шага дискритизации сигнала йри расширении частотного диапазона исследуемых сигналов в области высоких частот за счет одтэтактного (параллельного) сравнения величины приращения сигнала с величиной заданной относительной ошибки восстановления.

Для .достижения поставленной цели устройство дополнительно содержит второй блок сравнения и блок суммирования, первый вход которого соединен с выходом блока деления, второй вход - с вторым выходом блока памяти выходы блока суммирования подключены соответственно к второму входу перво1 о блока сравнения и к первому входу второго блока сравнения, управляющий вход которого соедине с четвертым выходом блока управления, второй вход второго блока сравнения подключен к первым входам блока памяти и первого блока сравнения, выход второго блока сравнения соединен с вторым входом логического блока, управляющий вход реверсивного счетчика подключен к третьему входу блока управления и управляющему выходу блока памяти.

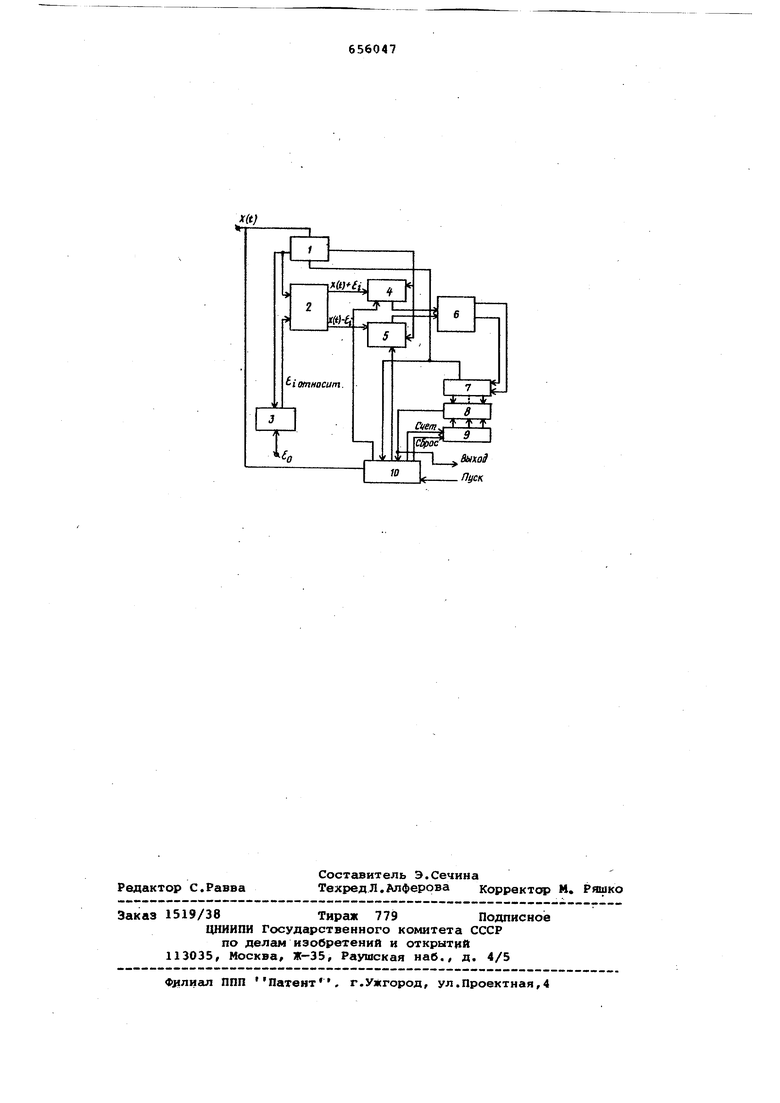

Блок-схема устройства приведена на чертеже.

Устройство содержит блок 1 памяти (аналоговой;, на вход которого подан исследуемый случайный сигнал, который, кроме того, подан на входы блока суммирования 2 и блока деления 3. Выход блока деления 3, в котором задается относительная ошибка восстановления CQJ , соединен с вторым входом блока суммирования 2. Выход блока суммирования 2 соединен с входаш. первого блока 4 сравнения и второго блока 5 сравнения, вторые входы которых соединены с выходом блока 1 памяти. Выходы блоков сравнения через логический блок 6 соединен с входом реверсивного счетчика 7. Выходы реверсивного счетчика 7 соединены с входами цифрового компаратора 8. Входы счетчика 9 также соединены с входами компаратора 8. На другие входы счетчика 9 подключены сигналы сброса и тактовой частоты от блока 10 управления, другие входы которого соединены с входами блоков 1,4 и 5, а вход блока 10 управления соединен с выходом компаратора 8.

Устройство работает следующим образом. В блоке деления 3 задается Значение относительной ошибки восстановления случайного сигнала зависимости от текущего значения амплитуды случайного сигнала х (t) на

выходе блока деления 3 формируются текущие значения относительной ошибки восстановления сигнала

, «((.)

г..-,

которые поступают в блок суммирования 2.

При подаче сигнала пуск устройство устанавливается в начальное состояние - блоком 10 управления сбрасывается счетчик 9 и включается в режим запоминания блок 1, который фиксирует текущее значение случайного сигнала х (t),После окончания аналогового запоминания случайного сигнала от блока управления 10 на вход счетчика 9 начинают поступать счетные импульсы, т.е. начинается формирование временного шага дискретизации входного сигнала. После сброса устройства в начальное состояние код реверсивного счетчика 7 соответствует нулевому значению. Нулевому значению соответствует в начале работы устройства и интервал дискретизации, так как компаратор 8 сразу же формирует выходной сигнал. Далее, в процессе работы устройства код реверсивного счетчика 7 изменяется.

Импульсы блока управления 10, поступая в счетчик 9, формируют в нем код, равный коду реверсивного счетчика 7. При равенстве кодов срабатывает цифровой компаратор 8, который формирует выходной сигнал и. через блок управления 10 подает одновременно сигналы строба на первый и второй блоки сравнения 4 и 5. На вход первого блока 4 сравнения с блока суммирования 2 подается текущее значение случайного сигнала в сумме с относительной ошибкой восстановления x(t). +Е , одновременно на вход второго блока 5 сравнения с блока суммирования 2 подается разность значений случайного сигнала и относительной ошибки восстановления x(t) - j . На вторые., входы блоков 4 и 5 с выхода блок 1 памяти подается ранее запомненное значение случайного сигнала x(t + ) , где t - задержка времени, пропорциональная коду реверсивного счетчика 7. Результаты этих сравнений фиксируются логическим блоком 6.

В зависимости от результатов сравнения блоками 4 и 5 логический блок Б формирует следующие команды на вход реверсивного счетчика 7.

В случае, если

x(-fc + € ) x(i;) + Е; или x(t + t ) x(t) - ,

код реверсивного счётчика 7 и шаги дискретизации растут на квант.

В случае, если x(t + t ) x(t) +, или x(t + ) x(t) -Cj код реверсивного счетчика 7 и шаг дискретизации уменьшаются на квант.

В случае, если х (1 + С )«: х (t) - или x(-t +t ) x(t) + код реверсивного счетчика 7 и шаг дискретизации уменьшаются на квант.

После сравнения кодов счетчика 9 и реверсивного счетчика 7 компаратором 8 код счетчика 9 сбрасывается и начинается новый цикл работы устройства, аналогичный предыдущему. В результате работы устройства после прохождения N циклов устанавливается значение кода реверсивного счетчика 7 при следующем равенстве вероятностей

.tl-xti)e,(t.cbx(t).E

При этом на выходе компаратора 8 формируется частота выборок случайного стационарного эргодического сигнала, которая может быть использована при оптимальном нахождении оценок функции и плотности распределения, математического ожидания, моментов и прочее.

После сброса устройство работает с минимальным интервалом дискретизации. При этом в блоке 1 памяти включается запоминающий конденсатор (на чертеже не показан) минимальной емкости, а блок 10 управления при этом формирует минимальное время запоминания .

Диапазон интервалов, код реверсивного счетчика, разбит равномерно на несколько частей. При достижении интервалом дискретизации одной из указанных границ в блоке 1 автоматичес:И подключается соответствующий запоминающий конденсатор. С ростом интервала дискретизации растут величины запоминающих конденсаторов, при уменьшении интервала - величины конденсаторов уменьшаются. Одновременно с переключением запоминающего конденсатора в блоке 1 изменяется время запоминания, строб блока 1, которое формируется в блоке управления 10.

Таким образом, погрешность от разряда запоминающего конденсатора сохраняется близкой и постоянной, не зависящей от частотного спектра случайного сигнала.

Такое устройство позволяет упростить аппаратуру при одновременном увеличении быстродействия. Это выгодно отличает предлагаемое устройство от известных, так как уменьшается погрешность измерения стати 1еских характеристик сигнала и расширяется

частотный диапазон измеряемых случайных сигналов. Все зто уменьшит расходы на изготовление и увеличит сферу применения устройства и, следовательно, дает технико-экономический эффект.

Формула изобретения

Устройство для определения временного шага дискретизации случайного

0 сигнала, содержащее счетчик, входы (счета и сброса которого соединены со ответственно с первым и вторым выходами блока управления, первый вход которого соединен с управляющим выходом компаратора, первая группа вхо5дов которого подключена к разрядным выходам счетчика, а вторая группа входов - к разрядным выходам реверсивного счетчика, входы сложения и вычитания которого подключены к вы0ходам логического блока fпервый вход которого соединен с выходом первого блока сравнения, управляющий вход которого соединен с третьим выходом блока управления, а первый вход - с

5 первым выходом блока памяти, вход которого является входом устройства и подключен ко второму входу блока управления, второй выход блока памяти соединен с входом блока деления,

0 отличающееся тем, что, с целью повышения быстродействия при упрощении устройства, оно содержит второй блок сравнения и блок суммирования, первый вход которого соеди5нен с выходом блока деления, второй вход - с вторым выходом блока памяти, выходы блока суммирования подключены соответственно к второму входу первого блока сравнения и к первому входу второго блока сравнения,

0 управляющий вход которого соединен с четвертым выходом блока управления, второй вход второго блока сравнения подключен к первым входам блока памяти и первого блока сравнения, вы5ход второго блока сравнения соединен с вторым входом логического блока, управляющий вход реверсивного счетчика подключен к третьему входу блока управления, и управляющему выходу блока памяти.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР №436438, кл. Н 03 К 13/17, 1971.

5

2,Авторское свидетельство СССР №226970, кл. G 06 J 5/00, 1967.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения времен-НОгО шАгА диСКРЕТизАции СигНАлА | 1978 |

|

SU807337A2 |

| Устройство для определения функции распределения | 1974 |

|

SU528573A1 |

| Устройство аналого-цифрового преобразования | 1977 |

|

SU641646A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПЛОТНОСТИ РАСПРЕДЕЛЕНИЯ ВЕРОЯТНОСТЕЙ СЛУЧАЙНОГО ПРОЦЕССА | 2000 |

|

RU2174706C1 |

| Статистический анализатор экстре-мумов | 1974 |

|

SU508787A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1343551A1 |

| Устройство для кодирования аналоговой информации | 1986 |

|

SU1338074A1 |

| Устройство для восстановления сигналов | 1988 |

|

SU1608706A1 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

Авторы

Даты

1979-04-05—Публикация

1977-04-18—Подача