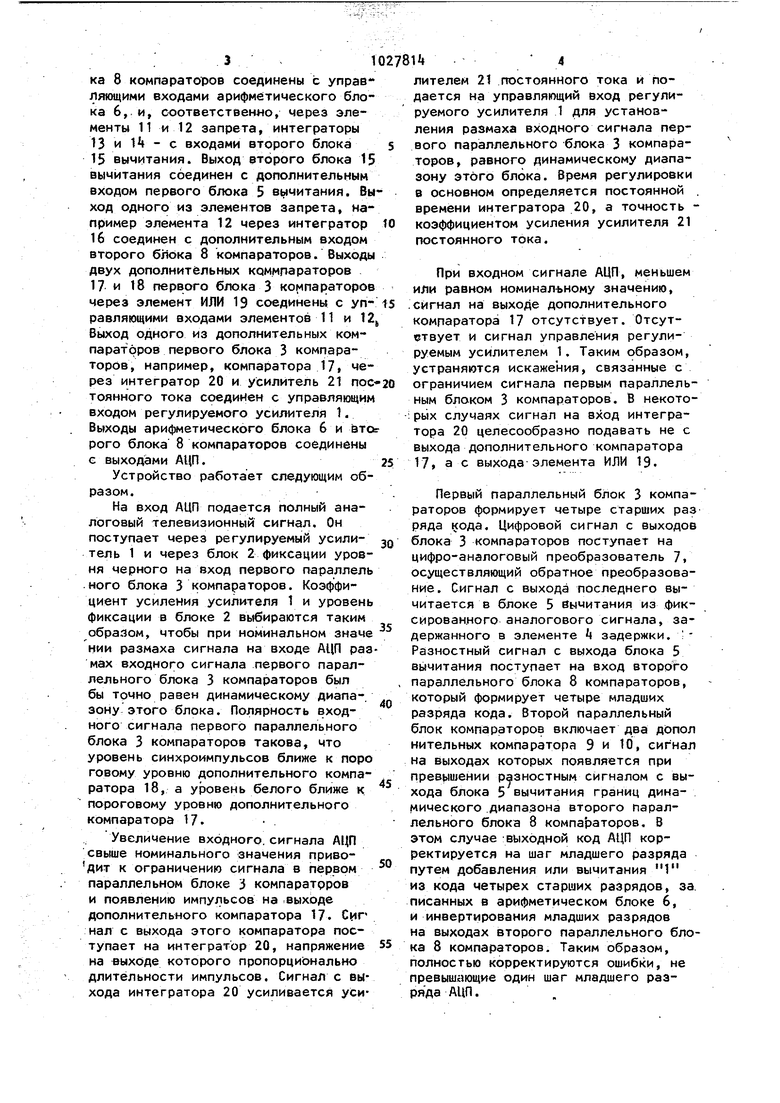

J Изобретение относится к технике, связанной с преобразованием сигнало в системах с импульсно-кодовой модуляцией. Для целей преобразования полного телевизионного сигнала в цифровую форму наиболее часто используются аналого-цифровые преобразователи ( АЦП) последовательно-параллельного типа. По основному авт.св. Vf 855993, известен аналого-цифровой преобразователь содержащий первый параллельный блок компараторов, вход которого соединен через элемент задержки с первым входом блока вычитания, второй вход которого соединен с выходом цифро-аналогового преобразователя (ЦАП), а выход - с входом второго параллельного блока компараторов, выходы двух дополнительных компараторов которого соединены с управляющими входами арифметического блока, входы которого соединены с выходами первого параллельного блока компараторов и входа ми ЦАП, а выходы - с выходами старших разрядов аналого-цифрового преобразователя, выходы младших разг рядов которого соединены с выходами второго параллельного блока компараторов, выходы двух дополнительных компараторов первого параллельного блока компараторов через элемент ИЛ соединены с управляющими входами двух элементов запрета, вторые вход которых соединены с выходами двух дополнительных компараторов второго параллельного блока компараторов, а выходы через соответствующие первый и второй интеграторы - с входами дополнительного блока вычитания, выход которого соединен с дополнительным входом первого блока вычитания, выход первого элемента запрета через третий интегратор соеди нен с дополнительным входом второго параллельного блока компараторов. В этом устройстве приняты эффективные меры для снижения искажений сигнала в АЦП путем коррекции инстр ментальных погрешностей преобразова ния, .но не -учтено влияние искажений ( ujyMOB) ограничения ГООсновной недостаток такого АЦП низкая точность преобразования, а также сильные искажения выходного сигнала при ограничении входного те левизионного сигнала в первом парал лельном блоке компараторов; невозможность коррекции ошибок преобразования величиной как превышающей, так и не превышающей шага квантования при превышении диапазоном изменения входного сигнала динамического диапазона первого параллельного блока компараторов. Цель изобретения - уменьшение погрешности преобразования. Поставленная цель достигается тем, что в аналого-цифровой преобразователь введены последовательно соединенные четвертый интегратор, усилитель постоянного тока, регулируемый усилитель и блок фиксации уровня черного, выход которого соединен со входом первого параллельног го блока компараторов, выход одного из дополнительных компараторов которого соединен со входом четвертого интегратора, при этом второй вход регулируемого усилителя соединен с входной клеммой. Сущность изобретения заключается в том, что вновь введенные узлы и связи позволяют автоматически уменьшать величину сигнала на входе первого параллельного блока компараторов до номинального значения, равного динамическому диапазону этого блока, при увеличении сигнала на входа АЦП сверх номинального значения и таким, образом устранить искажения сигнала, связанные с ограничением сигнала в первом блоке компараторов, что, в свою очередь, позволяет обеспечить гарантированную высокую точность АЦП в широком диапазоне изменения входного сигнала ,за счет более полного использования цепей автоматической коррекции ошигбок преобразования. На чертеже представлена структурная электрическая схема АЦП. Клемма Вход соединена че)ез регулируемый усилител.ь 1 и блок 2 фиксации уровня черного с входом первого параллельного блока 3 компараторов, а также через элемент k задержки с входом первого блока 5 вычитания. Выходы первого параллельного блока 3 компараторов соединены с арифметическим блоком б и через цифро-аналоговый преобразователь ( ЦАП7 7, блок 5 вычитания с входом второго параллельного блока, 8 компараторов. Выходы дополнитель ных компараторов Э и 10 второго бп(. ка 8 компараторов соединены с управляющими входами арифметического блока 6, и, соответственно, через элементы 11 и 12 запрета, интеграторы 13 и Н - с входами второго блока 15вычитания. Выход второго блока 15 вычитания соединен с дополнительным входом первого блока 5 вычитания. Вы ход одного из элементов запрета, например элемента 12 через интегратор 16соединен с дополнительным входом второго блока 8 компараторов. Выходы двух дополнительных коммпараторов 1 и 18 первого блока 3 компараторов через элемент ИЛИ 19 соединены с управляющими входами элементов 11 и 12 Выход одного из дополнительных компараторов первого блока 3 компараторов, например, компаратора 17, через интегратор 20 и усилитель 21 пос тоянного тока coeдиt eн с управляющим входом регулируемого усилителя 1. Вьтходы арифметического блока 6 и вто рого блока 8 компараторов соединены с выходами АЦП. Устройство работает следующим образом. На вход АЦП подается полный аналоговый телевизионный сигнал. Он поступает через регулируемый усилитель 1 и через блок 2 фиксации уровня черного на вход первого параллель ного блока 3 компараторов. Коэффициент усиления усилителя 1 и уровень фиксации в блоке 2 выбираются таким образом, чтобы при номинальном значе НИИ размаха сигнала на входе АЦП раз мах входного сигнала первого параллельного блока 3 компараторов был бы точно равен динамическому диапа-. зону этого блока. Полярность входного сигнала первого параллельного блока 3 компараторов такова, что уровень синхроимпульсов ближе к поро говому уровню дополнительного компаратора 18, а уровень белого ближе к пороговому уровню дополнительного компаратора 17. Увеличение входного, сигнала АЦП свыше номинального значения привоtдит к ограничению сигнала в первом параллельном блоке 3 компаратрров и появлению импульсов на (Выходе дополнительного компаратора 17. Сиг нал с выхода этого компаратора поступает на интегратор 20, напряжение на выходе которого пропорционально длительности импульсов. Сигнал с выхода интегратора 20 усиливается усилителем 21 постоянного тока и подается на управляющий вход регулируемого усилителя 1 для установления размаха входного сигнала первого параллельного блока 3 компараторов, равного динамическому диапазону этого блока. Время регулировки в основном определяется постоянной . времени интегратора 20, а точность коэффициентом усиления усилителя 21 постоянного тока. При входном сигнале АЦП, меньшем или равном номинал-ьному значению, .сигнал на выходе дополнительного компаратора 17 отсутствует. Отсутствует и сигнал управления регулируемым усилителем 1. Таким образом, устраняются искажения, связанные с ограничием сигнала первым параллельным блоком 3 компараторов. В некоторь1х случаях сигнал на вход интегратора 20 целесообразно подавать не с выхода дополнительного компаратора 17, ас выхода элемента ИЛИ 19. Первый параллельный бЛок 3 компараторов формирует четыре старших раз ряда кода. Цифровой сигнал с выходов блока 3 компараторов поступает на цифро-аналоговый преобразователь 7, осуществляющий обратное преобразование. Сигнал с выхода последнего вычитается в блоке 5 вычитания из фиксированного аналогового сигнала, задержанного в элементе k задержки. Разностный сигнал с выхода блока 5 вычитания поступает на вход BTopofo параллельного блока 8 компараторов, который формирует четыре младших разряда кода. Второй параллельный блок компараторов включает два допол нительных компаратора Э и 10, сигнал на выходах которых появляется при превышении разностным сигналом с выхода блока 5 вычитания границ динамического диапазона второго параллельного блока 8 компараторов. В этом случае :вых6дной код АЦП корректируется на шаг младшего разряда путем добавления или вычитания 1 из кода четырех старших разрядов, за. писанных в арифметическом блоке 6, и инвертирования младших разрядов на выходах второго параллельного блока 8 компараторов. Таким образом, полностью корректируются ошибки, не превышающие один шаг младшего разряда АЦП.

Коррекция ошибок, превышающих эту величину, производится следующим.об разом.

Смещение диапазона изменения значений разностного сигнала на входе второго параллельного блока 8 компараторов относительно динамического диапазона последнего приводит к различной вероятности появления импульсов на выходах дополнительных компараторов 9 и 10. Си|- налы с выходов этих компараторов через элементы 11 и 12 запрета поступают на входы соответствующих интеграторов 13 и Й напряжения на вы ходах которых пропорциональны вероятности появления импульсов на выходах дополнительных компараторов 9 и 10. С выхода дополнительного блока 15 вычитания снимается сигнал, пропорциональный разности этих напряжений, который используется для восстановления симметрии диапазона изменения значений разностного сигнала относительно середины динамического диапазона второго параллельного блока 8 компараторов, С этой целью он подается на дополнительный вход блока 5 вычитания. При симметрии диапазона изменения значений разностного сигнала относительно середины динамического диапазона второго параллельного блока 8 компараторов, в случае их совпадения импульсы на выходах дополнительных компараторов 9 и 10 отсутствуют.

При недопустимом превышении диапазоном изменения значений разностного сигнала динамического диапазона второго параллельного блока 8 компараторов, на выходах обоих допол нительных компараторов 9 и 10 с одинаковой вероятностью появляются импульсы. Эти импульсы с выходов одного из дополнительных компараторов 9 или 10, например компаратора 10, через элемент 12 запрета подаются на интегратор 14, напряжение на выходе которого пропорционально Вероятности появления импульсов на его входе. Это напряжение используется для подстройки динамического диапазона второго параллельного блока 8 компараторов в соответствии с диапазоном изменения значений разностного сигнала на его входе. При . превышении размаха входного сигнала АЦП номинального значения в процессе автоматического регулирования усиления усилителя 1 возможно ограничение входного сигнала в первом параллельном блоке 3 компараторов, приводящее к ограничению разностног сигнала во втором параллельном блоке 8 компараторов и появлению импульсов на выходах дополнительных компараторов 9 и 10. Это может привести к нежелательному изменению сигналов управления на дополнительных входах блока 5 вычитания и второго параллельного блока 8 компараторов. С целью исключения этого явления, в первый параллельный блок 8 компараторов введены два дополнительных компаратора 17 и 18 (аналогично двум дополнительным компараторам 9 и 10 во втором параллельном блоке 8 компараторов). При ограничении входного аналогового сигнала на их выходах возникают импульсы, которые объединены элементом ИЛИ 19 и подаются на управляющие входы обоих элементов 11 и 12 запрета. Таким образом, в этом случае импульсы с выходов дополнительных компараторов 9 и 10 не проходят на входы интеграторов 13, Т и 16, и ложной коррекции погрешности преобразования не происходит.

Если выбрать постоянную времени интегратора 20 малой, значительно меньшей постоянной времени интеграторов 13, Т и 16, то время автоматического регулирования коэффициента усиления регулируемого усилителя 1, время, в течение которого происходит ограничение сигналов в первом и втором параллельных блоках компараторов, а следовательно, и величина сигналов ложной коррекции тна дополнительных входах блока 5 вычитания и второго параллельного блока 8 компараторов будут малыми. В этом случае ошибкой преобразования, вызванной ложной коррекцией, вследствие ее малости можно пренебречь. Тогда возможно исклюмение из схемы АЦП эле ментов 11 и 12 запрета. .

Для устойчивости работы цепи компенсации погрешности преобразования необходимо иметь постоянную време-, нй интегратора Тб, большуюпостоянной времени интеграторов 13 иТ. Тогда пр возникновении одновременно ошибок смещения и согласования диапазонов обеспечивается регулирование динамического диапазона второго параллельного блока 8 компараторов после окончания компенсаиии смещения..

Технико-экономический эффект заключается в том, что. вновь введенные элементы и связи позволяют изменять динамический диапазон входного сигна ла, поступающего на первый параллель ный блок 8 компараторов так, что он всегда меньше или равен динамическому диапазону первого- параллельного блока компараторов. Поэтому при работе АЦП отсутствуют ошибки;преобразования, связанные с ограничением « сигнала в первом параллельном бЛоке компараторов. Кроме того, ошибки преобразования, превышающие один шаг йвантованИя,вне зависимости от величины входного сигнала ЛЦП, уменьшаются до шибок, не превышающих один шаг квантования. Эти ошибки, в свою очередь, корректируются с помощью дополнительных компараторов и арифметического блока. Таким образом, в устройстве достигается уменьшение по грешности аналого-цифрового преобразования и обеспечивается высокая

стабильность характеристик в процессе эксплуатации без проведения ручных регулировочных операциЙ7 что позволяет повысить устойчивость к воздействию дестабилизируюи|их 11 акторов и эксплуатационные харакТерИстики. аппаратуры цифрового телевидения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1979 |

|

SU855993A1 |

| Устройство формирования испытательных сигналов для цифровой телевизионной системы передач | 1985 |

|

SU1290566A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2045813C1 |

| Устройство контроля цифровых световодных систем передачи информации | 1986 |

|

SU1319290A1 |

| СПОСОБ ГЕОЭЛЕКТРОРАЗВЕДКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2006886C1 |

| ВЫСОКОИНФОРМАТИВНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ИСПОЛЬЗОВАНИЕМ ДЕЛЬТА-МОДУЛЯЦИИ ДЛЯ СЕЙСМИЧЕСКИХ ИССЛЕДОВАНИЙ | 1997 |

|

RU2128880C1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1418903A1 |

| Кодирующее устройство для передачи телевизионных сигналов | 1987 |

|

SU1555915A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2496228C1 |

| РЕВЕРСИВНЫЙ ЧИСЛО-ИМПУЛЬСНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2429563C1 |

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ по авт.св. № 855993, о т ,личаю1цийся тем, что, с целью уменьшения погрешности преобразования, введены последовательно соединенные четвертый инвертор, усилитель постоянного тока, регулируемый усилитель и блок фиксации уровня черного, выход которого соединен со входом первого параллельного бло ка компараторов, выход одного из дополнительных компараторов которого соединен со входом четвертого интегратора, при этом второй вход регулируемого усилителя соединен с входной клеммой. 1чЭ 00

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU855993A1 |

Авторы

Даты

1983-07-07—Публикация

1982-02-11—Подача