(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1982 |

|

SU1027814A2 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1056449A1 |

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| Устройство формирования испытательных сигналов для цифровой телевизионной системы передач | 1985 |

|

SU1290566A1 |

| СЛЕДЯЩИЙ АЦП МНОГОРАЗРЯДНЫХ ПРИРАЩЕНИЙ | 2016 |

|

RU2619887C1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2045813C1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012131C1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Преобразователь угла поворота вала в код | 1989 |

|

SU1633492A1 |

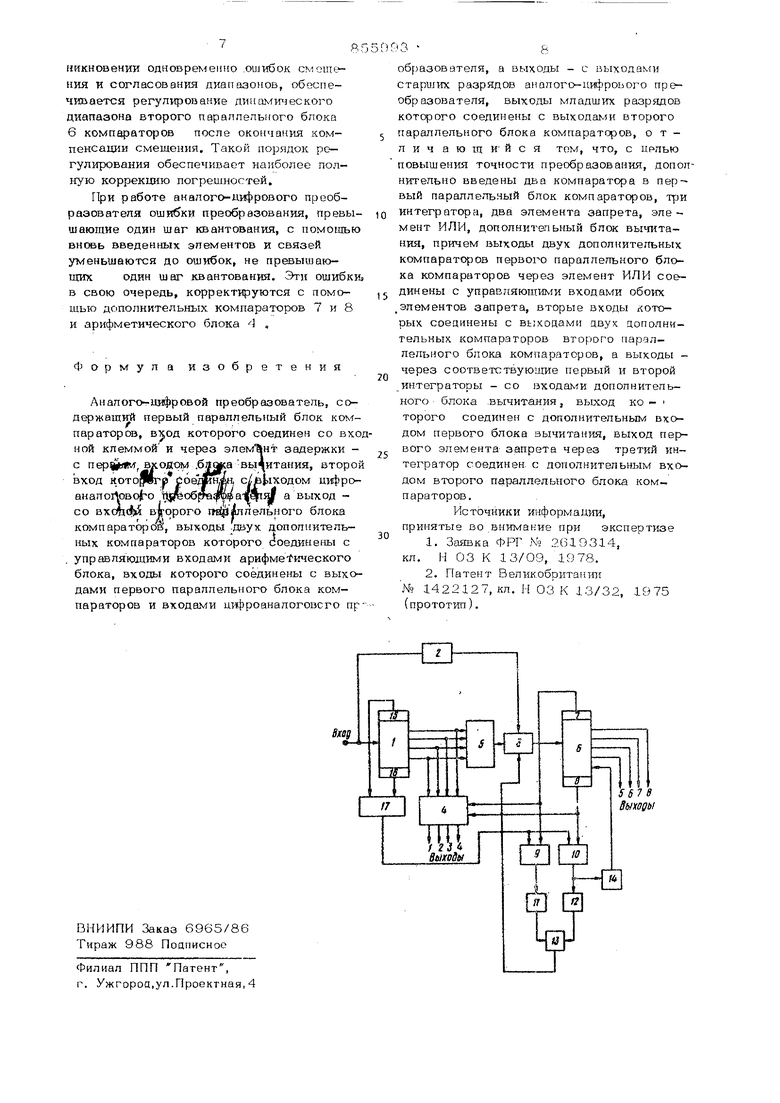

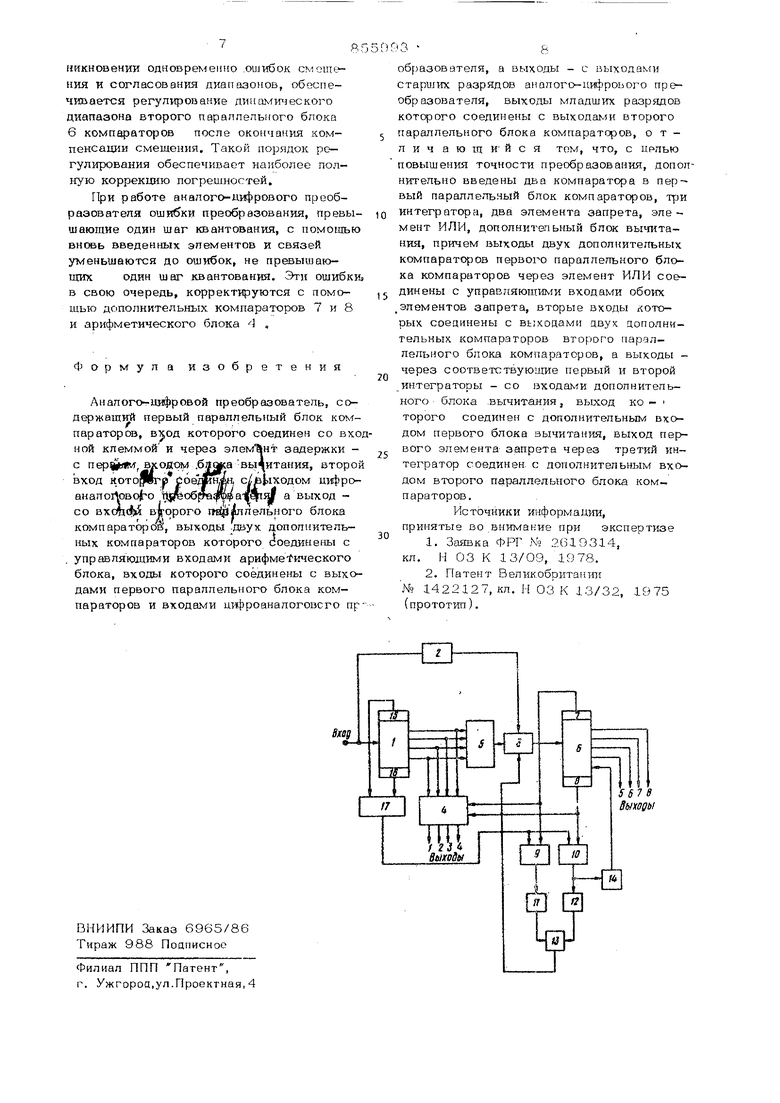

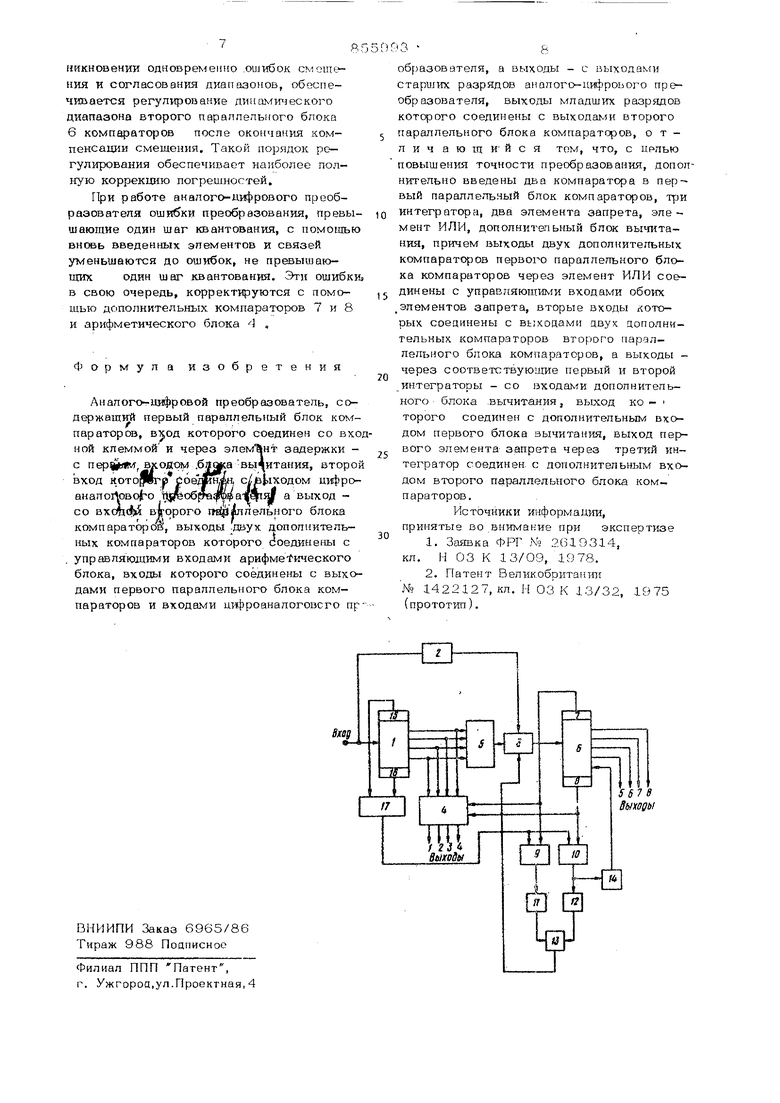

Изобретение относится к технике, связанной с преобразованием сигшпов в системах с импупьсно-кодовой модуляцией. Дпя целей преобразования широкопопоснык аналоговых сигналов в цифровую форму наиболее часто используются аналого-ци{)рОБые преобразователи (АЦП) поспедгаьатепьно-параллепьного типа. Известно устройство последовательно параллельного аналого-цифрового преобра зсгаакия, содЕфжащее один каскад грубого преобразования, один каскад точного преобразования, один ци})роаналоговый преобразователь (ЦАП), вычитающее уст ройстЕО и цифровой сумматор. Сигнал поступает на вхоа каскаца грубого преобразования, который формирует четы старших разряда кода. Цифровой сигнал с выходов каскада грубого преобразования поступает на UAfI, осуществляющий обратное преобразование. Сигнал с выход ЦАП вычитается в вычитающем устройст из входного аналогового сигнала. Раэностный сигнал поступает на вход каскада точного преобразования, который формирует че1ыре младших кода Г13 . Однаковэтом устройстве не предусмотрена коррекция ошибок преобразования. Наиболее близким по технической сущности и достигаемому результату к предлагаемому является аналого-цифровой преобразователь, содержащий первый параллельный блок компараторов, вход которого соединен со входной клеммой и через элемент задержки - с первым входом блока вычитания, второй вход которого соединен с выходом цифроаналогового преобразователя, а выход - со входом второго параллельного блока компараторе, выходы двух дополнительных компараторов которого соединены с управляющими входами ариф- метического блока, входы которого соединены с выводами первого параллельного блока компараторов и входами Ц|фроаиалогового преобразователя, а выходыс выходами старших разр5шов аналогоцифрового преобразователя, выходы младtaroc разрядов соединены с выход дами второго параллельного блока комп раторов. С цепью коррекции ошибок преоб разования во второй параллельный блок компараторов этого устройства введены два дополнительных компаратора, сигналы с выходов которых поступают на арифмети ческий блок. При попадании разнос7ного сигнала на входе второго параллельного блока компараторов за пределы его динами ческого диапазона по сигналу с выхода одного из дополнительных компараторов производится коррекция выходного кода на один шаг младшего разряда А ЦП. Введение такой коррекиш повышает точность преобразования и снижает требования к качеству работы первого параллельного блока компараторов . Недостаток такого АЦП невозможность коррекции ошибок , возникающих за счет неточной работы ЦАП, блока вычитания и второго параллельного блока компараторов, приводящей к ошибкаКТ, превышающим один шаг младшего разряда. Цель изобретения - повышение точности преобразования. Поставленная цель достигается тем, .что в аналого-цифровой преобразователь содержащий первый параллельный блок компараторов, вход которого соединен со входной кпеммой и через элемент задержки-с первым входом блока вычитания, второй вход которого соединен с выходом цифроаналогсвого преобразователя, а вы-. ход -со входом второго параллельного блока компараторов, выходы двух дополнительных компараторов которого соедине ны с управляющими входами арифметичес кого блока, входы которого соединены с выходами первого параллель юго блока компараторов и входами Ц14)роаналогового преобразователя,а выходы - с выходами старших разрядов аналоге- цифрового преоб разователя, выходы младших разрядов ко торого соединены с выходами второго параллельного блока компараторов „ дополнительно введены два компаратс- - ра в первый параллельный блок компараторов, три интегратора, два элемента запрета, эпемент ИЛИ, допопнитеп 11ЫЙ блок вычитания, причем выходы двух дополнительных кся параторов первого па раллельного блока компараторов через эл мент ИЛИ соединены с управляющими входами обоих элементов запрета, вторы входы которых соединены с выходами двух дополнительных компараторов второ го параллельного блока компаратс ов, а выходы - через соответствующие первый и второй интеграторы со входами допопнительно-го блока вычитания, выход которого соединен с дополнительным входом первого блока вычитания, выход первого элемента запрета через третий интегратор соединен с дополнитшьным вхо дом второго параллельного блока компараторов. Сущность изобретения заключается в том, что вновь введенные элементы и связи позволяют корректировать ошибки преобразования, возникающие из-за смещения диапазона значений разност ного сигнала на выходе первого блока вычитания, относительно динамического диапазона второго параллельного блока компараторов, а также из-за изменения дш амического диапазона второго параллельного блока компараторов. Тем самым не только сн1ГАаются требования к точности работы соответствующих узлов, но и обеспеч шаются наилучшие условия для осуществления цифровой коррекции ошибок. На чертеже представлена структурная схема предлагаемого АЦП. Входная клемма соединена со входом первого параллельного блока 1 KOivmapaторов и, через элемент 2 задержки - со входом блока 3 вычитания. Выходы первого параллельного блока 1 компараторов соединены с арифметическим блоком 4 и через цифроаналоговый преобразователь5 и блок 3 вычитандя - со входом второго паралпельноп) блоха 6 компараторов, выходы дополнительных ко1лпараторов 7и в второго параллельного блока 6 компараторов соединены с управляющими входами арифметического блока 4 и, соответственно, через элементы 9 и 10 за-прета интеграторы 11 и 12 - со входами дополнительного блока 13 вычитания. Выход дополнительного блока 13 вычитания соединен с дополнительным входом блока 3 вычитания. Выход ал агента 10 запрета через интегратор 14 соединен с дополнительным входом второго параллельного блока 6 компараторов. Выходы двух дополнительных компараторов 15 и 16 nepBOiO параллельного блока 1 компараторов через элемент ИЛИ 17 соединены с управляющими входами элементов 9 и 10 запрета. Выходы арифметического блока 4 и второго параллельного блока 6 компара торов соединены с выходами А1Я1,

Устройство работает следующим образом.

На вход AUn подается аналоговый сигнал. Он поступает на вход первого п& ралпепьного блока 1 компараторов, который формирует четыре старших разряда кода. Ци})ровой сигнал с выходов первого параллельного блока 1 компараторов поступает на щ{фроаналоговый преобразова- тепь 5, осуществляющий обратное npedeразование. Сигнал с выхода последнего вычитается в блоке 3 вычитания из жходного аиапогсжого сигнала, задержанного в элементе 2 задержки. Разностный сигнал с выхода блока 3 вычитания поступает на вход второго параллельного блока кот- параторов 6, который формирует четыре младших разряда кода. Вто - рой параллельный блок 6 комаарато ров включает два дополнительных компаратора 7 и 8, сигнал на выходах которых появляется при превышении разност ным сигиапом с выхода блока 3 вычитания границ динамического диапазона второго параллельного блока 6 компараторов. В этом случае выходной код АЦП коректируется на шаг младшего разряда путем добавления или вычитания логической из кода четырех старштгх разрядов, записанных в арифметическом блоке 4 и инвертирования младших разрядов на выходах второго параллельного блока 6 компараторе®. Таким образом, полностью корректируются ошибки, не превышающие один шаг младшего разряда А ЦП. Для коррекции ошибок, превышаюгогх эту величину, и служат дополнительно введенные элементы и связи.

Смещение диапазона изменения знач&ний разностного сигнала на входе второго параллельного блока 6 компараторов отно ситепьно динамического диапазона последнего приводит к различной вероятности появления импульсов на выходах дополнительных компараторсе 7 и 8. Сигналы с выходов этих компараторов через элементы 9 и 10 запрета поступают на входы соответствующих интеграторов 11 и 12, напряжения на выходах которых пропорциональны вероятности появления импульсов на выходах дополнительных компараторов 7 и 8. С выхода дополнительного блока 13 вычитания снимается сигнал, пропорциональный разности этих напряжений, который используется для восстановления симметрии диапазона изменения значений разностного сигнала относительно середины динамического диапазона второго параллельного блока б компараторов. С этой цолью он подается на дополнительный вход блока 3 вычитания.

При симметрии диапазона изменения зна. чений разностного сигнала относительно середины динамического диапазона второго параллельного блока 6 компараторов, в слу- чае их совпаде ия, импульсы на вьгходах дополнительных компараторов 7 и 8 отсутствуют. При недопустимом превьпиенити диапазоном изменения значений разностного сигнала - динамического диапазона второго параллельного блока 6 компараторов, на выходах обоих дополнительных кокшараторов 7 к 8, с одинаковой вероятностъю появляются импульсы. Эти импульсы с выходов одного из дополнительных компараторов 7 или 8, напркМф, компаратора 8, через элемент запрета, например , 1О подаются на интегратор 14, напряжение на выходе которого аропорционально, вероятности появ« лен1й1 импульсов на его входе. Это напряжение используется для подстройки динАмйческого диапазона второго параллельного блока G компараторов в соответствии с диапазоном изменения значений разностного сигнала на его входе. При ограниче1гаи входного сигнала в первом параллелыюм блоке 1 компаратс ов происходит ограничение разностного сигнала во втором параллельном блоке 6 компараторов и появление импульсов на выходах допсэтнктельных компараторов 7 и 8. Это может npimecTH к нежелательному изменению сигналов управления на допопнительных входах блока 3 вычитантга и второго

параллельного блока 6 компараторов..

С целью исключения этого явления в пер-

вый параллельный блок 1 компараторов

введены два дополнительных компара-

тора 15 и 16 (аналогично двум дополнительным компараторам 7 и 8 во втором параллельном блоке 6 компараторов). При ограничении входного аналогового сигнала на их выходах возникают импульсы, которые объединяются элементом ИЛИ 17 и подаются на управляющие входы обоих элементов 9 и Ю запрета. Таким образом, в этом случае импульсы с выходов дополнительных компараторов

7 и 8 не проходят на входы интеграторов 11, 12 и 14, и ложной коррекции погрешности преобразования не происходит.

Для устойчивости работы цепи компен55сашш погрешности преобразования необходимо KNieTb постоянную времени интег ратора 14, большую постоянной временг интеграторов 11 и 12. Тогда, при воэ- .

Авторы

Даты

1981-08-15—Публикация

1979-11-22—Подача