;;

СХ )

О 00

Изобретение относится к вычислительной технике и может быть использовано в системах связи с импульсно- кодовой модуляцией.

Целью изобретения является повышение точности преобразования.

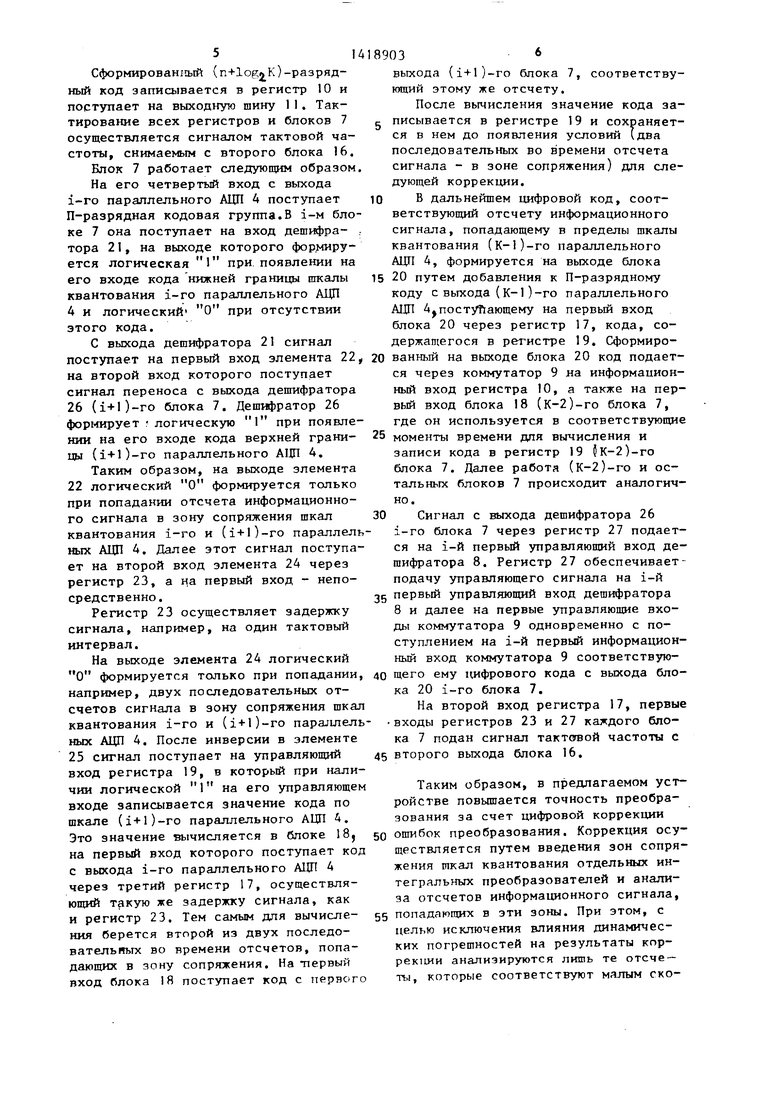

На фиг. I приведена функциональная схема преобразователя; на фиг.2 функциональная схема блока коррекции.

Аналого-цифровой преобразователь (фиг. 1) содержит входную шину 1, согласующий усилитель 2, К усилите

лей-ограничителей 3, К параллельных аналого-цифровых преобразователей (АЦП) 4, источник 5 напряжения ограничения, источник 6 опорного напряжения смещения, К-1 блоков 7 коррекции отибок, дешифратор 8, коммутатор 9, регистр 10, выходную шину 11, дешифратор 12, регистр 13 сдвига, регистр 14 сдвига, шину 15 сигнала тактовой частоты, блок 16 задержек .

Каждый из К-1 блоков 7 (фиг. 2) содержит регистр 17 сдвига, блок 18 вычитания, регистр 19, блок 20 сложения, дешифратор 21, элемент ИЛИ 22, регистр 23 сдвига, элемент ИЛИ 24, элемент НЕ 25, дешифратор 26, регист 27 сдвига.

Устройство работает следующим образом.

На входную шину 1 и далее на со- гласующий усилитель 2 поступает широкополосный информационный сигнал связи, например телевизионный сигнал В согласующем усилителе телевизионны сигнал усиливается, ограничивается п спектру, снова усиливается и привязывается к определенному уровню (например, по вершинам синхроимпульсов) Cииxpoи шyльcы частоты строк, необходимые для работы, могут быть пода- ны из вне, а могут быть выделены из телевизионного сигнала в одном из узлов согласующего усилителя 2, с выхода которого телевизионный сигнал поступает на объединенные первые входы К блоков усилителей-ограничителей 3, в которых осуществляется усиление сигнала, ограничение его с двух сторон и смещение. Усиление и смещение необходимы для согласования размаха преобразуемого сигнала с динамическим диапазоном каждого параллельного аналого-цифрового преобразователя (АЦП) 4. При этом диапазон изменения

10

5

0

5

0

5 о 5

0

5

преобразуемого сигнала разбивается на К равных участков по числу используемых параллельных АЦП 4. Напряжение ограничения вырабатывается источником 5. С выходов К усилителей-ограничителей 3 после усиления, деления и смещения и ограничения на первые входы соответствующих параллельных АЦП поступает 1/К части аналогового сигнала по размаху и смещению согласованные с динамическим диапазоном каждого параллельного АЦП 4.

Работой параллельных АЦП 4 управляет сигнал тактовой частоты. Выборка производится (стробируются компараторы) через определенный интервал времени после подачи переднего фронта тактового импульса. Этот интервал времени может отличаться для разных параллельных АЦП 4, что приводит к возникновению динамических погрешностей преобразования. Указанные отличия компенсируются блоком 16. Напряжение от источника 6 поступает параллельно на вторые входы параллельных АЦП 4, где используется для формирования диапазонов амплитудного квантования. На выходах каждого параллельного АЦП 4 формируется П-разрядный параллельный двоичный код.

Сопряжение шкал квантования параллельных АЦП 4 осуществляется сдвигом динамических диапазонов усилителей-ограничителей 3.

В устройстве не предъявляется жестких требований к точности сопряжения шкал квантования параллельных АЦП 4. При сопряжении необходимо обеспечить наложение граничных областей соседних шкал квантования на несколько (например, 3-5) шагов квантования. Величина зоны наложения должна быть достаточно большой, чтобы действие различных дестабилизирующих факторов (например, климатические условия) не приводило к появлению разрьшов в результирующей квантующей характеристике АЦП, связанных с пропаданием зоны наложения и расхождения щкал квантования. С другой стороны излишнее увеличение зоны наложения приведет к соответствующему уменьшению количества уровней амплитудного квантования в результирующей квантующей характеристике АЦП.

Зона наложения используется в устройстве для коррекции ошибок преобразования .

3,4

С выхода i-ro параллельного АЦП П-разрядные кодовые группы поступают на четвертые входы соответствующего блока 7, на первые входы которого поступает код с выхода (i-l)-ro блока 7. В i-M блоке 7 вычисляется и запоминается двоичная кодовая комбинация на выходе (i+l)-ro параллельного АЦП 4, соответствующая положению на его шкале квантования нижней границы шкалы квантования i-ro параллельного АЦП 4 (т.е. определяется нижняя граница зоны сопряжения шкал квантования i и (i+l)-ro параллельных АЦП 4). Эта операция осуществляется без перерыва обработки информационного сигнала в моменты времени, соответствующие незначительной скорости изменения его значений, например, при попадании не менее двух последовательных отсчетов информационного сигнала в зону сопряжения. Дпя этого используется сигнал, поступающий на второй вход i-ro блока 7 с третьего выхода (i+l)-ro блока 7. Логическая 1 соответствует появлению кода верхней границы шкалы квантования (например, при п 8:11111111) (i+l)-ro параллельного АЦП 4, логический О - отсутствию такового кода. Тем самым исключается влияние динамической составляющей погрешности преобразования на точность коррекции.

Указанная выше двоичная кодовая комбинация суммируется затем с каждой кодовой комбинацией, поступающей с выхода i-ro параллельного АЦП 4. Результат поступает на первый вход (i- -1)-го блока 7 и на соответствующий информационный вход коммутатора 9. На втором выходе i-ro блока 7 формируется сигнал логической I в случае появления на выходе соответствующего параллельного А1Ш 4 кода верхней границы его шкалы квантования и логического О при отсутствии указанного вьш1е кода. Сигналы с вторых выходов всех блоков 7 поступают на первые управляющие входы дешифратора 8.

С выхода К-го параллельного АЦП 4 П-разрядные кодовые группы поступают через регистр 13 на первый вход (К-1)-го блока 7 и на второй управляющий вход коммутатора 9. В (К-1)-м блоке 7 кодовые группы используются для вычисления и запоминания кодовой комбинации на выходе К-го параллель3

ного АЦП 4, соответствующей положению на его шкале квантования нижней границы шкалы квантования (К-1)-го

параллельного АЦП 4.

С выхода К-го параллельного АЦП 4 П-разрядные кодовые группы поступают на дешифратор 12, который формирует логическую 1 при появлении кода

верхней границы шкалы квантования

К-го параллельного АЦП 4, логический

О - при отсутствии такого кода.

С выхода дешифратора 12 сигнал

поступает на второй вход (К-1)-го

блока 7, где используется для опре-, деления момента попадания значений информационного сигнала в зону сопряжения щкал квантования К-го и (К-1)-го параллельных АЦП 4. Этот же сигнал

через регистр 14 поступает на второй управляющий вход дешифратора 8. Этот сигнал аналогичен по назначению сигналам, поступающим на первые управляющие входы дешифратора 8. Регистры 13

и 14 предназначены для задержки сигнала, например, на один тактовый интервал, аналогичный задержке сигнала в каждом блоке 7, связанной с анализом в блоках 7 двух последовательных

во времени отсчетов сигнала.

Дешифратор 8 по существу преобразует К-разрядный входной унитарный код в двоичный код управления коммутатором 9. Унитарный код характеризует

положение отсчетов информационного сигнала относительно шкал квантования параллельных АЦП 4. В зависимости от этого коммутатор 9 обеспечивает подключение кодовых комбинаций на вход

регистра 10 с выхода блока 7, ветствующего тому параллельному АЦП 4, в диапазоне амплитудного квантования которого попал информационный сигнал.

Разрядность кода на первых информационных входах коммутатора 9 является функцией i, например, при на соответствующий информационный вход коммутатора 9 поступает П-разрядный код с выхода регистра 13, а при на соответствующий вход коммутатора 9 поступает (n+log K)-pa3- рядный код с первого выхода первого блока 7. Все информацрюнные входы

коммутатора 9 рассматриваются как (п+1ор,)-разрядные. Недостающие старшие разряды для (2-К)-информационных входов полагаются равными нулк .

514

Сформированный (n+logj, К)-разрядный код записывается в регистр 10 и поступает на выходную шину 11. Тактирование всех регистров и блоков 7 осуществляется сигналом тактовой частоты, снимаемым с второго блока 16.

Блок 7 работает следующим образом.

На его четвертый вход с выхода i-ro параллельного АЦП 4 поступает П-разрядная кодовая группа.В i-м блоке 7 она поступает на вход дешифра- ; тора 21, на выходе которого формируется логическая 1 при появлении на его входе кода нижней границы шкалы квантования i-ro параллельного АЦП 4 и логический О при отсутствии этого кода.

С выхода дешифратора 21 сигнал поступает на первый вход элемента 22 на второй вход которого поступает сигнал переноса с выхода дешифратора 26 (i+l)-ro блока 7. Дешифратор 26 формирует г логическую 1 при появлении на его входе кода верхней грани- щи {i+l)-ro параллельного АЦП А.

Таким образом, на выходе элемента 22 логический О формируется только при попадании отсчета информационного сигнала в зону сопряжения шкал квантования i-ro и (i+l)-ro параллельных АЦП 4. Далее этот сигнал поступает на второй вход элемента 24 через регистр 23, а на первый вход - непосредственно.

Регистр 23 осуществляет задержку сигнала, например, на один тактовый интервал.

На выходе элемента 24 логический О формируется только при попадании, например, двух последовательных отсчетов сигнала в зону сопряжения шкал квантования i-ro и (i + O-ro параллельных АЦП 4. После инверсии в элементе 25 сигнал поступает на управляющий вход регистра 19, в который при наличии логической 1 на его управляющем входе записывается значение кода по шкале (i+l)-ro параллельного АЦП 4. Это значение вычисляется в блоке I8j на первый вход которого поступает код с выхода i-ro параллельного АЦП 4 через третий регистр 17, осуществляющий же задержку сигнала, как и регистр 23. Тем самым для вычисления берется второй из двух последовательных во времени отсчетов, попадающих в зону сопряжения. На -первый вход блока 1Я поступает код с первого

189036

выхода (i-bl)-ro блока 7, соответствующий этому же отсчету.

После вычисления значение кода за- 5 писывается в регистре 19 и сохраняется в нем до появления условий (два последовательных во времени отсчета сигнала - в зоне сопряжения) для следующей коррекции.

10 В дальнейшем цифровой код, соответствующий отсчету информационного сигнала, попадающему в пределы шкалы квантования (К-1)-го параллельного АЦП 4, формируется на выходе блока

15 20 путем добавления к П-разрядному коду с выхода (К-1)-го параллельного АЦП 4 постуГ1ающему на первый вход блока 20 через регистр 17, кода, содержащегося в регистре 19. Сформиро20 ванный на выходе блока 20 код подается через коммутатор 9 на информационный вход регистра 10, а также на первый вход блока 18 (К-2)-го блока 7, где он используется в соответствующее

25

моменты времени дпя вычисления и

записи кода в регистр 19 5к-2)-го блока 7. Далее работа (К-2)-го и остальных блоков 7 происходит аналогично.

30 Сигнал с выхода дешифратора 26

i-ro блока 7 через регистр 27 подается на i-й первый управляющий вход дешифратора 8. Регистр 27 обеспечивает- подачу управляющего сигнала на i-й

35 первый управляющий вход дешифратора 8 и далее на первые управляющие входы коммутатора 9 одновременно с поступлением на i-й первый информационный вход коммутатора 9 соответствую40 щего ему цифрового кода с выхода блока 20 i-ro блока 7.

На второй вход регистра 17, первые входы регистров 23 и 27 каждого блока 7 подан сигнал тактсгвой частоты с

45 второго выхода блока 16.

Таким образом, в предлагаемом устройстве повышается точность преобразования за счет цифровой коррекции

50 ошибок преобразования. Коррекция осуществляется путем введения зон сопряжения шкал квантования отдельных интегральных преобразователей и анализа отсчетов информационного сигнала,

55 попадающих в эти зоны. При этом, с целью исключения влияния динамических погрешностей на результаты коррекции анализируются лишь те отсчеты, которые соответствуют малым скоростям изменения значений информационного сигнала.

Формула изобретения

рекции ошибок соединены с соответствующими выходами каждого i-ro параллельного аналого-цифрового преобразователя, выходы которого соединены соответственно с вторыми входами первого регистра сдвига и входами второго дешифратора, причем выход второго регистра сдвига соединен с 10 вторым управляющим входом второго дешифратора, выходы которого соединены с соответствующими управляющими входами коммутатора.

2. Преобразователь по п. 1, о т1. Аналого-цифровой преобразователь, содержащей согласующий усипи- тель, вход которого является входной щиной, а выход соединен с первыми входами К усилителей-ограничителей, вторые входы которых объединены и соединены с выходом источника напряжения ограничения, а выходы К усилителей-ограничителей соединены соответ-,5 личающийся тем, что каждый ственно с первыми входами К парал- блок коррекции ошибок выполнен на лельных аналого-цифровых преобразова- двух дешифраторах, трех регистрах телей, вторые выходы которых объеди- сдвига, регистре, блоке вычитания, нены и соединены с выходом источника блоке сложения, двух элементах ИЛИ и опорного напряжения смещения, а тре- 2о элементе НЕ, выход которого соединен тьи входы соединены с соответствующими первыми выходами блока задержек, вход которого является шиной сигнала тактовой частоты, а второй выход

с управляющим входом регистра, инфор мационные входы которого соединены соответственно с выходами блока вычитания, первые входы которого являютрекции ошибок соединены с соответствующими выходами каждого i-ro параллельного аналого-цифрового преобразователя, выходы которого соединены соответственно с вторыми входами первого регистра сдвига и входами второго дешифратора, причем выход второго регистра сдвига соединен с вторым управляющим входом второго дешифратора, выходы которого соединены с соответствующими управляющими входами коммутатора.

2. Преобразователь по п. 1, о тличающийся тем, что каждый блок коррекции ошибок выполнен на двух дешифраторах, трех регистрах сдвига, регистре, блоке вычитания, блоке сложения, двух элементах ИЛИ и элементе НЕ, выход которого соединен

личающийся тем, что каждый блок коррекции ошибок выполнен на двух дешифраторах, трех регистрах сдвига, регистре, блоке вычитания, блоке сложения, двух элементах ИЛИ и элементе НЕ, выход которого соединен

с управляющим входом регистра, информационные входы которого соединены соответственно с выходами блока вычитания, первые входы которого являют

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цифровой передачи и приема телевизионного сигнала | 1985 |

|

SU1309327A1 |

| Устройство цифровой передачи и приема телевизионного сигнала | 1981 |

|

SU1001501A1 |

| Устройство кодирования телевизионного сигнала | 1986 |

|

SU1385330A1 |

| Многоканальное устройство приема сложных сигналов | 1989 |

|

SU1786664A1 |

| Система цифровой передачи и приема сигналов цветного телевидения | 1978 |

|

SU764150A1 |

| Система передачи и приема цифровой информации | 1988 |

|

SU1559361A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Цифровой коррелятор | 1976 |

|

SU610117A1 |

| Устройство передачи телевизионного сигнала | 1988 |

|

SU1570028A1 |

| Устройство п-разрядного аналого-цифрового преобразования | 1987 |

|

SU1674367A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах связи с импуль- сно-кодовой модуляцией. Изобретение позволяет повысить точность преобразования. Это достигается тем, что в аналого-цифровой преобразователь, содержащий согласующий усилитель 2, К усилителей-ограничителей 3, источник 5 напряжения ограничения, источник 6 опорного напряжения смещения, К параллельных аналого-цифровых преобразователей 4, регистр 10, блок 16 задержек, введены (К-1) блоков 7 коррекции ошибок, регистры 13 и 14 сдвига, дешифраторы 8 и 12, коммутатор 9. 1 з.п. ф-лы, 2 ил.

соединен с управляющим входом регист- 25 ся первмми входами блока коррекции

ра, выход которого является выходной щиной, отличающийся тем, что, с целью повьщ1ения точности преобразования, в него введены К-1 блоков коррекции ощибок, два регистра сдвига, два дешифратора и коммутатор, выход которого соединен с информационным входом регистра, первые информационные входы коммутатора соединены с соответствующими первыми выхода- „ гистра сдвига и первые входы второго ми блоков коррекции ошибок, второй и третьего регистров сдвига, второй информационный вход коммутатора объединен с первым входом (К-1)-го блока коррекции ошибок и соединен с выходом первого регистра сдвига, вторые выходы блоков коррекции ошибок соедивход последнего из которых соединен с выходом первого дешифратора и явля ется третьим выходом блока коррекци 40 ошибок, кроме первого блока коррекции ошибок, выход третьего регистра

нены с соответствующими первыми уп- сдвига является вторым выходом блока равляющими входами первого дешифрато- коррекции ошибок, второй вход второго ра, первый и третий выходы (1+1)-го регистра сдвига объединен с первым

блока коррекции ошибок, где ,2,... входом первого элемента ИЛИ и соеди- К-2, соединены соответственно с пер- нен с выходом второго элемента ИЛИ, вым и вторым входами i-ro блока кор- выход второго регистра сдвига соеди- рекции ошибок, второй вход (К-1)-го нен с вторым входом первого элемента блока коррекции ошибок объединен с ИЛИ, выход которого соединен с входом

первым входом второго регистра сдви-gg элемента НЕ, причем первый вход вто- га и соединен с выходом второго де- рого элемента ИЛИ соединен с выходом шифратора, третьи входы блоков кор- второго дешифратора, второй вход яв- рекции ошибок объединены с вторым ляется вторым входом блока коррекции входом второго и первым входом перво- ошибок, первым выходом которого явго регистров сдвига и соединены сgg ляется выход блока сложения, второй вторым выходом блока задержек, чет- вход которого соединен с выходом ре- вертые входы каждого i-ro блока кор- гистра.

ошибок, второй вход блока вычитания объединен с первым входом блока сложения и соединен с выходом первого регистра сдвига, первый вход которо- го объединен с входами первого и второго дешифраторов и является четвертым входом блока коррекции ошибок, третьим входом которого являются объединенные второй вход первого регистра сдвига и первые входы второго и третьего регистров сдвига, второй

вход последнего из которых соединен с выходом первого дешифратора и является третьим выходом блока коррекции ошибок, кроме первого блока коррекции ошибок, выход третьего регистра

| СТЕНД ДЛЯ ИСПЫТАНИЯ ТРУБ ВНУТРЕННИМ ДАВЛЕНИЕМ И НА ИЗГИБ И ГИДРАВЛИЧЕСКАЯ СИСТЕМА СТЕНДА | 2002 |

|

RU2222800C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Гозбенко В.П | |||

| ПРИБОР ДЛЯ ЦЕНТРИРОВАНИЯ | 1920 |

|

SU1107A1 |

| - Техника кино и телевид ения, 1984, № 12, с | |||

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-06—Подача