изобретение относвггся к аналоговой вычислительной технике.

Известно yctpoftcTBO, которое содержит широтно-импульсньгй модулятор, 1генератор пилообразного напряжения, кондекь 5 саторы, переключатели, компаратор, схему совпадения 13.

Недостатком этого устройства является низкая точность измерения, котсрая ограничена конечной чувствительностью Ю амплитудного компаратора и погрешностью, хранения информации на запоминающих кон Менсаторах,

Наиболее близким к предлагаемому устройству для измерения 14 я зводной яв- 15 ляется устройство, содержащее широтноимпульсный модулятор, подключенный к входу триггера и к первым входам перво-; го и второго элементов И, i Hepayop опоси ной частоты, связанный через элементы И 20 со счетными входами первого и BTcqjoro счетчиков, блок сравнения кодов и формирователь 1 2 .

Недостаток прототипа - конструктивная сложность, обусловленная использование 25 ем блока сравнения кодов и авухсчетчиков.

Цель изобретения-упрощение устройства.

Цель достигается тем, что дифференцирующее устройство, содержащее широтно-импульсный модулятор, вход которого является входом устройства, а выход соединен со счетным входюм тригг а и с первыми входами первовго и второго элементов И, вторые входы которых подключены к соответствующим выходам триггера, и формирователь импульсов, блок памяти и два элемента ЗАПРЕТ, вь ходы которых являются выходами устрой- ства, при этом выход первого,элемента jl: соединен с информационным входом блока

-,,. ЛЛ

памяти, выход второго элемента И сое- динен с информационным вхоД0м перво го элемента ЗАПРЕТ.управляющим входом Ъторого элемента ЗАПРЕТ и через формирователь импульсов связан с управляющим входом блока памяти,выход крто- рого соединен с управляющим входом первого элемента ЗАПРЕТ и с информационным входом второго элемента ЗАПРЕТ..

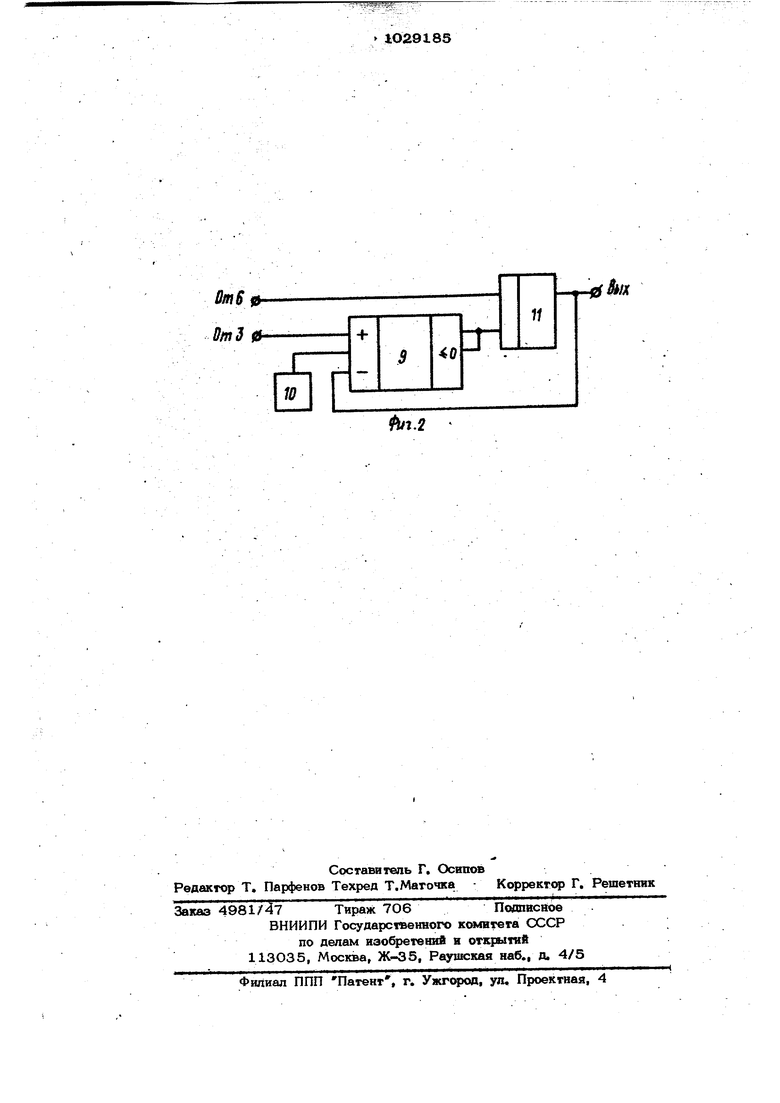

На фиг. 1 1фиведена функщкжальная схема устройства, на фиг. 2 - возможное 50 выполнение 6j{bKa памяти.

Устройство содержит шщютно импульсп ный модулятор 1, триггер 2, элементы И 3 и 4, блок памяти 5, формфбватепь импульсов 6, элементы ЗАПРЕТ 7 HjB. 55

Блок памяти 5 содержит реверсивный счетчик 9, генерат(Ч) 10 и RS-диггер 13 5. которого является у1фавляюпшм

входом блока, суммщ ующий вход реверсивнохх) счетчика 9 служит информацион ным Ексдом блока.

Устройство работает следующим образом.

В исходном положении триггер 2 и SJJOK памяти 5 установлень в нулевое, состояние (входы установки нуля не показаны). Входной аналоговый сигнал подается на вход щиротно-импульсного мо.дулятсра 1, генерирующего импульсы прямоугольной формы, изменения длительности которых соответствуют изменениям амплитуды входного сигнала. Г

Нулевое состояние триггера 2 paj eшает прохождение через элемент 3 нечетных Щ1фотно-модулированных импульсов на инфс мационный вход блока памяти 5, в котором запоминается их длительность. Задним фронтом щиротно-модул ованного импульса триггер 2 перебрасывается в единичное состояние, поэтому четные импульсы Проходят через элемент И 4.

Форм фователь 6 вырабатывает коротк импульс, по переднему фронту четных импульсов. По нему происходит считывание информации с блока памяти 5.

Импульс с блока памяти 5 и следующий ЩЁфотно-модушфОВанный импульс одновременно поступают на входы элементов ЗАПРЁТ 7 и 8. При этом, если длител ность второго щиротно-модулк5 ованнаго импулаьса больще длительности импульса, считанного с ока памяти 5, на вьосОДе элемента ЗАПРЕТ 7 появляется импульс, свидетельствующий о положительном знаке производной. Длительность выходного импульса пропорциональна величшю первой Щ)оязводной входного .

Если длительность второго шфотномодул фованного импульса меныие длительности импульса с блока памяти 5, то на выходе элемента ЗАПРЕТ 8 появляется импульс, свидетельствующий об отрицательном знаке хфоизводной. Его длительность также пр(Х10рциовальн1Э величине щ)оваводной входного сигнала.

При раавастве длительностей первого и второго Ш1фотн -модул1фованных импуль сов импульсы на выходах устройства отсутствуют что соответствует нулевому значению производной входного аналогового сигнала.

Угфощение устройства и возможность получение знака и величины 1фоиаводной в аналоговой (щ|фотно-импупьсной форме) оЩ)ёи&пяюг тёзшико-экотомический эффек ОТ использования изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференцирующее устройство | 1986 |

|

SU1367022A2 |

| Датчик разности фаз | 1980 |

|

SU962817A1 |

| Устройство для управления и защиты преобразователя | 1985 |

|

SU1336171A1 |

| Устройство для формирования символьных изображений на экране электронно-лучевой трубки | 1981 |

|

SU1010647A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1302255A1 |

| Широтно-импульсный модулятор | 1979 |

|

SU834884A1 |

| Устройство регулирования скорости | 1984 |

|

SU1210140A1 |

| Стабилизирующий конвертор | 1980 |

|

SU902010A1 |

| Устройство для управления и защиты преобразователя | 1986 |

|

SU1403281A2 |

| Стабилизированный преобразователь постоянного напряжения | 1981 |

|

SU995227A1 |

ДИФФЕРЕШИРУЮЩЕЕ УСТРОЙСТЕЮ, cpaqpKamiee широтнс -импульоный модупятф вход котср яю явияетсй входом устройогАа, а выход соединен со счетным входом tpHrr i н с (и входами первого и второго эле.ментов И Вторые входы хоторьпс подключены к cooiv ветствукяшш выходам тригг а, н формирователь нмпульсов, о т л н ч а ю ш е вся тем, что, с целью утфошеаия, устройство содержит блок памяти а два элемента ЗАПРЕТ выходы которых яваяются вь{- ходами при этом выход элемента И соедиие н с вяфсрмашюнным входом памяти, выход Btoporo мента И ооедивеи с ивфомацаовтлМ входом первого элемеЕГга ЗАПРЁТ« увравлт пщм входом элемеШ« 3iMIPET и ч еэ ф фмя| ователь импульсов свивав с ухфавляюшикг входом блока памяти выход которого соепшюн с управляющим входом элемента ЗАПРЕТ и с инфС Мацнсяным входом В1гор яч элемеЕгга ЗАПРЕТ.

Авторы

Даты

1983-07-15—Публикация

1982-01-04—Подача