Изобретение относится к электротехнике и может быть использовано в качестве источника вторичного электропитания различной радиоэлектронной аппаратуры.

Целью изобретения является повышение качества процесса регулирования с одновременным повышением надежности и снижением массы и объема.

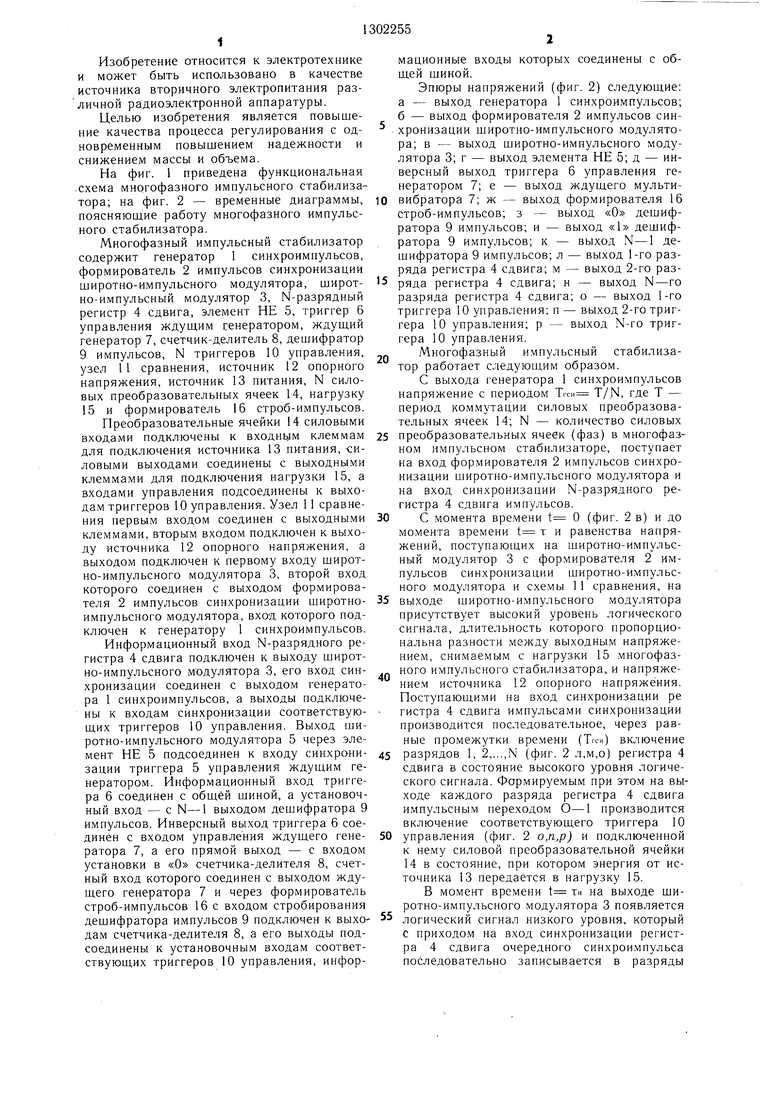

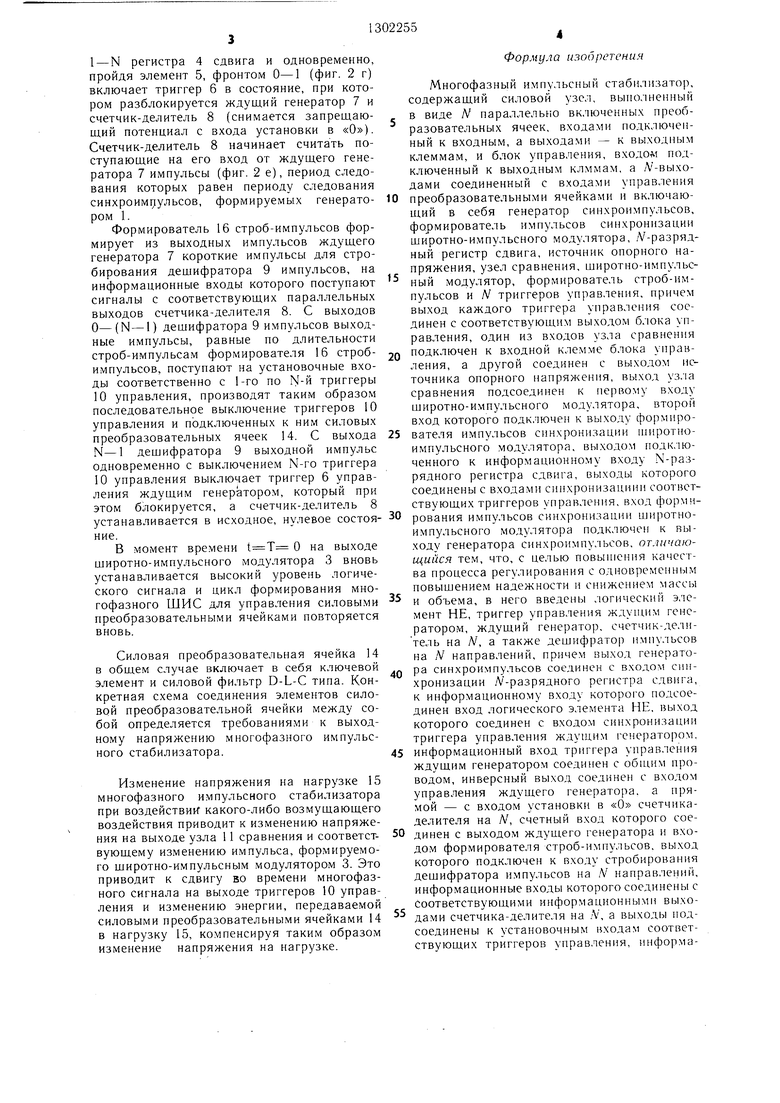

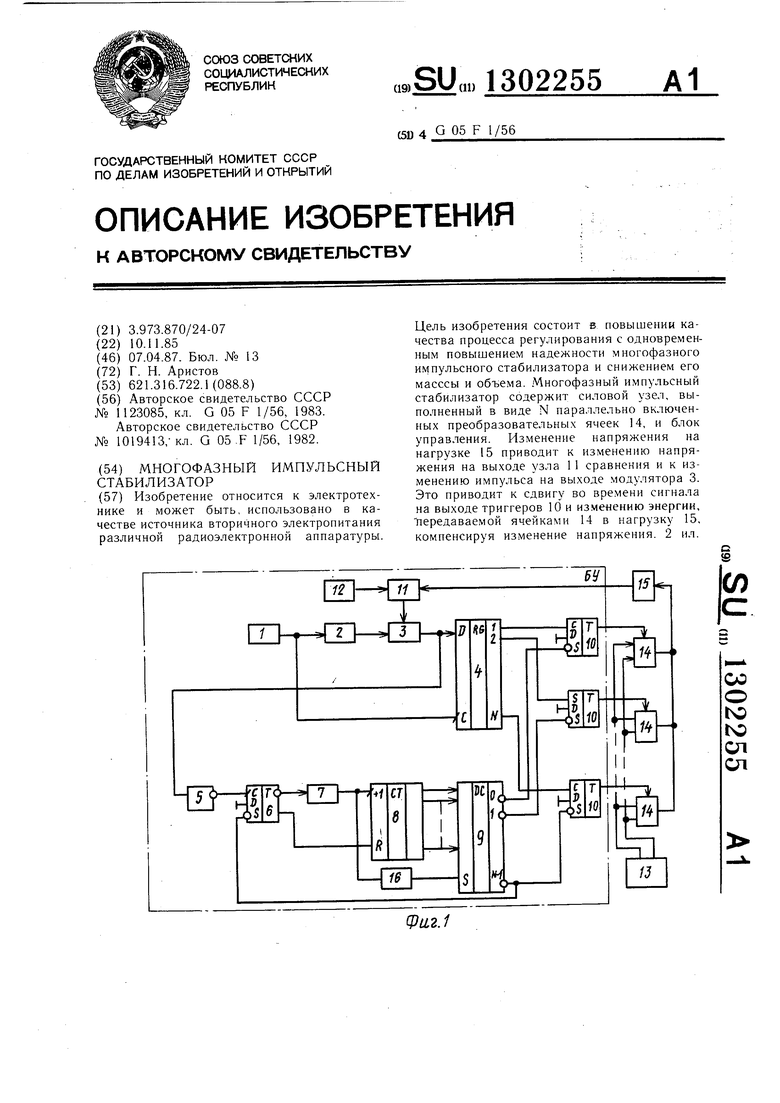

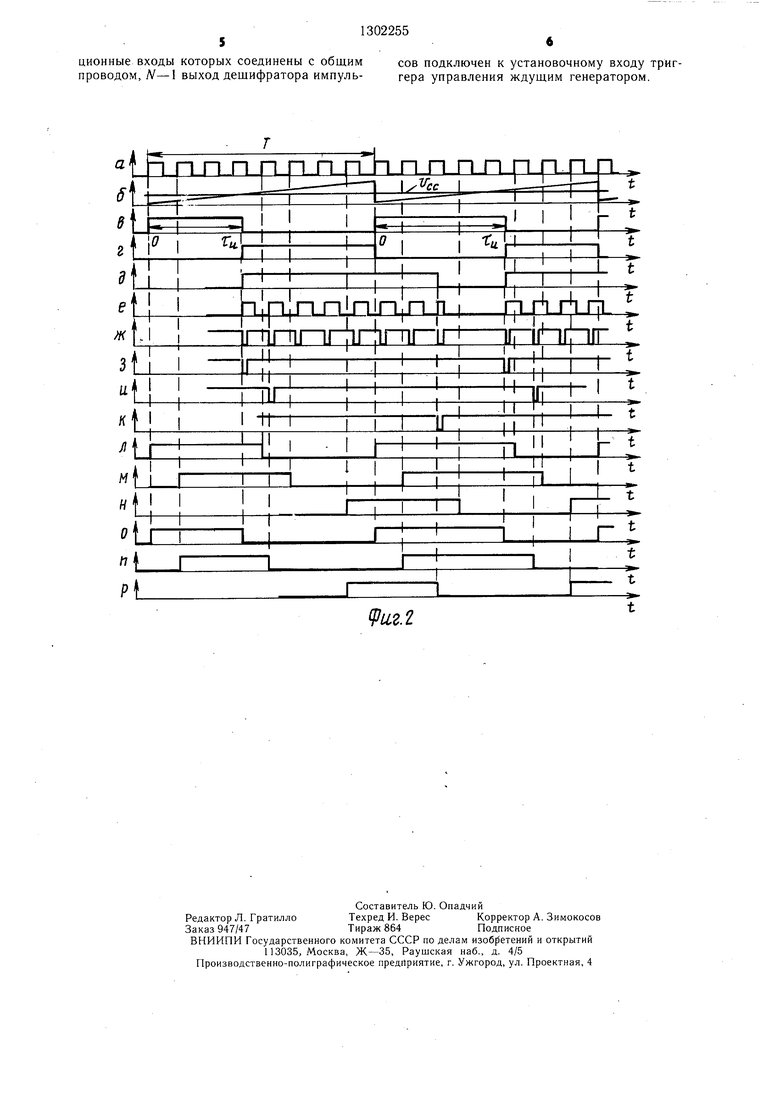

На фиг. 1 приведена функциональная .схема многофазного импульсного стабилизатора; на фиг. 2 - временные диаграммы, поясняющие работу многофазного импульсного стабилизатора.

Многофазный импульсный стабилизатор содержит генератор 1 синхроимпульсов, формирователь 2 импульсов синхронизации широтно-импульсного модулятора, широт- но-импульсный модулятор 3, N-разрядный регистр 4 сдвига, элемент НЕ 5, триггер 6 управления ждущим генератором, ждущий генератор 7, счетчик-делитель 8, дешифратор 9 импульсов, N триггеров 10 управления, узел 11 сравнения, источник 12 опорного напряжения, источник 13 питания, N силовых преобразовательных ячеек 14, нагрузку 15 и формирователь 16 строб-импульсов.

Преобразовательные ячейки 14 силовыми входами подключены к входнь;м клеммам для подключения источника 13 питания,-силовыми выходами соединены с выходными клеммами для подключения нагрузки 15, а входами управления подсоединены к выходам триггеров 10 управления. Узел 11 сравнения первым входом соединен с выходными клеммами, вторым входом подключен к выходу источника 12 опорного напряжения, а выходом подключен к первому входу широтно-импульсного модулятора 3, второй вход которого соединен с выходом формирователя 2 импульсов синхронизации широтно- импульсного модулятора, вход которого подключен к генератору 1 синхроимпульсов.

Информационный вход N-разрядного регистра 4 сдвига подключен к выходу широт- но-импульсного модулятора 3, его вход синхронизации соединен с выходом генератора 1 синхроимпульсов, а выходы подключены к входам синхронизации соответствующих триггеров 10 управления. Выход широтно-импульсного модулятора 5 через элемент НЕ 5 подсоединен к входу синхронизации триггера 5 управления ждущим генератором. Информационный вход триггера 6 соединен с общей шиной, а установочный вход - с N-1 выходом дещифратора 9 импульсов. Инверсный выход триггера 6 соединен с входом управления ждущего генератора 7, а его прямой выход - с входом установки в «О счетчика-делителя 8, счетный вход которого соединен с выходом ждущего генератора 7 и через формирователь строб-импульсов 16 с входом стробирования дещифратора импульсов 9 подключен к выхо дам счетчика-делителя 8, а его выходы подсоединены к установочным входам соответствующих триггеров 10 управления, инфори

мационные входы которых соединены с общей щиной.

Эпюры напряжений (фиг. 2) следующие: а - выход генератора 1 синхроимпульсов; б - выход формирователя 2 импульсов синхронизации широтно-импульсного модулятора; в - выход широтно-импульсного модулятора 3; г - выход элемента НЕ 5; Д - инверсный выход триггера 6 управления генератором 7; е - выход ждущего мульти10 вибратора 7; ж - выход формирователя 16 строб-импульсов; з - выход «О дешифратора 9 импульсов; и - выход «1 дешифратора 9 импульсов; к - выход N-1 дещифратора 9 импульсов; л - выход 1-го разряда регистра 4 сдвига; м - выход 2-го раз 5 ряда регистра 4 сдвига; н - выход N-го разряда регистра 4 сдвига; о - выход 1-го триггера 10 управления; п - выход 2-го триггера 10 управления; р - выход N-ro триггера 10 управления.

Многофазный импульсный стабилизатор работает следующим образом.

С выхода генератора 1 синхроимпульсов напряжение с периодом Тгси T/N, где Т - период ко.ммутации силовых преобразовательных ячеек 14; N - количество силовых

25 преобразовательных ячеек (фаз) в многофазном импульсном стабилизаторе, поступает на вход фор.мирователя 2 импульсов синхронизации широтно-импульсного модулятора и на вход синхронизации N-разрядного регистра 4 сдвига импульсов.

30 С момента времени t О (фиг. 2 в) и до момента времени t т и равенства напряжений, поступаюил.их на широтно-импульс- ный модулятор 3 с формирователя 2 импульсов синхронизации широтно-импульсного модулятора и схемы 11 сравнения, на

35 выходе широтно-импульсного модулятора присутствует высокий уровень логического сигнала, длительность которого пропорциональна разности между выходным напряжением, снимаемым с нагрузки 15 многофаз.J. ного импульсного стабилизатора, и напряжением источника 12 опорного напряжения. Поступающими на вход синхронизации ре гистра 4 сдвига импульсами синхронизации производится последовательное, через равные промежутки времени (Тгси) включение

45 разрядов 1, 2,...,N (фиг. 2 л,м,о) регистра 4 сдвига в состояние высокого уровня логического сигнала. Формируемым при этом на выходе каждого разряда регистра 4 сдвига импульсным переходом О-1 производится включение соответствующего триггера 10

50 управления (фиг. 2 о,п,р) и подключенной к нему силовой преобразовательной ячейки 14 в состояние, при котором энергия от источника 13 передается в нагрузку 15.

В момент времени t тн на выходе широтно-импульсного модулятора 3 появляется логический сигнал низкого уровня, который с приходом на вход синхронизации регистра 4 сдвига очередного синхроимпульса последовательно записывается в разряды

55

1 - N регистра 4 сдвига и одновременно, пройдя элемент 5, фронтом О-1 (фиг. 2 г) включает триггер 6 в состояние, при котором разблокируется ждущий генератор 7 и счетчик-делитель 8 (снимается запрещающий потенциал с входа установки в «О). Счетчик-делитель 8 начинает считать поступающие на его вход от ждущего генератора 7 импульсы (фиг. 2 е), период следования которых равен периоду следования синхроимг ульсов, формируемых генератором 1.

Формирователь 16 строб-импульсов формирует из выходных импульсов ждущего генератора 7 короткие импульсы для стро- бирования дещифратора 9 импульсов, на информационные входы которого поступают сигналы с соответствующих параллельных выходов счетчика-делителя 8. С выходов О-(N-1) дешифратора 9 импульсов выходные импульсы, равные по длительности строб-импульсам формирователя 16 строб- импульсов, поступают на установочные входы соответственно с 1-го по N-й триггеры 10 управления, производят таким образом последовательное выключение триггеров 10 управления и подключенных к ним силовых преобразовательных ячеек 14. С выхода N-1 дещифратора 9 выходной импульс одновременно с выключением N-ro триггера 10 управления выключает триггер 6 управления ждущим генератором, который при этом блокируется, а счетчик-делитель 8 устанавливается в исходное, нулевое состояние.

В момент времени О на выходе щиротно-импульсного модулятора 3 вновь устанавливается высокий уровень логического сигнала и цикл формирования многофазного ШИС для управления силовыми преобразовательными ячейками повторяется вновь.

Силовая преобразовательная ячейка 14 в общем случае включает в себя ключевой элемент и силовой фильтр D-L-C типа. Конкретная схема соединения элементов силовой преобразовательной ячейки между собой определяется требованиями к выходному напряжению многофазного импульсного стабилизатора.

Изменение напряжения на нагрузке 15 многофазного импульсного стабилизатора при воздействи какого-либо возмущающего воздействия приводит к изменению напряжения на выходе узла 11 сравнения и соответствующему изменению импульса, формируемого щиротно-импульсным модулятором 3. Это приводит к сдвигу во времени многофазного сигнала на выходе триггеров 10 управления и изменению энергии, передаваемой силовыми преобразовательными ячейками 14 в нагрузку 15, компенсируя таким образом изменение напряжения на нагрузке.

Формула изобретения

Многофазный импульсный стабилизатор, содержащий силовой узел, выполненный в виде N параллельно включенны.х преобразовательных ячеек, входами подключенный к входным, а выходами - к выходным клеммам, и блок управления, входом подключенный к выходным клммам, а /V-выхо- дами соединенный с входами управления

0 преобразовательными ячейками и включающий в себя генератор синхроимпульсов, формирователь импульсов синхронизации широтно-импульсного модулятора, /V-разряд- ный регистр сдвига, источник опорного напряжения, узел сравнения, щиротно-импульс ный модулятор, формирователь строб-импульсов и /V триггеров управления, причем выход каждого триггера управления соединен с соответствующим выходом блока управления, один из входов узла сравнения

Q подключен к входной клемме блока управления, а другой соединен с выходом источника опорного напряжения, выход уз. 1а сравнения подсоединен к первому входу щиротно-импульсного модулятора, второй вход которого подключен к выходу формиро5 вателя импульсов синхронизации щиротно- импульсного модулятора, выходом подключенного к информационному входу N-раз- рядного регистра сдвига, выходы которого соединены с входами синхронизациии соответствующих триггеров управления, вход форми0 рования импульсов синхронизации щиротно- импульсного модулятора подключен к выходу генератора синхроимпульсов, отличающийся тем, что, с целью повышения качества процесса регулирования с одновременным повыщением надежности и снижением массы

и объема, в него введены логический элемент НЕ, триггер управления ждущим генератором, ждущий генератор, счетчик-делитель на Л, а также дещифратор импульсов на N направлений, причем ЕВЫХОД генератоQ ра синхроимпульсов соединен с вxoдo синхронизации -разрядного регистра сдвига, к информационному входу которого подсоединен вход логического элемента НЕ, выход которого соединен с входом синхронизации триггера управления ждущим генератором.

5 информационный вход триггера управления ждущим генератором соединен с общим проводом, инверсный выход соединен с входом управления ждущего генератора, а прямой - с входом установки в «О счетчика- делителя на Л/, счетный вход которого сое0 динен с выходом ждущего генератора и входом формирователя строб-имнульсов, выход которого подключен к входу стробирования дещифратора импульсов на N направлений, информационные входы которого соединены с соответствующими информационными выхо дами счетчика-делителя на Л , а выходы подсоединены к установочным входам соответствующих триггеров управления, информационные входы которых соединены с общим проводом, yV-1 выход дешифратора импульfl t

сов подключен к установочному входу триггера управления ждущим генератором.

te.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок управления многофазным импульсным стабилизатором | 1985 |

|

SU1335956A1 |

| Многофазный импульсный стабилизатор напряжения | 1983 |

|

SU1156032A1 |

| Блок управления многофазным импульсным стабилизатором | 1983 |

|

SU1123085A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1019413A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1070528A1 |

| Многофазный импульсный стабилизатор | 1986 |

|

SU1449977A2 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265743A1 |

| Многофазный импульсный стабилизатор напряжения | 1987 |

|

SU1483438A1 |

| Многофазный импульсный стабилизатор | 1984 |

|

SU1196830A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265741A1 |

Изобретение относится к электротехнике и может быть, использовано в качестве источника вторичного электропитания различной радиоэлектронной апнаратуры. Цель изобретения состоит в повышении качества процесса регулирования с одновременным повышением надежности многофазного импульсного стабилизатора и снижением его масссы и объема. Многофазный импульсный стабилизатор содержит силовой узел, выполненный в виде N параллельно включенных преобразовательных ячеек 14, и блок управления. Изменение напряжения на нагрузке 15 приводит к изменению напряжения на выходе узла 1 1 сравнения и к изменению импульса на выходе модулятора 3. Это приводит к сдвигу во времени сигна,аа на выходе триггеров 10 и изменению энергии, передаваемой ячейками 14 в нагрузку 15, компенсируя изменение напряжения. 2 ил. СО со о N:) ГчЭ Са сд Фи,2.1

| Блок управления многофазным импульсным стабилизатором | 1983 |

|

SU1123085A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1019413A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-04-07—Публикация

1985-11-10—Подача