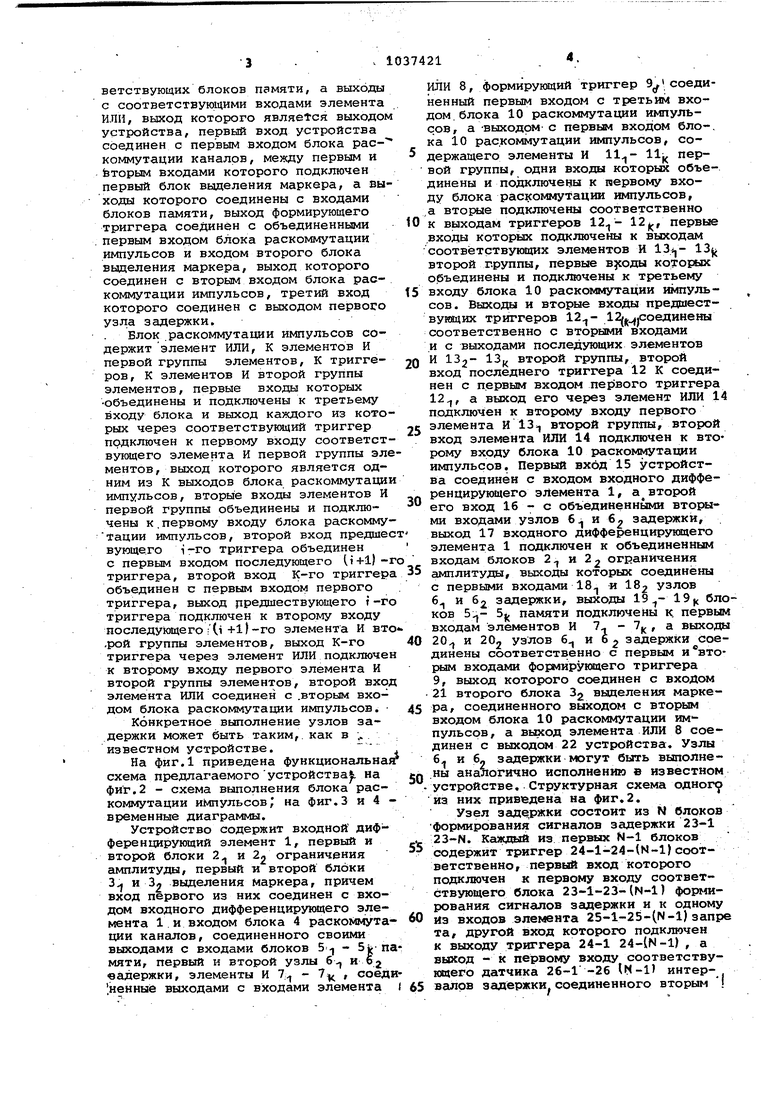

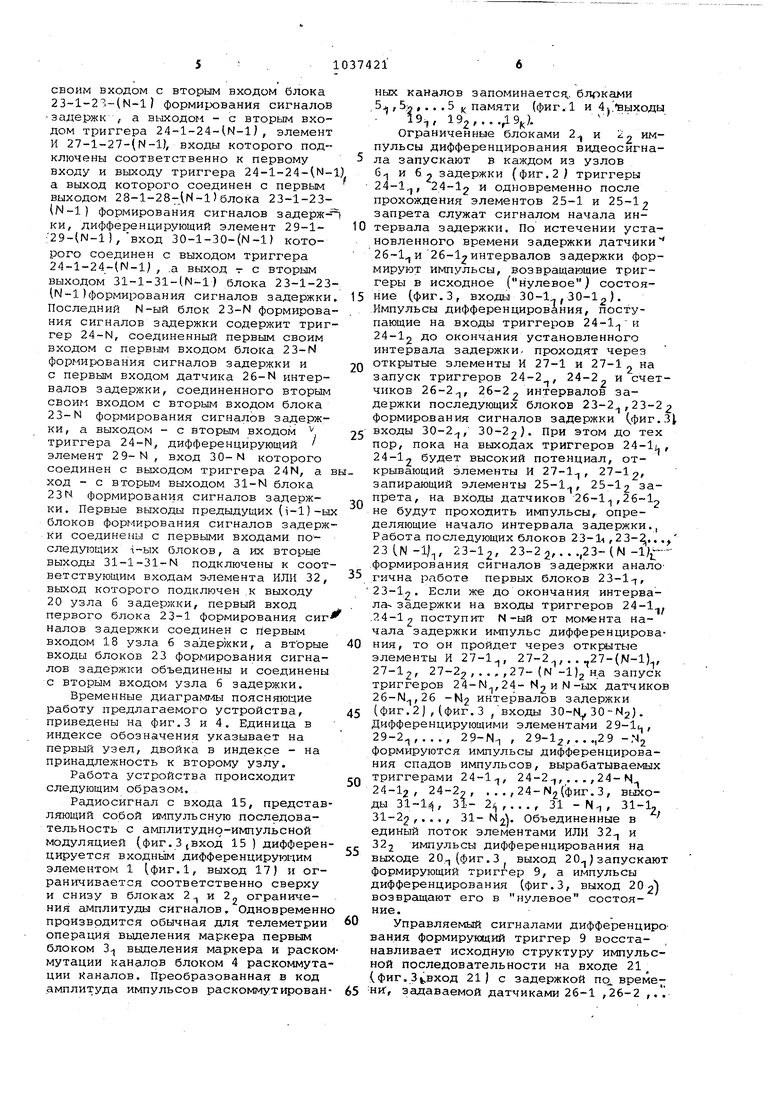

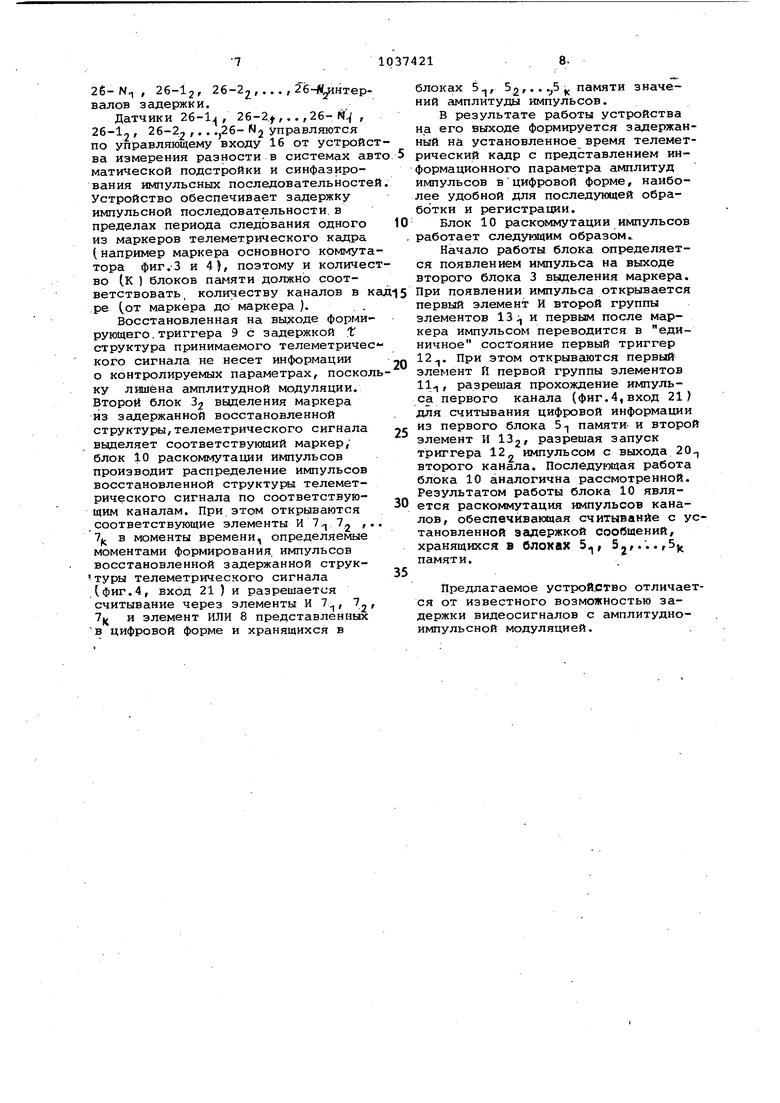

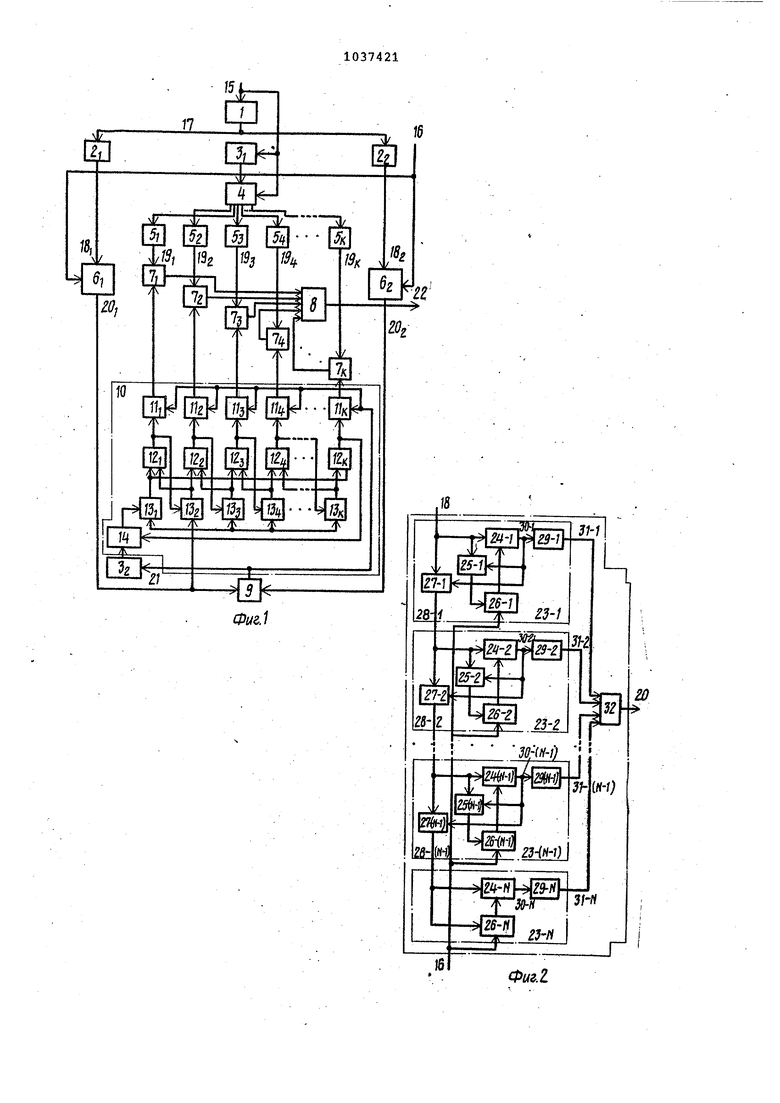

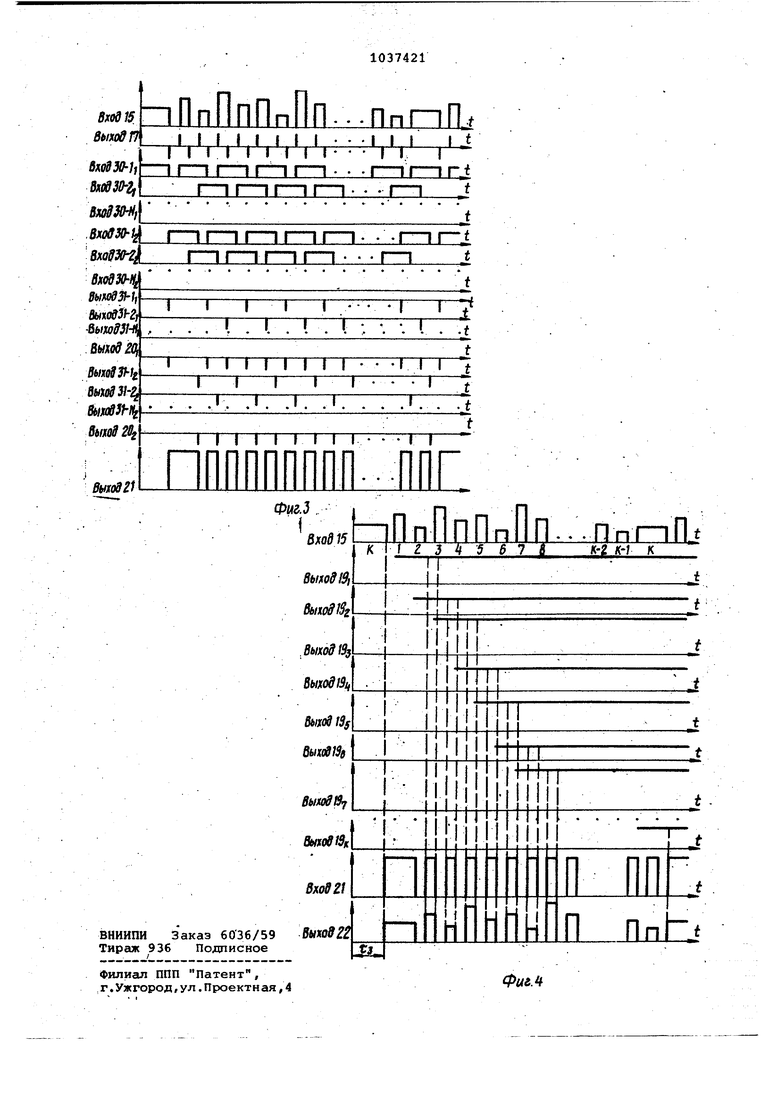

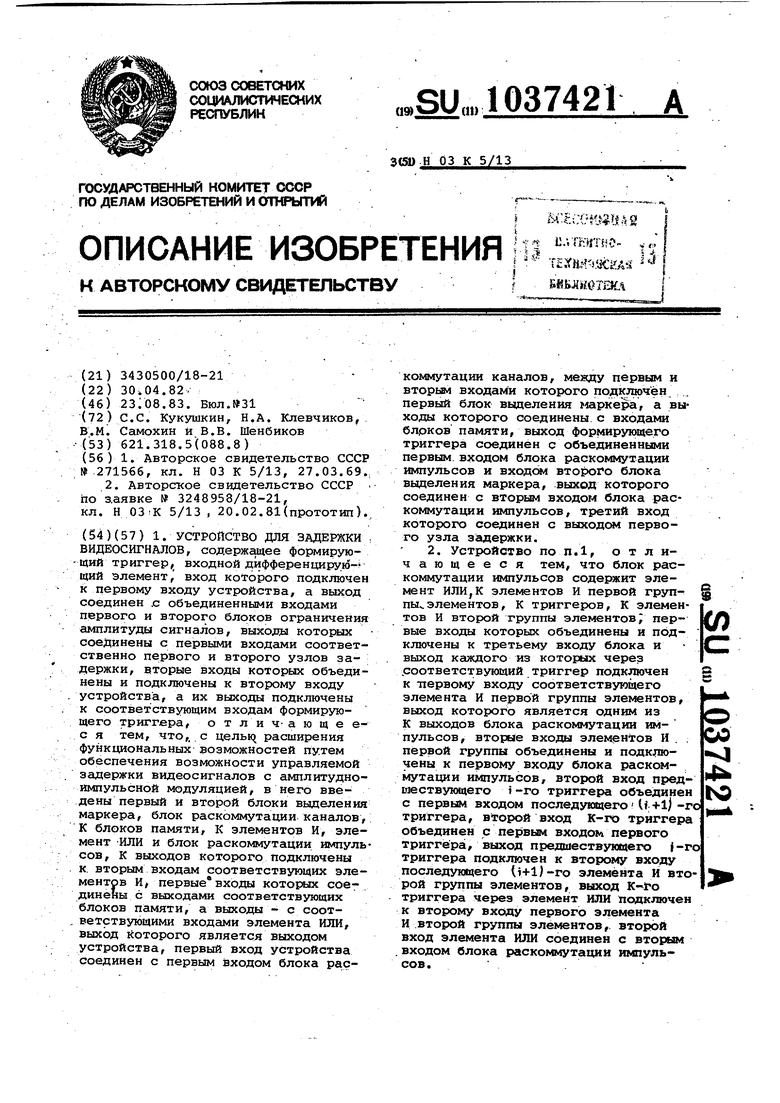

Изобретение относится к радиотехнике и предназначено для управляемой задержки видеосигналов в телеметрических vjHCTeMax с временным разделением каналов. Известно устройство, содержащее последовательно соединенные первый временной селектор, реверсный счетчик импульсов и дешифратор нуля, выход которого подключен к первому входу триггера, с входом первого временного селектора объединен вход последовательно соединенных дифференцирующей цепи и схемы задержки фронта импульса, выход которой подключен к второму входу триггера, первый выход которого является выходом устройства, а второй через второй временной селектор подключен к второму входу реверсивного счетчи ка импульсов, к объединенным вторым входам временных селекторов подключен выход генератора счетных импуль сов 1. Недостатками известного устройст являются низкое быстродействие, ограниченная точность задержки, невозможность задержки видеосигналов с амплитудно-импульсной модуляцией. Точность задержки в устройстве определяется частотой следования счетньк импульсов, которая, в свою очередь, ограничивается возможностя ми по быстродействию счета импульсов реверсивными счетчиками. Из условия обеспечения необходимой- точности задержки накладываются ограничения на частоту следования и дли тельность задерживаемых импульсов. Наиболее близким к предлагаемому nd технической реализации является устройство, содержащее формирующий триггер и первый узел задержки из К параллельных блоков формирования сигналов задержки, каждый из которы включает в себя триггер и дифференц рующий элемент, входной дифференцирующий элемент и аналогичный второй узел задержки, а в кавдый из узлов задержки введен блок ограничения амплитуды сигналов и элемент ИЛИ, при этом в каждом из узлов задержки в каждый из первых К-1 блоков форми рования сигналов задержки дополнительно введены элемент И, элемент ЗАПРЕТ, датчик интервалов задержки, а в К-ый блок формирования сигналов задержки каждого из.узлов задержки введен датчик интервалов задержки, причем вход триггера подключен к вх ду блока формирования сигналов заде ки, а выход объединенного по входу .первым входом триггера элемента-И подключен к первому выходу блока фо мирования сигналов задержки, между первым входом и вьрсодом триггера подключен элемент ЗАПРЕТ, выход KOT рого через датчик интервалов задерж ки подключен к второму входу триггера/ выход которого подключен к объединенным второму входу элемента И и входу Дифференцирующего элемента, выход которого подключен к второму выходу блока формирования сигналов задержки, в К-ом блоке формирования сигналов- задержки между первым и вторым входами подключен датчик интервалов задержки, выход триггера подключен к входу дифференцирующего элемента, выходы дифференцирующих элементов блоков формирования сигналов задержки подключены к соответствующим входам элемента ИЛИ, выход которого подключен к выходу узла задержки, а вход блока охраничения амплитуды сигн.алов, подключенного к входу первого блока формирования сигналов задержки, соединен с входом узла задержки входы первого и второго узлов задержки объединены и подключены к выходу входного дифференцирующего элемента, вход которого подключен к входу устройства, а выходы первого и второго узлов задержки подключены к соответствующим входам формирующего триггера, выход которого подключен к выходу устройства, объ.единенные вторые входы датчиков интервалов задержки обоих узлрь задержки подключены,к первому управляющему входу, а объединенные третьи (входы датчиков интервалов задержки - к второму управляющему входу устройства 2. Недостатком .этого устройства является невозможность управляемой задержки импульсов с амплитудно.импульсной модуляцией. Цель изобретения - расширение функциональных возможностей путем обес-. печения возможности управляемой задержки .видеосигналов с амплитудноимрульсной модуляцией. Поставленная цель достигается тем, что в устройс-гво, содержащее формирующий триггер, входной дифференцирующий элемент, вход которого прД ключен к первому входу устройства, а выход соединен с объединенными входами первого и ВТОРОГО блоков ограничения амплитуды сигналов, выходы которых соединены с первыгли входами соответственно первого и второго узлов задержки вторые, входы которых объединены и подключены к второму входу устройства, а их выходы подключены к соответствующим входам формирующего триггера, введены первый и второй блоки выделения маркера/ блок раскоммутации каналов, К блоков памяти/ К элементов И, элемент ИЛИ и блок раскс 4мутации импульсов, К выходов которого подключены к вторым входам соответствующих элементов И, первые входы которых соединены с выходами осответствующих блоков памяти, а выходы с соответствующими входами элемента ИЛИ, выход которого являемся выходо устройства, первый вход устройства соединен с первым входом блока раскоммутации каналов, между первым и Ьторым входами которого подключен первый блок выделения маркера, а вы ходы которого соединены с входами блоков памяти, выход формирующего триггера соединён с объединенными . первым входом блока раскоммутации импульсов и входом второго блока выделения маркера, выход которого соединен с вторым входом блока раскоммутации импульсов, третий вход которого соединен с выходом первого узла задержки. Блок раскоммутации импульсов содержит элемент ИЛИ, К элементов И первой группы элементов, К триггеров, К элементов И второй группы элементов, первые входы которых объединены и подключены к третьему входу блока и выход каждого из кото рых через соответствующий триггер подключен к первому входу соответст вующего элемента И первой группы эл ментов , выход которого является одним из К выходов блока раскоммутаци импульсов, вторые входы элементов И первой группы объединены и подключены к,первому входу блока раскомму тации импульсов, второй вход предше вующего 1-го триггера объединен с первым входом последующего U+1) триггера, второй вход К-го триггер объединен с первым входом первого триггера, выход рредшествующего т-г триггера подключен к второму входу последуквдего i4i+1)-го элемента И вт .рой группы элементов, выход К-го триггера через элемент ИЛИ подключе к второму входу первого элемента И второй группы элементов, второй вхсз элемента ИЛИ соединен с .вторым входом блока раскоммутации импульсов. Конкретное выполнение узлов задержки может быть таким,, как в ;. . известном устройстве. На фиг.1 приведена функциональна схема предлагаемогоустройства на фиг.2 - схема выполнения блока раскоммутаций импульсов; ка фиг.З и 4 временные диаграммы. Устройство содержит входной дифференхдарующий элемент 1, первый и второй блоки 2 2 о Р иичения амплитуды, первый и второй блбки 3 и 3 выделения Маркера, причем вход первого из них соединен с входом входного дифференцирующего элемента 1 и входом блока 4 раскоммута ции каналов, соединенного своими выходами с входами блоков 5 - 5fe- п 6. мяти, первый и второй узлы б-, и ь - 7к , вадержки, элементы И 7. ;ненныё выходами с входами элемента соед ИЛИ 8, формирующий триггер 9 соединенный первым входом с третьим входом, блока 10 раскоммутации импульсов, а -выходом с первым входом бло-. ка 10 раскоммутации импульсов, со11:. пердержащего элементы И вой группы, одни входы которых объединены и подключены к первому входу блока раскоммутации импульсов, ,а вторые подключены соответственно к выходам триггеров 12|, первые входы которых подключены к выходам соответствующих элементов И 13,- 13j второй группы, первые которых О15ъединены и подключены к третьему входу блока 10 раскоммутации импульсов. Выходы и вторые входы предшествующих триггеров 12|,|Соединены соответственно с вторыми входами и с выходами последующих элементов И 132- второй группы, второй вход последнего триггера 12 к соединен с п.ервым входом первого триггера 12, а выход его через элемент ИЛИ 14 подключен к второму входу первого элемента И 13 второй группы, второй вход элемента ИЛИ 14 подключен к второму входу блока 10 раскоммутации импульсов. Первый вход 15 устройства соединён с входом входного дифференцирующего элемента 1, а второй его вход 16 - с объединенными вторыми входами узлов 6 и 6, задержки, выход 17 входного дифференцирующего элемента I подключен к объединенным входам блоков 2 и 2 2 ограничения выходы которых соединены амплитуды, с первыми входами 18-J и 18; узлов выходы 19-,- 19,( бло6, и 6 ков 5|, памяти подключены к первым входам элементов И 7- - 7j, , а выходы 20 и 20, узлов 6 и 02 задержки соединены соответственно с первым ивторым входами формирукяцего триггера 9, выход которого соединен с входом 21 второго блока 3 выделения маркера, соединенного выходом с вторым входом блока 10 раскоммутации импульсов, а вькод элемента ИЛИ 8 соединен с выходом 22 устройства. Узлы 6 и 6- задержки могут быть выпояне.ны аналогично исполнению в известном устройстве. Структурная схема однозт из них приведена на фиг.2. Узел состоит из N блоков формирования сигналов задержки 23-1 23-N. КаждаШ из первых N-1 блоков содержит триггер 24-l-24-(N-l)соответственног первый вход которого подключен к первому входу соответствующего блока 23-1-23-(N-1) формирования сигналов задержки и к одному из входов элемента 25-l-25-(N-l)запре та, другой вход которого подключен к выходу триггера 24-1 24-lN-l) , а выход - к первому входу соответствующего датчика 26-1-26 1Н-1) интер-, вгшрв задержки соединенного вторым своим входом с вторым входом блока 23-l-23-(N-l формирования сигналов задержи , а выходом - с вторьом входом триггера 24-1-24-iN-l), элемент И 27-l-27-(N-l), входы которого подключены соответственно к первому входу и выходу триггера 24-1-24-lNа выход которого соединен с первым выходом 28-1-28-iH-l)блока 23-1-23(N-1) формирования сигналов задерж-п ки, дифференцирующий элемент 29-1:29-(N-l), вход 30-1-30-(N-1) которого соединен с выходом триггера 24-l-24-(N-l) , .а выход т с вторым выходом 31-1-31-iN-l) блока 23-1-23 IN-1)формирования сигналов задержки Последний N-ый блок 23-N формирова НИН сигналов задержки содержит триг гер 24-N, соединенный первым своим входом с первым входом блока 23-N формирования сигналов задержки и с первым входом датчика 26-N интервалов задержки, соединенного вторым своим входом с вторым входом блока 23-N формирования сигналов за,цержки, а выходом - с вторым входом триггера 24-N, дифференцирующий элемент 29-N , вход 30-N которого соединен с выходом триггера 24N, а ход - с вторым выходом 31-N блока 23N формирования сигналов задержки. Первые выходы предыдущих (i-1)-ы блоков формирования сигналов задерж ки соединены с первыми входами последующих i-HX блоков, а их вторые выходы 31-1-31-N подключены к соот ветствующим входам элемента ИЛИ 32, выход которого подключен .к выходу 20 узла 6 задержки, первый вход первого блока 23-1 формирования сиг Налов задержки соединен с первым входом 18 узла б задержки, а вторые входы блоков 23 формирования сигналов задержки объединены и соединены с вторым входом узла б задержки. Временные диаграмг т поясняющие работу предлагаемого устройства, приведены на фиг.З и 4. Единица в индексе обозначения указывает на первый узел, двойка в индексе - на принадлежность к второму узлу. Работа устройства происходит следующим образом. Радиосигнал с входа 15, представ ляющий собой импульсную последовательность с амплитудно-импульсной модуляцией (фиг.З (ВХОД 15 ) дифферен цируется входньлм дифференцирующим элементом 1 (.фиг.1, выход 17) и ограничивается соответственно сверху и снизу в блоках 2 и 22 ограничения амплитуды сигналов. Одновременн производится обычная для телеметрии операция выделения маркера первым блоком 3-) выделения маркера и раско мутации каналов блоком 4 раскоммута ции Каналов. Преобразованная в код амплитуда импульсов раскоммутирован ных каналов запоминается, блоками 5л ,5-2 ,. . .5 и- памяти (фиг.1 и 4j.выходы 19, 192,...9,). - Ограниченные блоками 2 и 2 импульсы дифференцирования видеосигнала запускают в каждом из узлов б-, и 6 2 задержки (фиг.2 триггеры 24-1, 24-12 и одновременно после прохождения элементов 25-1 и 25-12 запрета служат сигналом начала интервала задержки. По истечении установленного времени задержки датчики 26-1 интервалов задержки формируют импульсы, возвращающие триггеры в исходное (нулевое) состояние (фиг.З, входы 30-1,30-12). Импульсы дифференцирования, поступающие на входы триггеров 24-12 окончания установленного интервала задержки- проходят через открытые элементы И 27-1 и 27-1 на запуск триггеров 24-2, 24-2„ и счетчиков 26-2, 26-2 у интервалов задержки последующих блоков 23-2,23-22 формирования сигналов задержки (фиг.З входы 30-2, 30-22). При этом до тех пор, пока на выходах триггеров 24-li. , 24-12 будет высокий потенциал, открывающий элементы И 27-1, 27-12, запирающий элементы 25-1, 25-12 запрета, на входы датчиков 26-1,26-12 не будут проходить импульсы, определяющие начало интервала задержки.. Работа последующих блоков 23-1ч, 23-2|.. . 23 (N-11, 23-12, 23-22, ...,23-(N-i; формирования сигналов задержки аналогична работе первых блоков 23-1-,, 23-12. до окончания интервала- задержки на входы триггеров 24-1, .24-12 поступит N-ый от момента начала задержки импульс дифференцирования, то он пройдет через открытые элементы И 27-1, 27-2, . . .j27-(N-lL, 27-12, 27-2,..,,27- (N -1)2 на запуск триггеров 24-N,24- N2 и N-ых датчиков 26-N,26 -N2 интервалов задержки (фиг.2) , (фиг.З /входы ЗО-МуЗО-Мз). Дифференцирующими элементами 29-lc,, 29-2,..., 29-N-, , 29-12,...,2 9 -N2 формируются импульсы дифференцирования спадов импульсов, вырабатываемых триггерами 24-1, 24-2,...,24-N 24-12, 24-22, . . . , 24-N2(фиг. 3, выходы 31-1, 31- 2;,,..., 31 -N, 31-12 31-22 ,. .. , 31- N2). Объединенные в единый поток элементами ИЛИ 32-, и 322 импульсы дифференцирования на выходе 20, (фиг.З выход 20) запускают формирующий триггер 9, а импульсы дифференцирования (фиг.З, выход 202) возврсодают его в нулевое состояние. Управляемый сигналами дифференцирования формирующий триггер 9 восстанавливает исходную структуру импульсной последовательности на входе 21 (фиг.3)вход 21) с задержкой по време-ниг, задаваемой датчиками 26-1 ,26-2 ,., 26-NI , 26-12 г 26-22 ..., 2бН 2Интер валов задержки. Датчики 26-1., 26-2.,,, ,26-N , 26-12 , 26-2- ,. . .,26- Nj управляются по управляющему входу 16 от устройс ва измерения разности в системах ав матической подстройки и синфазирования импульсных последовательносте Устройство обеспечивает задержку импульсной последовательности, в пределах периода следования одного из маркеров телеметрического кадра (например маркера основного коммута тора фиг.-З и 4), поэтому и количе во (к ) блоков памяти должно соответствовать , количеству каналов в к ре (от маркера до маркера ). Восстановленная на выходе форми рующего . триггера 9 с задержкой t структура принимаемого телеметричес кого сигнала не несет информации о контролируемых параметрах, поскол ку лишёна амплитудной модуляции. Второй блок Sj вьщеления маркера из задержанной восстановленной структур, телеметрического сигнала выделяет соответствующий маркер/ блок 10 раскоммутации импульсов производит распределение импульсов восстановленной структуры телеметрического сигнала по соответствующим каналам. При.этом открываются соответствующие элементы И 7,, 7 , 7( в моменты времени, определяемые моментами формирования, импульсов восстановленной задержанной структуры телеметрического сигнала (фиг.4, вход 21 ) и разрешается считывание через элементы И 7, 7, 7(j и элемент ИЛИ 8 представленных в цифровой форме и хранящихся в блоках 5, 2--f K памяти значений амплитуды импульсов. В результате работы устройства на его выходе формируется задержанный на установленное время телеметрический кадр с представлением информационного параметра амплитуд импульсов вцифровой форме, наиболее удобной для последующей обработки и регистрации. Блок 10 раскоммутации импульсов работает следуквдим образом. Начало работы блока определяется появлением импульса на выходе второго блока 3 выделения маркера. При появлении импульса открывается первый элемент И второй группы элементов 13;, и первым после маркера импульсом переводится в единичное состояние первый триггер 12. При этом открываются первый элемент И первой группы элементов 11-,, разрешая прохождение импульса первого канала (фиг.4,вход 21) для считывания цифровой информации из первого блока 5 памяти и второй элемент И 132 разрешая запуск триггера 12„ импульсом с выхода 20 второго канала. Последующая работа блока 10 аналогична рассмотренной. Результатом работы блока 10 является раскоммутация импульсов каналов, обеспечивающая считывание с установленной задержкой сообщений, хранящихся в блоках 5, З. памяти. Предлагаемое устройство отличается от известного возможностью задержки видеосигналов с амплитудноимпульсной модуляцией.

lt-п

п

17

жн

±

е ниш

}б Фиг2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство передачи команд управления | 1982 |

|

SU1107303A1 |

| СПОСОБ ВОСПРОИЗВЕДЕНИЯ СИГНАЛОВ ЦИФРОВОЙ ИНФОРМАЦИИ С МАГНИТНОГО НОСИТЕЛЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1990 |

|

SU1825194A1 |

| УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ СИГНАЛОВ ЦИФРОВОЙ ИНФОРМАЦИИ С МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2014649C1 |

| Модель ветви сетевого графика | 1978 |

|

SU723594A1 |

| Устройство для задержки импульсов | 1981 |

|

SU980267A1 |

| Устройство передачи данных | 1977 |

|

SU634459A2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КООРДИНАТ ВРАЩАЮЩЕГОСЯ РЕАКТИВНОГО СНАРЯДА | 1997 |

|

RU2122175C1 |

| Однородный спектро-коррелометр | 1981 |

|

SU970382A1 |

| Устройство для моделирования систем массового обслуживания | 1988 |

|

SU1552196A1 |

| Телевизионный цветосинтезатор | 1985 |

|

SU1284006A1 |

1. УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ : ВИДЕОСИГНАЛОВ, содержащее формирующий триггер, входной дифференцирую-щий элемент, вход которого подключен к первому входу устройства, а выход соединен .с объединенными входами первого и второго блоков ограничения амплитуды сигналов, выходы KOTOjaix соединены с первыми входами соответственно первого и второго узлов задержки, вторые входы которых объединены и подключены к второму входу . устройства, а их выходы подключены к соответствующим входам формирующего триггера, отлич-ающе ес я тем, что,, с цельна расширения функциональных возможностей путем обеспечения возможности управляемой . задержки видеосигналов с амплитудноимпульсной модуляцией, в него введены первый и второй блоки выделения маркера, блок раскоммутации каналов, К блоков памяти, К элементов И, элемент ИЛИ и блок раскоммутации иитульсов, к выходов которого подключены к. вторым входам соответствукааих элементов И, первые входы котогялх соединены с выходами соответствующих блоков па.мяти, а выходы - с соответствующими входами элемента ИЛИ, выход icoToporo является выходом устройства, первый вход устройства соединен с первым входом блока раскоммутации каналов, между первым и вторым входами которого подключен первый блок вьщеления маркера, а выходы которого соединены с входами блрков памяти, выход формирующего триггера соединен с объединенными первым, входом блока раскоммутации импульсов и входсял второго блока выделения маркера, выход которого соединен с вторым входом блока раскоммутации импульсов, третий вход которого соединен с выходом первого узла задержки. 2. Устройство по П.1, отличающееся тем, что блок раскоммутации импульсов содержит элекент ИЛИ,К элементов И первой груп пьиэлементов, К триггеров, К элемен(О тов И второй группы элементовJ пер-вые входы которых объединены и подключены к третьему входу блока и выход каждого из которых через .соответствующий триггер подключен к первому входу соответствующего элемента И первой группы элементов, выход которого является одним из К выходов блока раскоммутации имоо пульсов, вторые входы элем,емтов И . . первой группы объединены и подключены к первому входу блока раском4: Ю мутации импульсов, второй вход предшествующего i-го триггера объедниеи с первым входом последующего (f -flj -го триггера, второй вход К-го триггера объединен с первым входом первого триггера, выход предшествунхаего j-ro триггера подключен к второму входу последующего (i+l)-ro элемента И второй группы элементов, выход K-fo триггера через элемент ИЛИ подключен к второму входу первого элемента И второй группы элементов,, второй вход элемента ИЛИ соединен с вторым .входом блока раскоммутации импульсов. .

Авторы

Даты

1983-08-23—Публикация

1982-04-30—Подача