(5) УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задержки видеосигналов | 1982 |

|

SU1037421A1 |

| Устройство для измерения средней частоты серии импульсов | 1990 |

|

SU1737356A1 |

| Устройство для моделирования систем массового обслуживания | 1981 |

|

SU962970A1 |

| Цифровой измеритель длительности пачки импульсов | 1980 |

|

SU892412A1 |

| Цифровой частотомер с нониусной интерполяцией | 1980 |

|

SU868612A1 |

| Временный селектор импульсов | 1979 |

|

SU839039A1 |

| Селектор импульсов по длительности | 1979 |

|

SU813760A1 |

| Селектор импульсов по периоду следования | 1976 |

|

SU660223A1 |

| Устройство для многоканального контроля | 1983 |

|

SU1110313A2 |

| Измеритель временных интервалов | 1987 |

|

SU1597859A2 |

Изобретение относится к радиотех нике, автоматике, вычислительной и измерительной технике и преднаэначено для управляемой задержки импульсных сигналов. Известно устройство, которое содержит последовательно соединенные первый временной селектор, между вы ходом и вторым входом которого подключен первый оход и первый выход первого триггера, первый собирательный элемент, второй триггер, второй временной селектор,первый пересчетный блок, второй собирательный элемент, вспомогательный пересчетный блок, выход которого подключен ко второму входу первого триггера, второй выход которого подключен к третьему входу второго временного селек тора, а также последовательно соединенные генератор счетных импульсов, третий временной селектор, вторые и третьи входы которого объединены с соответствующими входами второго временного селектора, и второй пересчетный блок, второй вход которого объединен с вторым входом первого пересчетного блока и подключен к выходу вспомогательного пересчетного блока, а выход подключён ко второму . входу первого собирательного элемента и второму входу третьего три1- гера, выход которого соединен с первым входом третьего временного селектора, выход первого пересметного блока-элемента соединен со вторым входом второго триггера и первым входом третьего триггера, выходы вспомогательного пересчетного блока соединены с соответствующими входами матрицы Cl . Однако данное устройство имеет недостаточные быстродействие и точность. Наиболее близким по технической сущности к предлагаемому является устройство, которое представляет собой последовательно соединенные пер398вый временной селектор, реверсивный счетчик импульсов и дешифратор нуля, выход которого подключен к первому входу триггера, с входом первого spe менного селектора объединен вход последовательно соединенных дифференцирующей цепи и схемы задержки фронта импульса, выход которой подключен к второму входу триггера, первый выход которого является выходом устройства, а второй через второй временной селектор подключен к второ му входу реверсивного счетчи1 а импульсов, к объединенным вторым входам временных селекторов подключен выход генератора счетных импульсов 21. Недостаток известного устройства заключается в сложности технического решения, низком быстродействии и ограниченной точности задержки. Точность задержки в устройстве опре деляется частотой следования счетных импульсов, которая в свою очередь ограничивается возможностями по быстродействию счета импульсов реверсивными счетчиками. Из условия 1э6еспечения необходимой точности задержки накладываются ограничения на частоту следования и длительность задерживаемых импульсов. Цель изобретения - повышение быст родействия уст ройства . Поставленная цель достигается тем что в устройство, содержащее формирующий триггер и первый узел задержки из К параллельных блоков формирования сигналов задержки, каждый из {Которых включает в себя триггер и дифференцирующий элемент, введены входной дифференцирующий э..емент и аналогичный второй узел задержки, а Q каждый из узлов задержки введены блок ограничения амплитуды сигналов и элемент ИЛИ, при этом в каждом из узлов задержки в каждый из первых К-1 блоков формирования сигналов за держки введены элемент И, элемент ЗАПРЕТ, датчик интервалов задержки, а в К-й блок формирования сигналов задержки каждого из узлов введен да мик интервалов задержки, причем вход триггера подключен к входу блока фо мирования сигналов задержки, а выход объединенного по входу с первым вхо дом триггера элемента И подключен к первому выходу блока формирования сигналов задержки, между первым вхо ДОМ и выходом триггера включен элемент ЗАПРЕТ, выход которого через датчик интервалов задержки подключен к второму входу триггера, выход которого подключен к объединенным второму входу элемента И и входу дифференцирующего элемента, выход которого подключен к второму выходу блока формирования сигналов задержки, в IC-M блоке формирования сигналов задержки между первым и вторым входами включен датчик интервалов заЬержки, выход триггера подключен к входу дифференцирующего элемента, выходы дифференцирующих элементов блоков формирования сигналов задержки подключены к соответствующим вхо- дам элемента ИЛИ, выход которого подключен к выходу узла задержки, а вход блока ограничения амплитуды сигналов, подключенного к входу первого блока формирования сигналов задержки, соединен с входом узла задержки, входы первого и второго узлов задержки объединены и подключены к выходу входного дргф(юренцирующего элемента, вход которого подключен к входу устройства, а выходы первого и второго узлов задержки подключены к соответствующим входам формирующего триггера, выход которого подключен к выходу устройства, объединенные вторые входы датчиков интервалов задержки обоих узлов задержки подключены к первому управляющему входу, а объединенные третьи входы датчиков интервалов задержки - к второму управляющему входу устройства. На фиг. 1 приведена структурноя электрическая схема устройства. . Устройство содержит дифференцирующий блок 1, блоки ограничения амплитуды сигналов 2-1., 2-2, элементы ИЛИ 3-1, 3-2, формирующий триггер k, узлы 5-2 задержки, блоки формирования сигналов задержки 6-Ц, 6-2, 6-(К-1) 6-К, б-Ц, 6-2i, 6-(К-1)2, 6-К, элементы И 7-Ц, 7-21, 7-CK-1L, 7-4, 7-2,, 7-fK-l)2, элемент ЗАПРЕТА 3-1i, 8-2V, 8-(К-1) 8-1,1, 8-22 8-(К-1)2, дифференцирующие элементы 9-1, 9-2 , 9-(К-1)-,, 9-К, 9-12.. 9-22, 9-(к-1)7. S-KJ. датчики интервалов задержки Ю-Ц, 10-2, lO-(K-l), 10-К., 10-1.2, 10-2.1, 10-(К-1)„, Ю-К-, триггеры 11-Ц, 11-2.,, lT-(K-l)i, 11-К-,, 11-12.О1-2д 11 - (К-13а, 41 -Кг, выход 12 устройст-

ва, выход 13, управляющие входы И, 15. Единица в индексе указывает на 1-й узел, два в индексе указывает на 2-й узел. ,

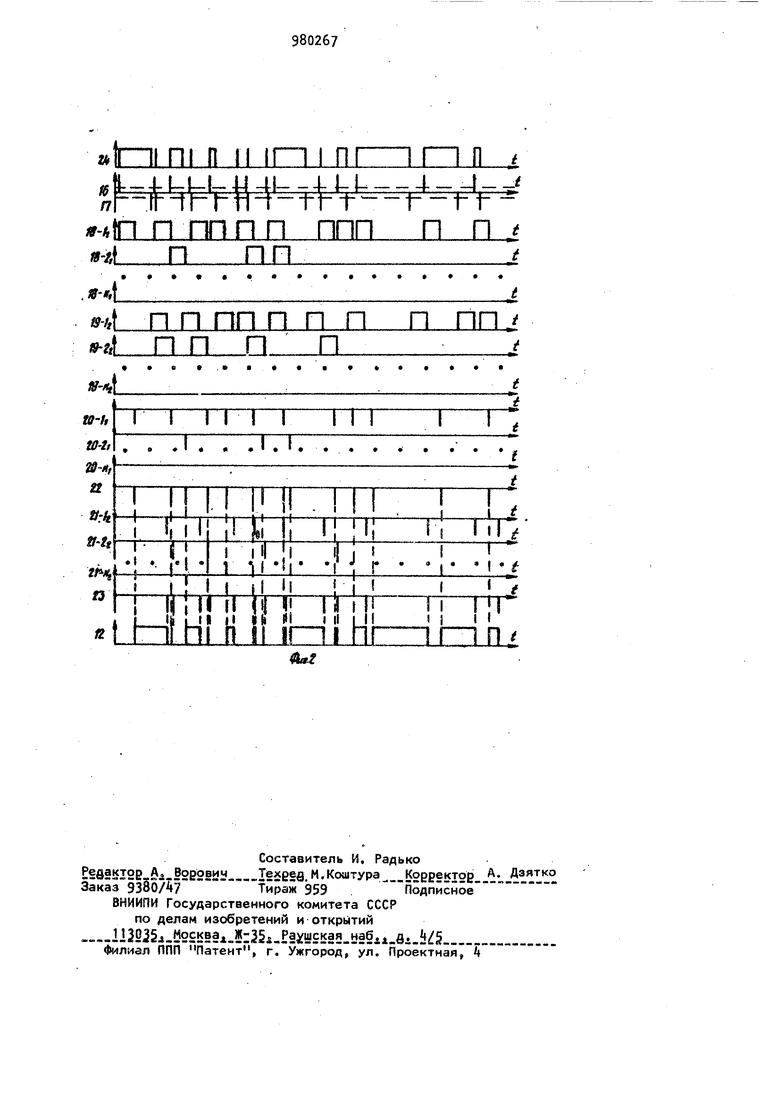

На фиг. 2 приведены временные ди s аграммы, поясняющие работу устройства.

Устройство работает следующим образом.

Импульсный сигнал дифференцирует- ся дифференцирующим блоком 1 (. 1) и ограничивается сверху вниз в блоках ограничения амплитуды сигналов 2-1, 2-2 первого и второго узлов 5-1 5-2 задержки соответственно (фиг. 2, поз. 16, 17).

Импульсы дифференцирования кают-в каждом из узлов задержки 5-1, 5-2 триггеры 11-1-, 11-12 первого и второго блоков формирования сигналов задержки 6-1, 6-12 одновременно после прохождения элементов ЗАПРЕТ 8-1-, , ;8-l2 служат сигналом начала инервала задержки. По иctёчeнии уста- is новленного времени задержки датчики 10-li, 10-12 формируют импульсы, возвращающие триггеры в исходное (нулевое) состояние (фиг. 2, поз. 18-1-,, 9-12) Импульсы дифференцирования, jg поступающие на входы триггеров 11-1 11-1/1 Д° окончания установленного интервала задержки, проходят через открытые элементы И 7-Ц 7-12 запуск триггеров 11-2-;, 11-22. и Датчиков| 10-2.,, 10-2 2 интервалов задержки последующих блоков формирования сигналов задержки 6-2, 6-22 С) i поз. 18-2, 19-22). При этом до тех пор, пока на выходах триггеров 11-1.J будет высокий потенциал, открывающий элементы И 7-1ij 7-1 2 и запирающий элементы ЗАПРЕТ 8-Ц, 8-1«1, на входы датчиков 10-Ц, 10-12 не будут проходить импульсы, опре- .. деляющие начало интервала задержки. Работа последующих блоков 6-1-,, .. 6- (К- 1 )-j , 6- 1 2 6-2о. . 6-(К-1)2 формирования сигналов задержки аналогична работе первых блоков 6-Ц, 6-12 t Если же до оконча ния интервала задержки на входы триггеров 11-1, 11-12 поступает К-й от момента начала задержки импульс дифференцирования, то он проходит через открытые элементы И 7-1-f ,7-2, 7-(К-1).,, 7-12. 7-22 7-(К-1)2 на запуск триггеров 11-К, 11-К 2 и К-х датчиков 10-К,, 10-Kj интервалов .

задержки (.фиг. 2, поз. 18-К.,, 19-К2) Дифференцирующими элементами 9-1-) 9-2-,;9-(К-1).,, 9-K,,9-l2, 9-22 9-(К-1)2 9-К2 формируются импульсы дифференцирования спадов импульсов, I вырабатываемых триггерами 11-1.., 11-2, 11-(К-1), 11-К.,, 11-1,, 11-2« 11-(K-1)/3t 11-К2 (фиг, 2, поз. 20-Ц, 20-2-,, 20-К, 21-1 21-22 21-Ki). Объединенные s единый поток элементами ИЛИ.3-1 3-2 импульсы 27 дифференцирования запускают формирующий триггер , а импульсы дифференцирования 23 возвращают его в нулевое состояние. Управляемый сигналами дифференцирования формирующий триггер 4 восстанавливает исходную импульсную последовательность 2 с задержкой по времени, задаваемой датчиками , 10-2, lO-(K-r)-,, 10-К, 10-12 0-22j10-(K-1)2 10-К интервалов задерж- ки (фиг. 2, поз. 12).

Датчики 10-Ц, 10-2, lO-(K-l).,, 10-К.,, 10-12 (К-1)4, 1д-К2 при этом могут управляться как. ному входу, так и по нескольким, например от устройства измерения разности фаз грубо . и точно в системах автоматической подстройки и синтезирования, импульсных последовательностей .

Предлагаемое устройство выгодно отличается от устройства-прототипа технической реализацией, более высоким быстродействием и точностью задержки импульсов.

Формула изобретения

I

Устройство для задержки импульсов содержащее формирующий триггер и первый узел задержки из К параллельных блоков формирования сигналов задержки, каждый из которых включает в себя триггер и дифференцирующий элемент, отличающееся тем, что, с целью повышения быстродействия, EI него введены входной дифференцирующий элемент и аналогичный второй узел задержки, а в каждый из узлов задержки введены блок ограничения амплитуды сигналов и элемент, ИЛИ, при этом в каждом из узлов задержки в каждый из первых К-1 блоков формирования сигналов задержки введены элемент И, элемент ЗАПРЕТ, датчик интервалов задержки, а в К-й

каждого из узлов задержки введен датчик интервалов задержки,примем вход триггера подключен к входу блока фориироаания сигналов задержки, а выход объединенного по входу с первым вхо дом триггера элемента И подключен к первому выходу блока формирования сигналов задержки, между первым входом и выходом триггера включен элемент ЗАПРЕТ, выход которого через датчик интервалов задержки подключен к второму входу триггера, выход которого подключен к объединенным второму входу элемента И и входу дифференцирующего элемента, выход которого подключен к второму выходу формирования сигналов задержки, и К-м блоке формирования сигналов задержки между первым и вторым входами включен датчик интервалов задержки, выход триггера подключен к входу дифференцирующего элемента, выходы дифференцирующих элементов блоков формирования сигналов задержки подключены к соответствующим входам элемента ИЛИ, выход которого подключен к выходу узла задержки, вход

лов, подключенного к входу первого блока формирования сигналов задержки , соединен с входами узла задержки, входы первого и второго узлов задержки объединены и подключены к выходу входного дифференцирующего элемента, вход которого подключен к входу устройства, а выходы первого и второго узлов задержки подключены к соответствующим входам формирующего триггера, выход которого подключен к выходу устройства, объединенные вторые входы датчиков интервалов задержки обоих узлов задержки подключены к первому управляющему входу, а объединенные третьи входы датчиков интервалов задержки - к второму управляющему входу устройства,

Источники информации, принятые во внимание при экспертизе

с. .

Авторы

Даты

1982-12-07—Публикация

1981-02-20—Подача