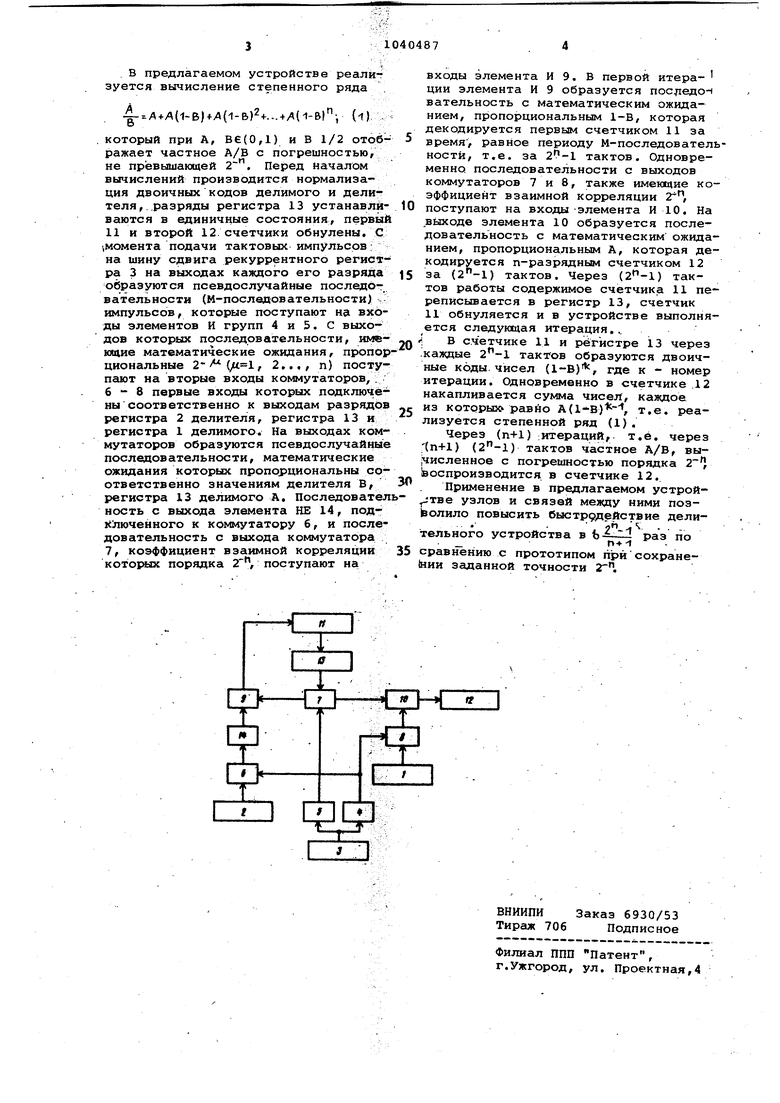

Изобретение относится к вычислительной техник может быть использовано в различных вычислительных устройствах и в стохастических вычислительных машинах. Известно устройство для деления дввич.ных Чисел, в котором используется датчик случайных чисел 1. , Недостатком устройства является аппарэтурная сложность и отсутствие универсальности. Наиболее близким по технической сущности к предлагаемому является стохастическое устройство для деления двоичных чисел, содержащее регист делимого, регистр делителя, рекурент ный регистр сдвига, первую и вторую .группу элементов И, первый и второй коммутаторы, элемент И, счетчик, при этом выходы разрядов рекуррентного регистра сдвига соединены с соответствующими входами элементов И первой группы в прямой, а с входами элементов И второй группы - в обратной пос ледовательности, выходы элементов И первой группы соединены с второй гру пой входов первого коммутатора, а вы ходы элементов И второй группы соеди нены с второй группой входов второго KONwyTaTOpa, первая группа входов первого коммутатора присоединена к выходам регистра делителя, выход эле мента И соединен с входом счетчика. Для выполнения операции деления осуществляется преобразование двоичных чисел в псевдослучайные последовательности, генерируемой датчиком случайных чисел. Структура схемы известного устройства является неизмей ной при любом значении делителя, что обеспечивает его -универсальность (2 Однако при требуемой точности порядка 2 вычисление частного производится за () тактов, что может оказаться неприемлемым в быстродейст вующих вычислительных устройствах. Цель изобретения - повышение быст родействия, Поставленная.цель достигается тем что псевдосфохастическое устройство для деления двоичных чисел, содержащее регистры делителя и делимого, первый коммутатор, первая группа вхо дов которого соединена с выходами разрядов регистра йелителя, второй коквлутатор, первую и вторую группы элементов И, выходы которых соединены соответственно с второй группой входов первого коммутатора и первой группой входов второго коммутатора, рекуррентный регистр сдвига, выходы разрядов которого соединены с соответствукхаими входами элементов И пер вой группы в прямой, а с входс1МИ эле ментов И второй группы - в обратной последовательности, первый счехчик, первый элемент И, выход которого сое динен с входом первого счетчика, дополнительно содержит второй счетчик, регистр, третий коммутатор, второй элемент И, элемент НЕ, вход которого соединен с выходом первого коммутатора, а выход - с первьлм входом первого элемента И, выходы разрядов первого счетчика соединены с входами регистра, выходы разрядов которого сое-; динены с второй группой входов второро коммутатора, первый и второй/ выходы второго коммутатора соединены соответственно с вторым входом первого элемента И и с первым входом второго элемента И, выходы разрядов регистра делимого соединены с первой группой -входов третьего коммутатора, вторая группа входов которого подключена к выходам первой группы элементов И, а выход соединен с вторым входом второго элемента И, выход второго элемента И соединен со входом второго счетчика, выходы, разрядов которого являются выходами устройства. На чертеже представлена блок схема устройства. Схема содержит регистр 1 делимого, регистр 2 делителя, рекуррентный регистр 3 сдвига, первую 4 и вторую 5 группы элементов И, первый 6, второй 7 и третий 8 коммутаторы, первый 9 и второй 10 элементы И, первый 11 и второй 12 счетчики, регистр 13, элемент НЕ 14, Выходы разрядов регистров делимого 1 и делителя 2 соединены с первыми группами входов соответственно третьего 8 и первого 6 коммутаторов, Выходы разрядов рекуррентного регистра 3 сдвига соединены с- соответству:1сщими входами элементов И первой группы 4 в прямой, а с входами элет ментов И второй группы 5 - в обратной последовательности. Выходы первой группы 4 элементов И соединены с вторыми группами входов первого б и третьего 8 коммутаторов, а выходы второй группы 5 элементов И соединены с первой группой входов второго коммутатора 7, Выход первого ко1мвлутатора 6 через элемент НЕ 14 соединен с первым входом первого элемента И 9, второй вход которого соединен с первым выходом второго комму- татора 7, а выход соединен с входом первого счетчика 11, Выходы разрядов первого счетчика 11 соединены с входами регистра 13, выходы разрядов которого соединены с второй группой входов второго кс 1мутатора.7. Второй выход второго коммутатора 7 боединеи с первым входом второго элемента И 10, второй вход которого соединен с выходом третьего коммутатора 8, а выход соединен с входом второго ч;счетчика 12, Устройство работает следующим образом , В предлагаемом устройстве реалйт зуется вычисление степенного ряда 4- Л+А(1-В)+Л(1-6)2-1-...+х4(-1-В| . который при А, В6(0,1) и в 1/2 отображает частное А/В с погрешностью, не превышающей 2. Перед началом вычислений производится нормализация двоичных кодов делимого и делит теля, разряды регистра 13 устанавливаются в единичные состояния, первый 11 и второй 12. счетчики обнулены. С момента подачи тактовых импульсов: на шину сдвига рекуррентного регистра 3 на выходах каждого его разряда образуются псевдослучайные последовательности (М-послвдовательности)импульсов, которые поступают на входы элементов И групп 4 и 5. С выходов которых последовательности, имеющие математические ожидания, пропор циональные 2- (., 2..., п) поступают на вторые входы коммутаторов, . 6-8 первые входы которых подключены соответственно к выходам разрядов регистра 2 делителя, регистра 13 и регистра 1 делимого. На выходах коммутаторов образуются псевдослучайные последовательности, математические ожидания которых пропорциональны со ответственно значениям делителя В г регистра 13 делимого А. Последовател ность с выхода элемента НЕ 14, подключенного к коммутатору 6, и последовательность с выхода коммутатора 7, коэффициент взаимной корреляции КОТО1ЖЛС порядка 2, поступают на входы элемента И 9. В первой итерации элемента И 9 образуется последов вательность с математическим ожиданием, пропорциональным 1-В, которая декодируется первым счетчиком 11 за время, равное периоду М-последовательностй, т.е. за тактов. Одновременно, последовательности с выходов коммутаторов 7 и 8, также имеющие коэффициент взаимной корреляции 2, поступают на входы элемента И 10. На .выходе элемента 10 образуется последовательность с математическим ожиданием, пропорциональным А, которая декодируется п-разрядным счетчиком 12 за () тактов. Через () тактов работы содержимое счетчика 11 переписывается в регистр 13, счетчик 11 обнуляется и в устройстве выполняется следугацая итерация... ; В с.четчике 11 и регистре 13 через .каждые тактов образуются двоичные коды, чисел (1-В), где к - номер итерации. Одновременно в счетчике 12 накапливается сумма чисел, каждое из КОТОРЫХ равно A(l-B)-, т.е. реализуется степенной ряд (1). Через (п+1) ;итераций, т.е. через (п+1) () тактов частное А/В, вы|численное с погрешностью порядка (Воспроизводится в счетчике 12. Применение в предлагаемом устрой1-ве узлов и связей мелдау ними позЬолило повысить быстр9Действие дели чп , s: . тельного устройства в fe -4 1 раз по п- равнению с прототипом при сохранении заданной точности 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Стохастическое устройство для деления двоичных чисел | 1978 |

|

SU769550A1 |

| Вероятностное устройство для выполнения математических операций | 1980 |

|

SU932494A1 |

| Псевдостохастическое устройство для выполнения математических операций | 1983 |

|

SU1233151A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Устройство для деления двоичных чисел | 1982 |

|

SU1084785A1 |

| Устройство для деления чисел | 1981 |

|

SU1013948A1 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

ПСЕВДОСТОХАСТИЧЕСКОБ УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ДВОИЧНЫХ ЧИСЕЛ, СО-. держащее регистры делимого и делителя, первый коммутатор, первая группа входов которого соединена с выходами разрядов регистра делителя, второй коммутатор, первую и вторую группы; элементов И, выходы которых соединены соотЕзтственно с второй группой входов первого,коммутатора и первой группой входов второго коммутатора/рекуррентньй регистр сдвига,выходы разрялов которого соединены с соответствующими входами элементов И первой группы в прямой, а с входами элемен- , тов И второй группы - в обратной последовательности, первый счетчик, первый элемент И, выход которого соединен с входом первого счетчика, о т личающеес я. тем, что, с целью повышения быстродействия, оно дополнительно содержит второй счетчик, регистр, третий коммутатор, второй элемент И, элемент НЕ, вход которого соединен с выходом первого коммутатора, а выход - с первым входом первого элемента И, выходы разрядов первого счетчика соединены с входами регистра, выходы разрядов которого сое- динены с второй группойвходов второ-3 го коммутатора, первый и второй выхо- сл ды второго коммутатора соединены соответственно с вторым входом первого элемента И и с первым входом второго элемента И, выходы разрядов регистра делимого соединены с первой группой входов третьего коммутатора, йторая группа входов которого подключена к выходам первой группы элементов И, а выход соединен с вторым входом вто4 рого элемента И, выход второго элемента И Соединен с входом второго . о счетчика, выходы разрядов которого 4 ОС являются выходами устройства. vl

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Яковлев В.В | |||

| и др | |||

| Стохастические вычислительные машины | |||

| Л., Машиностроение , с,, 95-97 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Стохастическое устройство для деления двоичных чисел | 1978 |

|

SU769550A1 |

Авторы

Даты

1983-09-07—Публикация

1982-04-02—Подача