Изобретение относится к вычислительной технике и может быть исполг:,- зовано в различных вычислительных: машинах .

Целью изобретения является расширение функциональных возможностей устройства за счет использования функционального преобразования чисел,

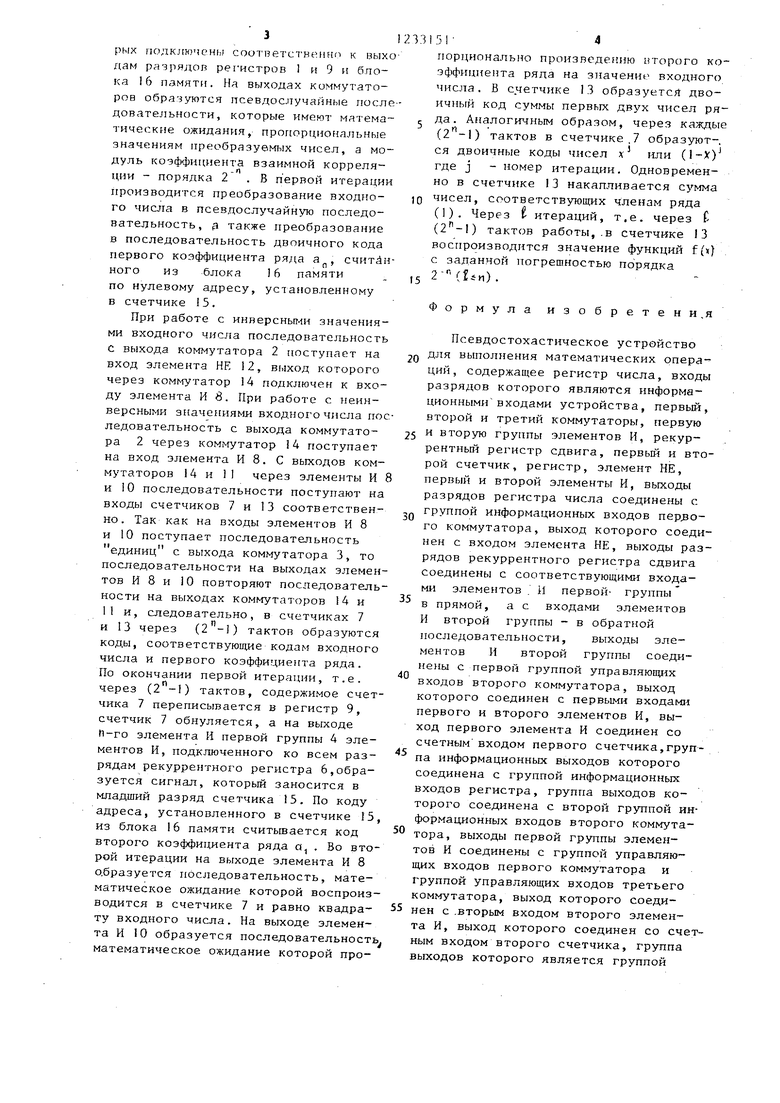

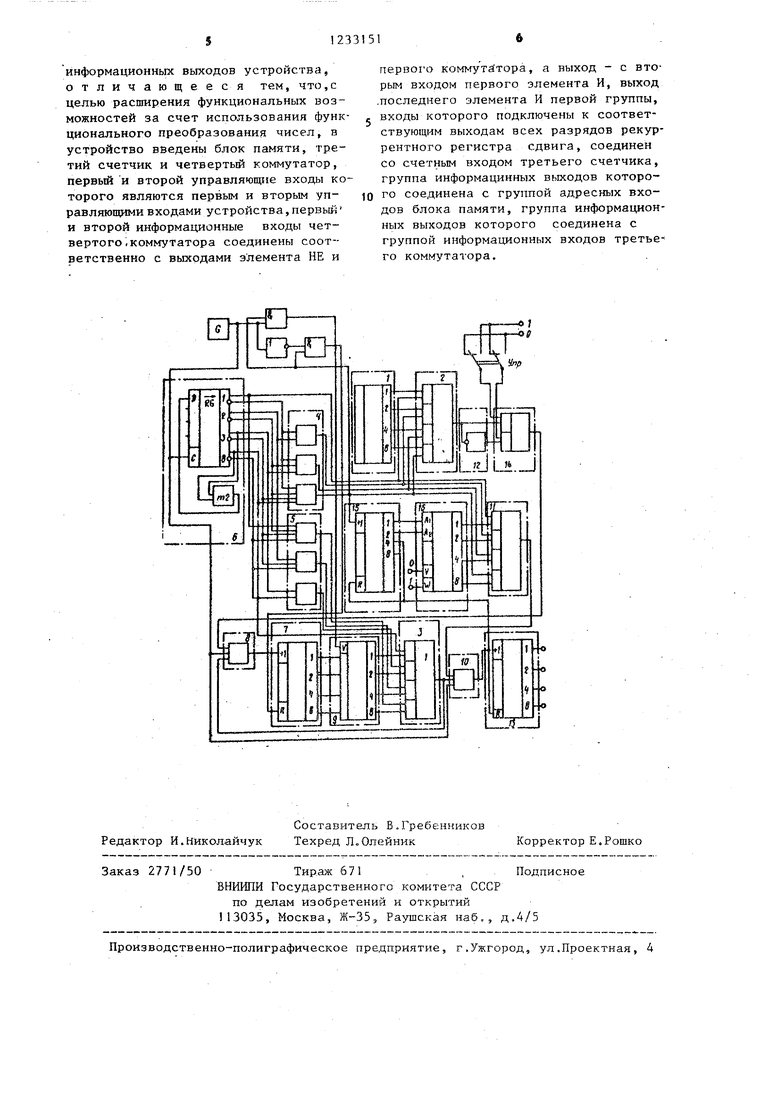

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит регистр 1 числа, первый 2 и второй 3 коммутаторы, первую 4 и вторую 5 группы элементов И,рекуррентный регистр 6 сдвига первый счетчик 7 5 первый элемент И S, регистр 9, второй элемент И 10, третий коммутатор II, элемент НЕ 12,второй счетчик 13, четвертый коммутатор 14, третий счетчик 5 и блок 16 памяти.

Регистр 6 сдвига с выходами, подключенными в прямой поспедовательнос- ти к вхрдам группы 4 элементов И, вы- .ходы которых присоединены к управляющим входам коммутатора 11, на вторые входы которого подключены информационные выходы блока 16 памяти, составляют преобразователь двоичных кодов коэффициентов , записанных в блоке I6 памяти, в псевдослучайную последовательность. С аналогичными связями регистр 6 сдвига, группа 4 элементов И, коммутатор 2 и регистр 1 составляют преобразователь двоичного кода входного числа (аргумента) ,в псевдослучайную последовательность, а регистр 6 сдвига с выходами,подключенными в обратной последовательности к группе 5 элементов И,,коммутатор 3 и регистр 9 образуют преобразователь .кода регистру. 9 в псевдослучайную последовательность.

Выходы коммутаторов И и 3 соединены с входами элемента И 10, выходы , коммутаторов 3 и I4 соединены с входа ми элемента И 8. Элементы И 8 и 10 вы полняют роль умножителей. Выход элемента И 8 соединен со счетным входом Н-разрядного счетчика 7, группа информационных выходов которого соединена, с информационными входаъси регист ра 9.

Выход коммутатора 2 соединен с входом элемента НЕ 12 и с вторым ин- формагщонным входом коммутатора 14, первый информационный вход которого гфисоединен к выходу элемента НЕ 12. Первьй и второй управляюпще входы

S

коммутатора 14,являются входами устройства. Выход элемента И 10 присоединен к входу ff -разрядного счетчика 13, выходы разрядов которого являются информационными выходами устройства. Третий счетчик 15 подключен к выходу 1 -гo элемента первой группы 4 элементов И, входы которого присоединены ко всем выходам разрядов рекуррентного регистра 6 сдвига. Информационные выходы третьего счетчика 15 присоединены к адресным шинам блока 16 памяти.

Устройство работает следующим образом,

В устройстве реализуется вычисление функций, представленных степенными рядами вида

а:х

J--0

,/x/M.

()

35

30

35

40

45

50

55

Число членов ряда (1) выбирается для обеспечения точности представления функции порядка , т.е. , где и - разрядность устройства,

В блоке 16 памяти хранятся в двоичном коде значеиия коэффициентов членов ряда (j} с помощью которых значения функций отображаются с погрешностью, не превьияающей 2 . Перед началом вычислений с помощью управляющего входного сигнала, подаваемого на входы коммутатора 14, выбирается режим работы устройства: либо с Г Шверсией преобразуемого числа, например, для вычисления корней k -и степени, либо с использованием неинверсных значений, например, при вычислении тригонометрических функций. Счетчики 7, 13 и 15 устанавливаются Б нулевое состояние. В регистр 1 заносится код входного числа. Регистры 6 и 9 устанавливаются в единичное состояние, с момента подачи тактовых импульсов на шину сдвига рекуррентного регистра 6 на вьгходах каждого его разряда образуются псевдослучайные последовательности импульсов (М-последовательности). которые поступают на входы элементов И групп 4 и 5. С выходов элементов И rpynrt 4 и 5 последовательности, имеющие математические ожидания, пропорциональные 2 (р 1 ,2,3, . . . ,п)., поступают на управляющие входы коммутаторов 2,3 и 11, информационные входы кого3

рых подключены соответственно к выходам разрядов регистров 1 и 9 и блока 16 памяти. На вь(ходах коммутаторов образуются псевдослучайные последовательности, KOTOpbte имеют матема- тические ожидания, прог орциональные значениям преобразуемых чисел, а модуль гсоэффицнента взаимной корреляции - порядка 2 . В первой итерации производится преобразование входио- го числа в псевдослучайную последовательность, э также преобразование в последовательность двоичного кода первого коэффициента ряда а, считай кого из блока 16 памяти по нулевому адресу, установленному в счетчике 15.

При работе с иннерсньп-1И значениями входного числа последовательность с выхода коммутатора 2 поступает на вход элемента НЕ 12, выход которого через кoм fyтaтop 14 подключен к входу элемента И 8. При работе с неин- версиыми значениями входного числа последовательность с выхода коммутато- ра 2 через коммутатор i4 поступает на вход элемента И 8. С выходов коммутаторов 14 и 11 через элементы И и 10 последовательности поступают на входы счетчиков 7 и 13 соответственно. Так как на входы элементов И 8 и 10 поступает последовательность единиц с выхода коммутатора 3, то последовательности на выходах элементов И 8 и 10 повторяют последовательности на выходах коммутаторов 14 и 11 и, следовательно, в счетчиках 7 и 13 через (2 -1) тактов образуются коды, соответствующие кодам входного числа и первого коэффициента ряда. По окончании первой итерации, т.е. через (2 -1) тактов, содержимое счетчика 7 переписывается в регистр 9, счетчик 7 обнуляется, а на выходе ti-ro элемента И первой группы 4 элементов И, подключенного ко всем раз- рядам рекуррентного регистра 6,образуется сигнал, который заносится в младший разряд счетчика 5. По коду адреса, установленного в счетчике 15 из блока 16 памяти считьшается код второго коэффициента ряда а, . Во второй итерации на выходе элемента И 8 образуется последовательность, математическое ожидание которой воспроизводится в счетчике 7 и равно квадра- ту входного числа. На выходе элемента И 10 образуется последовательность математическое ожидание которой про

Q

0 5

0

15 г ,

порционально произведению нторого коэффициента ряда на значение входного числа. В счетчике 13 образуете двоичный код суммы первых двух чисел ряда. Аналогичным образом, через каждые () тактов в счетчике .7 образуют-, ся двоичные коды чисел х или (1-Х) где j - номер итерации. Одновременно в счетчике 13 накапливается сумма чисел, соответствующих членам ряда (1). Через i итераций, т.е. через С () тактов работы,.в счетчике 13 воспроизводится значение функций f() . с заданной погрешностью порядка 2- Ч - п).

Формула нзобретени.я

Псевдостохастическое устройство для выполнения математических операций, содержащее регистр числа, входы разрядов которого являются информационными входами устройства, первый, второй и третий коммутаторы, первую и вторую группы элементов И, рекур- рентньй регистр сдвига, первый и второй счетчик, регистр, элемент НЕ, первый и второй элементы И, выходы разрядов регистра числа соединены с группой информационных входов перло- го коммутатора, выход которого соединен с входом элемента НЕ, выходы разрядов рекуррентного регистра сдвига соединены с соответствующими входами элементов . И первой- группы в прямой, а с входами элементов И второй группы - в обратной последовательности, выходы элементов И второй группы соединены с первой группой управляюпц1х входов второго коммутатора, выход которого соединен с первыми входами первого и второго элементов И, выход первого элемента И соединен со счетным входом первого счетчика,группа информационных выходов которого соединена с группой информационных входов регистра, группа выходов которого соединена с второй группой информационных входов второго коммутатора, выходы первой группы элементов И соединены с группой управляющих входов первого коммутатора и группой управляющих входов третьего коммутатора, выход которого соединен с .вторым входом второго элемента И, выход которого соединен со счетным входом второго счетчика, группа выходов которого является группой

информационных выходов устройства, отличающееся тем, что,с целью расширения функциональных возможностей за счет использования функционального преобразования чисел, в устройство введены блок памяти, третий счетчик и четвертый коммутатор, первый и второй управляющие входы которого являются первым и вторым управляющими входами устройства, первый и второй информационные входы четвертого, коммутатора соединены соответственно с выходами элемента НЕ и

первого ком гутатора, а выход - с вторым входом первого элемента И, выход .последнего элемента И первой группы,

J входы которого подключены к соответствующим выходам всех разрядов рекуррентного регистра сдвига, соединен со счетивп входом третьего счетчика, группа информацинных выходов которо10 го соединена с группой адресных входов блока памяти, группа информационных выходов которого соединена с группой информационных входов третьего коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Псевдостохастическое устройство для деления двоичных чисел | 1982 |

|

SU1040487A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU962931A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| Вероятностное устройство для выполнения математических операций | 1980 |

|

SU932494A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1980 |

|

SU940168A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Анализатор спектров | 1982 |

|

SU1023341A1 |

| Устройство для реализации быстрых преобразований | 1986 |

|

SU1416981A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

Изобретение относится к области вычислительной техники и может быть использовано в различных вычислительных устройствах и в стохастических вычислитет ьных машинах. Цель - расширение функциональных возможностей за счет использования функционального преобразования чисел. Дополнительно введенные блок памяти, третий счетчик и четвертый коммутатор, соединен-; ные определенным образом С остальными узлами схемы, позволяют расширить набор выполняемых математических операций вида функционального ;Преоб- разования чисел, например извлечения корня, вычисления логарифмов, тригонометрических функций и т.д., при сохранении быстродействия и точности. 1 ил. i (Л ts5 со со

Составитель В .Грее)енников Редактор И Никол-айчук Техред Л,ОлейникКорректор Е.Рошко

Заказ 2771/50 Тираж 671 , , , Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д,4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| Яковлев В,В., Федоров Р,Ф | |||

| Стохастические вычислительные машины,- Л.: Машиностроение, 1974 | |||

| Псевдостохастическое устройство для деления двоичных чисел | 1982 |

|

SU1040487A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-23—Публикация

1983-03-30—Подача