(54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

I ... ; -/fai il I

1 V r e--- fv . ,:

Для достижения поставленной цели АУ содержит блок ускоренного умножения, сдвитатель, регистр сдвигателя, коммутатор входа сдвигателя, узел управления савигателем, дешифраторы регистров основного сумматора, байтового сумматора и сдвигателя, входы которых подключены к выходам соответствующих регистров, а выходы подключены ко входам узла управления сдвигателем, выход которого подключен к управляющему входу сдвигателя, первый вход которого подключен к выходу коммутатора входа сдвигателя, входы которого соединены с выходами регистров первого и второго операндов и первого и второго регистров. Выход сдвигателя подключен ко входу регистра сдвигателя, выход которого подключен ко входам регистров первого и второго операндов и первого и второго регистров. Входы блока ускоренного умножения подключены к выходам регистров первого и второго операндов, а первый и второй выходы соединены с третьими входами коммутаторов соответственно первого и второго входов основного сумматора. Третий вход блока ускоренного умножения подключен ко второму входу сдвигателя.

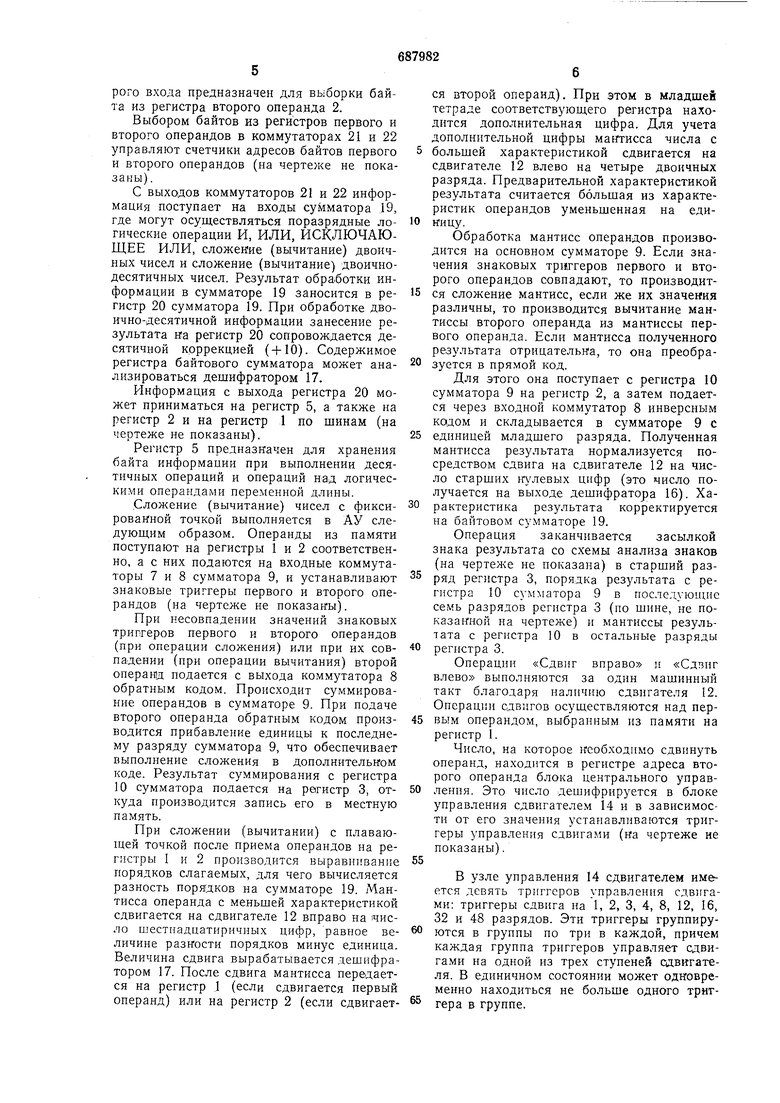

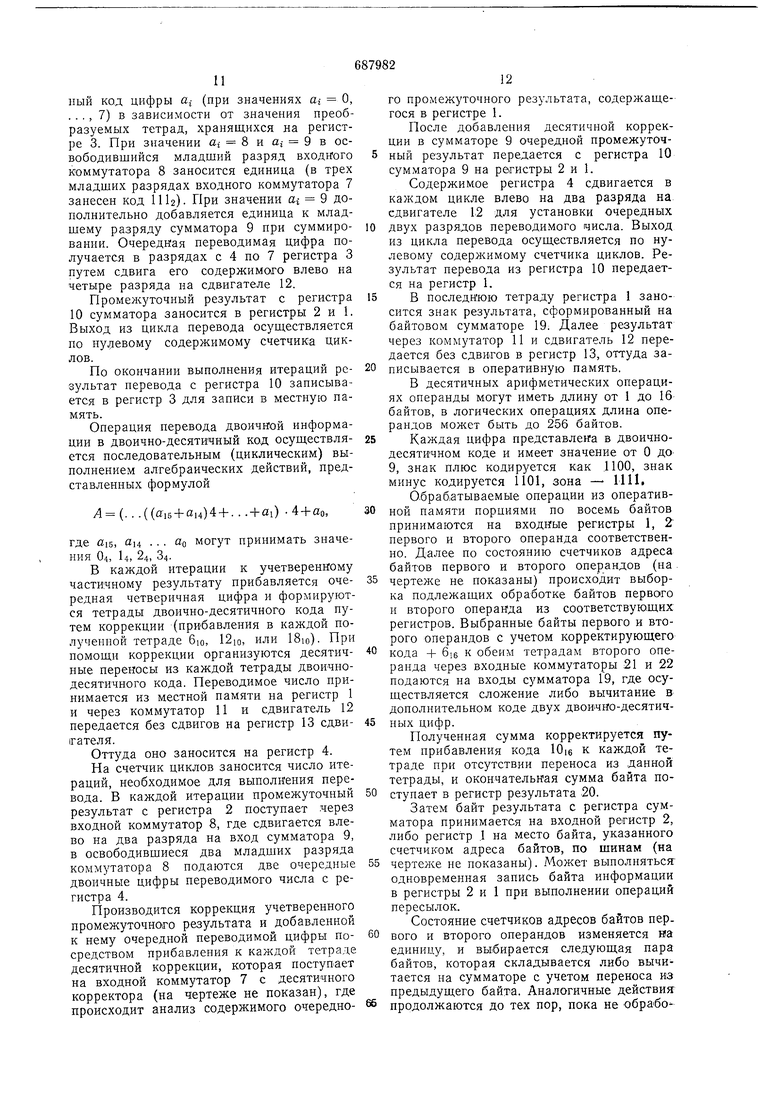

На чертеже представлена схема АУ.

Оно содержит регистр первого операнда 1, регистр второго операнда 2, первый, второй и третий регистры 3, 4, 5, блок ускоренного умножения 6, коммутатор 7 первого входа основного сумматора, коммутатор 8 второго входа основного сумматора, основной сумматор 9, регистр .10 основного сумматора, коммутатор 1,1 сдвигателя и сдвигатель 12, регистр 13 сдвигателя, узел управления 14 сдвигателем, входящий в состав блока 6, регистр младшей части произведения 15, дешифраторы регистров основного сумматора, байтового сумматора и сдвигателя 16, 17, 18, байтовый сумматор 19, регистр 20 байтового сумматора, коммутатор 21 первого входа байтового сумматора, коммутатор 22 второго входа байтового сумматора, входящие в состав блока 6 дешифратор мнол ителя 23, коммутатор кратных 24, дерево сумматоров 25 и дополнительный сумматор 26, входную шину 27 первого операнда, входную щину 28 второго операнда, шину связи 29 с оперативной памятью.

АУ позволяет выполнять полный набор команд ЕС ЭВМ, включая арифметические оперЗЦии над числами расширенного формата.

Информация в предлагаемом АУ обрабатывается следуюшнм образом.

Первый операн д принимается из местной или оперативной памяти на регистр 1, второй операнд - на регистр 2.

Для выполнения сложения (вычитания), сравнения поразрядных логических операций И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ операнды подаются на входные коммутаторы 7 и 8 сумматора 9. На коммутатор 8 возможен прием информации из регистров 2, 4 с выхода дерева сумматоров 25 блока ускоренного умножения 6. Через коммутатор 8 информация может передаваться прямым, обратным кодами и со сдвигами влево на один и два разряда.

На коммутатор 7 возможен прием информации из регистров I и 3 и с выхода

дерева сумматора 25 блока 6.

Через коммутатор 7 информация может передаваться прямым кодом и со сдвигом влево на один, два и три разряда, а также со сдвигом на три разряда вправо.

С выходов коммутаторов 7 и 8 информация поступает на входы сумматора 9, где производится ее обработка.

Результат обработки информации в сумматоре 9 заносится на регистр 10 сумматора 9. В случае необходимости производится анализ содержимого регистра сумматора 9 дешифратором 16.

Информация с выхода регистра 10 может приниматься на регистры 1-4. Для

выполнения сдвигов информация подается через входной коммутатор 11 на сдвигатель 12. На коммутатор И осуществляется прием информации с регистров 1-4. С выхода коммутатора 11 информация

поступает на вход сдвигателя 12, тде производятся ее сдвиги. Сдвиги могут производиться как вправо, так и влево, на величину от нуля до 63 разрядов за один такт. Число сдвигов может определяться

значением константы, находящейся в унравляющем слове микрокоманды, значением выхода дешифратора цифр частного (на чертеже не показан), значением выхода дешифратора 16, значением выхода дешифратора 17, значением выхода дешифратора 18. Информация, обработанная на сдвигателе 12, заносится в регистр 13 сдвигателя. Содержимое регистра сдвигателя может анализироваться дешифратором 18.

Информация с выхода регистра 13 сдвигателя может приниматься на регистры 1-4. Регистр 13 сдвигателя является также выходным регистром АУ, откуда производится запись информации в оперативную память по шине 29.

Для действия с порядками чисел с плаваюшей точкой и для побайтной обработки двоично-десятичных и логических операндов применяется сумматор 19.

Информация на первый и второй входы байтового сумматора 19 поступает соответственно через коммутаторы 21 и 22. Коммутатор 21 первого входа сумматора предназначен для выборки байта информации из регистра первого операнда I, для выборки байтовой информации из регистра 5, для коррекции +6 при сложении двоично-десятичных чисел, для преобразования информации в обратный код. Коммутатор 22 второго входа предназначен для выборки байта из регистра второго операнда 2.

Выбором байтов из регистров первого и второго операндов в коммутаторах 21 и 22 управляют счетчики адресов байтов первого и второго операндов (на чертеже не показаны).

С выходов коммутаторов 21 и 22 информация поступает на входы сумматора 19, где могут осуществляться поразрядные логические операции И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ, сложение (вычитание) двоичных чисел и сложение (вычитание) двоичнодесятичных чисел. Результат обработки информации в сумматоре 19 заносится в регистр 20 сумматора 19. При обработке двоично-десятичной информации занесение результата на регистр 20 сопровождается десятичной коррекцией (+10). Содержимое регистра байтового сумматора может анализироваться дешифратором 17.

Информация с выхода регистра 20 может приниматься на регистр 5, а также на регистр 2 и на регистр 1 по шинам (на чертеже не показаны).

Регистр 5 предназначен для хранения байта информации при выполнении десятичных операций и операций над логическими операндами переменной длины.

Сложение (вычитание) чисел с фиксированной точкой выполняется в АУ следующим образом. Операнды из памяти поступают на регистры 1 и 2 соответственно, а с них подаются на входные коммутатор з1 7 и 8 сумматора 9, и устанавливают знаковые триггеры первого и второго операндов (на чертеже не показаны).

При несовпадении значений знаковых триггеров первого и второго операндов (при операции сложения) или при их совпадении (при операции вычитания) второй операнд подается с выхода коммутатора 8 обратным кодом. Происходит суммирование операндов в сумматоре 9. При подаче второго операнда обратным кодом производится прибавление единицы к последнему разряду сумматора 9, что обеспечивает выполнение сложения в дополнительном коде. Результат суммирования с регистра 10 сумматора подается на регистр 3, откуда производится запись его в местную память.

При сложении (вычитании) с плавающей точкой после приема операндов на регистры 1 и 2 производится выравнивание порядков слагаемых, для чего вычисляется разность порядков на сумматоре 19. Мантисса операнда с меньшей характеристикой сдвигается на сдвигателе 12 вправо на число шестнадцатиричных цифр, равное величине разности порядков минус единица. Величина сдвига вырабатывается дешифратором 17. После сдвига мантисса передается на регистр 1 (если сдвигается первый операнд) или на регистр 2 (если сдвигается второй операнд). При этом в младшей тетраде соответствующего регистра находится дополнительная цифра. Для учета дополнительной цифры мантисса числа с большей характеристикой сдвигается на сдвигателе 12 влево на четыре двоичных разряда. Предварительной характеристикой результата считается большая из характеристик операндов уменьшенная на единицу.

Обработка мантисс операндов производится на основном сумматоре 9. Если значения знаковых триггеров первого и второго операндов совпадают, то производится сложение мантисс, если же их значения различны, то производится вычитание мантиссы второго операнда из мантиссы первого операнда. Если мантисса полученного результата отрицательна, то она преобразуется в прямой код.

Для этого она поступает с регистра 10 сумматора 9 на регистр 2, а затем подается через входной коммутатор 8 инверсным кодом и складывается в сумматоре 9 с единицей младшего разряда. Полученная мантисса результата нормализуется посредством сдвига на сдвигателе 12 на число старших нулевых цифр (это число получается на выходе дещифратора 16). Характеристика результата корректируется на байтовом сумматоре 19.

Операция заканчивается засылкой знака результата со схемы анализа знаков (на чертеже не показана) в старший разряд регистра 3, порядка результата с регистра 10 сумматора 9 в последуюи1,ие семь разрядов регистра 3 (по шине, не показанной на чертеже) и мантиссы результата с регистра 10 в остальные разряды регистра 3.

Операции «Сдвиг вправо и «Сдвиг влево выиолняются за один машинный такт благодаря наличию сдвигателя 12. Операции сдвигов осушествляются над первьш операндом, выбранным из памяти на регистр 1.

Число, на которое необходимо сдвинуть операнд, находится в регистре адреса второго операнда блока центрального управления. Это число дешифрируется в блоке управления сдвигателем 14 и в зависимости от его значения устанавливаются триггеры управления сдвигами (на чертеже не показаны).

В узле управления 14 сдвигателем имеется девять триггеров уиравления сдвигами: триггеры сдвига на 1, 2, 3, 4, 8, 12, 16, 32 и 48 разрядов. Эти триггеры группируются в группы по три в каждой, иричем каждая группа триггеров управляет сдвигами на одной из трех ступеней савигателя. В единичном состоянии может одновременно находиться не больше одного трнггера в группе.

Таким управлением обеспечивается выполнение сдвига информации на число разрядов от О до 63. Сдвиг влево выполняется при помощи «перекрестной передачи информации через входной коммутатор И сдвигателя, сдвига вправо на необходимое число разрядов на сдвигателе 12 и обратной «перекрестной передачи через входную логику при приеме информации на регистр 13 сдвигателя. С этого регистра результат поступает на регистр 3 для записи в местную память.

Логические операции И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ выполняются на основном сумматоре 9, где кроме сложения операндов предусмотрено выполнение выше перечисленных логических функций.

Результат с регистра 10 основного сумматора поступает на регистр 3.

Для выполнения операций умножения применяется блок ускоренного умножеяия 6.

Умножение производится младшими разрядами вперед одновременно на 12 разрядов с запоминанием переноса из предыдущих 12 разрядов множителя. Анализ очередных 12 разрядов множителя находящегося на регистре второго операнда 2 производится в дешифраторе множителя 23, затем в коммутаторе кратных 24 происходит формирование шести кратных множимому. Полученные кратные, являющиеся произведениями множимого на соответствующие пары разрядов множителя, суммируются в двухрядном коде на дереве сумматоров 25. На выходах дерева сумматоров получается частичное произведение в двухрядном коде. Полученное частичное произведение, сдвинутое на сдвиговых цепях дерева на 12 разрядов вправо, добавляется к новому частичному произведению на стадии его формирования. Применение «конвейерного метода обработки информации позволяет совмещать во времени выполнение итераций умнол ;ения. Последовательностью выполнения итераций управляет счетчик итераций (на чертел-се не показан).

При умножении чисел с плавающей запятой перед выполнением итераций умножения производится (в случае необходимости) нормализация сомножителей путем сдвига их мантисс влево на сдвигателе 12 на число старших шестнадцатиричных нулей, вырабатываемых дешифратором 16, который представляет собой дешифратор пулевых шестнадцатиричных цифр. Производится также коррекция промежуточной характеристики результата (сумма характеристик сомножителей - 64) путем вы|1итания из нее на сумматоре 19 числа левых сдвигов мантисс множимого и множителя. По окончании выполнения итераций умножения на блоке 6 результат умножения в двухрядном коде подается с выходов дерева сумматора 25 через входные коммутаторы 7 и 8 на входы сумматора 9, где производится приведение переносов.

При умножении чисел с фиксированной точкой результат, полученный на регистре 10 основного сумматора, заносится на регистр 3 для записи в местную память.

При умножении чисел с плавающей точкой полученная мантисса результата подвергается (в случае необходимости) остаточной нормализации посредством сдвига ее влево на сдвигателе 12 на четыре двоичных разряда и коррекции характеристики результата (вычитания из нее на сумматоре 19 единицы). После нормализации мантисса и характеристика результата заносятся на регистр 3 для записи в местную память.

В операциях умножения чисел с плавающей точкой и результатом расширенного формата (длина мантиссы 128 двоичных разрядов) для формирования младшей части результата используется дополнительный сумматор 26.

В каждой итерации после получения частичного произведения на выходе дерева сумматоров 25 и сдвига его на 12 разрядов вправо три выдвинутые тетрады в двухрядном коде поступают на входы дополнительного сумматора 26, где происходит приведение переносов. Полученные три шестнадцатиричные цифры записываются под управлением счетчика итераций в соответствующие разряды регистра младшей части произведения. По окончании выполнения итераций умножения на -блоке 6, полученная на регистре 15 младшая часть мантиссы произведения подается на вход сдвигателя 12, где производятся необходимые для остаточной нормализации результата сдвиги. Нормализованная младшая часть мантиссы результата заносится в регистр 3. В старший байт регистра 3 заносится характеристика младшей части реззльтата. Затем производится запись младшей части результата в местную память. В предлагаемом АУ предусмотрена возможность выполнения умножения без блока ускоренного умножения с использованием основного сумматора 9. Умножение осуществляется младшими разрядами вперед одновременно на три разряда без анализа четвертого с предварительным формированием утроенного множимого, которое хранится в регистре 3.

В АУ применяется метод деления без восстановления остатка с анализом четырех старших разрядов очередного остатка. Перед началом выполнения итераций деления производится нормализация делителя: сначала шестнадцатиричная (число левых сдвигов кратно четырем и определяется значением выхода дешифратора 16), а затем двоичная (число левых сдвигов определяется значением выхода дешифратора

9

18,который представляет собой дешифратор нулевых разрядов сдвигателя). Общее

число сдвигов вычисляется на сумматоре

19,и производится нормализация делимого путем сдвига его влево иа сдвигателе 12 на общее число левых сдвигов делителя.

В случае деления с плавающей точкой предварительно производится независимая шестнадцатиричная нормализация делимого и делителя, после чего производится двоичная нормализация делителя, и в соответствии с числом левых сдвигов делителя производится двоичная нормализация .делимого. Чтобы при делении с плавающей точкой использовать те же управляю10

щие цепи, что и при делении с фиксированной точкой, необходимо дополнительно сдвинуть мантиссы делимого и делителя влево на семь двоичных разрядов.

Нормализованный делитель помещается в регистр 2, а нормализованное делимое - в регистр 1.

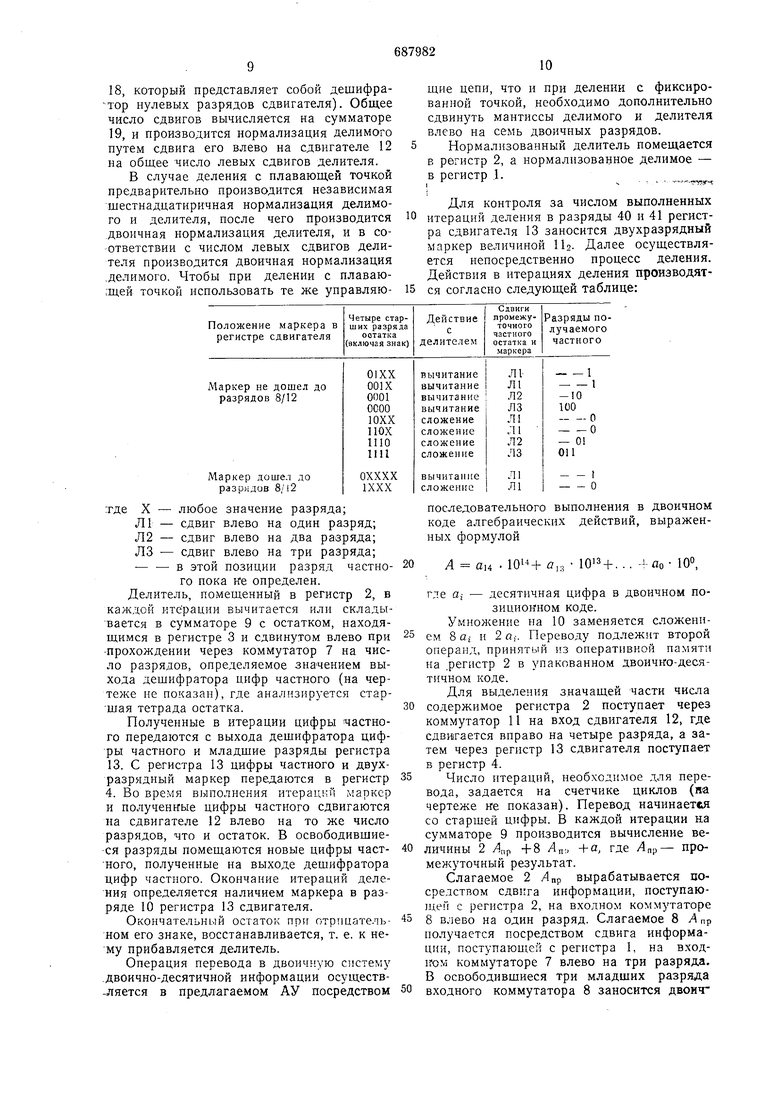

Для контроля за числом выполненных итераций деления в разряды 40 и 41 регистра сдвигателя 13 заносится двухразрядный маркер величиной Ib. Далее осуществляется непосредственно процесс деления. Действия в итерациях деления производятся согласно следующей таблице:

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Арифметическое устройство с фиксированной точкой | 1984 |

|

SU1241230A1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Устройство для умножения | 1977 |

|

SU695364A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

тде X - любое значение разряда; Л1 - сдвиг влево на один разряд; Л2 - сдвиг влево на два разряда; ЛЗ - сдвиг влево на три разряда; - - в этой позиции разряд частного пока ке определен. Делитель, помещенный в регистр 2, в каждой итерации вычитается или складывается в сумматоре 9 с остатком, находящимся в регистре 3 и сдвинутом влево при прохождении через коммутатор 7 на число разрядов, определяемое значением выхода дешифратора цифр частного (на чертеже пе показан), где анализируется старшая тетрада остатка. Полученные в итерации цифры частного передаются с выхода дешифратора цифры частного и младшие разряды регистра 13. С регистра 13 цифры частного и двухразрядный маркер передаются в регистр 4. Во время выполнения итераций маркер и полученные цифры частного сдвигаются на сдвигателе 12 влево на то же число разрядов, что и остаток. В освободившиеся разряды помещаются новые цифры частного, полученные на выходе дешифратора цифр частного. Окончание итераций деления определяется наличием маркера в разряде 10 регистра 13 сдвигателя. Окончательный остаток при отрицательном его знаке, восстанавливается, т. е. к нему прибавляется делитель. Операция перевода в двоичную систему .двоично-десятичной информации осуществ-ляется в предлагаемом АУ посредством последовательного выполнения в двоичном коде алгебраических действий, выраженных формулой Л ai4 . fl,3 10з + ... 10°, гле и; - десятичная цифра в двоичном позиционном коде. Умножение на 10 заменяется сложением 8 Qj и 2 и,-. Переводу подлежит второй операнд, принятый из оперативной памяти на .регистр 2 в упакованном двоично-десятичном коде. Для выделения значащей части числа содержимое регистра 2 поступает через коммутатор 11 на вход сдвигателя 12, где сдвигается вправо на четыре разряда, а затем через регистр 13 сдвигателя поступает в регистр 4. Число итераций, необходимое для перевода, задается на счетчике циклов (на чертеже не показан). Перевод начинается со старшей цифры. В каждой итерации на сумматоре 9 производится вычисление величины 2 Лр +8 Лп;, +а, где А„р- промежуточный результат. Слагаемое 2 Лдр вырабатывается посредством сдвига информации, поступаюи.;еГ| с регистра 2, на входном коммутаторе 8 влево на один разряд. Слагаемое 8 Лпр получается посредством сдвига информации, поступающей с регистра 1, на вход1 ом коммутаторе 7 влево на три разряда, В освободившиеся три младших разряда входного коммутатора 8 заносится двоич

11

иый код цифры ttj (при значениях а, О, . . . , 7) в зависимости от значения преобразуемых тетрад, хранящихся на регистре 3. При значении uj 8 и oii 9 в освободившийся младший разряд входного коммутатора 8 заносится единица (в трех младших разрядах входного коммутатора 7 занесен код ПЬ). При значении а; 9 дополнительно добавляется единица к младшему разряду сумматора 9 при суммировании. Очередная переводимая цифра получается в разрядах с 4 по 7 регистра 3 путем сдвига его содержимого влево на четыре разряда на сдвигателе 12.

Промел.уточный результат с регистра 10 сумматора заносится в регистры 2 и 1. Выход из цикла перевода осуществляется по нулевому содержимому счетчика циклов.

По окончании выполнения итераций результат перевода с регистра 10 записывается в регистр 3 для записи в местную память.

Операция перевода двоичной информации в двоично-десятичный код осуществляется последовательным (циклическим) выполнением алгебраических действий, представленных формулой

А(. . .((ai5-bai4)4 + . . . + ai) 4-f «о,

где «15, GU ... GO могут принимать значения 04, Ц, 24, 84.

В каждой итерации к учетверенному частичному результату прибавляется очередная четверичная цифра и формируются тетрады двоично-десятичного кода путем коррекции (прибавления в каждой полученпой тетраде бю, 12io, или 18io). При помощи коррекции организуются десятичные переносы из каждой тетрады двоичнодесятичного кода. Переводимое число иринимается из местной памяти на регистр 1 и через коммутатор И и сдвигатель 12 передается без сдвигов на регистр 13 сдвигателя.

Оттуда оно заносится на регистр 4.

На счетчик циклов заносится число итераций, необходимое для выполнения перевода. В каждой итерации промежуточный результат с регистра 2 поступает через входной коммутатор 8, где сдвигается влево на два разряда на вход сумматора 9, в освободивщиеся два младших разряда коммутатора 8 подаются две очередные двоичные цифры переводимого числа с регистра 4.

Производится коррекция учетверенного промежуточного результата и добавленной к нему очередной переводимой цифры посредством прибавления к каждой тетраде десятичной коррекции, которая поступает на входной коммутатор 7 с десятичного корректора (на чертеже не показан), где происходит анализ содержимого очередно12

го промежуточного результата, содержащегося в регистре 1.

После добавления десятичной коррекции в сумматоре 9 очередной промежуточ5 ный результат передается с регистра 10 сумматора 9 на регистры 2 и 1.

Содержимое регистра 4 сдвигается в каждом цикле влево на два разряда на сдвигателе 12 для установки очередных

10 двух разрядов переводимого числа. Выход из цикла перевода осуществляется по нулевому содержимому счетчика циклов. Результат перевода из регистра 10 передается на регистр 1.

15 В последнюю тетраду регистра 1 заносится знак результата, сформированный на байтовом сумматоре 19. Далее результат через коммутатор 11 и сдвигатель 12 передается без сдвигов в регистр 13, оттуда за0 писывается в оперативную память.

В десятичных арифметических операциях операнды могут иметь длину от 1 до 16 байтов, в логических операциях длина операндов может быть до 256 байтов.

5 Каждая цифра представлена в двоичнодесятичном коде и имеет значение от О до9, знак плюс кодируется как 1100, знак минус кодируется 1101, зона - 1111. Обрабатываемые операции из оперативной памяти порциями по восемь байтов принимаются на входные регистры 1, 2 первого и второго операнда соответственно. Далее по состоянию счетчиков адреса байтов первого и второго операндов (на

5 чертел :е не показаны) происходит выборка подлежащих обработке байтов первого и второго операнда из соответствующих регистров. Выбранные байты первого и второго операндов с учетом корректирующего

кода + 6i6 к обеим тетрадам второго операнда через входные коммутаторы 21 и 22 подаются на входы сумматора 19, где осуществляется сложение либо вычитание в дополнительном коде двух двоично-десятич5 ных цифр.

Полученная сумма корректируется путем прибавления кода lOie к каждой тетраде при отсутствии переноса из данной тетрады, и окончательная сумма байта по0 ступает в регистр результата 20.

Затем байт результата с регистра сумматора принимается на входной регистр 2, либо регистр 1 на место байта, указанного счетчиком адреса байтов, по шинам (на

5 чертеже не показаны). Может выполняться: одновременная запись байта информации в регистры 2 и 1 при выполнении операций пересылок.

Состояние счетчиков адресов байтов пер.

0 вого и второго опер андов изменяется на единицу, и выбирается следующая пара байтов, которая складывается либо вычитается на сумматоре с учетом переноса из предыдущего байта. Аналогичные действия продолжаются до тех пор, пока не обработаются все байты операндов. Результат суммирования (вычитания) с регистра 1 пересылается через сдвигатель 12 в оперативную память.

При выполнении операции УМНОЖЕНИЕ ДЕСЯТИЧНОЕ сомножители принимаются в регистры 1, 2. Затем второй операнд, находящийся в регистре 2, сдвигаетСя вправо на 4 разряда, тем самым выдвигается знак, и в старшем байте формируются дополнительные разряды.

Умножение начинается с умножения второго операнда на младшие байты первого операнда: сначала на правую цифру, а затем на левую цифру, которые хранятся в регистре 5 (в знаковом байте умножение выполняется на одну цифру, и происходит формирование знака по правилам алгебры) . Промежуточные произведения, полученные при умножении на каждую цифру, накапливаются в регистре 1, сдвигаются вправо на четыре разряда на сдвигателе 12, и младший байт произведения отсылается из регистра 13 в оперативную память на место соответствующего байта первого операнда. Промежуточное произведение также временно запоминается в регистре 3, а в регистр 1 принимается из оперативной памяти следующий байт первого операнда, на который будет продолжено умножение. Затем этот байт пересылается в регистр 5.

Затем циклы умножения повторяются. При умножении на каждую цифру первого операнда производится анализ этой цифры на дешифраторе 17.

Если анализируемая цифра множителя равна нулю или десяти, то частичное произведение сдвигается вправо на четыре разряда без прибавления множимого. При равенСтве цифры множителя десяти прибавляется елТ.иница к следующей цифре множителя.

Если значение цифры множителя находится в пределах от единицы до пяти, то множимое прибавляется к частичному произведению число раз, равное значению цифры множителя.

Если цифра множителя больше пяти, но меньше десяти, то множимое вычитается из частичного произведения число раз, равное дополнению цифры множителя до десяти. При этом к следующей цифре множителя прибавляется единица.

Цифры множителя хранятся в регистре 5, а при каждом прибавлении, либо вычитании множимого из частичного произведения происходит уменьшение, либо увеличение цифры множителя на единицу. Когда цифра множителя уменьшится до нуля нли увеличится до девяти, умножение на данную цифру закончится.

После каждого умножения на две цифры (байт) вычитается единица из длины первого операнда. Умножение заканчивается как только длина первого операнда станет равна длнне второго операнда.

Таким о.бразом, введение в АУ блока универсального сдвигателя позволяет выполпять операции сдвигов за 160 не (независимо от числа сдвигов) в то время, как в прототипе время выполнения операций сдвигов занимать до 1,8 мкс и зависит от числа сдвигов. Использование сдвпгателя позволяет также значительно ускорить выполнение операций как с фиксированной точкой, так и с плавающей точкой. Так в операции умножения с фиксированной точкой при сокращенин количества итераций умножения, в случае равенства 15-ти старших разрядов множителя знаковому разряду, производится сдвиг полученного произведения на 15 разрядов вправо за один машинный такт (160 нсек). В операции деления с фиксированной точкой при приведении делителя к нормализованному виду также используются возможности сдвигателя для сдвига делителя на количество нулевых разрядов в делителе за один машинный такт. Время выполнения операций сложення, умножения, деления с плавающей точкой сокращается за счет сдвига мантисс за один машинный такт при нормализации операндов и результата.

Введение блока ускоренного умножения п оптимальная организация связи его с остальным оборудованием АУ позволяет выполнять операцию умножения в 3,5- 4 раза быстрее, чем в прототипе. Применение блока ускоренного умножения позволяет также выполнять операцию умножения . с расширенным результатом (длина мантиссы - 128 двоичных разрядов).

Формула изобретения

Арифметическое устройство, содержаuiee регистры первого и второго операндов, первый, второй и третий регистры, основной сумматор, байтовый сумматор, коммутаторы первого и второго входов основного сумматора, коммутаторы первого и второго входов байтового сумматора, регистры основного и байтового сумматоров, причем выходы коммутаторов первого и второго входов основного сумматора соединены с соответствующими входами основного сумматора, выход которого подключен ко входу регистра основного сумматора, выход которого соединен со входами регистров первого и второго операндов и первого и второго регистров, другие входы регистров первого и второго операндов соединены со входами устройства, первые и вторые входы коммутаторов первого н второго входов основного сумматора подключены к выходам соответственно регистра первого операнда и первого регистра и регистра второго операнда и второго регистра, выходы коммутаторов первого и второго входов

15

байтового сумматора подключены к соответствующим входам байтового сумматора, выход которого подключен ко входу реГистра байтового сумматора, выход которого соединен со входом третьего регистра, входы коммутатора первого входа байтового сумматора подключены к выходам регистра первого операнда и третьего регистра, вход коммутатора второго входа байтового сумматора соединен с выходом регистра второго операнда, отлич ающ е е с я тем, что, с целью повышения быстродействия, устройство содержит блок ускоренного умножения, одвигатель, регистр сдвигателя, коммутатор входа сдвигателя, узел управления сдвигателем и дешифраторы регистров основного сумматора, байтового сумм-атора и сдвигателя, входы которых подключены к выходам соответствуюш,их регистров, ,а выходы подключены ко входам узла управления сдвигателем, выход которого подключен к управляющему входу сдвигателя, первый

1C

вход которого подключен к выходу коммутатора входа сдвигателя, входы которогосоединены с выходами регистров первого и второго операндов и первого и второго регистров, выход сдвигателя подключен ко входу регистра сдвигателя, выход которого подключен ко входам регистров первого и второго операндов и первого и второго регистров, входы блока ускоренного умножения подключены к выходам регистров первого и второго операндов, а первый и вто- рой выходы соединены с третьими входами коммутаторов соответственно первого и второго входов основного сумматора, третий выход блока ускоренного умножения подключен ко второму входу сдвигателя.

Источники информации, принятые вовнимание при экспертизе:

Авторы

Даты

1982-01-07—Публикация

1978-01-03—Подача