Изобретение относится к области вычислительной техники, может быть использоваио, в частности, для аппаратной реализации оиерадии деления в специализированных цифровых вычислительных машинах, работающих в двоичной системе счнсленпя с фиксированной запятой.

По основному авт. св. Х 497585 известно двоичное устройство деления, состоящее из двух одноразрядных сумматоров-вычитателей, двух иакопительных сдвиговых регистров, рециркуляционного сдвигового регистра, блока формирования констаит, блока анализа знака исевдочастиого, блока анализа сходимости ироцесса, блока сброса и блока управления, причем выход блока анализа знака псевдочастиого соединен с иервыми выходами первого и второго сул маторов-вычитателей, выходы которых подключены соответственно к ииформационным входам накопительных сдвиговых регистров, управляющие входы которых связаны соответственно с нервым и вторым выходами блока управления, причем выходы накопительных сдвиговых регистров соединены соответственно с вторыми входами сум.маторов-вычитателей, а выход знакового разряда второго накопительного сдвигового регистра подключен к входу блэка анализа знака псевдочастного. Вход блока анализа сходимости процесса

соединен с дополнительным выходом второго накопительного сдвигового регистра, а выход - с входом блока сброса, выход которого связан с входом блока унравлення, первый и второй дополнительные выходы которого соединены соответственно с входами блока формирования констант и рециркуляционного сдвигового регистра, выходы которых иодключены соответственно к третьим входам сумматоров-вычитателей 1.

Однако это устройство предназначено только для деления двух двоичиых чисел при условии, что делитель У больше делимого X, это сужает интервалы изменения аргументов

(операндов).

Цель изобретения - расширение интервалов изменения каладого аргумента до любой величины ,0, представленной в двоичной форме с фиксированной запятой,

т. е. расширеиие класса задач, решаемых устройством.

Поставленная цель достигается тем, что в двоичное устройство деления дополнительно введен блок анализа соотношения между делимым и делителем, первый вход которого соединен с выходом блока анализа знака нсевдочастного, второй вход - с третьим выходом блока управления, а выход соедииен с вторым входом блока управления.

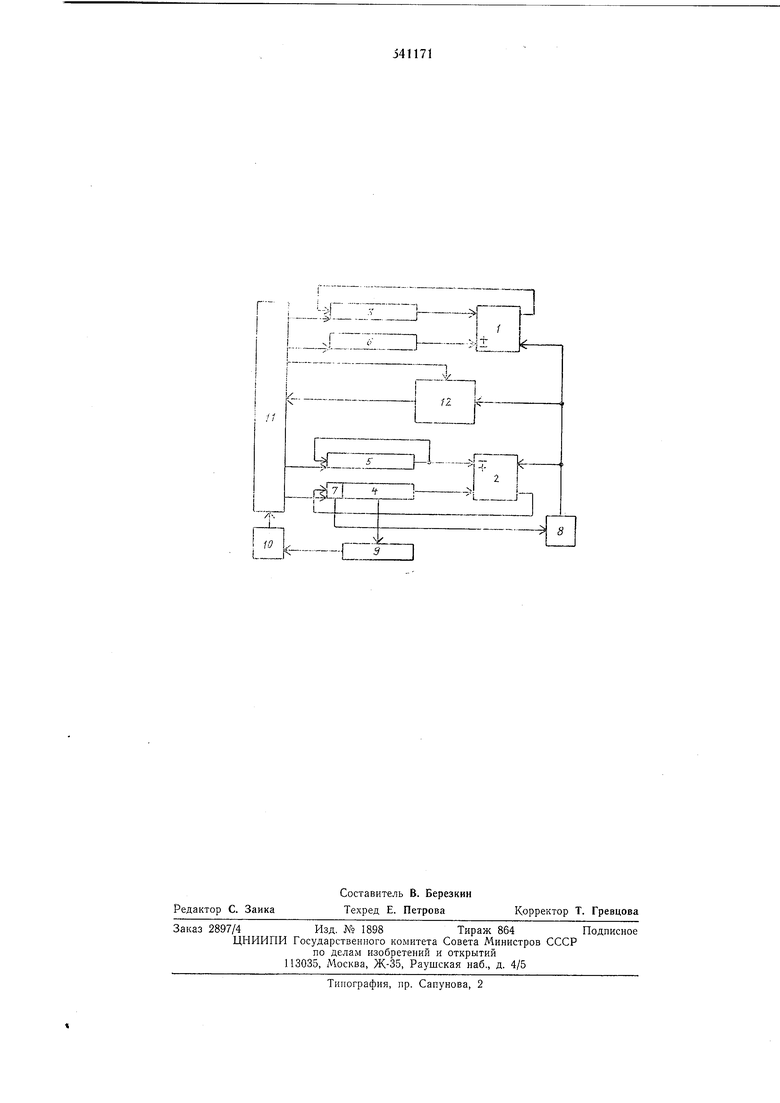

Логический блок анализирует соотношеыия 1между делимым и делителем в каждой итерации и обеспечивает иовторение итерации с /-М иоказателем необходимое число раз. На чертеже изображена блок-схема двоичного устройства деления. Двоичное устройство деления содержит одиоразрядные сумматоры-вычитатели 1 и 2 комбинационного тина, накоиительные сдвиговые регистры 3 и 4, рециркуляционный сдвиговый регистр 5 (вход и выход которого соединены между собой), блок 6 формирования констант вида , знаковый разряд 7 иакоиительиого сдвигового регистра 4, блок 8 анализа знака псевдочастиого, блок 9 анализа сходимости процесса, блок 10 сброса, блок И управления и блок 12 анализа соотиощения делимым и делителем. Выход блока 8 анализа знака псевдочастного соединен с первыми (управляющими) входами сумматоров-вычитателей 1 и 2 и с иервым входом блока 12 анализа соотношеиия делимым и делителем. Выход первого накопительного сдвигового регистра 3 соединен с вторым входом сумматора-вычитателя 1, выход которого соединен с информациоиньш входом нервого накоиительного сдвигового регистра 3. Выход второго накопительного сдвигового регистра 4 соединен с вторым входом сумматора-вычитателя 2, выход которого соединен с информациоииым входом второго накопительного сдвигового регистра 4. Выход знакового разряда 7 этого регистра соединен с входом блока 8 анализа знака псевдочастного. Дополнительный выход второго накопительного сдвигового регистра 4 соединен с входом блока 9 анализа сходимости процесса, выход которого через блок 10 сброса соединен с первым входОМ блока 11 управления. Выход блока 6 формирования констант соединен с третьим (унравляемым) входом сумматора-вычитателя 1. Выход рециркуляционного сдвигового регистра 5 соединен с третьим (управляемым) входом сумматор-вычитателя 2. Первый выход блока И управления соеди нен с унравляющнм входом накопительного сдвигового регистра 3, первый дополнительный выход блока 11 управления - с входом блока 6 формирования констант. Второй выход блока 11 управления соединен с управляющим входом наконительного сдвнгового регистра 4, второй дополнительный выход блока 11 управления - с управляющим входом рециркуляционного сдвигового регистра 5. Третий выход блока 11 управления соединен с вторым входом блОКа 12 анализа соотнощения между делимым и делителем, выход которого соединен с вторым входом блока 11 управления. Блок 6 формирования констант может быть выполнен в виде логического автомата или одиостороннего заноминающего устройства с поразрядной выборкой очередной константы 2 каждым тактовым сдвигающим импульсом. Блок 8 анализа знака исевдочастотного выиолнен, иаиример, в виде триггера с логическими элементами. Блок 9 анализа сходимости процесса представляет собой цифровую схему сравнения кода с логическим иулем. Блок 10 сброса содерл ит триггер с логическими эле.ментами. Блок 11 зиравления состоит из генератора тактовых сдвигающих имнульсов, счетчиков, дещифратора, логических элемеитов. Блок анализа соотнощения между делимым и делителем 12 содержит, иаиример, триггеры, логические элементы и т. и. Входом двоичного устройства деления являются входы разрядов второго накопительного сдвигового регистра 4 для делимого X и входы разрядов рециркуляционного сдвигового регистра 5 для делителя У. Выходом устройства являются выходы разрядов первого накопительного сдвигового регистра 3. Процесс операции деления основан на нрииципе псевдоделеиия и псевдоумножеиия в итерациоином процессе, который описывается разностно-итерационным алгоритмом из системы рекурреитных соотнощений Ао.о X Xj.i : I ш X-j I - qiY2-J Хп, k . .,{ +1, при Xj i гО (/, Slgn.Y/ г : -1, ,,0 .0,0 о f+i J Zn, k где / 0, 1, n является показателем итерации;k является порядковым но , мером итерации; п - число разрядов аргумента. При помощи операции псевдоделения (первое рекурреитиое соотнощеиие алгоритма) в каждой итерации определяется очередная (для следующей итерации) цифра псевдочастного qi и при помощи оиерации псевдоумножения (второе рекуррентное соотнощение) преобразуется в очередное приближение частного в двоичной системе счисления. Операции нсевдоделения и псевдоумножеиия выполняются при помощи элементарных деиствнй сложения - вычитания и сдвига. Цикл вычисления состоит из k итераций. Каждая итерация включает в себя параллельное вычисление рекуррентных соотнощеиий, но каждое из которых вычисляется иоследовательным путем за я + т+1 тактов, где т-число дополнительных разрядов для компенсации погрещности усечения при сдвиге, а одик такт необходим для сдвига значения делителя У в каждой итерации. Двоичное устройство деления работает следующим образом. Первоиачальио в первом накопительном сдвиговом регистре 3 устанавливается нулевое значение, во второй накопительный сдвиговый регистр 4 в параллельном виде заносится значение делимого X, а в рециркуляционный сдвиговый регистр 5 заносится в параллельном коде значение делителя Y. В любой итерации с первых двух выходов блока 11 управления выдается цоследовательность (серия) тактовых сдвигающих импульсов для сдвига и продвижения содержания рециркуляционного регистра 5 и продвижения содержания накопительных сдвиговых регистров 3 и 4 в сумматор-вычитатели 1 и 2, а также для выборки очередной константы из блока 6 формирования констант. Результат итерации поразрядно заносится младшими разрядами вперед с выхода сумматоров-вычитателей 1 и 2 в освобождающейеся при сдвиге (продвижении) старщие разряды накопительных сдвиговых регистров 3 и 4 соответственно и продвигаются в сторону младших разрядов (к началу этих регистров), аналогично переписывается содержание рециркуляционного сдвигового регистра 5. В зависимости от значения знака содержания второго накопительного сдвигового регистра 4 блок 8 анализа знака псевдочастного вырабатывает сигнал управления (очередпую цифру нсевдочастного). При положительном знаке содержания второго накопительного сдвигового регистра 4 очередная цифра псевдочастного равна плюс единице, и сумматор-вычитатель 1 работает в режиме суммирования, а сумматорвычитатель 2-в режиме вычитания. При отрицательном знаке содержания очередная цифра псевдочастного равна минус единице, сумматор-вычитатель 1 работает в режиме вычитания, а сумматор-вычитатель 2-в режиме сложения. Вычитание производится при помощи дополнения. Блок анализа соотношения между делимым и делителем 12 производит проверку выполнения условий j, г У-2-J путем анализа изменения знака очередной цифры псевдочастного. В случае выполнения условия (цифра псевдочастного остается прежней) величина показателя / на следующей итерации не изменяется. При .-Y-Z-i, т. е. при перемене знака цифры псевдочастного происходит изменение величины показателя итерации на единицу. Таким образом, значение делимого У, сдвинутое на , вычитается из содержания второго накопительного сдвигового регистра 4 в сумматоре-вычитателе 2, а константа 2-J суммируется с содержанием первого накопительного сдвигового регистра 3 в сумматоревычитателе 1 до тех пор, пока содержание второго накопительного сдвигового регистра 4 не станет отрицательным. В конце цикла операции деления в первом накопительном сдвиговом регистре 3 находится частное от деления X на Y, а содержание второго накопительного сдвигового регистра 4 равно нулю. Для подавляющего больщинства значений аргументов (делимого и делителя) итерационный процесс вычисления сходится на итерации, порядковый номер которой меньше величины п+. В этом случае во втором накопительном сдвиговом регистре 4 содержание равно нулю, блок 9 анализа сходимости процесса, который сравнивает содержание накопительного сдвигового регистра 4 с логическим нулем, выдает сигнал останова процесса вычисления. Сигнал запоминается в блоке 10 сброса, который выдает команду в блок 11 управления прекратить выдачу тактовых сдвигающих импульсов на следующей итерации. Благодаря асинхронному режиму работы двоичного устройства деления быстродействие из-за повторения ряда итераций понижается незначительно для деления двух двоичных чисел, представленных в форме с фиксированной запятой с интервалом изменения каждого из аргументов от нуля до единицы. Двоичное устройство деления с унифицированнойпараллельно-последовательнойструктурой состоит из простых стандартных цифровых схем и элементов и может быть изготовлено при помощи интегральной технологии с высокой степенью итерации. Устройство совмещает требования надежности, быстродействия, точности, технологичности и унификации, а также определяет оптимальное использование аппаратуры. Использование устройства целесообразно в качестве специализированного вычислительного блока для выполнения операции деления в реальном масштабе времени или при большой частоте обращения к этой операции в управляющих системах и в настольных вычислителях. Формула изобретения Двоичное устройство деления но авт. св. № 497585, отличающееся тем, что, с целью расширения класса решаемых задач, в него введен блок анализа соотношения между делимым и делителем, первый вход которого соединен с выходом блока анализа знака псевдочастного, второй вход-с третьим выходом блока управления, а выход соединен с вторыл входом блока управления. Источники информации, принятые во внимание при экспертизе: 1. Авт. св. № 497585, кл. G 06F 7/39, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичное устройство деления | 1974 |

|

SU497585A1 |

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

| Устройство для вычисления тригонометрического тангенса | 1973 |

|

SU537344A1 |

| Устройство для вычисления кубического корня | 1973 |

|

SU516037A1 |

| Устройство для вычисления гиперболического тангенса | 1973 |

|

SU526890A1 |

| Устройство для умножения | 1975 |

|

SU579615A1 |

| Устройство для вычисления экспоненциальной функции | 1973 |

|

SU538366A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1973 |

|

SU536490A1 |

| Устройство для вычисления обратного гиперболического тангенса | 1973 |

|

SU465630A1 |

| Устройство для формирования гиперболических функций | 1973 |

|

SU484522A1 |

Авторы

Даты

1976-12-30—Публикация

1975-08-18—Подача