Изобретение относится кэлектронной технике, в частности к техноло- гии энергонезависимых, электрически перепрограммируемых интегральных схем памяти, на основе МНОП-транзисторов.

При проектировании и изготовлении полупроводниковых постоянных запоминающих устройств необходимо последовательно решать две задачи; создание отдельных, составляющих РОЙСТВО, ячеек памяти, а такл{е компоновка ячеек в интегральную матрицу-накопитель.

Известен способ изготозления отдельных ячеек памяти на основе транзисторов со структурой металл-нит.рид кремния-двуокись кремния - кремо

ний (МНОП), запись информации в которых осуществляется путем захвата

о ю в двухслойном диэлектрике носителей заряда, инжектированных из металла или кремния при приложении между ними электрического поля. Под действи00ем захваченного в диэлектрике заряда входные вольтамперные характеристики МНОП-транзистора сдвигаются в ту или иную сторону и величина изменения его порогового напряжения является мерой хранимой в ячейке ин({юрмации„ Изменяя электрофизические характеристики диэлектрика в процессе изготовления, можно достаточно просто управлять параметрами МНОП-элемента памяти Например, для увеличения времени хранения информации в элементе памяти применяют различные технологические приемы:

наносят на межфазную границу

SiO Si,,N4npn формировании слоев диэ.лектрикон, тонкую островковую пленку тантала, платины, вольфрама,., кремния или германия;

изменяют режим формирования слоев диэлектрика таким образом, чтобы в слое его содержалось бы .не менее 5 свободного кремния, либо путем вариации температуры; и состава газовой среды слой выращивают переменHojo состава по тогг1ине;

.формируют, сгюй 81зКф так, чтобы его про.водимость не менее чем .в два раза превышала проводимость слоя 3i.02... :

Используя все эти технологические приемы, в принципе, возможно создавать интегральные матрицы ячеек памя-. ти лобой инфо рмаЦионной емкости и |

на И.Х основе изготавливать блоки па.мяти вычислительной техники.

Однако такой подход является не- приемлемым для практической реализации, поскольку количество выводов в . каждой такой матрице пропорционально ..ее информационной емкости, а количество м.ежсоединений в блоке памяти . будет, следовательно, таюке возрастать пропорционально числу матриц. Отсюда-, чемвыше будет информационная емкость бгюка памяти на основе таких матриц, тем меньше будет надежность его работы. Поэтому наиболее рпти- ; мальным, с точки зрения потребительс ких качеств, является изготовление . в составе одного интегрального устройства и матрицы-накопителя ячеек памяти, и управляющих ее работой вспомогательных схем ввода и вывода информации, дешифрации и т.д„ Естественно, что эти вспомогательные схемы должны изготавливаться по единой с матрицей-накопителем технологии и на основе тех же . конструктивных решений.

Наиболее близким к настоящему техническому решению-является способ изготовления интегральных . памяти на основе МНОП-транзисторов, вклочающий формирование на полупроводниковой подложке пленки окисла-, кремния тощиной 30-200 им над каналами транзисторов с постоянным пороговым напряжением, формирование

пленки окисла кремния тол1ниной 115 им над каналами транзисторов с переменным напря)(ением и {|гармированием над каналами всех транзисторов пленки нитрида кремния из парогазовой смеси, содержа1ней аммиак и моносилаНо

В этой интегральной схеме (ИС) транзисторы С .переменным пороговым i напряжением входят в схзстав матрицы- накопителя и являются-ячейками памяти, транзисторы с постоянным пороговым напряжением входят в сое-, тав управляющих схем ввода и-вывода информации. Способ заключается в . , следу101цем. В кремниевой подложке . -. п-типа с помощью стандартных опера- : ций маскирования и диффузии создают . локальные области р-типа, являющиеся -.истоками и стоками для всех тран-. . зисторов ИС, Затем над.областями каналов -Транзисторов, которые расположены между соответствуюи1ими областя5.ми р-типа, формируют пленку SiO, причем вначале.форнируют толстую , (более 30-50 нм) пленку над канала. мй транзисторов с постоянным пороговым напряжением, а затем над областя0 .ми каналов ячеек памяти формируют тонкую (1-15 нм) пленку SiO, После этого на области каналоввсех транзисторов одновременно наносят пленку , поверх которой создают металлические электроды затворов путем стандартных операций -фотолитографии по напыляемой поверх пленке металла и термического вжигания.

Однако указанный способ изготовления. ИС памяти, несмотря на простоту реализации, не обеспечивает получения стабильных и воспроизводимых характеристик записи и хранения информации, что затрудняет эксплуатацию ИС особенно при повышенных температурах. Указанные недостатки обус- ловлены тем, что пленка изготавливаемых ИС выполняет одновременно две функции:.

является средой для записи и хранения носителей заряда в транзисторах с переменным пороговым напряжением;

является защитной пленкой в затворной структуре транзисторов с постоянным пороговым напряжением.

Такое .двойственное использование пленки предъявляет противоречивые к ней тпебования. С одной стороны, для обеспечения работы ячеек памяти пленка должна содержат в своем объеме возможно большее количество центров захвата носителей заряда для повышения надежности.зап си информации и воспроизводимости в личины уровня записи. С .другой стороны, для стабильной работы транзис торов схем ввода и вывода информаци в условиях повышенных температур| в пленке не должно содержаться никаких центров захвата. Естествен- но, что в этом случае всегда прихо. дится искать компромисс между стабильностью работы ИС при повышенньгх температурах и уровнем записи информации. Одновременное улучшение этих Параметров в известном способа невозможно;Целью изобретения является повы-. шение стабильности и воспроизводимости характеристики записи и хранения информации. Цель достигается тем, что в способе изготовления интегральных схем. памяти на основе МНОП-транзисторов, вклочающем формирование на полупроводниковой подложке пленки окисла, кремния толщиной 30-200 нм над каналами транзисторов с постоянным пороговым напряжением, формирование пленки окисла кремния толщиной 15.НМ над каналами транзисторов с . переменным пороговым напряжением и ч формирование над каналами всех транзисторов пленки нитрида кремния из парогазовой- смеси, содержащей аммиак И моносилан, пленку нитрида кремния формируют при соотношений аммиака и моносилана 300:1-1000:1, а затем над каналами транзисторов с переменным пороговым напряжением на пленки нитрида кремния внедряют ионы азота или кремния дозой Т , В основу изобретения положено следующее физическое явление. Ионное облучение диэлектриков типа нитрида кремния, химическая связь в которых является не чисто ковалентной, а обладает некоторой долей ионности, способствует образованию в их объеме ловушек для носителей заряда. Эти ловушки образуются за счет разры ва и деформации- связей между составляющими нитрид кремния элементами при торможении внедря-:мух ионов, Таким образом, суть предлагаемого способа изготовления ИС памяти 8 лочается в том, что требуемые свойства пленки SijN4, наносимой одновременно на области каналов различных по .назначению транзисторов в ИС, обеспечиваются не одной, как в прототипе, а двумя различными операциями - нанесением пленки и последующим локальным ионнымоблучением, что естественно расширяет возможности процесса. При формировании пленки Si3N4 из парогазовой смеси, содержащий моносилан и аммиак, при большом количестве аммиака образуется однородная по составу пленка с миним.альным количеством ловушек для носитёлей заряда. При этом указанные свойства такой пленки не изменяются в процессе ее эксплуатации. Следовательно, при работе ИС в любых условиях повышенная температура, высокие питающие напряжения) в затворной структуре транзисторов вспомогательных схем ИС (схем ввода и вывода информации).не имеет место процесс захвата носителей заряда и пороговые напряжения этих транзисторов будут стабильными, что и требуется для надежной работы ИС. Степень требуемого пересыщения парогазовой смеси аммиаком может быть определена в каждом конкретном случае экспериментально, например, по результатам дрейфа порогового напряжения М - ОП-транзисторов при термополевых испытаниях (температура К, электрическое поле в затворной структуре 10 В/см). Например, для пленок , полученных при соотношении аммиака и мрносилана в смеси 10:1, 100:1, 300:1, 500:1 и 1000:1, дрейф порогового напряжения обычно составляет относительно исходного (до испытания) значения напряжения 100, 20, 20, .5 и. 2%, соответственно. Естественно, что при использовании таких пленок а нашем случае наиболее предпочтительными являются пленки, полученные при соотношении аммиака и моносилана равном 300 и более.. Известный из прототипа способ изготовления ИС при таких соотношениях полностью теряет свой..смысл, поскольку элементы памяти в ИС функционировать не будут из-за очень малой концентрации ловушек для зарядов в . Для обеспечения одновременно со стабильностью параметров ИС и возожности надежной и воспроизводимой

записи информации в элементах памяти ад областями каналов этих транзисторов пленку 31зМ4 облучают ионами азота или кремния. Облучением достигается образование в пленке ловуек для захвата и хранения информаионного заряда, под действием которого пороговоенапряжение элементов памяти и:зменяется в требуемую сторону,ю Поскольку процесс Формирования заданых свойств затворного диэлектрика лементов памяти производится локаль-- / о, то на .стабильности работы другик элементов ИСон никак не ска-|5

зывается. , .. .

.Изменяя Концентрацию ловушек, ихнергетическую глубину и пространственное распределение по слою ., которые определяются дозой, типом 20 внедряемого иона и энергией .ионов соответственно, можно для неизменных Условий записи варьировать величину Захватываемого информационного заряДа.. Для повышения надежности и вое- 25 производимости уровня записи заряда в элементы памяти Иб в предлагае- . . MOM спасо.бе конкретизированы тип и концентрация ионов, используемых для облучения и глубина их проникновения 30 в пленку SigMA Применение ионов эле-, ментов компонентов нитрида кремния кремния ИЛИ; азота обусловлено, вопервых, их электрической нейтральHocTbtov.B кремнии, во-вторых тем,jj

.что указанные ионы 6бразу от в глубокие ловушки примерно одинаковой энергетической глубины, не отжигаю-щИеся в процессе последующих операций формирования контактов затворов 40 транзисторов при температурах до .1073 К. Проводимость пленки SijN при этом практически не изменяется. Выполнение требования нейтральности выбранных ионов обеспечивает отсут- дЗ стеие подлегирования области канала МНОП-элементов памяти при частичном проникновении ионов в эту область подложки при облучении пленки ., Образование моноэнергетического глу- -« бокого уровня связано с тем, что выбранные ионы, являясь составными частями . будут образовывать в объеме, плойки дополнительные химические связи, то есть изменять ее стехио- .. метрию в требуемую сторону. Образующиеся ловушки для зарядов не отличаются по свойствам от имею1.нихся в п.пенке, поэтому высота их энергетического барьера для носителей заряда при записи и хранении информации совпадает как между собой, так .и вновь введенными облучением и генетическими ловушками. Это исключает какую-либо невоспроизводимост 8 величине захватываемого при записи заряда и следовательно в величине .логическихуровней для каждого элемента памяти в ИС. Иевоспроизводимость логических уровней .элементов памяти в ИС, изготавливаемых по предлагаемому способу, устраняется и тем, что облучение пленки производится на вао ее тоЛ1цину. Ловушки в этом случае образуются по всему объему пленки и запись зарядов поэтому как из металлического электро.да затвора, так и из области канала осуществляется на ловушки одинаковог типа. Исходя из .этого, можно опреде лить энергию внедряемых ионов. Известно, что для обеспечения торможения в объеме пленки SifN4 - 99,9 внедряемых ионов по всей тоги1ине плеки необходимо выполнить условие d R;p , где d - толщина пленки, RP и U.Rp- проекция и среднеквадратическое отклонение пробега ионов в ,,, зависящие от энергии ионов. Для используемых в предлаг ёмом способе тол1цин . 7.00-1 ОООА диапазон энергий ионов кремния должен быть в.8-50 кэВ, ионов азота 5.38 кэ8. Доза ионов того или иного типа должна быть I. , Диапазон изменения доз ионов определен экспериментально.

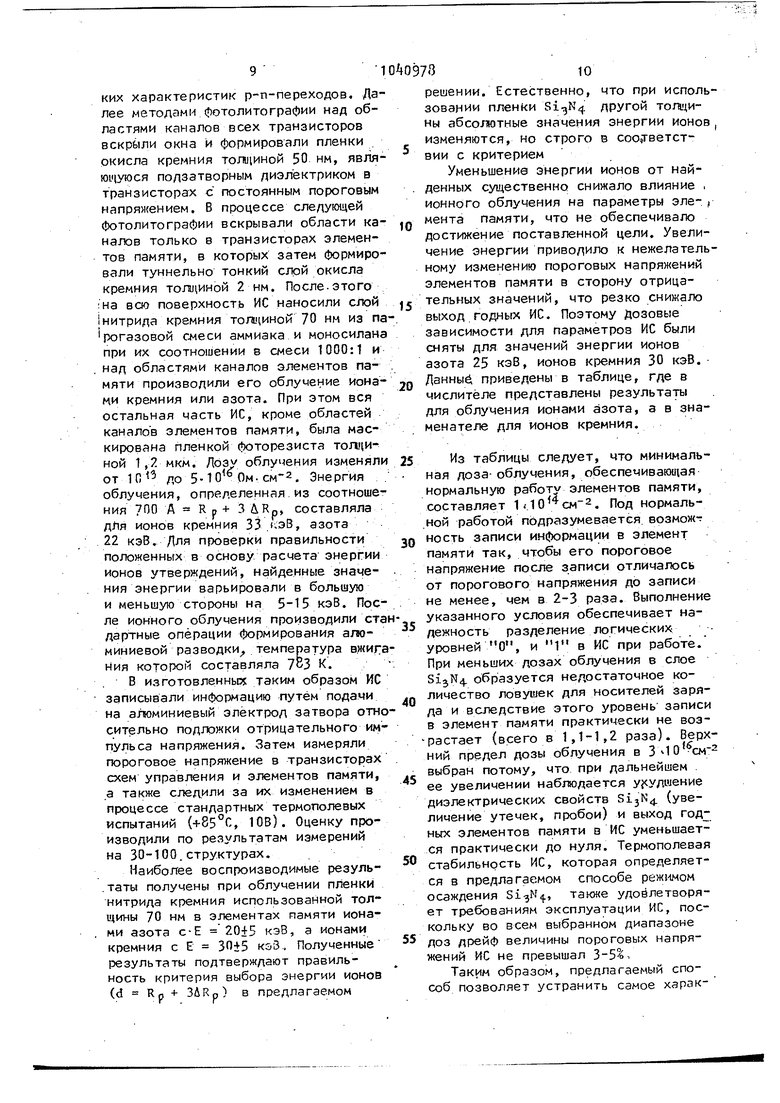

Приме р. Производилось опро.бование предлагаемого способа при Изготовлении ИС МНОП-перепрограммиру1емых постоянных запоминающих уст. 1ройств, вк/вдчающих матрицу-накопитель элементов памяти и схемы управления. ИС изготавливали на кремниевых подложках п-типа с удельным сопротивлением ,5 Ом-см. После химической обработки подложки окисляли до толцин окисла 0,7 мкм. Затем в окисле методами Фотолитографии вскрывали окна под области истоков и стоков составляЮ1чих ИС транзисторов. 3 полученные окна производили диффузию примеси противоположного типа проводимости, например, бора, после чего знозь производили термическое О1смсление, до толии ны окисла 0,20,3 Д.ПЯ улучше:.|и.я электрических характеристик р-п-переходов. Да лее методами фотолитографии над областями каналов всех транзисторов вскрЬ1ЛИ окна и формировали пленки окисла кремния толщиной 50 ни, явля ющуюся ползатворным диэлектриком в транзисторах с постоянным пороговым напряжением. В процессе следующей фотолитографии вскрывали области ка налов только в транзисторах элементов памяти, в которых затем формиро вали туннельно тонкий слой окисла кремния тоициной 2 нм. После.этого :на всю поверхность ИС наносили слой 1нитрида кремния тоя111иной 70 нм из п рогазовой слеси аммиака и моносилан при их соотношении в смеси 1000:1 и . над областями каналов элементов памяти производили его облучение ионами кремния или азота. При этом вся остальная часть ИС, кроме областей каналов элементов памяти, была маскирована пленкой фоторезиста толциной 1,2 мкм. Лозу облучения изменяли от 1П до .см-2. Энергия облучения, определенная.из соотношения 7ПО А R р + 3 ЛКр, составляла дЛя ионов кремния 33.(.эВ, азота 22 кэВ. Для проверки правильности положенных в основу расчета энергии ионов утверждений, найденные значания энергии варьировали в большую и меньшую стороны на 5-15 кэВ. После ионного облучения производили ста дартные операции формирования аломиниевойразводки температура в. ния которой составляла 783 К. В изготовленньк таким образом ИС записывали информацию путём подачи на аломиниевый электрод затвора отно сительно подложки отрицательного импульса напряжения. Затем измеряли пороговое напряжение в транзисторах схем управления и элементов памяти, а также следили за их изменением в процессе стандартных термополевых испытаний (+85°С, 10В). Оценку производили по результатам измерений на 30-100.структурах. Наиболее воспроизводимые резуяь.таты получены при облучении пленки нитрида кремния использованной толщины 70 нм в элементах памяти ионами азота с-Е 2045 кэВ, а ионами кремния с Е ЗП45 коЗ.. Полученные результаты подтверждают правильность критерия выбора энергии ионов (d RP + в предлагаемом решении. Естественно, что при использовании пленки другой тогацины абсолютные значения энергии ионов, изменяются, но строго в соо,тветствии с критерием Уменьшение энергии ионов от найденных существенно снижало влияние , ионного облучения на параметры эле-, мента памяти, что не обеспечивало достижение поставленной цели. Увеличение энергии приводило к нежелательному изменению пороговых напряжений элементов памяти в сторону отрицательных значений, что резко снижало выход годнь Х ИС. Поэтому Дозовые зависимости для параметров ИС были сняты для значений энергии ионов азота 25 кэВ, ионов кремния 30 кэВ. Данные приведены в таблице, где в числителе представлены результаты для облучения ионами азота, а в знаменателе для ионов кремния. Из таблицы следует, что минимальная доза- облучения, обеспечивающая нормальную работу элементов памяти. составляет 1 10сн Под нормальной работой подразумевается возмож-г ность записи информации в элемент памяти так, чтобы его пороговое напряжение после записи отличалось от порогового напряжения до записи не менее, чем в 2-3 раза. Выполнение указанного условия обеспечивает надежность разделение логических уровней О, и 1 в ИС при работе. При меньших дозах облучения в слое Si5N4 образуется недостаточное количество ловушек для носителей заряда и вследствие этого уровень записи в элемент памяти практически не возрастает (всего в 1,1-1,2 раза). Верхний предел дозы облучения в 3 Ю -CM выбран потому, что при дальнейшем . ее увеличении наблюдается у{ удшение диэлектрических свойств SijN (увеличение утечек, пробои) и выход годных элементов памяти в ИС уменьшается практически до нуля. Термополевая стабильность ИС, которая определяется в предлагаемом способе реж1-1мом осаждения , также удовлетворят требованиям эксплуатации ИС, поскольку во всем выбранном диапазоне доз дрейф величины пороговых напряений ИС не превышал 3-5%. Таким образом, предлагаемый способ позволяет устранить самое характерное для известного способа физическое ограничение, за клочащееся в-, противоречивости требований, предъяв ляемых к пленке нитрида Сравнение с базовым аналогом, в качестве которого выбрана техАология изготовления ИС памяти на НОГ|,-ддоанзисторах типа 559РР1 (SKO ,) показывает, что использование пред82лагаемого способа позволяет существенно увеличить выход годных ИС примерно в 1,3 раза без какого-либо усложнения их конструкции, при минимальном повышении трудоемкости изготовления кристаллов. При этом существенно улучшаются эксплуатационные характеристики ИС за счет расширения температурного диапазона их работы. . I . ; . Т. .

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ записи информации в запоминающий элемент на МДП-структурах | 1981 |

|

SU1012701A1 |

| Элемент памяти и способ его изготовления | 1989 |

|

SU1767535A1 |

| ЭЛЕМЕНТ ПАМЯТИ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1981 |

|

SU1012704A1 |

| Способ записи информации в запоминающий элемент мноп-типа | 1977 |

|

SU658599A1 |

| Ячейка памяти | 1978 |

|

SU752476A1 |

| Способ повышения радиационной стойкости микросхем статических ОЗУ на структурах "кремний на сапфире" | 2019 |

|

RU2727332C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МДП БИС | 1990 |

|

SU1762688A1 |

| Элемент памяти для постоянного запоминающего устройства | 1982 |

|

SU1079079A1 |

| Способ уменьшения величины положительного заряда в проводниковых структурах | 1979 |

|

SU862270A1 |

| Способ записи и считывания информации в МНОП-элементе памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405089A1 |

повышенные утечки через диэлектрик, пробой затвора.

| С А Н И Е РЕТЕНИЯ | 0 |

|

SU387705A1 |

| Способ утилизации отработанного щелока из бучильных котлов отбельных фабрик | 1923 |

|

SU197A1 |

| Патент США N 3877055, кл | |||

| Клапан | 1919 |

|

SU357A1 |

| Способ утилизации отработанного щелока из бучильных котлов отбельных фабрик | 1923 |

|

SU197A1 |

Авторы

Даты

1992-07-15—Публикация

1982-03-19—Подача