ел

о

00

со

Изобретение относится к вычислительной технике и может быть использовано для создания как электрически программируемых постоянных запоминающих устройств, так и многократно программируемых запо- .{линающих устройств повышенной информа- йионной емкости на основе СДП-структур, 1 частности МНОП-транзисторов. i Целью изобретения является гговышение информационной емкости.

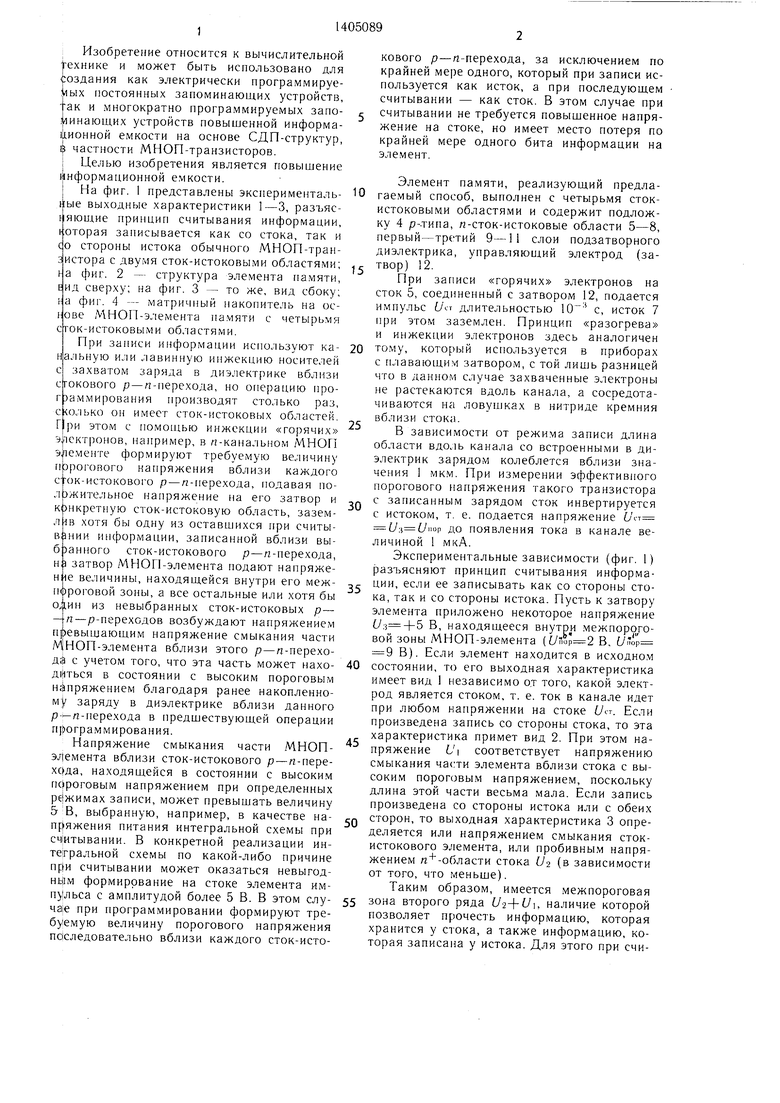

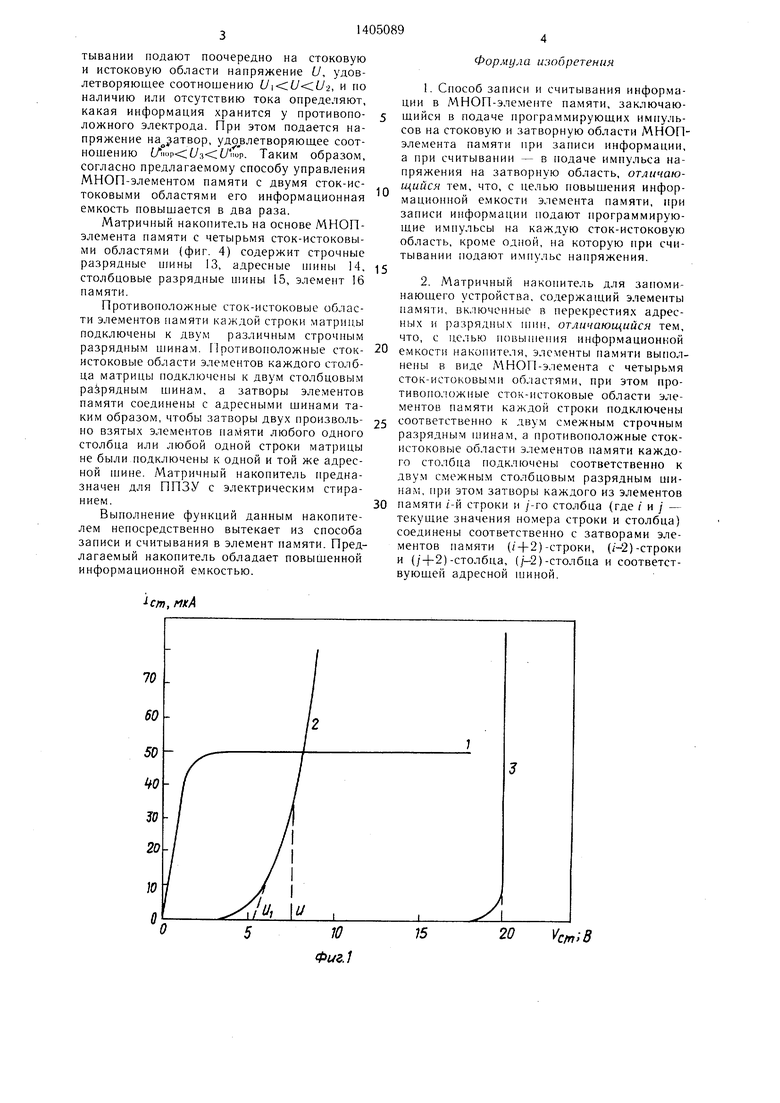

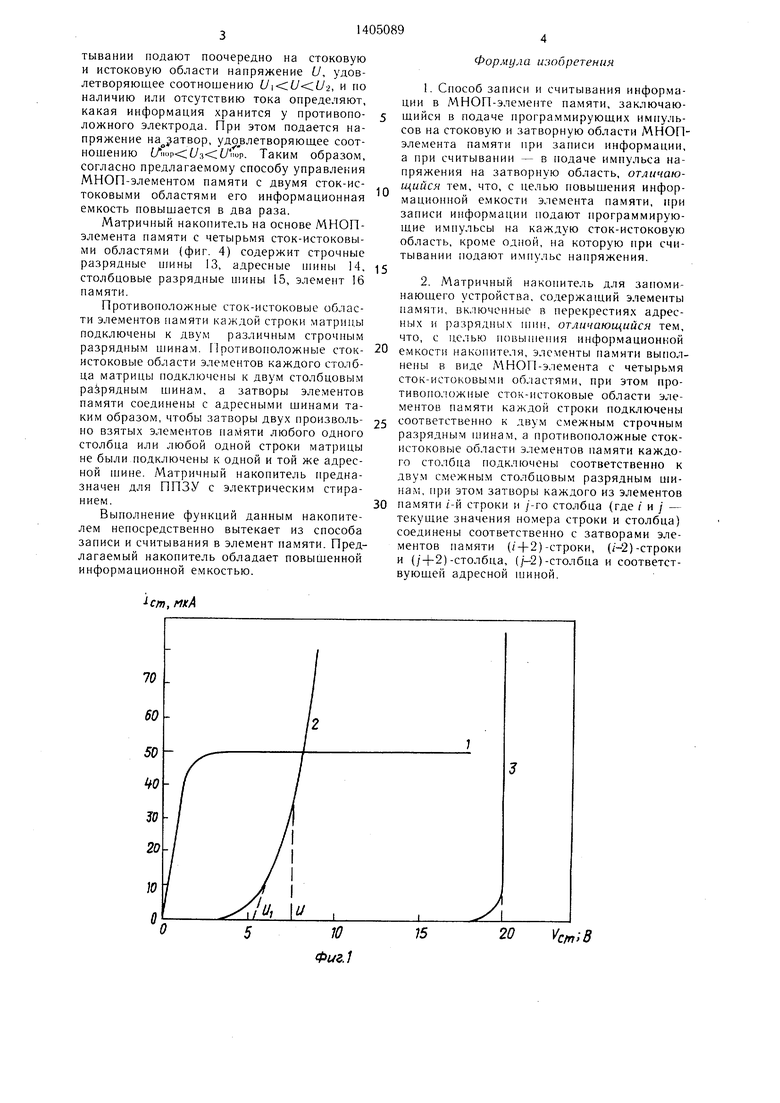

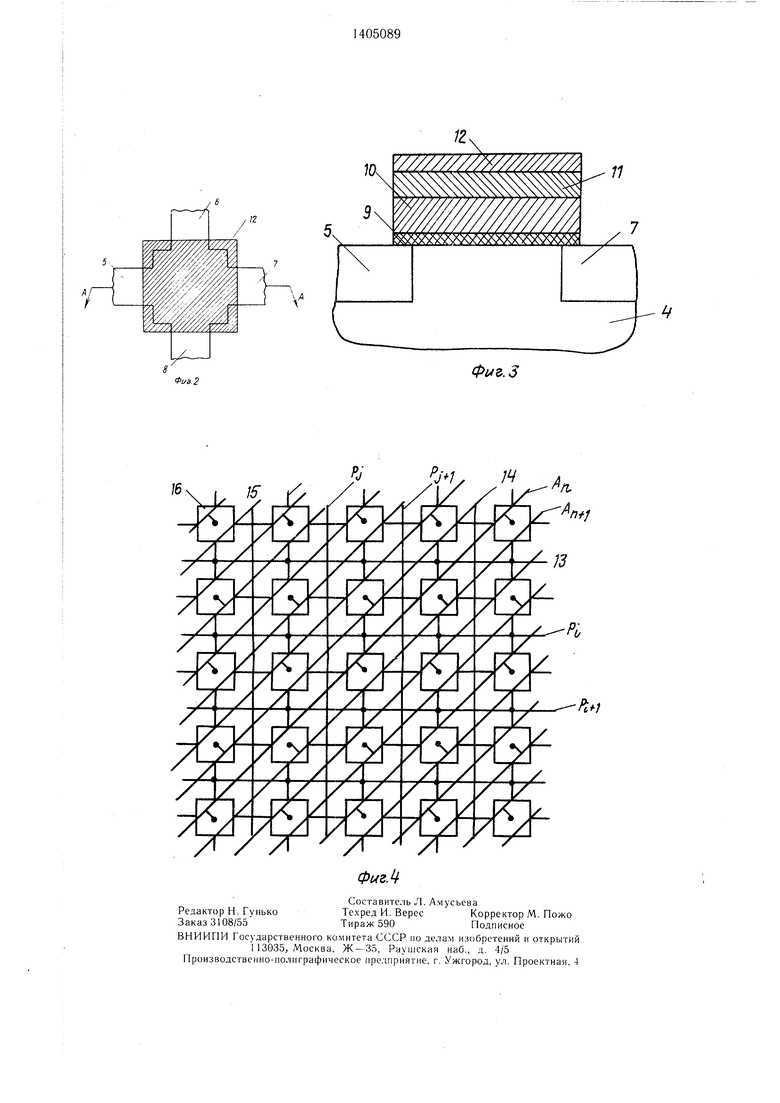

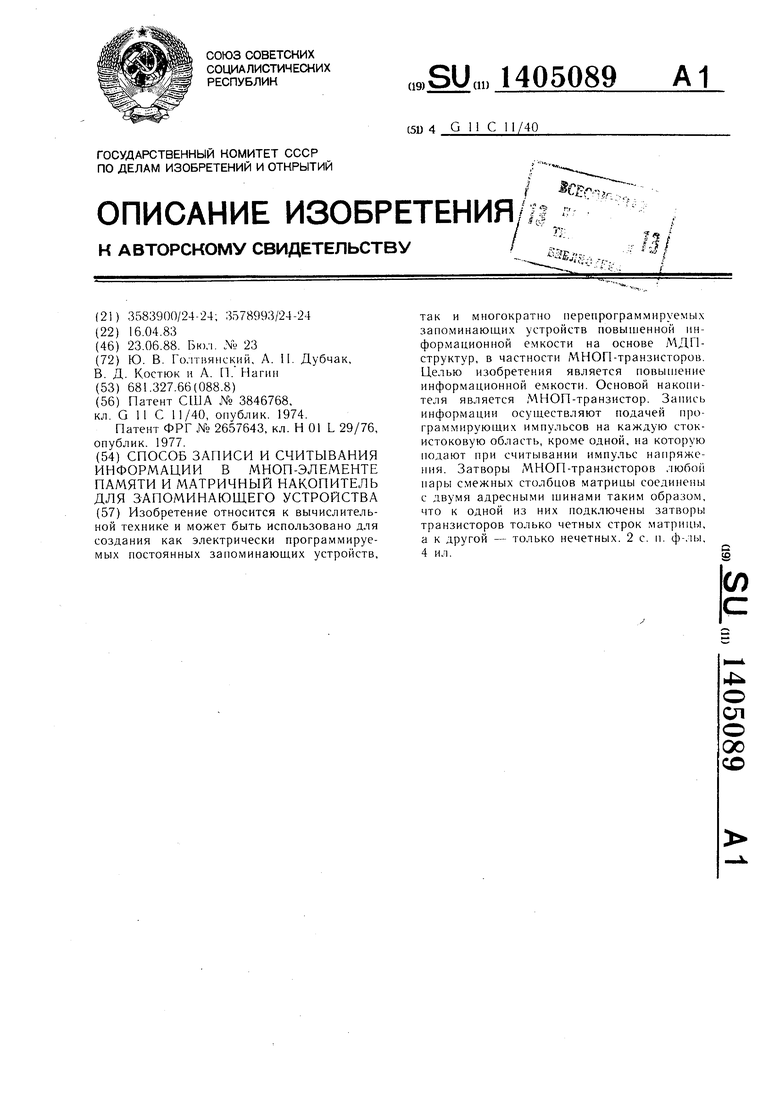

На фиг. 1 представлены эксперименталь- 1 ые выходные характеристики 1-3, разъяс- F яющие принцип считывания информации, оторая записывается как со стока, так и со стороны истока обычного МНОП-тран- истора с двумя сток-истоковыми областями; hja фиг. 2 - структура элемента памяти, ид сверху; на фиг. 3 - то же, вид сбоку; а фиг. 4 - матричный накопитель на ос- ове МНОП-элемента памяти с четырьмя ток-истоковыми областями.

При записи информации используют ка- альную или лавинную инжекцию носителей захватом заряда в диэлектрике вблизи окового р -п-перехода, но операцию программирования производят столько раз, олько он имеет сток-истоковых областей. Г1)и этом с помощью инжекции «горячих |пектронов, например, в п-канальном МНОП элементе формируют требуемую величину пэрогового напряжения вблизи каждого сток-истокового р - «-перехода, подавая по- л:1жительное напряжение на его затвор и конкретную сток-истоковую область, зазем- Л1В хотя бы одну из оставшихся при считы- в;пнии информации, записанной вблизи вы- б)анного сток-истокового р-«-перехода, Hi3 затвор МНОП-элемента подают напряжение величины, находящейся внутри его межпороговой зоны, а все остальные или хотя бы один из невыбранных сток-истоковых р- - л-р-переходов возбуждают папряжением превышающим напряжение смыкания части М|НОП-элемента вблизи этого р-п-перехо- д: с учетом того, что эта часть может находиться в состоянии с высоким пороговым н;И1ряжением благодаря ранее накопленному заряду в диэлектрике вблизи данного р- п-перехода в предшествующей операции программирования.

Напряжение смыкания части МНОП- э/(емента вблизи сток-истокового р-п-пере- хода, находящейся в состоянии с высоким псфоговым напряжением при определенных ре|жимах записи, может превышать величину 5В, выбранную, например, в качестве напряжения питания интегральной схемы при считывании. В конкретной реализации интегральной схемы по какой-либо причине при считывании может оказаться невыгодным формирование на стоке элемента импульса с амплитудой более 5 В. В этом слу- Maie при программировании формируют требуемую величину порогового напряжения последовательно вблизи каждого сток-исто5

5

кового р-rt-перехода, за исключением по крайней мере одного, который при записи используется как исток, а при последующем считывании - как сток. В этом случае при считывании не требуется повышенное напряжение на стоке, но имеет место потеря по крайней мере одного бита информации на элемент.

Элемент памяти, реализующий предла0 гаемый способ, выполнен с четырьмя сток- истоковыми областями и содержит подложку 4 р--типа, п-сток-истоковые области 5-8, первый-третий 9-11 слои подзатворного диэлектрика, управляющий электрод (затвор) 12.

При записи «горячих электронов на сток 5, соединенный с затвором 12, подается импульс Уст длительностью с, исток 7 при этом заземлен. Принцип «разогрева и инжекции электронов здесь аналогичен

0 тому, который используется в приборах с плавающим затвором, с той разницей что в данном случае захваченные электроны не растекаются вдоль канала, а сосредотачиваются на ловушках в нитриде кремния вблизи стока.

В зависимости от режима записи длина области вдоль канала со встроенными в диэлектрик зарядом колеблется вблизи значения 1 мк.м. При измерении эффективного порогового напряжения такого транзистора с записанным зарядом сток инвертируется с истоком, т. е. подается напряжение fy.-)t/iiop до появления тока в канале величиной 1 мкА.

Экспериментальные зависимости (фиг. 1) разъясняют принцип считывания информации, если ее записывать как со стороны стока, так и со стороны истока. Пусть к затвору элемента приложено некоторое напряжение 6. В, находящееся внутр|1 .межпорс;го- вой зоны МНОП-элемента ( В, U«of 9 В). Если элемент находится в исходном

0 состоянии, то его выходная характеристика имеет вид 1 независимо от того, какой электрод является стоком, т. е. ток в канале идет при любом напряжении на стоке . Если произведена запись со стороны стока, то эта характеристика примет вид 2. При этом напряжение L l соответствует напряжению смыкания части элемента вблизи стока с высоким пороговы.м напряжением, поскольку длина этой части весьма мала. Если запись произведена со стороны истока или с обеих сторон, то выходная характеристика 3 определяется или напряжением смыкания сток- истокового элемента, или пробивным напряжением « -области стока Ui (в зависимости от того, что меньше).

Таким образом, имеется межпороговая

5 зона второго ряда U-2-{-U, наличие которой позволяет прочесть информацию, которая хранится у стока, а также информацию, которая записана у истока. Для этого при счи0

5

5

0

тывании подают поочередно на стоковую и истоковую области напряжение U, удовлетворяющее соотношению .U-2, и по наличию или отсутствию тока определяют, какая информация хранится у противоположного электрода. При этом подается напряжение на атвор, удо влетворяю1яее соотношению U of U: lU nup. Таким образом, согласно предлагаемому способу управления МНОП-элементом памяти с двумя сток-ис- токовыми областями его информационная емкость повышается в два раза.

Матричный накопитель на основе МНОП- элемента памяти с четырьмя сток-истоковы- ми областями (фиг. 4) содержит строчные разрядные шины 13, адресные П1ины 14, столбцовые разрядные шины 15, элемент 16 памяти.

Противоположные сток-истоковые области элементов памяти каждой строки матрицы подключены к двум различным строчным разрядным шинам. Противоположные сток- истоковые области элементов каждого столбца матрицы подключены к двум столбцовым разрядным шинам, а затворы элементов памяти соединены с адресными шинами таким образом, чтобы затворы двух произвольно взятых элементов намяти любого одного столбца или любой одной строки матрицы не были подключены к одной и той же адресной шине. Матричный накопитель предназначен для ППЗУ с электрическим стиранием.

Выполнение функций данным накопителем непосредственно вытекает из способа записи и считывания в элемент памяти. Предлагаемый накопитель обладает повышенной информационной емкостью.

ст, MX А

Формула изобретения

. Способ записи и считывания информации в МНОП-элементе памяти, заключаюшийся в подаче програ.ммируюших импульсов на стоковую и затворную области МНОП- элемента памяти при записи информации, а при считывании - в подаче импульса напряжения на затворную область, отличаю щийся тем, что, с целью повышения информационной емкости элемента памяти, при записи информации подают программирующие импульсы на каждую сток-истоковую область, кроме одной, на которую при считывании подают импульс напряжения.

2. Матричный накопитель для запоми- наюшего устройства, содержащий элементы памяти, включенные в перекрестиях адресных и разрядных шин, отличающийся тем, что, с целью повышения информационной емкости накопителя, элементы памяти выполнены в виде МНОП-элемента с четырьмя сток-истоковыми областями, при этом про- тивог10, ожные сток-истоковые области элементов памяти каждой строки подключены

5 соответственно к двум смежным строчным разрядным шинам, а противоположные сток- истоковые области элементов памяти каждого столбца подключены соответственно к двум смежным столбцовым разрядным шинам, |ри этом затворы каждого из элементов

0 памяти ; -й строки и /-го столбца (где / и / - текущие значения номера строки и столбца) соединены соответственно с затворами элементов памяти (/ + 2)-строки, (/-2)-строки и {/4-2)-столбца, (/-2)-столбца и соответствующей адресной шиной.

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ записи и считывания информации в МНОП-элементе памяти,МНОП-элемент памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405088A1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| Матричный накопитель | 1980 |

|

SU974412A1 |

| Ячейка памяти для оперативного запоминающего устройства с энергонезависимым хранением информации | 1986 |

|

SU1531163A1 |

| Матричный накопитель и способ управления записью, считыванием и стиранием информации в накопителе | 1987 |

|

SU1596392A1 |

| НАКОПИТЕЛЬ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1995 |

|

RU2106022C1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Авторегулируемый формирователь напряжения записи для электрически программируемых постоянных запоминающих устройств на КМОП-транзисторах | 1988 |

|

SU1631606A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ НА МДП-ТРАНЗИСТОРАХ С ИЗМЕНЯЕМЫМ ПОРОГОВЫМ ВКЛЮЧЕНИЕМ | 1985 |

|

RU1378681C |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

Изобретение относится к вычислительной технике и может быть использовано для создания как электрически программируемых постоянных запоминающих устройств, так и многократно перепрограммируемых запоминающих устройств повып еннай информационной емкости на основе МДП- структур, в частности МНОП-транзисторов. Целью изобретения является повьииение информационной емкости. Основой теля является МНОП-транзистор. Запись информации осуществляют подачей программирующих импульсов на каждую сток- истоковую область, кроме одной, на которую подают при считывании импульс напряжения. Затворы МНОП-транзисторов любой нары смежных столбцов матрицы соединены с двумя адресными щинами таким образом, что к одной из них подключены затворы транзисторов только четных строк матрицы, а к другой - только нечетных. 2 с. п. ф-.1ы, 4 ил. eg

cmiS

Физ.2

Редактор Н. Гумько Заказ 3108/55

Составитель Л. Амусьева Техред И. ВересКорректор М. Пожо

Тираж 590Подписное

ВНИИПИ Государственного комитета СССР но делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

77

Фиг.З

L./

/

/

014ZM

| Патент США № 3846768, кл | |||

| Приспособление с иглой для прочистки кухонь типа "Примус" | 1923 |

|

SU40A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| ПОЕЗД, НАГРУЖЕННЫЙ РЕЛЬСАМИ, ДЛЯ ТРАНСПОРТИРОВКИ СВАРЕННЫХ ПО ДЛИНЕ РЕЛЬСОВ С ЗАЖИМНЫМИ ПРИСПОСОБЛЕНИЯМИ ДЛЯ РЕЛЬСОВОГО ПРОФИЛЯ | 2014 |

|

RU2657643C2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

Авторы

Даты

1988-06-23—Публикация

1983-04-16—Подача