сятого элемента И-НЕ, выходы третьего и девятого элементов И-НЕ через четвертый элемент ИЛИ-НЕ соединены с первым входом одиннадцатого элемента И-НЕ, вторые входы десятого и одиннадцатото элементов И-НЕ объединены между собой и соединены с вторым выходом источника синхрони-. зирующих сигналов, выходы десятого и одиннадцатого элемента И-НЕ соединены соответственно с входами сложения и вычитания первого счетного разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный счетчик импульсов | 1981 |

|

SU974594A1 |

| Устройство для определения экстремума | 1982 |

|

SU1070505A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1451857A1 |

| Устройство для записи цифровой информации | 1983 |

|

SU1123051A1 |

| ОХРАННОЕ КОДОВОЕ УСТРОЙСТВО | 1990 |

|

SU1834548A1 |

| Устройство для контроля регистра сдвига | 1980 |

|

SU911530A1 |

| Устройство для вычитания и добавления импульсов | 1989 |

|

SU1676077A1 |

| Устройство для моделирования систем массового обслуживания | 1990 |

|

SU1711179A1 |

| ОХРАННОЕ КОДОВОЕ УСТРОЙСТВО | 1990 |

|

SU1834549A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ | 1993 |

|

RU2041562C1 |

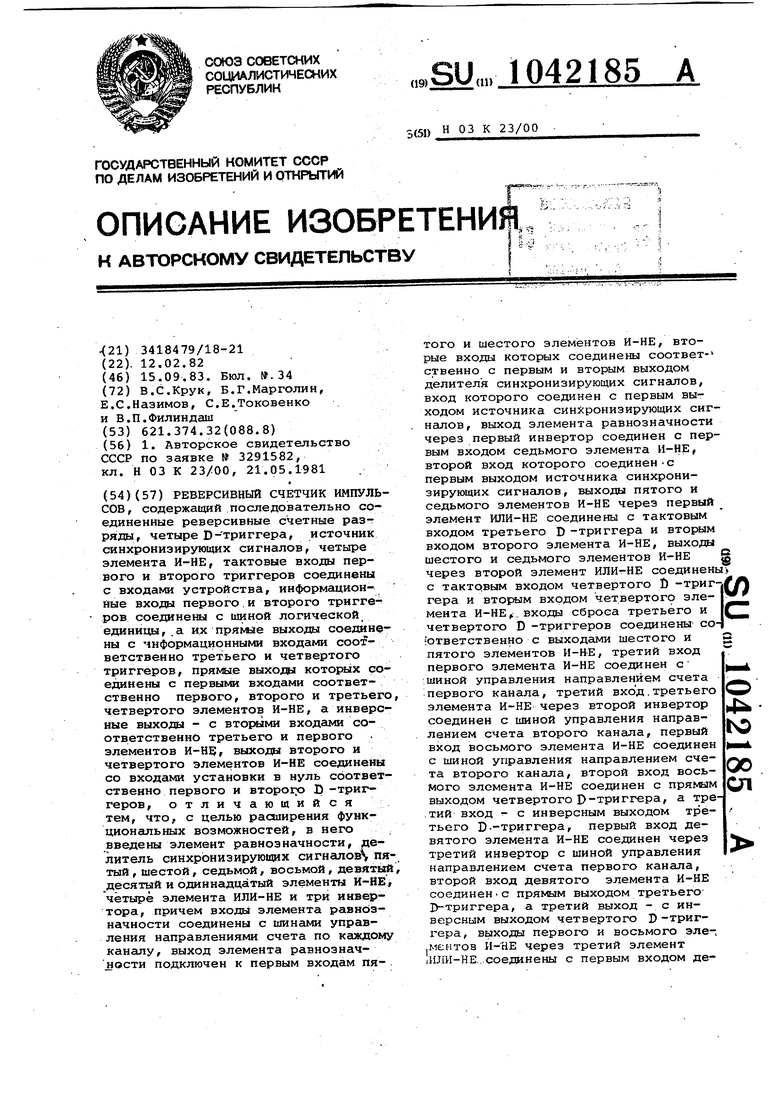

РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ, содержащий последовательно соединенные реверсивные счетные разряды, четыре D-триггера, источник синхронизирующих сигналов, четьфе элемента И-НЕ, тактовые входы первого и второго триггеров соединены с входами устройства, информационные входы первого.и второго триггеров соединены с шиной логической единицы, .а их прямае выходы соединенны с информационными входами соответственно третьего и четвертого триггеров, пря1Ф1е выходы которых соединены с первыми входами соответственно первого, второго и третьего, четвертого элементов И-НЕ, а инверсные выходы - с вторыми входами соответственно третьего и первого элементов И-НБ, выходы второго и четвертого элементов И-НЕ соединены со входами установки в нуль соответственно первого и второгчэ D-триггеров , отличающийся тем, что, с целью расширения функциональных возможностей, в него введены элемент равнозначности, делитель синхронизирующих сигналов пятый, шестой, седьмой, восьмой, девятый, десятый и одиннадцатый элементы И-НЕ, четыре элемента ИЛИ-НЕ и три инвертора, причем входы элемента равнозначности соединены с шинами управления направлениями счета по каждому каналу, выход элемента равнозначности подключен к первым входам пя-. того и шестого элементов И-НЕ, вторые входы которых соединены соответственно с первым и вторым выходом делителя синхронизирующих сигналов, вход которого соединен с первым выходом источника синхронизирующих сиг. налов, выход элемента равнозначности через первый инвертор соединен с первым входом седьмого элемента И-НЕ, второй вход которого соединенС первым выходом источника синхронизирующих сигналов, выходы пятого и седьмого элементов И-НЕ через первый элемент ИЛИ-НЕ соединены с тактовым входом третьего D -триггера и вторым входом второго элемента И-НЕ, выходы шестого и седьмого элементов И-НЕ f через второй элемент соединены: ica. |(Л с тактовым входом четвертого Ъ -триг-j гера и вторым входом четвертого элемента И-НЕ входы сброса третьего и 1| четвертого D -триггеров соединены co-J ответственно с выходами шестого и С пятого элементов И-RE, третий вход первого элемента И-НЕ соединен с шиной управления направлением счета первого канала, третий вход.третьего 4 1чЭ элемента И-НЕ через второй инвертор соединен с шиной управления направлением счета второго канала, первый вход восьмого элемента И-НЕ соединен с шиной управления направлением сче00 та второго канала, второй вход восьел мого элемента И-НЕ соединен с прямым выходом четвертого D-триггера, а тре.тий вход г- с инверсным выходом третьего D--триггера, первый вход девятого элемента И-НЕ соединен через третий инвертор с шиной управления направлением счета первого канала, второй вход девятого элемента И-НЕ соединенс прямым выходом третьего1 -триггера, а третий выход - с инверсным выходом четвертого D-триггера, выходы первого и восьмого эле-. |Ментов И-НЕ через третий элемент |НЛИ-НЕ...соединены с первым входом де

1

Изобретение относится к радиоэлектронике и может быть испольэован в автоматике, вычислительной и циф-. ровой измерительной технике.

Известен реверсивный счетчик импульсов, содержащий последовательно соединенные реверсивные счетные разряды, источник синхронизирующих сигналов, четыре D -триггера, четыре элемента И-НЕ. Этот источник обеспечивает совмещенный счет входных сигналов, поступающих по разным каналам при совпадении их во времени С ЗНедостаток известного устройства ограниченные функциональные возможности, обусловленные жестким определением направления счета сигналов, поступающих по разным каналам: сложение по первому и вычитание - по второму. В универсальных, счетчиках требуется как коммутация входов еложения и вычитания, так и обеспечение Счета сигналов по обоим каналам в одном направлении.

Целью изобретения является расширение функциональных возможностей устройства, т.е. обеспечение возможности управления направлением счета сигналов, поступающих по двум каналам. .Поставленная цель достигается тем что в реверсивный счетчик импульсов, содержащий последовательно соединенные реверсивные счетные разряды, первый, второй, третий и четвертый 35-триггера, источник синхронизирующих сигналов, четыре элемента И-НЕ, тактовые входы первого и второго триггеров соединены с входами устройства, информационные входы первого и второго триггеров соединены с шиной логической единицы, а их прямые выходы соединены с информационными входами соответственно третьего и четвертого триггеров, прямые выходы которых соединены с первыми входами соответственно первого, вто рого и третьего, четвертого элементов И-НЕ, а инверсные выходы - с вторыми входами соответственно третьего и первого элементов И-НЕ, выходы второго и четвертого элементов И-НЕ соединены -со входами установки в нуль соответственно первого и второго D -триггеров, введены элемент равнозначности, делитель синхронизирующих сигналов пятый, шестой, седьмой, восьмой, девятый, десятый и одиннадцатый элементы И-НЕ, четыре эле 1ента ИЛИ-НЕ и три инвертора, причем входы элемента равнозначности соединены с шинами управления направлениями счета по,каждому каналу, выход элемента равнозначности подключен к первым входам пятого и шестого элементов И-НЕ, вторые входы которых соединены соответственно с первым и вторым выходом делителя синхронизирующих сигналов, вход которого соединен с первым выходом источника синхронизирующих сигналов, выход элемента равнозначности через первый инвертор соединен с первым входом седьмого элемента И-НЕ, второй вход которого соединен с первым выходом источника синхронизирующих сигналов, выходы пятого и седьмого элементов И-ИЕ через первый элемент ИЛИ-НЕ соединены с тактовым входом третьего D-триггера и вторым входом второго элемента И-НЕ, выходы шестого и седьмого элементов И-НЕ через второй элемент ИЛИ-НЕ соединены с тактовым входом четвертогоD-триггера и BTopbiM входом четвертого элемента И-НЕ, входы сброса третьего и четвертого D -триггеров соединены соответственно с выходами шестого и пятого элементов И-НЕ, третий вход первого элемента И-НЕ соединен, с ишной управления направлением счета первого канала, третий вход третьего элемента И-НЕ через второй инвертор соединен с шиной управления направлением счета второго канала, первый вход восьмого элемента И-НЕ соединей с шиной управления направлением счета второго канала, второй вход восьмого элемента И-НЕ соединен с прямым выходом четвертого D -триггера, а третий вход - с инверсным выходок третьего 1) -триггера, первый вход девятого элемента И-НЕ соединен через третий инвертор с шиной управления направлением счета первого канала, второй вход девятого элемента И-НЕ соединен с прямым выходом третьего D -триггера, а третий выход - с инверсным выходом четвертого D -триггера, выходы первого и восьмого элементов И-НЕ через третий ИЛИ-НЕ соединены с пер.jBHM входом десятого элемента И-НЕ, выходы .третьего и девятого элементо И-НЕ через четвертый элемент ИЛИ-НЕ соединены с первым входом одиннадцатого элемента И-НЕ, вторые входы десятого и одиннадцатого элементов И-НЕ объединены между собой и со-: единены с вторым выходом источника синхронизирующих сигналов, выходы десятого и одиннадцатого элементов И-НЕ соединены срответствен.но с вхо дами сложения и вычитания первого счетного разряда.; На чертеже представлена функционгшьная схема устройства. Реверсивный счетчик импульсов содержит последовательно соедийенны реверсивные счетные разряды 1, источник 2 синхронизирующих сигналов, |четыре D-триггера З-б, четыре эле-|мента И-НЕ 7-10, тактовые входы 11 и 12 триггеров 3 и 4, по которым поступают соответственно счетные сигналы сложения и вычитания, инфор мационные входы 13 и 14 триггеров 3 и 4 соединены с шиной единичного потенциала. Выходы триггеров 3 и 4 соединены с D-входами триггеров 5 и б соответственно, тактовый вход триггера 5 соединен с первым входом элемента И-НЕ 7, второй вход которо го соединен с единичным выходом триггера 5, а выход элемента И-НЕ 7 соединен со входом сброса триггера 3, единичный выход триггера 5 и нулевой выход триггера б соединены со входами элемента Й-НЕ 9, тактовы вход триггера б соединен с первыМ; входом элемента 8, второй вхо которого соединен с единичным выходом триггера б, а выход элемента И-НЕ 8 соединен с входом сброса триггера 4, единичный выход триггер б и нулевой выход триггера 5 соединены со входами элемента И-НЕ 10 элемент 15 равнозначнрсти, делитель 16 синхронизирующих сигналов, пя-тый, шестой, седьмой, восьмой, девятый, десятый и одиннадцатый элементы И-НЕ 17-23, четыре элемента ИЛИ-НЕ 24-27, три инвертора 28-Зр входы элемента 15 равнозначности соединены с шинами 31 и 32 управлёнця направлениями счета по первому и второму каналам соответственно, выход элемента 15 подключен к первы входам элемента 17 и 18, вторые:вхо ды которых соединены соответственно с первым и ВТО1ЯЛМ входом делителя 16, вход которого соединен со втбрым выходом источника 2 синхронизирующих сигналов, выход элемента 15 через инвертор 30 соединен с первым входом элемента 19, второй вход коTopofo соединен со вторым выходом, источника 2, выходы элементов 17 и 19 через первый элемент ИЛИ-НЕ 24 соединены с входом тригге а 5, выходы элементов 18 и 19 через элемент ИЛИ-НЕ 25 соединены с тактовым входом триггера б, входы сброса триггеров 5 и 6 соединены с выходами элементов 18 и 17 соответственно, прямой выход триггера 5 соединен с первым входом элемента 21, инверсный выход триггера 5 соединен со входом элемента 20, прямой выход триггера б соединен с первым входом элемента 20, инверсный выход триггера б соединен со входом элемента 21. Первый вход элемента 9 соединен с шиной 31 управления направлением счета первого канала, первый вход элемента 10 через инвертор 29 соединен с шиной 32 управления направлением счета второго канала, первый вход восьмого элемента 20 соединен с шиной 32, первый вход элемента 21 через инвертор 28 соединен с шиной 31, выходы элементов 9 и 20 через элемент ИЛИ-НЕ 26 соединены с первым входом элемента 22, выходы элементов 10 и 21 через элемент 27 соединены с первым входом элемента 23, вторые входы элементов 22 и 23 объединены между собой и соединены с первым выходом источника 2, выходы элемен- . тов 22 и 23 соединены соответственно с входами сложения и вычитания пер- вого счетного разряда 1. Рассмотрим работу устройства в режиме вычитания по каждому каналу. В этом случае по шинам 31 и 32 управления направлениями счета поступают уровни логического нуля, при этом на выходе элемента 15 уровень логической единицы. Уровень логической единицы будет на выходе элемента 15 при работе устройства в режиме суммирования по каждому, каналу, в этом случае по шинам управления направлениями счета поступают. уровни логической единицы. В исходном положении триггеры З-б находятся в нулевом состоянии, . Поэтому на выходах :элементов 7-10 и 20, 21 - уровень логической единицы, вследствие этого на выходах . ментов 26-27 - уровень логического нуля, поэтому на выходах элементов 22 и 23 (на входах сложения и вычитания первого счетного paзpядa будут уровни логической единицы. . Источник 2 вырабатывает тактовые сигналы Т1 и Т2. Делитель 16 синхронизирующих сигналов делит тактовые сигналы ТР1 на два и вырабатывает два одинаковых по частоте, но сдвинутых друг относительно друга сигнала ТЗ и Т4. Первый счетный импульс, поступаю щий на вход первого канала 11, neper

водит триггер 3 в единичное состояние. Ближайший импульс ТЗ сначала проходит через элемент 17 и подтверждает нулевое состояние триггера 6, затем проходит через элемент 24 на тактовый вход триггера 5 и переводит его в единичное состояние, на инверсном выходе этого триггера - логический нуль, после чего этот же импульс поступает через элемент 7 на вход сброса триггера 3 и устанавл вает его в нуль. Так как на всех трех входах элемента 21 уровня логической единицы, то на его выходе будет уровень логического нуля, следовательно на выходе элемента 27 будет уровень логической единицы поэтому через элемент 23 на вход вычитания первого счетного разряда 1 пройдет один импульс Т2.

Второй счетный импульс, поступающий на вход второго канала 12, переводит триггер 4 в единичное состояние. Ближайший импульс Т4 проходит через элемент, 18 на вход сброса триггера 5 и устанавливает его в исходное состояние, затем проходит через элемент 25 на тактовый вход триггера б и переводит его в единичное состояние,, на инверсном выходе этого триггера - логический нуль, после чего этот же импульс поступает через элемент 8 на вход сброса триггера 4 и устанавливает его в нуль. Таким образом, по импульсу Т4 на втором и третьем входах элемента 21 появляются уровни логического нуля, а на всех входах элемента 10 будут уровни логической единицы, поэтому на выходах этих элементов будут соответственно уровни логической единицы и логического нуля. На выходе элемента 27 удерживается уровен логической единицы, поэтому еще один импульс Т2 проходит на входвычитания первого счетного разряда. Следующий импульс ТЗ, прошедший через элемент 17, устанавливает триггер б в исходное нулевое состояние.

При поступлении третьего и четвертого счетных импульсов по первому и второму каналам соответственно схема работает аналогично описанноjMy выше.

При работе устройства в режиме ложения по каждому каналу работают элементы 9 и 20, элемент 26 и элемент 22, счетные сигналы Т2 поступают при этом на вход сложения первого счетного разряда. На выходах элементов 10 и 21 - уровни логической единицы, на выходе элемента 27 - уровень логического нуля, поэтому сигналы Т2 на вход вычитания первого счетного разряда не поступают.

Рассмотрим работу устройства в режиме сложения по первому каналу и в режиме вычитания по второму.

В этом случае по шине управления направлением счета первого канала поступает уровень логической единицы, а второго канала - уровень логического нуля. На выходе элемента 15 при разноименных логических уров нях на шинах управления направлением счета каждого канала будет ;урове логического нуля. Поэтому на выхода элементов 17,18, 20 и 21, инвертор 30 постоянно находится уровень логической единицы.

В исходном положении триггеры 3-6 находятся в нулевом состоянии, следовательно на инверсных выходах триггеров 5 и 6 будут уровни логической единицы, а на выходах элементов 7-10 - уровень логической едницы, вследствие этого на выходах элементов 26, 27 уровейь логическог нуля, поэтому на выходах элементов 22 и 23 будут уровни логической единицы.

Счетные сигналы, поступающие одновременно (в одном промежутке между соседними импульсами Т1) на вход первого и второго каналов 11 и 12, переводят соответственно триггеры 3 и 4 в единичное состояние. Ближайший импульс Т1 проходит через элемент 19, элементы 24 и 25, переводит триггеры-5 и 6 в единичное состояние, после чего этот же импульс поступает через элементы 7 и 8 соответственно на входы сброса триггеров 3, 4 и устанавливает их в нулевое состояние. На выходах элементов 9 и 10 продолжают оставаться .уровни логической единицы, так как на их третьи входы с инверсных выходов триггеров 26 и 27 продолжают оставаться уровни логического нуля и сигналы Т2 не поступаю : на входы сложения и вычитания первого счетного разряда. Таким образом, при одновременном поступлении (в одном промежутке между соседними импульсами Т1) входных сигналов по первому каналу на сложение, а по второму на вычитание или наоборот, импульсы на вход первого счетного разряда не поступают.

Следующий счетный имцульс, поступающий на вход первого канала, переводит триггер 3 в единичное состояние. Ближайший импульс Т1 проходит через элементы 19, 24 и подтверждает единичное состояние триггера 5, а также проходит через элемент 7 и устанавливает триггер 3 в нулевое состояние. Этот же импульс Т1 проходит через элемент 25 на тактовый вход триггера 6, устанавливает его в нулевое состояние, так как на его информационном входе имеется уровеньлогического нуля. На всех входах элемента 9 будут уровни логической единицы, поэтому на его выходе будет

уровень логического нуля, а на выходе элемента 26 будет уровень логической единицы и на вход сложения первого счетного разряда 1 через элемент 22 пройдет один импульс Т2.

Следующий счетный импульс, постулающий на вход второго канала, переводит триггер 4 в единичное состояние. Ближайший импульс Т1 проходит через элементы 19 и 25, переводит триггер б в единичное состояние после чего этот же импульс поступает через элемент 8 на вход сброса триггера 4 и устанавливает его внулевое состояние Импульс Т1 через элемент 24 устанавливает триггер 5 в нулевое состояние, так как на его информационном входе имеется в это время уровень логического нуля, вследствие чего на выходе элемента 9 устанавливается уровейь логической единицы, а н-а выходе элемента 26 уровень логического нуля, поэтому сигналы Т2 через элемент 22 не проходят. В это же время на всех входах элемента 10 устанавливаются уровни логической единищ, поэтому на его

выходе будет уровень логического нуля, а на выходе элемента 27 усг тановится уровень логической единицы и ближайший лмпульс Т2 пройдет через элемент 23 на вход вычитания первого счетного, разряда 1.

При поступлении следующего импулса, по второму каналу устройство работает так же как описано выше, и еще один импульс Т2 поступает на вход вычитания первого счетного разряда.

При работе устройства в режиме вычитания по первому каналу и сложения по второму работают элементы 21 и 20 соответственно.

Таким образом, введение в реверсивный счетчик дополнительных элементов - элемента равнозначности, делителя синхронизирующих сигналов, элементов И-НЕ, элемента ИЛИ-НЕ и инверторов позволяет управлять направлением счета входных сигнапоэ поступающих по двум каналам, т.е. обеспечивает расширение функциональных возможностей реверсивного счетчика импульсов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР по заявке № 3291582, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-09-15—Публикация

1982-02-12—Подача