||й

СП

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля сигналов произвольной формы | 1986 |

|

SU1406527A1 |

| Формирователь сигналов произвольной формы | 1987 |

|

SU1465956A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Преобразователь кода во временной интервал | 1985 |

|

SU1300637A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1056452A1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

Изобретение относится к информационно-измерительной и вычислительной технике и может быть использовано в системах автоматического контроля и управления технологическими процессами. Изобретение позволяет повысить точность преобразования путем адаптации. Это достигается тем, что в аналого-цифровой преобразователь, содержащий элемент сравнения, тактовый генератор, элемент И, регистр сдвига, триггеры, элементы И, введены элементы сравнения, делители частоты, вентильные элементы, источник постоянных напряжений, ключи, счетчик, элементы задержки, блок вычитания, аналоговые сумматоры, сумматор, «нвертор, элементы ИЛИ. 3 ил.

OQ СП

Изобретение относится к информационно-измерительной и вычислительной технике и может быть использовано в системах автоматического контроля и управления технологическими процессами.

Целью изобретения является повышение точности преобразования путем адаптации.

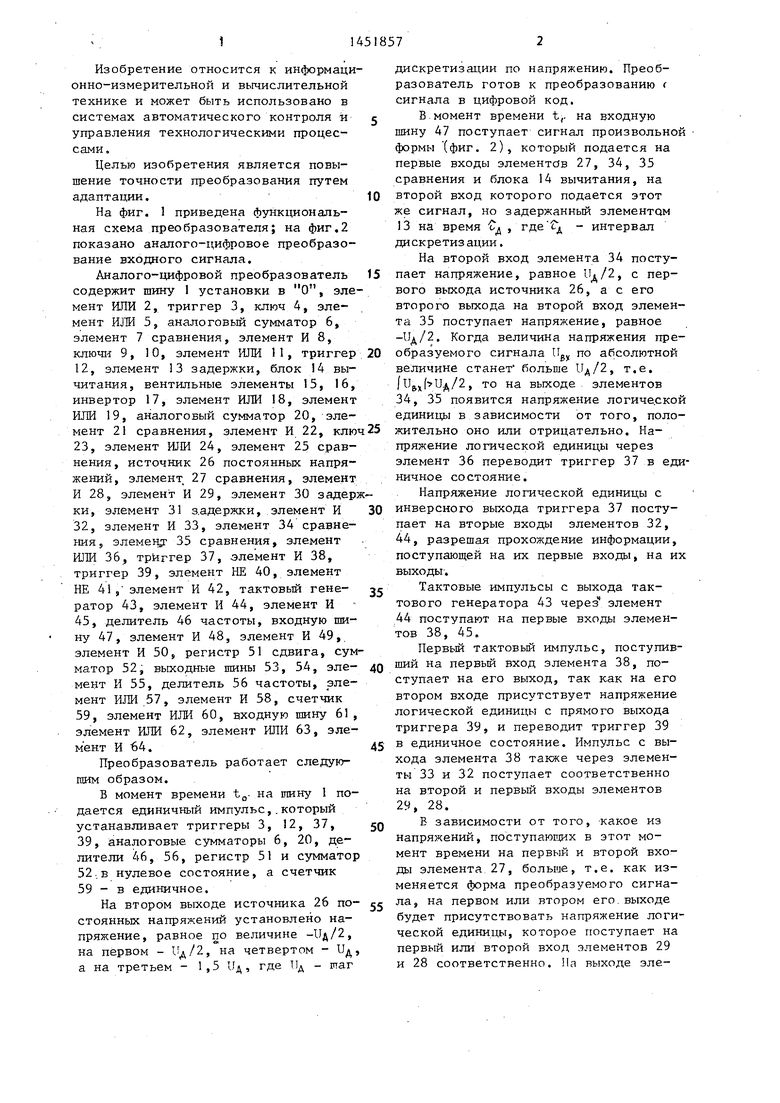

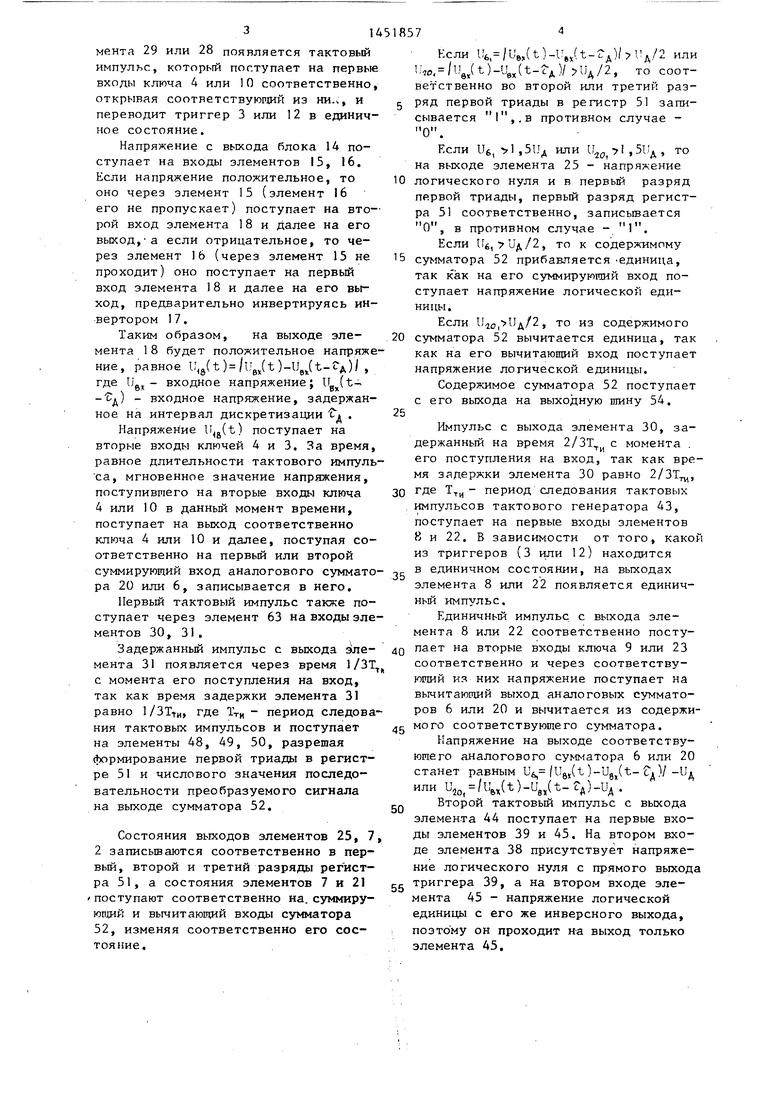

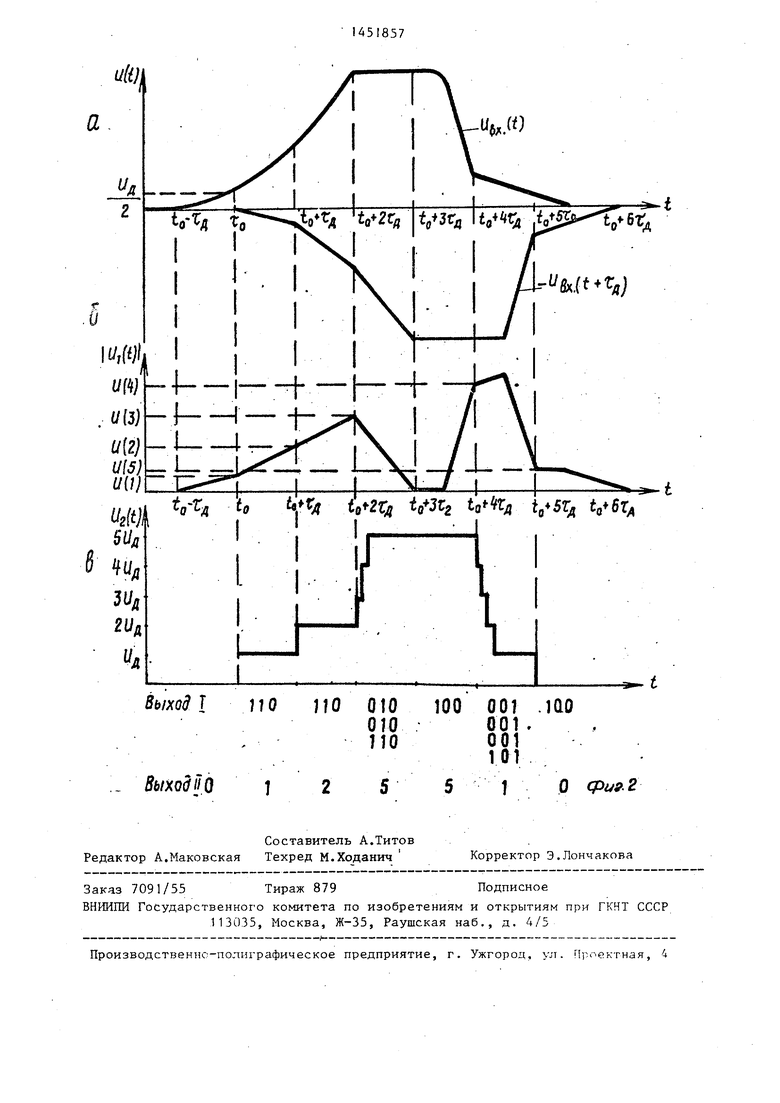

На фиг. 1 приведена функциональная схема преобразователя; на фиг.2 показано аналого-цифровое преобразование входного сигнала.

Аналого-цифровой преобразователь содержит шину 1 установки в О, элемент ИЛИ 2, триггер 3, ключ 4, элемент ИЛИ 5, аналоговый сумматор 6, элемент 7 сравнения, элемент И 8, ключи 9, 10, элемент ИЛИ 11, триггер 12, элемент 13 задержки, блок 14 вычитания, вентильные элементы 15, 16, инвертор 17, элемент ИЛИ 18, элемент ИЛИ 19, аналоговый сумматор 20, элемент 2 сравнения, элемент И 22, клю 23, элемент ИЛИ 24, элемент 25 сравнения, источник 26 постоянных напряжений, элемент 27 сравнения, элемент И 28, элемент И 29, элемент 30 задерки, элемент 31 з.адержки, элемент И 32, элемент И 33, элемент 34 сравнения, элеменд- 35 сравнения, элемент ИЛИ 36, триггер 37, элемент И 38, триггер 39, элемент НЕ 40, элемент НЕ 41, элемент И 42, тактовый гене- ратор 43, элемент И 44, элемент И 45, делитель 46 частоты, входную шину 47, элемент И 48, элемент И 49,. элемент И 50, регистр 51 сдвига, сумматор 52, выходные шины 53, 54, зле- мент И 55, делитель 56 частоты, элемент ИЛИ 57 J элемент И 58, счетчик 59, элемент ИЛИ 60, входную шину 61, элемент ИЛИ 62, элемент ИЛИ 63, элемент И 64.

Преобразователь работает следующим образом.

В момент времени на шину 1 подается единичный импульс,.который устанавливает триггеры 3, 12, 37, 39, аналоговые сумматоры 6, 20, делители 46, 56, регистр 51 и сумматор 52,в нулевое состояние, а счетчик 59 - в единичное.

На втором выходе источника 26 по- стоянных напряжений установлено напряжение, равное по величине -ид/2, на первом - Ид/2,на четвертом - ид а на третьем - 1,5 Ид, где Ид - шаг

дискретизахтии по напряжению. Преобразователь готов к преобразованию ( сигнала в цифровой код,

В, момент времени t,. на входную шину 47 поступает сигнал произвольно формы (фиг. 2), который подается на первые входы элементбв 27, 34, 35 сравнения и блока 14 вычитания, на второй вход которого подается этот же сигнал, но задержанный элементам 13 на время , гдеТд - интервал дискретиз ации.

На второй вход элемента 34 поступает напряжение, равное 1 д/2, с первого выхода источника 26, ас его второго выхода на второй вход элемента 35 поступает напряжение, равное -ид/2. Когда величина напряжения преобразуемого сигнала Ugj, по абсолютной величине станет больше , т.е. , то на выходе, элементов 34, 35 появится напряжение логическо единицы в зависимости от того, положительно оно или отрицательно. Напряжение логической единицы через элемент 36 переводит триггер 37 в едничное состояние.

Напряжение логической единицы с инверсного выхода триггера 37 поступает на вторые входы элементов 32, 44, разрешая прохождение информации, поступающей на их первые входы, на и

ВЫХОДЫ .

Тактовые импульсы с выхода тактового генератора 43 через элемент 44 поступают на первые входы элементов 38, 45,

Первый тактовый импульс, поступивший на первый вход элемента 38, поступает на его выход, так как на его втором входе присутствует напряжение логической единицы с прямого выхода триггера 39, и переводит триггер 39 в единичное состояние. Импульс с выхода элемента 38 также через элементы 33 и 32 поступает соответственно на второй и первый входы элементов 24, 28.

В зависимости от того, какое из напряжений, поступающих в этот момент времени на первый и второй входы элемента 27, больше, т.е. как изменяется форма преобразуемого сигнала, на первом или втором его.выходе будет присутствовать напряжение логической единицы, которое поступает на первый или второй вход элементов 29 и 28 соответственно. На выходе элемента 29 или 28 появляется тактовый импульс, который поступает на первые входы ключа 4 или 10 соответственно, открывая соответствуюршй из ни., и переводит триггер 3 или 12 в единичное состояние.

Напряжение с выхода блока 14 поступает на входы элементов 15, 16, Если напряжение положительное, то оно через злемент 15 (элемент 16 его не пропускает) поступает на вто-- рой вход элемента 18 и далее на его выход, а если отрицательное, то через элемент 16 (через элемент 15 не проходит) оно поступает на первьй вход элемента 18 и далее на его выход, предварительно инвертируясь инвертором 17.

Таким образом, на выходе элемента 18 будет положительное напряжение, равное l4a(t)/Ujt)-Ujt-rA)J , где UgK - входное напряжение; Ug(t- ) - входное напряжение, задержанное на интервал дискретизации .

Напряжение (t) поступает на вторые входы ключей 4 и 3, За время, равное длительности тактового импуль- са, мгновенное значение напряжения, поступившего на вторые входы ключа 4 или 10 в данный момент времени, поступает на выход соответственно ключа 4 или 10 и далее, поступая соответственно на первый или второй суммирующий вход аналогового сумматора 20 или 6, записывается в него.

Первый тактовый импульс также поступает через элемент 63 на входы элементов 30, 31.

Задержанный импульс с выхода элеента 31 появляется через время 1/ЗТ с момента его поступления на вход, так как время задержки элемента 31 равно 1/ЗТти, где IV - период следоваия тактовых импульсов и поступает а элементы 48, 49, 50, разрешая ормирование первой триады в регисте 51 и числового значения последовательности преобразуемого сигнала а выходе сумматора 52.

Состояния выходов элементов 25, 7, 2 записьюаются соответственно в первый, второй и третий разряды региста 51, а состояния элементов 7 и 21 Поступают соответственно на. суммирущий и вычитающий входы сумматора 52, изменяя соответственно его сосояние.

Если U6, /Uв,(t)-U.,(t-гд)./2 или I70, /UJt)-U„(t-гд)/ ид/2, то соответственно во второй или третий раз- ряд первой триады в регистр 51 записываетсяО.

1,,в противном случае 0

Если life, 1,5U или 2(7, на выходе элемента 25 - напряжение 0 логического нуля и в первый разряд первой триады, первый разряд регистра 51 соответственно, записьгеается О, в противном случае - 1.

Если Ufi, и д /2, то к содержимому 5 сумматора 52 прибавляется единица, так как на его суммирующий вход поступает напряжение логической единицы.

Если ,д/2, то из содержимого 0 сумматора 52 вычитается единица, так как на его вычитающий вход поступает напряжение логической единицы.

Содержимое сумматора 52 поступает с его выхода на выходную щину 54. 5

Импульс с выхода элемента 30, задержанный на время 2/ЗТ с момента . его поступления на вход, так как время задержки элемента 30 равно 2/ЗТ, 0 где период следования тактовых импульсов тактового генератора 43, поступает на первые входы элементов 8 и 22. В зависимости от того, какой из триггеров (3 или 12) находится в единичном состоянии, на выходах элемента 8 или 22 появляется единичный импульс.

Единичный импульс, с выхода элемента 8 или 22 соответственно посту- Q пает на вторые входы ключа 9 или 23 соответственно и через соответствующий из них напряжение поступает на вычитающий выход аналоговых сумматоров 6 или 20 и вычитается из содержи- g МОго соответствующего сумматора.

Напряжение на выходе соответствующего аналогового сумматора 6 или 20 станет равным и fUaK(t )-Ugj(t-Сд)/-Ид

или u,„ /u,,(t)-u„(t-г)-uд.

Второй тактовый импульс с выхода

элемента 44 поступает на первые входы элементов 39 и 45. На втором входе элемента 38 присутствует напряжение логического нуля с прямого выхода g триггера 39, а на втором входе элемента 45 - напряжение логической единицы с его же инверсного выхода, поэтому он проходит н-а выход только элемента 45,

Тактовый импульс с выхода элемента И 45 поступает на счетньА вход делителя 46 и на элементы 55, 58,

Так как состояние счетчика 59 единичное, то на выходе элемента 57 при- сутс-гвует напряжение логической единицы, которое поступает на второй вход элемента 55,разрешая прохождение тактового импульса на его выход, с которого тактовый импульс поступает на счетный вход делителя 56, сдвигающий вход регистра 51, сдвигая информацию в нем на один разряд, и на выходную шину 61, На выходной шине 53 появляется первый разряд первой триады, а на выходной шине 61 - тактовый импульс, соответствующий пер- в.ому разряду первой триады.

Если на выходе элемента 25 присутствует напряжение логической единицы, т.е. напряжение на первом его входе меньпш 1,5ид, то тактовый импульс проходит через элемент 58 на счетный вход счетчика 59, вычитая из его содержимого единицу.

Третий тактовый импульс с выхода элемента 44, пройдя через элемент 45, поступает на счетный вход делителя 46 и на элементы 55, 58,

Напряжение логической единицы с выхода элемента 57 поступает на элементы 55, Зв, С выхода элемента 55 тактовый импульс поступает на вход делителя 56, на сдвигающий вход регистра 51, сдвигая информацию в нем на один разряд, и на выходную шину 61.

На выходной шине 53 будет второй разряд первой триады, а на выходной шине 61 - второй тактовьй импульс, соответствующий второму разряду первой триады,

Третий тактовый импульс поступает через элемент 58 на счетный вход счетчика 59, вычитая из его содержимого единицу, т,е. его содержимое станет равным единице,

Четвертый тактовый импульс с выхода элемента 44 через элемент И 45 .поступает на счетный вход делителя 46 и на элементы 55, 58.. Так как в счетчике 59 записана единица, то на его первом выходе присутствует напряжение логической единицы, которое поступает на выход элемента 57, на выходе элемента 55 появляется импульс, который пос,тупает на счетньш вход делителя 56, на сдвигающий вход

5

регистра 51, сдвигая информацию в нем на один разряд, и на выходную шину 61.

На выходной шине 53 появляется третий разряд первой триады, а на выходной шине 61 - тактовый импульс, соответствуюш 1й третьему разряду триады,

Так как делитель 56 имеет коэффициент деления три, то на его выходе появляется единичный импульс, котс(- рьй поступает на первый вход элемента И 64. Если и4 :ид/2 и ,, то на выходе элемента 62 - напряжение логического нуля, которое поступает на второй вход элемента И 64, и импульс, поступивпшй на первый его- вход, не проходит на выход.

Если иб,- 11д/2 или , то импульс проходит на выходэлемента 64, так как на втором его входе присутствует напряжение логической еди- ницы. Но в этом случае Ug-|Ug(t)- -HB,( t- С-д )f 1 , 5U или U,;o, (U6,( t) - ti,(t-t.)/ 1,5U., и при прохождении

ол (Ц

Предыдущих трех импульсов на выход элемента 58 они не проходят, так как

на его третьем входе присутствует напряжение логического нуля, и содержимое счетчика 59 остается неизменным, т.е. находится в единичном состоянии .

С выхода элемента 64 единичный импульс поступает на входы элементов 30, 31.

С выхода элемента 31 задержанный импульс поступает на элементы 48, 49,

50 через время 1/ЗТу с момента поступления его на вход.

В соответствующие разряды регистра 51 записываются- состояния элементов 7, 21, 35. Так будет сформирована

вторая триада преобразования сигнала в регистре 51.

Если содержимое аналогового сумматора 6 или 20 больше напряжения Уд/2, то на выходе соответственно элемента

7 или 21 - напряжение логической единицы, а если оно больше 1,5Пд, то на выходе элемента 25 присутствует напряжение логического нуля, в противном случае на выходах элементов 7 и

21 - напряжение-логического нуля, а на выходе элемента 25 - логической единицы.

Состояние выхода элемента 49 поступает на суммируюпшй вход сумматоpa 52, a состояние выхода элемента 50 - на вычитающий вход сумматора 52

Если на выходе элемента 49 или 50 напряжение логической единицы, то состояние сумматора 52 изменяется.

Через время 2/31, на выходе элеме

та 30 появляется задержанный на время . 2/ ЗТ, импульс, который поступает на первые входы элементов 8 и 22, на вторые входы которых поступает напряжение с инверсных выходов триггеров 3 и 12 соответственно, В зависимости от того, какой из них находися в единичном состоянии. Напряжение логической единицы с его инверсного выхода пропускает задержанный импульс, поступивший на первый вход соответственно элемента 8 или 22, на его выход. Этот импульс открьшает соответственно ключ 9 или 23, на вычитающий вход соответствующего аналогового сумматора 6 или 20 поступает напряжение, равное Уд, которое вычитается из содержимого соответствующего, аналогового сумматора 6 или 20

Следующий тактовый импульс с выхода элемента 44, пройдя через элемент 45, поступает на счетный вход делителя 46 и на элементы 55, 58, Если на выходе элемента 57 - напряжение логического нуля, то тактовый i импульс не проходит на вькоды элементов 55, 58,

Если на выходе элемента 25 было напряжение логического нуля, т,е. напряжение на его первом входе больше 1,5Ui до поступления второго импульса с выхода элемента 44, то сос- тоярие счетчика 59 остается единичным, так как на первом входе элемента 58 присутствовало напряжение логического нуля и импульсы на его выход не проходили.

В этом случае преобразователь работает по описанному вьше алторитму, только через элемент 58 не будут проходить тактовые импульсы на счетный вход счетчика 59, Когда на выходе элемента 25 появится напрзвкенив логической единицы после очередного вы читания из содержимого аналогового сумматора 6 или 20 напряжения, равного Ui , то следующие три тактовых импульса, пройдя через элемент 58 на смежный вход счетчика 59, установят его в нулевое состояние.

Когда на выходе делителя 46 по- единичный импульс, это будет

518578

свидетельствовать о второй точке дискретизации, так как С д п .Т, где

10

20

15

,

п - коэффициент деления делителя 46, период следования тактовых им И

пульсов. Этот импульс через элементы 33 и 32 поступит на элементы 28 и 29,

В зависимости от того, на каком выходе элемента 27 присутствует напряжение логической единицы, единичный импульс пройдет через элемент 28 или 29 на его выход. Этот единичный импульс установит (или оставит в единичном состоянии ) триггер 3 или 12 и переведет (или оставит в нулевом состоянии) триггер 12 или 3. Единичный импульс отктроет также на время его длительности ключ 4 или 10. К содержимому аналогового сумматора 6 или 20 соответственно суммируется мгновенное значение разности напряжений в моменты времени,.соответствующие второй и первой точкам дискретизации, т.е. U,g /U- (t+ cд)- 25 -Ujt)/ .

Если до того,в первой точке дискретизации UgJ(t)-U(t-Г д) 0, а во второй точке дискретизации U (t+t)- -Ug(t) О, то в аналоговом суммато- 30 ре 20 будет напряжение, по величине равное ,(t + Гд)-Ug(t)/.

Если lyt)-Ug(t-tд) О, а iyt+ + д)0, то в аналоговом сумматоре 6 будет напряжение, по величине рав- 35 нее U6 /Ujt+ i)-U,(t)/.

Если lyt)-Ug,() о и Ug()(t)0, то ъ аналоговом сумматоре 6 будет/напряжение, по величине равное U6-/UeJt+e-)-U(t)+U«,/y а если 40 б)-и,() О и Ujt+r)-Ue,(t) «с. О, то в аналоговом сумматоре 20 будет напряжение, по величине равное

ад.)()+и2о,/, где , /11,.К.ид/, -ид/2 и ид/2-, и; 45 , -ид/2 и о,, где k - число уровней дискретизации по амплитуде на интервале дискретизации по времени.

Есди иб,ид/2 или , то на выходе элемента 7 или 21 соответственно - напряжение логической единицы, в противном случае - напряжение логического нуля.

Если и.1,5ид или ,5ид, то

50

55

на выходе элемента 25 - напряжение логического нуля, в противном случае- напряжение логической единицы.

Единичный импульс с выхода делителя 46 через элемент 60 также поступает на установочньш вход. счетчика. 59, устанавливая его в единичное состояние, и через элемент 63 - на входы элементов 30 и 31. Единичный импульс, задержанный элементом 31, поступает на элементы 48, 49 и 50. В зависимости от состояния выходов элементов 7, 21, 25 в регистре 51 будет сформирована следующая триада.

Состояния выходов элементов 49, 50 поступают соответственно на суммирующий и вычитающий входы сумматора 52. В зависимости от поступающих на них напряжений изменяется состояние сумматора 52. Содержимое сумматора 52 поступает на выходную шину 54.

Задержанный импульс с выхода элемента 30 поступает на элементы S и 22. При наличии на первом входе элемента 8 или 22 напряжения логической единицы на выходе его появляется задержанный импульс , из содержимого

1/31.,, поступит на элементы 48,49, 50, разрешая перепись состояния вы ходов элементов 7, 21 и 25 соответ 5 ственно в первый, второй и третий разряды регистра 51. В регистре 51 будет -сформирована очередная триад

Выходное напряжение логического нуля или единицы с выходов элемент 10 49, 50 подается соответственно на суммирующий или вычитающий вход су м-атора 52. .

Содержимое сумматора 52 увеличи вается или уменьшается на единицу 15 зависимости от того, ка какой его вход поступило напряжение логическ единицы. Содержимое сумматора 52 п ступает на выходную .пшну 54.

Импульс с выхода второго элемен

20 30, задержанный на время 2/31

и

по

ступает на элененты В, 22. В завис мости от того, какой из триггеров (3 или 12) находится в единичном состоянии, напряжение логической

«-v W vy«i:iruri , ncnip/l ftcnilti JlUl ИЧсСКОИ

аналогового сумматора 6 или 20 соот- 25 единицы с инверсного выхода одного

ветственно вычитается напряжение, равное ид.

Следующий тактовый импульс тактового генератора 43 через элементы 44, 45 поступает на счетный вход делителя 46 и на элементы 55, 58. ;

Если на выходе элемента 25 сравнения напряжение логического нуля, т.е. иб.г1,5ид или , то импульс . проходит, если же ,5ид или U,2o 155ид5 то на вьЕход элемента 58 этот импульс не проходит, так как на первом его входе напряжение логического нуля, и состояние счетчика 59 остается без изменения. Через элемент 55 импульс поступает на счетный. вход делителя 56, сдвигающий вход регистра 51, сдвигая его содержимое на один разряд (при этом на.выходной

из них пропускает единичный задерж ный импульс на выход элемента 8 или 22 соответственно, при этом открыва ется на время длительности импульса

30 ключ 9 или 23 соответственно. Напря жение , равное Ыд, с выхода соответствующего ключа 9 или 23 поступает на вычитаюгчий вход соответственно аналогового сумматора 6 или 20. Со35 держимое сумматора 6 или 20 уменьшится на Пд и станет равным 11 )/ - ид или соответстве , (t+4)(t)/ -ид. Если и, 1,5ид или и(гог,1,5ид , то на выходе

40 элемента 25 - напряжение логическог нуля и прео бразователь будет работа по описанному алгоритму до тех пор, пока не выполнится неравенство 1Ь /Uв(t+гд)-U6,(t)/-k.Uд 1,5ид или

-Q -вц - / - tjx / - Д - Д

щине .53 появляется содержимое перво- 45 гс, (+ }-lUt l -k-U. 1,50. го разрйда считьтаемпй тпияпм) .м на v-i -г

го разрйда считьшаемой триады),и на выходную шину 61 , свидете 1ьствуя о том, что на выходную шину 53 выдан первьй разряд триады../

Второй и третий импульсы совершают те же .действия, что и пред1,1дущий. Отличие только в том, что после третьего импульса на выходе делителя 56 появится единичный импульс, который поступит на входы элементов 30, 31, если на втором входе элемента 64 напряжение логической единицы.

Задержанный импульс на выходе элемента 31 появится через время,, равное

где k-1,1.При выполнении этих неравенств на выходе элемента 25 появля ется напряжение логической едицицы, которое поступает на первый вход эл

50 мента .58, разрешая тем самым прохож дение на его выход импульсов, посту пающих на его второй вход. После эт го три импульса поступают на вычита ющий вход счетчика 59 и его состоя55 ние становится нулевым. Напряжение логического нуля с его выходов, про дя через элемент 57,. запрещает прохождение импульсов через элементы 5 58, а единичный импульс с выхода де

45185710

1/31.,, поступит на элементы 48,49, 50, разрешая перепись состояния выходов элементов 7, 21 и 25 соответ- 5 ственно в первый, второй и третий разряды регистра 51. В регистре 51 будет -сформирована очередная триада.

Выходное напряжение логического нуля или единицы с выходов элементов 10 49, 50 подается соответственно на суммирующий или вычитающий вход сум- м-атора 52. .

Содержимое сумматора 52 увеличивается или уменьшается на единицу в 15 зависимости от того, ка какой его вход поступило напряжение логической единицы. Содержимое сумматора 52 поступает на выходную .пшну 54.

Импульс с выхода второго элемента

20 30, задержанный на время 2/31

и

поступает на элененты В, 22. В зависимости от того, какой из триггеров (3 или 12) находится в единичном состоянии, напряжение логической

«-v W vy«i:iruri , ncnip/l ftcnilti JlUl ИЧсСКОИ

25 единицы с инверсного выхода одного

25 единицы с инверсного выхода одного

из них пропускает единичный задержанный импульс на выход элемента 8 или 22 соответственно, при этом открывается на время длительности импульса

30 ключ 9 или 23 соответственно. Напряжение , равное Ыд, с выхода соответствующего ключа 9 или 23 поступает на вычитаюгчий вход соответственно аналогового сумматора 6 или 20. Со35 держимое сумматора 6 или 20 уменьшится на Пд и станет равным 11 )/ - ид или соответствен , (t+4)(t)/ -ид. Если и, 1,5ид или и(гог,1,5ид , то на выходе

40 элемента 25 - напряжение логического нуля и прео бразователь будет работат по описанному алгоритму до тех пор, пока не выполнится неравенство 1Ь /Uв(t+гд)-U6,(t)/-k.Uд 1,5ид или

/ - tjx / - Д - Д

45 гс, (+ }-lUt l -k-U. 1,50. v-i -г

гс, (+ }-lUt l -k-U. 1,50. v-i -г

где k-1,1.При выполнении этих неравенств на выходе элемента 25 появляется напряжение логической едицицы, которое поступает на первый вход элемента .58, разрешая тем самым прохождение на его выход импульсов, посту пающих на его второй вход. После этого три импульса поступают на вычитающий вход счетчика 59 и его состояние становится нулевым. Напряжение огического нуля с его выходов, пройдя через элемент 57,. запрещает проождение импульсов через элементы 55, 58, а единичный импульс с выхода деи

лителя 56 частоты разрешает формиров ние последней триады на второй точке дискретизации, вычитание из содержимого первого 6 или второго 20 аналогового сумматора величины U и окончательно формирует состояние сумматора 52, соответствующее значению ам гшитуды напряжения на второй точке дискретизации.

Формула изобретения

Аналого-цифровой преобразователь, содержащий первьш элемент сравнения, первый вход которого является входной шиной, тактовый генератор, выход которого соединен с первым входо первого элемента И, регистр сдвига, четыре триггера, четырнадцать элемен тов И, отличающийс я тем, что, с целью повышения точности, в него введены пять элементов сравнения, два делителя частоты, два вентильных элемента, источник постоянны напряжений, четыре ключа, счетчик импульсов, три элемента задержки, блок вычитания, два аналоговых сумматора, сумматор, инвертор, два элемента НЕ, двенадцать элементов ИЛИ, пер вые входы первого, второго, третьего четвертого и пятого элементов ИЛИ, входы установки в О первого и второго триггеров, первого и второго делителей частоты, регистра сдвига и сумматора объединены и являются шиной установки нуля, вьгеод первого элемента ИЛИ соединен с входом установки в О третьего триггера, второй вход первого элемента ИЛИ объеди йен с вторым входом второго элемента ИЛИ и соединен с выходом второго элемента И, третий вход первого элемент ИЛИ объединен с входом установки в 1 четвертого триггера, с первым

входом первого ключа, с вторым входо третьего элемента ИЛИ и соединены с выходом третьего элемента И, первый вход которого объединен с входом первого элемента НЕ и соединен с первым выходом второго элемента сравнения, второй вход третьего элемента И объединен с первыми входами второго и четвертого элементов И и соединен с выходом пятого элемента И, первый

вход которого соединен с выходом шестого элемента ИЛИ, второй вход объединен с вторым входом первого та И и соединен с инверсным выходом

1 2

второго триггера, вход установки в 1 которого соединен с выходом седьмого элемента ШШ, первый и второй входы которого соединены соответственно с выходами первого и третьего элементов сравнения,- первый вход последнего из которых объединен с первыми входами первого и второго элементов сравнения, входом первого элемента задержки и первым входом блока вычитания, второй вход третьего элемента сравнения объединен с первыми входами четвертого и пятого элементов сравнения и соединен с первым выходом источника постоянных напряжений, второй выход которого соединен с вторым входом первого элемента сравнения, третий выход соединен с первым входом шестого элемента сравнения, четвертый выход соединен с первыми входами второго и третьего ключей, второй вход второго кпюча соединен с выходом шестого элемента И, выход второго ключа, соединен с вычитающим входом первого аналогового сумматора, суммируюш ий вход которого соединен с выходом четвертого ключа, а вход установки в нулевое состояние соединен с выходом третьего элемента ИЛИ, выход первого аналогового сумматора соединен с вторым входом четвертого элемента сравнения и первым входом восьмого элемента ИЛИ, второй вход которого объединен с вторым входом пятого элемента сравнения и соединен с выходом второго аналогового сумматора, выход восьмого элемента ИЛИ соединен с вторым входом шестого элемента сравнения, выход которого соединен с первыми входами седьмого и восьмого элементов И, второй вход седьмого элемента И объединен с первыми входами девятого и десятого элементов И и соединен с выходом второго элемента задержки, второй вход девятого элемента И объединен с первым входом девятого элемента ИЛИ и соединен с выходом четвертого элемента сравнения, второй вход десятого элемента И объединен с вторым входом девятого .элемента ИЛИ и соединен с выходом пятого элемента сравнения, выход седьмого элемента И соединен с первым информационным входом регистра сдвига, выход девятого элемента И соединен с вторым информационным входом регистра сдвига и вычитающим входом сумматора,

сугдаирующий вход которого.объединен с третьим информационным входом регистра сдвига, соединен с выходом десятого элемента И, сдвигающий вход регистра сдвига объединен со счетным входом второго делителя частоты и соединен с выходом одиннадцатого элемента И, который является первой выходной шиной, выходы регистра сдвига и сумматора являются соответственно второй и третьей выходными шинами, выход второго делителя частоты соединен с первым входом двенадцатого элемента И, второй вход которого соединен с выходом девятого элемента ИЛИ, а выход соединен с первым входом десятого элемента ИЛИ, второй вход которого объединен с вторым входом пятого элемента ИЛИ, первым входом шестого элемента ИЛИ и соединен с выходом первого делителя частоты, третий вход десятого элемента ИЛИ объединен с вторым входом шестого элемента ИЛИ, входом установки в 1 первого триггера и соединен с выходом тринадцатого элемента И, выход десятого элемента ИЛИ соединен с входами второго и третьего элементов задержки, выход последнего из которых соединен с первыми входами че- тьфнадцатого и шестого элементов И, второй вход последнего .из которых соединен с прямым выходом третьего триггера, вход установки в 1 которого объединен с первым входом четвертого ключа, вторым входом четвертого элемента ИЛИ, третьим входом второго элемента ИЛИ и соединен с выходом четвертого элемента И, второй вход которого объединен с входом второго элемента НЕ и соединен с вторым выходом в горого элемента сравнения, выход второго элемента НЕ соединен с вторым входом второго элемента И,

третий вход которого соединен с выходом первого элемента НЕ, второй вход второго элемента сравнения объединен

с вторым входом блока вычитания и соединен с выходом первого элемента задержки, выход блока вычитания соединен с входами первого и второго вентильных элементов, выход первого

вентильного элемента через инвертор соединен с первым входом одиннадцатого элемента ИЛИ, втррой вход которого соединен с выходом второго венг тильного элемента, а выход соединен

с вторыми входами первого и четвертого ключей, выход первого элемента И соединен с первыми входами пятнадцатого и тринадцатого элементов И, второй вход тринадцатого элемента И

соединен с прямым выходом первого триггера, инвер.сный выход которого соединен с вторым- входом пятнадцатого элемента И, выход которого соединен со счетным входом первого делителя частоты, вторым входом восьмого элемента И и первым входом одиннадцатого элемента И, второй вход которого объединен с третьим входом восьмого элемента И и соединен с выходом

двенадцатого элемента ИЛИ, входы которого соединены с соответствующими выходами счетчика импульсов, счетный вход которого соединен с выходом восьмого элемента И, а вход установки в О - с выходом пятого элемента ИЛИ, выход первого ключа соединен с суммирующим входом второго аналогового сумматора, вычитаюг й вход которого соединен с выходом третьего

ключа, второй вход которого соединен с выходом четырнадцатого элемента И, второй вход которого соединен с прямым выходом четвертого триггера, вход установки в О которого соединен с

выходом второго элемента ЯПИ,

t,-t

5&/x(7 I no no

Выход iii)

V3t:2 V5r V6ry,

too

001 GDI 001 101

1

lao

0 (puf. 2

| Быхтияров Г.Д | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| М.: Сов | |||

| радио, 1980, с | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Гитис Э.И | |||

| Преобразователи информации для электронных цифровых вычислительных устройств | |||

| М.: Энергия, 1975, с | |||

| РАССЕИВАЮЩИЙ ТОПЛИВО МЕХАНИЗМ | 1920 |

|

SU298A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1989-01-15—Публикация

1986-12-25—Подача