8

/V

о

v

О

с

v N

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор импульсов | 1989 |

|

SU1707752A1 |

| Дельта-модулятор | 1988 |

|

SU1510090A2 |

| Синхронное счетное устройство | 1985 |

|

SU1283962A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Перестраиваемый делитель частоты | 1989 |

|

SU1629991A1 |

| Двоичный счетчик импульсов с контролем ошибок | 1977 |

|

SU687601A1 |

| Устройство для задержки импульсов | 1988 |

|

SU1713093A1 |

| Устройство корректировки фазы для схем синхронизации | 1989 |

|

SU1706037A1 |

| Преобразователь серии импульсов в прямоугольный импульс | 1986 |

|

SU1383473A1 |

| Делитель частоты с переменным коэффициентом деления | 1990 |

|

SU1812636A1 |

Изобретение относится к импульсной технике и может быть использовано для выделения составляющих цифровых потоков информации в системах управления и синхронизации, а также в фазовых преобразователях для управления приводами роботов или станков с числовым программным управлением с фазовой системой управления. Цель изобретения - повышение быстродействия и надежности устройства путем согласования задержек воздействия управляющего и корректирующего сигналов с опорной входной импульсной последовательностью. Цель достигается введением в устройство трех элементов ИЛ И 4-6, счетно- готриггера 7, логического элемента РАВНОЗНАЧНОСТЬ 9 и элемента 10 задержки. Кроме того, устройство содержит первый 1,

Фиг.1

второй 2 и третий 3 синхронные D-триггеры, логический элемент И 8, входные опорную 12, корректирующую 11 и управляющую 13 шины сигналов, а также выходную шину 14. Устройство позволяет формировать на своем выходе при отсутствии корректирующих сигналов на входной шине 11 прореженную в два раза опорную импульсную последовательность, поступающую на входную шину 12, При наличии на управляющей шине 13 единичного уровня напряжения по каждому корректирующему импульсу в выходную последовательность добавляется один имИзобретение относится к импульсной технике и может быть использовано для выделения составляющих цифровых потоков информации в системах управления и синхронизации, а также в фазовых преобразователях для управления приводами роботов или станков с числовым программным управлением с фазовой системой управления.

Цель изобретения - повышение быстродействия и надежности устройства путем согласования задержек воздействия управляющего и корректирующего сигналов с опорной входной импульсной последовательностью.

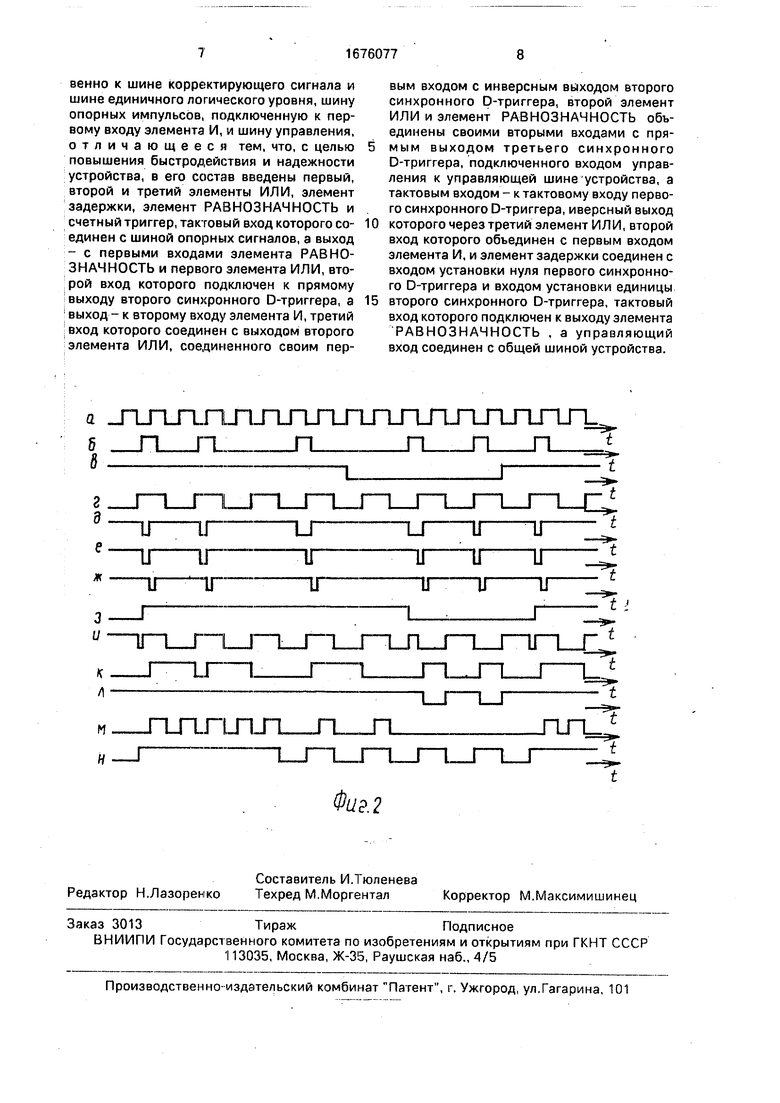

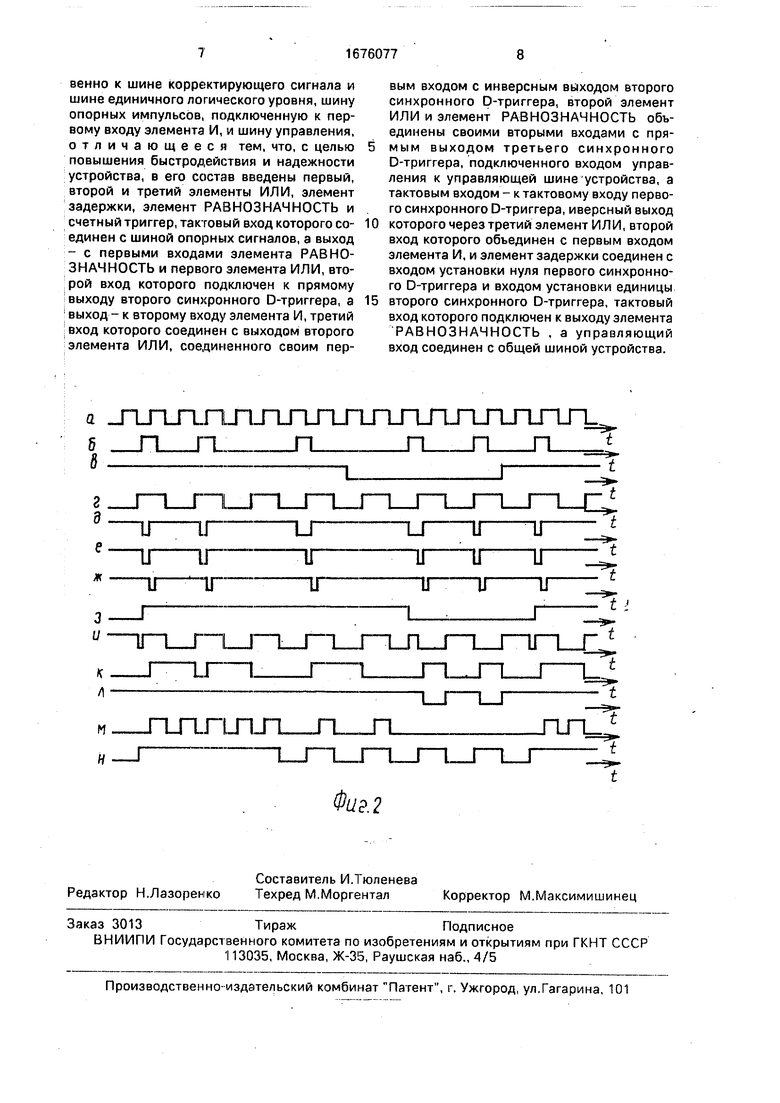

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство содержит первый 1, второй 2, третий 3 синхронные D-триггеры, первый 4, второй 5 и третий 6 элементы ИЛИ, счетный триггер 7, элементы И 8, РАВНОЗНАЧНОСТЬ 9 и задержки 10, а также входные шины корректирующего 11, опорного 12 и управляющего 13 сигналов и выходную шину 14,

Тактовый вход первого синхронного D- триггера 1 объединен с входной шиной 11 корректирующего сигнала и тактовым входом третьего синхронного D-триггера З, управляющий вход которого подключен к входной шине 13 управляющего сигнала. Шина 12 опорного сигнала подключена к тактовому входу счетного триггера 7 и первому входу элемента И 8, второй и третий входы которого соединены с выходами первого 4 и второго 5 элементов ИЛИ, соответственно. Выход счетного триггера 7 объединен с первым входом элемента РАВНОЗНАЧНОСТЬ 9 и первым входом первого элемента ИЛИ4, второй вход которого соединен с прямым выходом второго синхронного D-триггера 2, объединенного инпульс опорной частоты. В случае отсутствия входного управляющего воздействия из выходной последовательности по каждому корректирующему импульсу вычитается один импульс. Период поступления импульсов коррекции на входную шину 11 должен быть не менее двух периодов опорной частоты. Причем на выходной шине 14 в зависимости от периодичности корректирующих импульсов могут быть достигнуты и предельные последовательности - от полного отсутствия выходных импульсов до частоты, равной частоте опорных сигналов. 2 ил.

версным выходом с первым входом второго элемента ИЛИ 2, второй вход которого подключен к прямому выходу третьего синхронного D-триггера З и второму входу элемента

РАВНОЗНАЧНОСТЬ 9. Выход элемента РАВНОЗНАЧНОСТЬ 9 объединен с тактовым входом второго синхронного D-триггера 2, вход управления которого соединен с общей шиной устройства, а вход установки

единицы подключен к выходу элемента 10 задержки и входу установки нуля второго синхронного D-триггера 2, соединенного инверсным выходом через третий элемент ИЛИ, второй вход которого подключен к

входной шине 12 опорного сигнала, с входом элемента 10 задержки. Причем управляющий вход синхронного D-триггера 1 объединен с шиной логической единицы устройства, выходная шина 14 которого подключена к выходу элемента И 2.

Устройство работает следующим образом.

В исходном состоянии, когда корректирующие импульсы отсутствуют, независимо

от состояния третьего синхронного D-триггера 3, на выходной шине 14 присутствует прореженная в два раза опорная импульсная последовательность. Первый синхронный D-триггер 1 находится в единичном

состоянии по инверсному выходу (фиг. 2д). Этот единичный уровень блокирует прохождение нулевого сигнала через элемент ИЛИ 6, запрещая тем самым установку второго синхронного D-триггера 2 в единичное состояние по его S-входу, Счетным триггером 7 осуществляется деление входной опорной частоты на шине 12 (фиг. 2а) в два раза (фиг. 2г), причем переключение его из одного состояния в другое происходит по задним

фронтам опорной импульсной последовательности. Для сохранения длительности импульсов входной последовательности

элементом РАВНОЗНАЧНОСТЬ осуществляется инвертирование поделенной на два опорной импульсной последовательности в случае, когда на выходе третьего синхронного D-триггера З присутствует нулевой уровень. Второй синхронный D-триггер 2 по каждому положительному перепаду напряжения на тактовом входе подтверждает свое нулевое состояние. Следовательно, в исходном состоянии на инверсном выходе синхронного D-триггера 2 находится единичный уровень, который через элемент ИЛИ 5 воздействует на третий вход элемента И 9 и разрешает прохождение сигналов через элемент И 8. На второй вход элемента И 8 поступает поделенная на два частота опорных импульсов с выхода триггера 7, поскольку на прямом выходе второго синхронного D-триггера 2 присутствует нулевой уровень сигнала. Таким образом, на выходе элемента И 8, т.е. на выходной шине 14 устройства (фиг. 2м), формируется прореженная в два раза опорная импульсная последовательность,

При наличии на управляющей шине 13 единичного уровня напряжения и корректирующих импульсов на входной шине 11 устройство производит добавление импульсов к последовательности, формируемой на его выходе в исходном состоянии.

По первому корректирующему импульсу, поступившему на шину 11 (фиг. 26), срабатывает третий синхронный D-триггер З, на выходе которого формируется единичный уровень напряжения (фиг. 2з). По каждому корректирующему импульсу на шине 11 по его переднему фронту срабатывает синхронный D-триггер 1 (фиг. 2д), обеспечивая формирование на выходе элемента 10 задержки короткого импульса, устанавливающего второй синхронный D-триггер 2 в единичное состояние (фиг.2к). Возврат триггера 2 в исходное нулевое состояние производится по переднему фронту импульса с выхода элемента РАВНОЗНАЧНОСТЬ (фиг. 2и), т.е. по переднему фронту следующего за корректирующим импульсом сигнала с выхода счетного триггера 7 (фиг. 2г).

Таким образом, по каждому корректирующему импульсу на шине 11 и при наличии управляющего единичного сигнала на шине 13 в прореженную в два раза выходную последовательность (фиг. 2м) опорных импульсов с входной шины 12 (фиг. 2а) добавляется один импульс из опорной последовательности.

При наличии на управляющей шине 13 нулевого уровня напряжения и корректирующих импульсов на входной шине 11 устройство производит вычитание импульсов

из последовательности, формируемой на его выходе в исходном состоянии.

По первому корректирующему импуль: су, поступившему на шину 11 (фиг. 26), срэ- бзтывает третий синхронный триггер 3, на выходе которого формируется нулевой уровень напряжения (фиг. 2з). По каждому кор- ректирующему импульсу на шине 11, по его переднему фронту, срабатывает первый

0 синхронный D-триггер 1 (фиг. 2д), обеспечивая формирование на выходе элемента 10 задержки короткого импульса, устанавливающего второй синхронный D-триггер 2 в единичное состояние (фиг. 2к). Возврат

5 триггера 2 в исходное нулевое состояние производится по переднему фронту импуль- са с выхода элемента РАВНОЗНАЧНОСТЬ 9 (фиг. 2и), работающего в данном режиме в виде инвертора импульсов с выхода счетно0 го триггера 7, т.е. возврат триггера 2 в исходное состояние производится по заднему фронту импульса с выхода счетного триггера 7. При этом на выходе второго элемента ИЛИ 5 формируется нулевой уровень сигна5 ла (фиг. 2л), стробирующий прохождение импульсов опорной частоты через элемент И 8 на выходную шину 14 устройства (фиг. 2м).

Таким образом, по каждому корректиру0 ющему импульсу на шине 11 и при отсутствии управляющего сигнала на шине 13 из прореженной в два раза входной последо- - вательности опорных импульсов на шине 12 вычитается один импульс.

5 Период поступления импульсов коррекции на шину 11 устройства должен быть не менее двух периодов опорной частоты, присутствующей на входной шине 12. Причем на выходной шине 14 устройства в зависи0 мости от периода подачи корректирующих импульсов могут быть получены и предельные импульсы последовательности - от полного отсутствия импульсов до частоты, равной частоте следования опорных им5 пульсов.

Изобретение не требует специальной синхронизации управляющего и корректирующего сигналов к импульсам опорной частоты, надежно в работе в силу своей

0 относительной простоты и позволяет достичь минимальную задержку распространения входного сигнала на выход устройства, равную времени задержки распространения сигнала в логическом элемен5 те И.

Формула изобретения

Устройство для вычитания и добавления

импульсов, содержащее три синхронных Dтриггера, тактовый вход и вход управления

первого из которых подключены соответственно к шине корректирующего сигнала и шине единичного логического уровня, шину опорных импульсов, подключенную к первому входу элемента И, и шину управления, отличающееся тем, что, с целью повышения быстродействия и надежности устройства, в его состав введены первый, второй и третий элементы ИЛИ, элемент задержки, элемент РАВНОЗНАЧНОСТЬ и счетный триггер, тактовый вход которого соединен с шиной опорных сигналов, а выход - с первыми входами элемента РАВНОЗНАЧНОСТЬ и первого элемента ИЛИ, второй вход которого подключен к прямому выходу второго синхронного D-триггера, а выход - к второму входу элемента И, третий вход которого соединен с выходом второго элемента ИЛИ, соединенного своим перa jTTLTinjariJTrmj

б П ППП ГТ п

вым входом с инверсным выходом второго синхронного D-триггера, второй элемент ИЛИ и элемент РАВНОЗНАЧНОСТЬ объединены своими вторыми входами с прямым выходом третьего синхронного D-триггера, подключенного входом управления к управляющей шине устройства, а тактовым входом - к тактовому входу первого синхронного D-триггера, иверсный выход

которого через третий элемент ИЛ И, второй вход которого объединен с первым входом элемента И, и элемент задержки соединен с входом установки нуля первого синхронного D-триггера и входом установки единицы

второго синхронного D-триггера, тактовый вход которого подключен к выходу элемента РАВНОЗНАЧНОСТЬ , а управляющий вход соединен с общей шиной устройства.

| Устройство для вычитания и добавления импульсов | 1983 |

|

SU1127083A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для вычитания и добавления импульсов | 1986 |

|

SU1370755A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-09-07—Публикация

1989-09-15—Подача