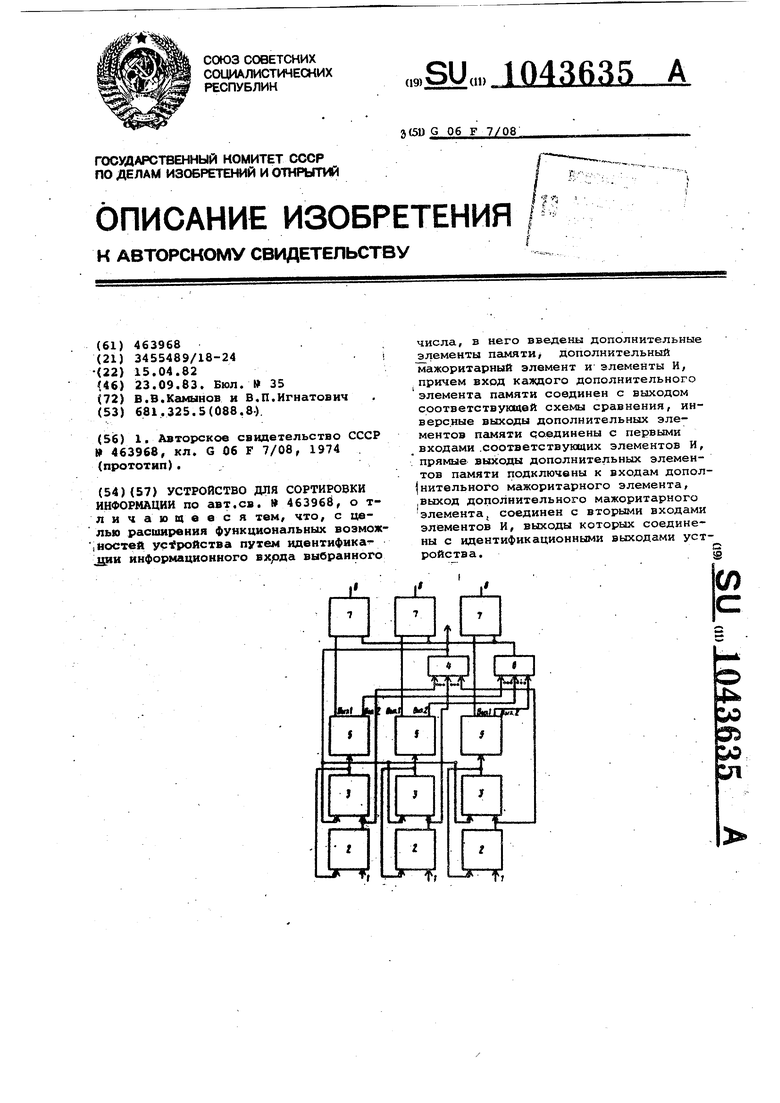

Изобретение относится к автомат ке и вычислительной технике и может быть использовано в автоматизирован ных системах управления и мультипро раммных вычислительных системах. По основному авт.СБ. 463968 из вестно устройство, которое содержит элементы памяти, схемы сравнения и мажоритарный элемент/ причем выходы всех элементов памяти соединены с входами мажоритарного элемента,выход которого соединен- с первыми входами схем сравнения и выходом устройства каждый вход устройства соединен с первым входом соответствующего элемента памяти, выход каждого иэ которых соединен с вторым входом соответ ствующей схемы сравнения, выход каждой схемы сравнения соединен с вторьли входом одноименного элемента памяти 1. . Недостаток известного устройства заключается в невозможности идентифи цировать для вычислительной системы информационный вход, по которому пос тупило в устройство К-е по величине число. Цель изобретения - расширение функциональных возможностей устройст ва путем .идентификации информационно |го входа, по которому поступило в устройство К-е по величине число. Цель достигается .тем, что в устройство введены дополнительные эле-г менты памяти, дополнительный мажоритарный элемент и элементы И-, причем вход каждого дополнительного элемента памяти соединен с выходом соответ ствующей схемы сравнения, инверсные выходы дополнительных элементов памя ти соединены с первыми входами соответствующих элементов И, прямые выходы дополнительных элементов памяти подключены к входам дополнительного мажоритарного элемента, выход дополнительного мажоритарного элемента соединен с вторыми входами элементов И, выходы которых соединены с иденти фикационными выходами устройства. Указанная совокупность элементов и связей позволяет осуществлять иден тификацию информационного входа, по которому поступило в устройство К-е по величине число, путем выделения с помощью дополнительного элемента памяти и элементов И К-й схемы сравнения, на выходе которой не было сиг нала Неравенствоi в момент времени, определяемый дополнительным мажоритарным элементом. На чертеже представлена схема пре лагаемого устройства. Устройство содержит и входов 1, элементы памяти 2,схемы сравнения 3, , мажсэритарный элемент 4 м-к+1 из П , дополнительные элементы 5 памяти, дополнительный мажоритарный элемент 6 n-l из И , элементы И 7 и идентификационные выходы 8. Каждый из входов 1 соединен- с информационным входом соответствующего элемента 2 памяти, а его выход соединен с вторым входом соответствующей схемы 3 сравнения и мажоритарного элемента 4, выход которого подключен к первым входам всех схем 3 сравнения. Выход каждой схемы 3 сравнения соединен с блокировочным входом соответствукяцего элемента памяти и входом соответствующего дополнительного элемента 5 памяти. .Инверс.ные выходы всех дополнительных элементов 5 памяти подключены к первым входам соответствующих элементов 4, а прямые выходы - к входам дополнительного мажоритарного элемента. Выход дополнительного мажоритарного элемента 6 соединен с вторыми входами всех элементов И 7. Выходы элементов И 7 соединены с идентификационными выходами устройства. Устройство работа.ет следующим образом. На входы 1 подаются обрабатываемые числа последовательным двоичным кодом, начиная со старших разрядов. Значения одноименных разрядов всех поступивших чисел запоминаются соответствующими элементами 2 памяти и передаются на входы мажоритарного элемента 4. Если число единиц, поступивших на входы мажоритарного элемента 4, Не меньшеего порога (ll-K+l), на -его выходе формируется также единичное одноименного разряда выходного числа. При невыполнении указанного условия выходное число в данном разряде принимает нулевое значение. Сформированное значение разряда выходного числа подается на один из входов схем 3 сравнения, где производится его сравнение со значениями одноименных разрядов, подаваемыми на входы мажоритарного элемента 4. При неравенстве схема 3 сравнения вырабатывает сигнал, который поступает на блокировочный вход элемента 2 памяти и блокирует в нем прием последующих, разрядов чисед с входа 1 устройства. Элемент памяти независимо от значения последующих разрядов числа, подаваемого на его информационный вход, остается в состоянии, соответствующем значению первого несравнившегося разряда. Вырабатываемый сигнал также поступает на вход дополнительного элемента 5 памяти, устанавливая его по инверсному выходу в состояние О, а по прямому выходу - в состояние I . По мере поступления на входы 1 устройства разрядов обрабатываемых чисел на его выходе формируется последовательность значений К-го по величине числа, а на входы.дополнитель ного мажоритарного элемента б по мере формирования К-го по величине чис Ла поступают единичные сигналы с дополнительных элементов 5 памяти, соответствующих входам 1, по которым передается это число. При достижении порога срабатывания И-1 из п дополнительного мажоритарного элемента б ецциничное значение сохранится на инверсном выходе только у дополнительного элемента 5 памяти, соответствупцего входуД, по которому пе редавсшось К-е число. На выходе мажо ритарного элемента 6 формируется еди ничный сигнал, который открывает эле мент И 7 в случае, если на его пер- вом входе присутствует единичный сиг нал с дополнительнтэго элемента 5 памяти. При этом на выходе 8 элемента И 7, соответствующего входу 1, по ко торому передавалось К-е чиЬло, форми руется сигнал на остальных выходах 8 - сигнал О., Таким образом, введение в устройство дополнительных элементов и связей позволяет .по сравнению с прототипом дополнительно идентифицировать вход, по которому передавалось К-епо величине число, что дает возможность использовать его в мультипрограммных вычислительных процессах для обработки запросов, приоритет которых задается источником запроса в виде последовательного двоичного кода., По сравнению с извёстнЕлм предлагаемое устройство более универсально, так как для расширения диапазона приоритетов в известном устройстве требуется увеличить разрядность регистров и коммутаторов каналов, а в предлагаемом только изменить разрядность поступающего на входы последовательного кода без увеличения оборудования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для сортировки чисел | 1979 |

|

SU792248A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1989 |

|

SU1667280A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1702434A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1989 |

|

SU1709569A1 |

| РЕЗЕРВИРОВАННЫЙ СЧЕТЧИК | 1996 |

|

RU2103815C1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1990 |

|

SU1716628A1 |

| РЕЗЕРВИРОВАННЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1997 |

|

RU2122282C1 |

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

УСТРОЙСТВО ДЛЯ СОРТИРОВКИ ИНФОРМАЦИИ ПО авт.св. 4639бё, о тличающееся тем, что, с целью расширения функциональных возможМюстей устройства путем ндентификаjjHH информационного вхрда выбранного числа, в него введены дополнительные элементы памяти дополнительный мажоритарный элемент и элементы И, причем вход каждого дополнительного элемента памяти соединен с выходом соответствующей схемы сравнения, инверсные выходы дополнительных элементов памяти соединены с первыми входами .соответствующих элементов И, . прямые выходы дополнительных элементов памяти подключены к входам допол|нительного мажоритарного элемента, ,выход дополнительного мажоритарного элементаJ соединен с вторыми входами элементов И, выходы которых соединены с идентификационными выходами устройства,ty (Л 4 :/э z :д

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сортировки информации | 1972 |

|

SU463968A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| (прототип). | |||

Авторы

Даты

1983-09-23—Публикация

1982-04-15—Подача