4i 00 СП

to

Ю

Изобретение относится к области цифровой вычислительной техники и может быть использовано в систе мах прерывания вычислительных систем, в том числе в управляющих вычислительных машинах и комплексах.

Цель изобретения - повышение быстродействия устройства.

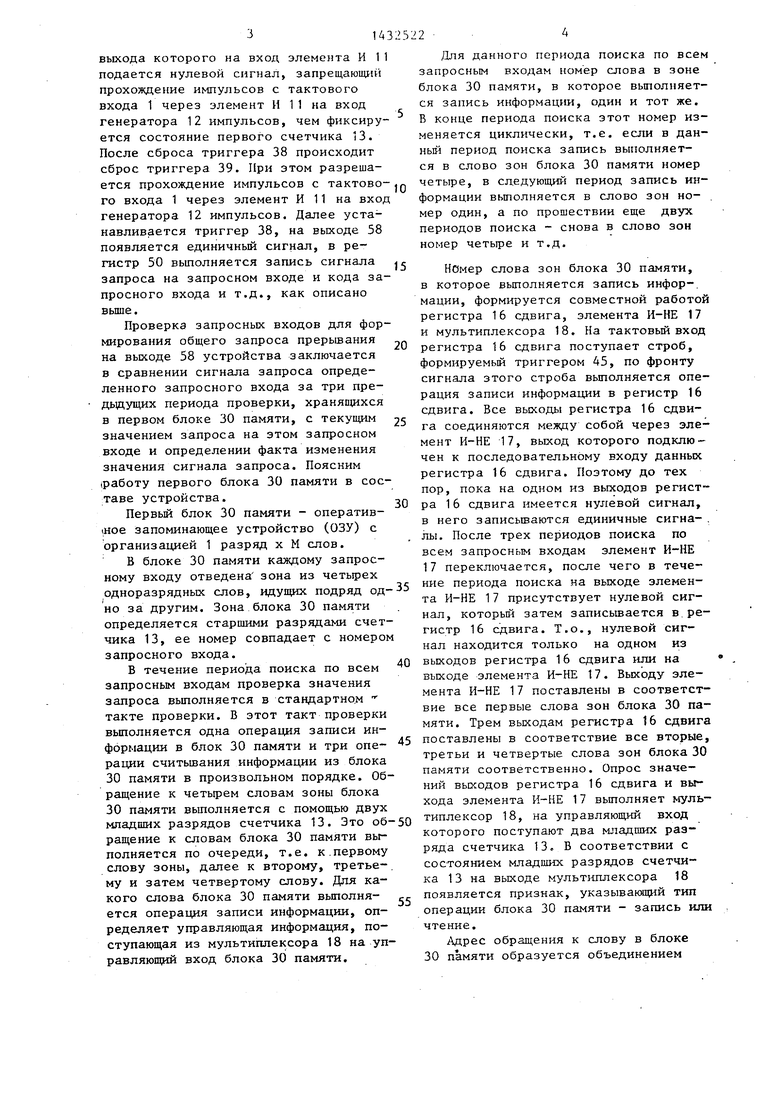

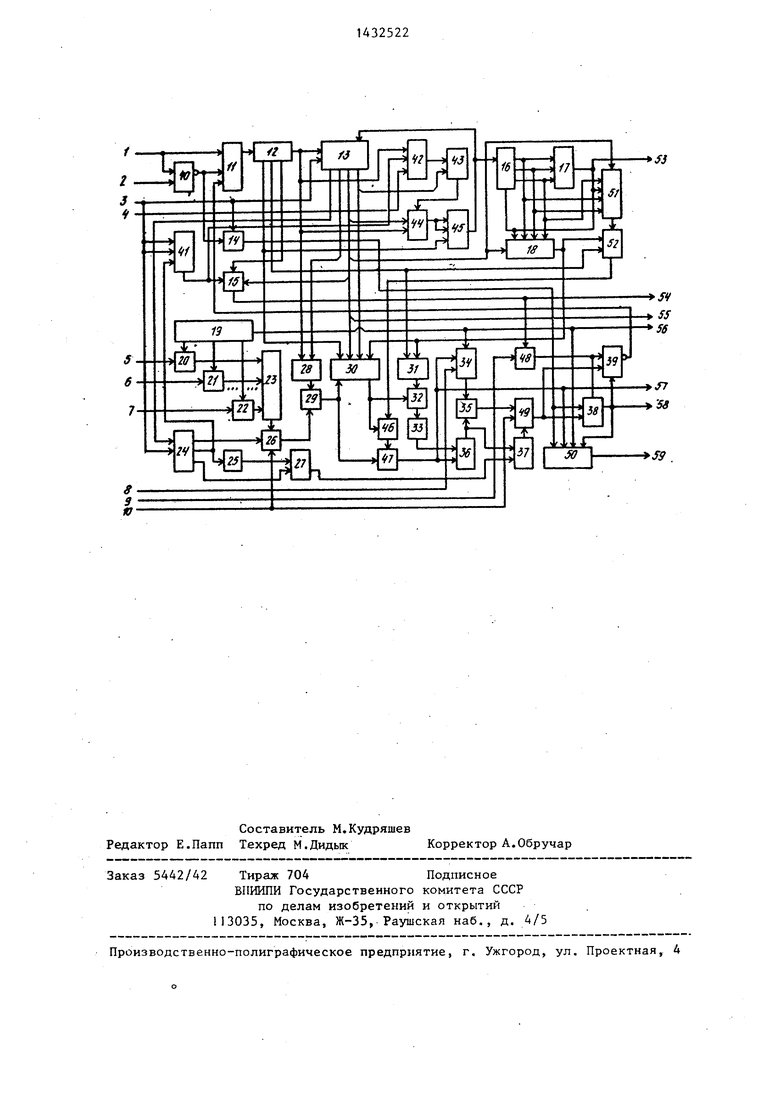

На чертеже приведена структурная схема устройства.

Устройство содержит тактовый вход 1 устройства, вход 2 сброса запроса прерьшания устройства, вход 3 началь

Первый счетчик 13, на который с некоторой частотой поступают импульсы с выхода генератора 12 импульсов, при ПОМ01ДИ дешифратора 19 и элементов И 20-22 группы в каждом такте проверки наличия запроса на группе входов 5-7 проверяет запросный вход группы, номер которого совпадает с содержимым старших разрядов первого счетчика 13, поступающим на вход дешифратора 19 с выхода первого счетчика 13. Эта проверка запросного входа заключается в сравнении значений

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования сигнала прерывания | 1983 |

|

SU1112365A1 |

| Устройство для формирования сигнала прерывания | 1984 |

|

SU1241242A1 |

| Устройство формирования сигнала прерывания и обмена | 1985 |

|

SU1269133A1 |

| Устройство формирования сигнала прерывания | 1985 |

|

SU1290327A1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1550518A1 |

| Устройство для циклического опроса инициативных сигналов | 1988 |

|

SU1599858A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДВИЖЕНИЯ ТРАНСПОРТНЫХ СРЕДСТВ | 1992 |

|

RU2054198C1 |

| Устройство для прерывания программ | 1985 |

|

SU1341636A1 |

| Устройство для ввода информации | 1987 |

|

SU1471187A2 |

| Приоритетное устройство | 1985 |

|

SU1411744A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в системах прерывания вычислительных систем, в том числе в управляющих вычислительных машинах и комплексах. Целью изобретения являетсй повышение быстродействия устройства путем сокращения времени реакции. Устройство содержит, шесть триггеров, три регистра сдвига, два мажоритарных, элемента, четыре мультиплексора,, десять элементов И, два регистра и схему сравнения. В устройстве происходят совмещение во времени поиска следующего запросного входа, содержащего запрос, с вьщачей объекту общего запроса прерывания и установка ограничения на число опрашиваемых запросных входов, упрощение процедуры сброса общеро запроса пре- рьшания и процедуры начального сброса устройства. Кроме того, в устройстве применяется внешняя маска преры- вания параллельно с внутренней маской jg прерьшания и указывается неисправная зона первого блока памяти в режиме самоконтроля. 1 ил. (Л

ного сброса устройства, группу входовj5 сигнала запроса на этом запросном 4 данных устройства, группу запросных входов 5-7 устройства, вход 8 блокировки устройства, вход 9 запрета прерывания устройства, вход 10 режима устаройства, элемент И 11, генератор 20 12 импульсов, счетчик 13, элемент И 14, элемент И 15, регистр 16 сдвига, элемент И-НЕ 17, мультиплексор 18, дешифратор 19, элементы И 20-22 группы, ИЛИ 23, счетчик 24, элемент НЕ 23,25 разрядов первого счетчика 13 и провходе за три предьщущих периода проверки, хранящихся в первом блоке 30 памяти, с текущим значением сигнала запроса на запросном входе и определении факта изменения значения сигнала запроса. Если на данном запросном входе сигнал запроса не изменил значения, то через некоторое время происходит изменение на единицу старших

мультиплексор 26, элемент И 27, элемент И 28, триггер 29, блок памяти 30, элемент И 31, регистр 32 сдвига, мажоритарный элемент З З, блок 34 памяти, элемент И 35, элементы 36 и 37 сложения по модулю два, триггеры 38- 41, параллельньй регистр 42, схему 43 сравнения, элемент И 44, триггер 45, регистр 46 сдвига, мажоритарный элемент 47, элемент И 48, мультиплек30

веряется. следующий по порядку запросный вход. Если обнаружено изменение значения сигнала запроса на данном запросном входе и ранее не бьш установлен триггер 38 (т.е. не было общего запроса прерьшания), то установится триггер 38, на выходе 58 устройства установится единичньй сигнал, в регистр 50 выполняется запись значения сигнала запроса на запросном вхосор 49, регистр 50, мультиплексор 51, 35 (нулевой разряд регистра 50) и коэлемент И 52, выход 53 признака устройства, тактовый выход 54 устройства, группы адресных выходов 55 и 56 устройства, выход 57 разрешения устройства, сигнальный выход 58 устройства, группу кодовых выходов 59 устройства.

Устройство работает в двух .режимах - основном и режиме самоконтроля. Режим работы определяется сигналом, поступающим на вход 10.

При работе в основном режиме выполняется периодический опрос входов 5-7 устройства, входы 5-7 опрашиваются по очереди, последним в периоде опрашивается запросный вход, имеющий порядковый номер, равный коду, занесенному ранее в регистр 42, затем опрос входов 5-7 вьшолняется сначала.

40

45

50

да запросного входа (остальные разряды регистра 50). Значения сигнала запроса и кода запросного входа и выхода регистра 50 поступают на выходы 59 устройства, в дальнейшем они используются для формирования начального адреса программы обслуживания прерывания. Одновременно с этим разрешается работа триггера 39, так как снимается нулевой сигнал с входа сбро са этого триггера. Затем происходит изменение на единицу старших разрядов первого счетчика 13 и проверяется следующий по порядку запросный вход группы 5-7. При этом вьшолняется совмещение поиска следующего запроса прерывания с обслуживанием текущего общего запроса прерывания.

В случае, если обнаружено измене-В основном режиме второй мульти- 55 ние значения сигнала запроса на данплексор 26 коммутирует сигнал с Bbf- хода элемента ИЛИ 23 на вход тригг,е- ра 29.

сигнала запроса на этом запросном разрядов первого счетчика 13 и провходе за три предьщущих периода проверки, хранящихся в первом блоке 30 памяти, с текущим значением сигнала запроса на запросном входе и определении факта изменения значения сигнала запроса. Если на данном запросном входе сигнал запроса не изменил значения, то через некоторое время происходит изменение на единицу старших

веряется. следующий по порядку запросный вход. Если обнаружено изменение значения сигнала запроса на данном запросном входе и ранее не бьш установлен триггер 38 (т.е. не было общего запроса прерьшания), то установится триггер 38, на выходе 58 устройства установится единичньй сигнал, в регистр 50 выполняется запись значения сигнала запроса на запросном вхо (нулевой разряд регистра 50) и ко0

5

0

да запросного входа (остальные разряды регистра 50). Значения сигнала запроса и кода запросного входа и выхода регистра 50 поступают на выходы 59 устройства, в дальнейшем они используются для формирования начального адреса программы обслуживания прерывания. Одновременно с этим разрешается работа триггера 39, так как снимается нулевой сигнал с входа сброса этого триггера. Затем происходит изменение на единицу старших разрядов первого счетчика 13 и проверяется следующий по порядку запросный вход группы 5-7. При этом вьшолняется совмещение поиска следующего запроса прерывания с обслуживанием текущего общего запроса прерывания.

В случае, если обнаружено измене-ном запросном входе и ранее бьш установлен второй триггер 38, то устанавливается триггер 39, с инверсного

выхода которого на вход элемента И 1 подается нулевой сигнал, запрещающий прохождение импульсов с тактового входа 1 через элемент И 11 на вход генератора 12 импульсов, чем фиксируется состояние первого счетчика 13. После сброса триггера 38 происходит сброс триггера 39. При этом разрешается прохождение импульсов с тактового входа 1 через элемент И 11 на вход генератора 12 импульсов. Далее устанавливается триггер 38, на выходе 58 появляется единичньй сигнал, в регистр 50 выполняется запись сигнала запроса на запросном входе и кода запросного входа и т.д., как описано вьше.

Проверка запросных входов для формирования общего запроса прерьшания на выходе 58 устройства заключается в сравнении сигнала запроса определенного запросного входа за три пре- дьщущих периода проверки, храняпщхся в первом блоке 30 памяти, с текугцим значением запроса на этом запросном входе и определении факта изменения значения сигнала запроса. Поясним 1работу первого блока 30 памяти в составе устройства.

Первьй блок 30 памяти - сператив- ное запоминающее устройство (ОЗУ) с организацией 1 разряд х М слов.

В блоке 30 памяти каждому запросному входу отведена зона из четырех одноразрядных слов, идущих подряд одно за другим. Зона блока 30 памяти определяется старшими разрядами счетчика 13, ее номер совпадает с номером запросного входа.

В течение периода поиска по всем запросным входам проверка значения запроса выполняется в стандартном такте проверки. В этот такт проверки выполняется одна операция записи информации в блок 30 памяти и три операции считьшания информации из блока 30 памяти в произвольном порядке. Обращение к четырем словам зоны блока 30 памяти вьшолняется с помощью двух младших разрядов счетчика 13. Это обращение к словам блока 30 памяти выполняется по очереди, т.е. к.первому слову зоны, далее к второму, третьему и затем четвертому слову. Для какого слова блока 30 памяти вьшолня- ется операция записи информации, определяет управляющая информация, поступающая из мультиплексора 18 на управляющий вход блока 30 памяти.

o

5

0

5

0

5

0

5

0

5

Для данного периода поиска по всем запросным входам номер слова в зоне блока 30 памяти, в которое выполняется запись информации, один и тот же. В конце периода поиска этот номер изменяется циклически, т.е. ecjm в данный период поиска запись выполняется в слово зон блока 30 памяти номер четыре, в следующий период запись информации выполняется в слово зон номер один, а по прошествии еще двух периодов поиска - снова в слово зон номер четьфе и т.д.

Номер слова зон блока 30 памяти, в которое выполняется запись инфор-. мации, формируется совместной работой регистра 16 сдвига, элемента И-НЕ 17 и мультиплексора 18. На тактовый вход регистра 16 сдвига поступает строб, формируемый триггером 45, по фронту сигнала этого строба выполняется операция записи информации в регистр 16 сдвига. Все выходы регистра 16 сдвига соединяются между собой через элемент И-НЕ 17, выход которого подключен к последовательному входу даиньос регистра 16 сдвига. Поэтому до тех пор, пока на одном из выходов регистра 16 сдвига имеется нулевой сигнал, в него записываются единичные сигна- , лы. После трех периодов поиска по всем запросным входам элемент И-НЕ 17 переключается, после чего в течение периода поиска на выходе элемента И-НЕ 17 присутствует нулевой сигнал, который затем записьшается в. регистр 16 сдвига. Т.о., НУЛЕВОЙ сигнал находится только на одном из выходов регистра 16 сдвига или на выходе элемента И-НЕ 17. Выходу элемента И-НЕ 17 поставлены в соответствие все первые слова зон блока 30 памяти. Трем выходам регистра 16 сдвига поставлены в соответствие все вторые, третьи и четвертые слова зон блока 30 памяти соответственно. Опрос значений выходов регистра 16 сдвига и вьг- хода элемента И-НЕ 17 выполняет мультиплексор 18, на управляющий вход которого поступают два младших разряда счетчика 13, В соответствии с состоянием младших разрядов счетчика 13 на выходе мультиплексора 18 появляется признак, указывающий тип операции блока 30 памяти - запись или чтение.

Адрес обращения к слову в блоке 30 памяти образуется объединением

5 14325226

младших и старших разрядов счетчи-чения запроса за предьщущие периоды

ка 13.проверки с выхода блока 30 памяти в

Такт проверки изменения значениярегистр 32 сдвига выполняются во врезапроса на запросном входе в данноммя трех операций считьшания информапериоде поиска одинаков для всех зон ции из блока 30 памяти. Управление

блока 30 памяти и состоит из подачизаписью информации в регистр 46 сдвикода запросного входа на дешифраторга с выхода блока 30 памяти обеспе- 19, адресные входы блоков 30 и 34 па-чивают элемент И 52, мультиплексоры

мяти и регистр 50, операции записи 18 и 51. Мультиплексор 51 обеспечиватекущего значения запроса с выходает опрос выходов регистра 16 с цвига

элемента ИЛИ 23 через мультиплексори выхода элемента И-НЕ 17 в иной по26 в триггер 29, четырех операций об-следовательности, чем мультиплексор

ращения к блоку 30 памяти, трех one-18, т.е. начиная с третьего выхода

раций записи значения запроса за трирегистра 16 сдвига, далее опрашивапредыдущих периода проверки в регистрется выход элемента И-НЕ 17 и остав32 сдвига, двух операций записи зна-шиеся выходы регистра 16 сдвига.Данчения запроса за два предьщущих пери гные с выходов мультиплексоров 18 и 51

ода проверки в регистр 46 сдвига,подаются на входы элемента И 52, что

операции сравнения сигналов запросаобеспечивает пропуск двух стробов

20 t f

за четыре периода проверки с помощьюзаписи за такт на вход регистра чо мажоритарных элементов 33 и 47 и эле-сдвига; в результате этого опера- мента сложения по модулю два 36, onerЦии записи значения запроса за пре- . рации записи общего сигнала прерьша-дьщущие периоды проверки с выхода ния с выхода мультиплексора 49, BTpnr-jg блока 30 памяти в регистр 46 выпол- геры 38 и 39.няются во время двух из трех опера- Строб записи информации в триггерции считывания информации из первого 29 формируется элементом И 28 по сов-блока 30 памяти.

падению двух инверсных значений сиг-После четьфех операций обращения нала младших разрядов счетчика 13 блоку 30 памяти выполнена операция строба, присутствующего на первомзаписи значения сигнала запроса в выходе генератора 12 импульсов. С вы-этот блок, что обеспечивает исполь- хода второго элемента И 28 строб пос-зование значения запроса в следую- тупает на тактовый вход триггера 29.щие периоды проверки; в регистре 32 При этом триггер 29 фиксирует значе-имеется трехразрядное слово, содер- ние запроса, поступившее на его ин-35 жащее значение запроса за три преды- формационный вход с выхода мульти-дущих периода проверки, а в регист- плексора 26, на весь такт поиска.ре 46 сдвига - двухразрядное слово, Это обеспечивает возможность асин-содержащее значения запроса за два хронной работы источников запросовпредьщущих периода проверки; прерьшаний и устройства.Для обеспечения вьщеления фронта Информация с выхода триггера 29или среза сигнала на фоне одиночных поступаетна информационньй вход бло-или групповых помех используются мака 30 памяти и вход мажоритарногожоритарные элементы 33 и 37. На пер- элемента 47. Эта информация записы-вьй вход второго мажоритарного эле- вается в блок 30 памяти тогда, когда мента 47 поступает информация выхода с выхода мультиплексора 18 поступаеттриггера 29, на два других входа ма- признак записи в блок 30 памяти.жоритарного элемента 47 поступает ин- После записи значения запроса вформация с выхода регистра 46 сдвига. триггер 29 выполняются четыре one-Информация с трех разрядов регистра рации обращения к блоку 30 памяти, 32 сдвига поступает на три входа ма- каждая из которых сопровождается при-жоритарного элемента 33. Информация знаком записи или считьшания, посту-с выходов мажоритарных элементов 33 пающим из мультиплексора 18. Этоти 47 сравнивается первым элементом признак поступает также на второй36 сложения по модулю два, который вход элемента И 31, при этом запре-55 формирует на выходе сигнал 1 при щается запись информации в регистрнесовпадении сигналов на входах и 32 сдвига во время операции записИ;сигнал О при совпадении. Сигнал в блок 30 памяти. Т.о., операции зна-на выходе элемента 36 сложения по модулю два свидетельствует о наличии фронта или среза сигнала на опрашиваемом запросном входе и необходимости формирования общего запроса прерывания .

Блок 34 памяти - это постоянное запоминающее устройство с организацией 1 разряд X Р слов. Этот блок содержит признаки разрешения форьш- рования общего запроса прерывания по фронту или срезу сигнала запроса,т.е вьшолняется наложение маски. Работа блока 34 памяти может быть запрещена сигналом на входе 8. Для этого на входе 8 устанавливается сигнал 1, что вызьшает появление единичного сигнала на выходе блока 34 памяти и разрешение формирования общего запроса прерьгоания. Если на входе 8 установлен сигнал О, то формируется внутренняя маска прерьшания.

Адрес обращения к слову блока 34 памяти образуется слиянием старших разрядов счетчика 13 и информации на выходе мажоритарного элемента 47. В блоке 34 в слове, соответствующем данной зоне памяти блока 30 и значению запроса, поступившему из мажоритарного элемента 47, хранится информация Разрешено (1) если разрешено формирование общего запроса прерьшания, и Запрет (О) в противном случае.

Элемент И 35 формирует значение сигнала прерывания, которое через мультиплексор 49 поступает на информационные входы триггеров 38 и 39. Строб записи информации в триггеры 38 и 39 формируется элементом И 14 и девятым элементом И 48. Элемент И 14 формирует на своем выходе строб по совпадению единичных сигналов на младших разрядах счетчика 13 и строба, присутствующего на четвертом выходе генератора 12 импульсов, при условии, если установлен триггер 41, т.е. на его выходе сигнал 1. Элемент И 48 формирует строб на выходе, если на входе 8 установлен единичньй сигнал. Триггер 38 устана.вливается по срезу сигнала на выходе девятого элемента И 48. Триггер 39 устанавливается по фронту сигнала на выходе элемента И 48. Триггер 39 устанавливается по фронту сигнала на выходе элемента И 48. Срабатывание триггеров 38 и 39 от разных фронтов строба обеспечивает совмещение появления

0

5

0

общего запроса прерывания с поиском следующего запросного входа, для которого будет сформирован общий запрос прерьшания. При установке триггера 38 разрешается установка триггера 39, так как сигнал с прямого выхода триггера 38 поступает на вход сброса триггера 39 и, так как этот сигнал 1, разрешается его установка. Ранее триггер 38 был сброшен и в силу приоритета входа сброса была запрещена установка триггера 39 сигналом О на входе Сброс триггера 39.

При установке триггера 38 на его выходе формируется общий запрос прерьшания, поступающий на выход 58 устройства, а по фронту этого сигнала в регистр 50 выполняется запись кода запросного входа и значение сигнала запроса на этом входе, вьщеленное на фоне помех. Сигналы с выхода регистра 50 поступают на выходы 59 уст- 5 ройства, при этом на время обращения к программе обработки запроса прерывания фиксируется код запросного входа, содержащего запрос прерьшания.

Если установлен триггер 38, а на выходе мультиплексора 49 имеется еди- ничньм сигнал во время строба на выходе элемента И 48, то устанавливается триггер 39 и запрещает прохождение импульсов тактовой частоты через элемент И 11. Этим фиксируется код следующего запросного входа, содержащего запрос прерывания, для его последующей записи в параллельный регистр 42 после обработки пред ддущего общего запроса прерывания от другого запросного входа.

Для сброса (обнуления) общего заподаетсясигнал 1 де 1

гер 40, выходной сигнал U на инверсном выходе которого, пройдя через элемент И 14, вьшолняет сброс триггера 38 и регистра 50, а также запрещает прохождение импульсов тактовой частоты через элемент И t1, что обеспечивает отсутствие потерь следующих запросов прерьтанш на запросных входах устройства при затягивании сигнала Сброс на входе 2 5 сброса запроса прерывания.

При включении питания узлы устрой- ства находятся в неопределенном состоянии. Поэтому на вход 3 поступает

0

5

0

5

проса прерьшания на вход 2

, по срезу импульса на вхо- устройства устанавливается триг-

О

0

сигнал О, который сбрасывает двоичные счетчики 13 и 24, триггеры 38- 41 и 45, регистры 50 и 42. При сбросе триггера 41 на четыре периода поиска блокируется формирование стробов на выходе элемента И 15 Иj следовательно, блокируется формирование общего запроса прерывания. При этом обеспечивается надежная запись данных в блок 30 памяти, а также повыу шается прои:зводительность устройства за счет более точной привязки начала формирования общего запроса прерывания к моменту завершения заполнения блока 30 памяти и завершению переходного процесса на запросных входах 5-7 устройства.

Для сокращения периода поиска и, следовательно, повьшгения производительности устройства, используется установка уровня опрашиваемых запросных входов. При этом исключаются затраты времени на опрос запросных: входов, коды которых превьш1ают уста- новленньш уровень. Для этого используются регистр 42, схема 43, элемент И 44 и триггер 45.

После подачи сигнала начального сброса на вход 3 сброса триггер 41 сброшен и сброшен регистр 42. После установки триггера 41 разрешается запись данных, присутствуюш 1х на входе 4, в регистр 42. Данные являются двоичным кодом последнего опрашиваемого запросного входа группы запросных входов 5-7. Данные заносятся в регистр 42 по фронту сигнала на первом вьосоде генератора 12 импульсов. Смену данных рекомендуется производить при наличии сигнала низкого уровня на выходе 53, так как это гарантирует-отсутствие ложных общих запросов прерываний Код уровня опрашиваемых запросных входов снимается с выходов регистра 42 и поступает на вторую группу входов схемы 43 сравнения, на первую группу входо которой поступают сигналы старших разрядов счетчика 13. При совпадении кодов сигналов на первой и второй группах входов схема 43 формирует сигнал 1, при не совпадении - сигнал О. При наличии сигналов 1 на выходах младших разрядов счетчика 13, первом выходе генератора 12 импульсов и схемы 43 разрешается установка в единичное состояние триггера 45-, так как на его вход сброса и ин0

5

формационный вход поступает сигнал 1. Триггер 45 устанавливается в единичное состояние по срезу сигнала на втором выходе генератора 12 импульсов, при этом будет сброшен счетчик 13 и выполнена запись данных в регистр 16 сдвига. Триггер 45 уста-, навливается в нулевое состояние по срезу сигнала на первом выходе генератора 12 импульсов.

В ряде задач построения систем прерываний дополнительно к внутренней маске прерывания, формируемой g блоком 34 памяти, требуется формировать внешнюю маску прерывания, запрещая формирование общего запроса пре- рьшания для определенных запросных входов, групп запросных входов или всех запросных входов устройства. Для этого используется вход 9 прерывания, адресные выходы 56 и 55 устройства и выход 57 устройства. Сигнал запрета подается на вход 9 прерывания в соответствии с адресом зоны блока 30 памяти, где хранятся значения .сигналов запросного входа и значения сигнала на этом запросном входе аналогично формировании маски блоком

34памяти.

При работе в режиме самоконтроля устройство функционирует следующим образом. На вход 10 режима ус тройст- ва подается 1, которая задает режим самоконтроля, переключает мультиплек- соры 26 и 46 на коммутацию эталонной информации, .

В этом режиме мультиплексор 26 запрещает прохождение сигнала с выхода элемента ИЛИ 23 на вход триггера 29 и разрешает передачу эталонного сигнала с первого выхода счетчика 24 на вход триггера 29.

Теперь устройство формирует сигнал прерьшания на выходе элемента И

35в соответствии с эталонным, периодически меняющим полярность, сигналом на первом выходе счетчика 24, которьй служит имитатором входных сигналов

на запросных входах устройства. 0

Формула изобретения

Устройство для формирования сигнала прерьшания, содержащее элемент 5 НЕ, семь элементов И, два счетчика, дешифратор, группу элементов И, элемент ИЖ, генератор тактовых импульсов, три триггера, два блока памяти.

D

0

5

11

два регистра сдвига, элемент И-НЕ, два мультиплексора, первьй мажори- тарньй элемент, два элемента сложения по модулю два, причем первый вход первого элемента И соединен с тактовым входом устройства, выходы старших разрядов первого счетчика соединены с входами дешифратора, с первой группой адресных выходов устройства, с первой группой входов адреса первого и второго блоков памяти, выход переполнения первого счетчика соединён со счетным входом второго счетчика, выходы мпадших разрядов первого счетчика соединены с соответствующими входами второго элемента И, с второй группой входов адреса первого блока памяти и с адресными входами первого мультиплексора, первый выход генератора импульсов соединен с первыми входом третьего элемента И, инверсные выходы младших разрядов первого счетчика соединены с соответствующими входами третьего элемента И, второй выход, генератора

.импульсов соединен с тактовым входом первого блока памяти, третий выход генератора импульсов соединен с вторым входом второго элемента И, каж- дьй выход дешифратора соединен с первым входом одноименного элемента И группы, вторые входы элементов И группы соединены с одноименными запросными входами устройства, выходы элементов И группы соединены с входами элемента ИЛИ, выход третьего элемента И соединен с тактовым входом первого триггера, выход первого триггера соединен с информационным входом первого блока памяти, выход первого блока памяти соединен с информационным входом первого регистра сдвига, первьм, второй и третий выходы второго регистра сдвига соединены

,с первым, вторым и третьим входами элемента И-НЕ, с первым, вторым и третьим информационными входами первого мультиплексора соответственно, выход элемента И-НЕ соединен с входом данных второго регистра сдвига и с четвертым информационным входом первого мультиплексора, выход первого мультиплексора соединен с входом управления записью первого блока па-

входом первого элемента сложения по модулю два, выход второго блока памяти соединен с первым входом четве того элемента И, выход первого элемента сложения по модулю два соединен с вторым входом четвертого элемента И, выход второго триггера является сигнальным выходом устройст5

10

15

20

25

30

35

40

45

50

ва, первый вход пятого элемента И с единен с входом начального сброса устройства, управляюпцш вход второг мультиплексора соединен с входом ре жима устройства, первый разрядный выход второго счетчика соединен с nepBbfi i информационным входом второго мультиплексора, выход элемента ИЛИ соединен с вторым информационнь входом второго мультиплексора, выхо второго мультиплексора соединен с и формационным входом первого триггер второй разрядньй выход второго счет чика соединен с входом элемента НЕ, третий разрядньй выход второго счет чика соединен с первым входом шесто го элемента И, выход элемента НЕ со динен с вторым входом шестого элеме та И, выход шестого элемента И сое динен с первым входом второго элеме та сложения по модулю два, выход пя того .элемента И соединен с входом сброса второго триггера, отличающееся тем, что, с целью повышения быстродействия устройства в него введены четвертьй, пятый и шестой триггеры, третий регистр сдв га, второй мажоритарньй элемент, тр тий и четвертьй мультиплексоры, вос мой, девятьй и десятьй элементы И, первьй и второй регистры и схема ср нения, причем тактовьй вход третьег триггера соединен с тактовым входом устройства,- выход первого элемента соединен с входом запуска генератор импульсов, выходы старших разрядов первого счетчика соединены с группой информационных входов первого регис ра и с первой группой входов схемы сравнения, выходы младших разрядов первого счетчика соединены с адрес ными входами третьего мультиплексора, с соответствующими входами вось мого элемента И и являются второй группой адресных выходов устройства первьй выход генератора импульсов

выходы первого регистра сдвига соединен со счетньгм входом первого

мяти,

соединены с входами первого мажоритарного элемента, выход первого мажоритарного элемента соединен с первым

счетчика, с тактовым входом второго регистра и с соответствующим входо седьмого элемента И, четвертьй выхо

входом первого элемента сложения по модулю два, выход второго блока памяти соединен с первым входом четвертого элемента И, выход первого элемента сложения по модулю два соединен с вторым входом четвертого элемента И, выход второго триггера является сигнальным выходом устройст5

ва, первый вход пятого элемента И соединен с входом начального сброса устройства, управляюпцш вход второго мультиплексора соединен с входом режима устройства, первый разрядный выход второго счетчика соединен с nepBbfi i информационным входом второго мультиплексора, выход элемента ИЛИ соединен с вторым информационньм входом второго мультиплексора, выход второго мультиплексора соединен с информационным входом первого триггера, второй разрядньй выход второго счетчика соединен с входом элемента НЕ, третий разрядньй выход второго счетчика соединен с первым входом шестого элемента И, выход элемента НЕ соединен с вторым входом шестого элемента И, выход шестого элемента И соединен с первым входом второго элемента сложения по модулю два, выход пятого .элемента И соединен с входом сброса второго триггера, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены четвертьй, пятый и шестой триггеры, третий регистр сдвига, второй мажоритарньй элемент, третий и четвертьй мультиплексоры, восьмой, девятьй и десятьй элементы И, первьй и второй регистры и схема сравнения, причем тактовьй вход третьего триггера соединен с тактовым входом устройства,- выход первого элемента И соединен с входом запуска генератора импульсов, выходы старших разрядов первого счетчика соединены с группой информационных входов первого регисг- ра и с первой группой входов схемы сравнения, выходы младших разрядов первого счетчика соединены с адресными входами третьего мультиплексора, с соответствующими входами восьмого элемента И и являются второй группой адресных выходов устройства, первьй выход генератора импульсов

соединен со счетньгм входом первого

счетчика, с тактовым входом второго регистра и с соответствующим входом седьмого элемента И, четвертьй выход

генератора импульсов соединен с первыми входами восьмого и девятого элементов И, выход первого триггера соединен с первым входом второго мажоритарного элемента, выход первого блока памяти соединен с информационным входом третьего регистра сдвига, первый, второй и третий выходы второго регистра сдвига соединены с первым, вторым и третьим информационными дами третьего мультиплексора, выход элемента И-НЕ соединен с четвертым информационным входом третьего мультиплексора и является выходом признака устройства, выход первого мультиплексора соединен с вторыми входами восьмого и девятого элементов И, выход третьего мультиплексора соединен с третьим входом девятого элемента И, выход первого элемента сложения п модулю два соединен с вторым- входом второго элемента сложения по модулю два, выход второго триггера соедине с входом сброса четвертого триггера и тактовым входом первого регистра, управляющий вход четвертого мультиплексора соединен с входом режима устройства, вход управления чтением второго блока памяти соединен с входом блокировки устройства, второй разрядньм выход второго счетчика соединен с тактовым входом пятого триггера, выход пятого элемента И соединен с входом сброса первого регистра, выходы первого регистра являются группой кодовьк выходов устройства, выход девятого элемента И соединен с тактовым входом третьего регистра сдвига, выход восьмого элемента И соединен с тактовым входом первого регистра сдвига, выход третьего регистра сдвига соединен с вторым входом второго мажоритарного элемента, выход четвертого элемента И соединен с первым информационным входом четвертого мультиплексора, выход второго элемента сложения по модулю два соединен с вторым информационным входом четвертого мульти0

5

5

0

5

0

5

плексора, выход четвертого мультиплексора соединен с информационными входами второго и четвертого триггеров, инверсный выход четвертого триггера соединен с вторым входом первого элемента И, выход второго мажоритарного элемента соединен с . вторым адресным входом второго блока памяти, с вторым входом второго элемента сложения по модулю два, с со -- ответствующим входом группы инфорна- .иионньк входов первого регистра и является вьгходом разрешения устройства, вход сброса прерывания устройства соединен с информационным входом третьего триггера, выход которого соединен с третьим входом первого элемента И и с вторым входом пятого элемента И, вход сброса и информационный вход пятого триггера, первый вход сброса первого счетчика и вход сброса второго счетчика соединены с входом начального сброса устройства, выход пятого триггера соединен с третьим входом второго элемента И и с входом сброса второго регистра, выход второго элемента И соединен с первым входом десятого элемента И и является тактовым вьрсодом устройства, вход запрета прерывания устройства соединен с вторьм входом десято- го элемента И, выход десятого элемента И соединен с тактовым входом второго триггера и тактовым входом четвертого триггера, группа входов данных устройства соединена с группой информационных входов второго регистра, выходы второго регистра соединены с второй группой входов схемы сравнения, выход схемы сравнения соединен с третьим входом седьмого элемента И, выход седьмого элемента И соединен с входом сброса и информационным входом шестого триггера, выход шестого триг-. гера соединен с тактовым входом второго регистра сдвига и вторым входом сброса первого счетчика, тактовьй вход шестого триггера соединен с вторым выходом генератора импульсов.

Л

/

| Устройство формирования сигнала прерывания | 1983 |

|

SU1112365A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования сигнала прерывания | 1984 |

|

SU1241242A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-23—Публикация

1987-04-20—Подача