Изобретение относится к автоматике и вычислительной технике и может, быть использовано при построении резервированных автоматических систем управления повышенной точности, в частности в системах обработки и передачи служебной и измерительной информации.

Цель изобретения - расширение области применения устройства путем обеспече- ния обработки асинхронных кодовых сообщений переменной длины.

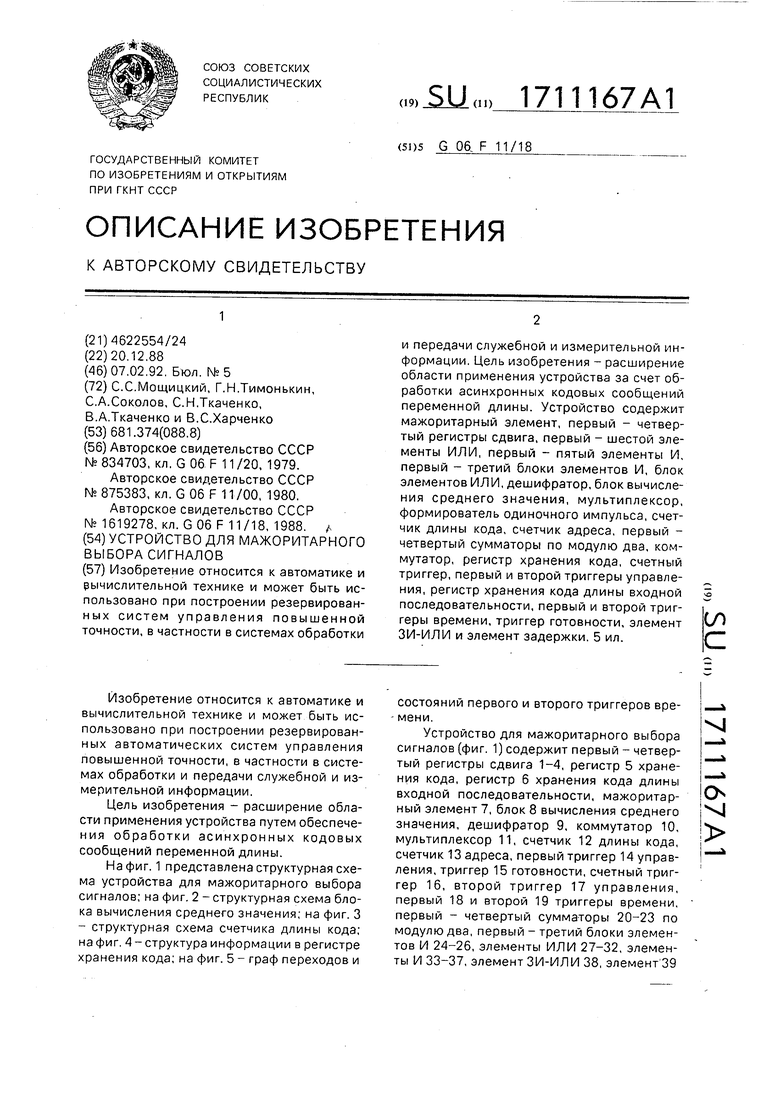

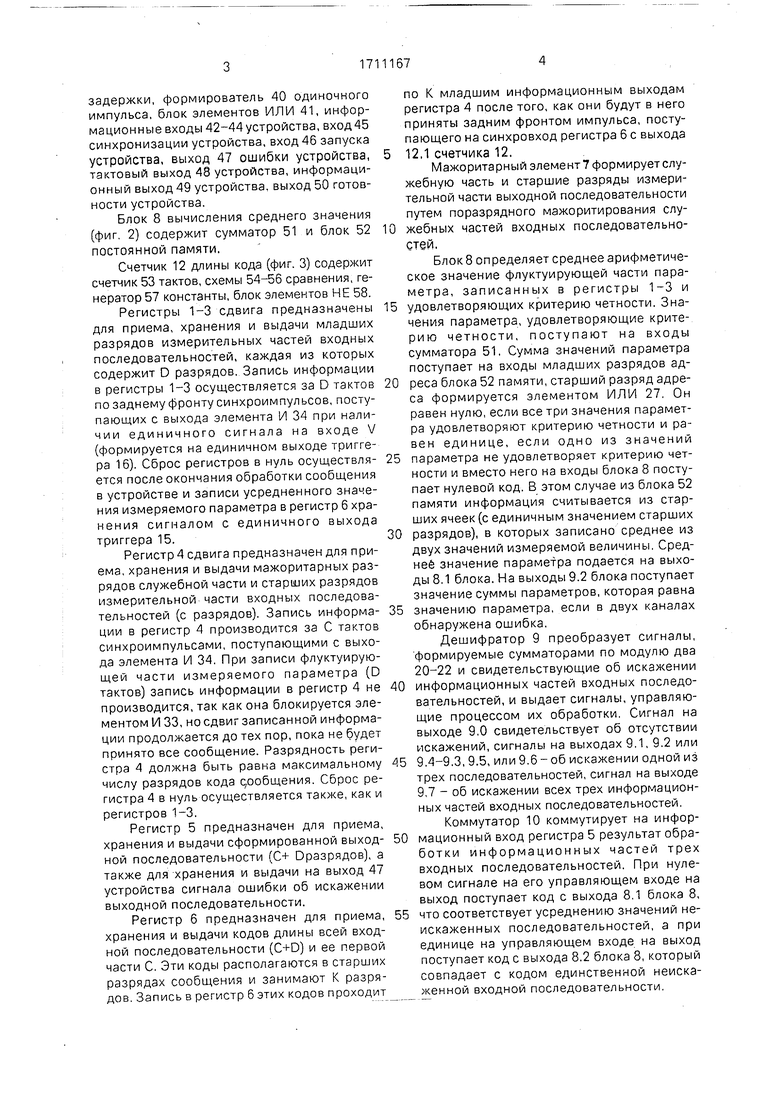

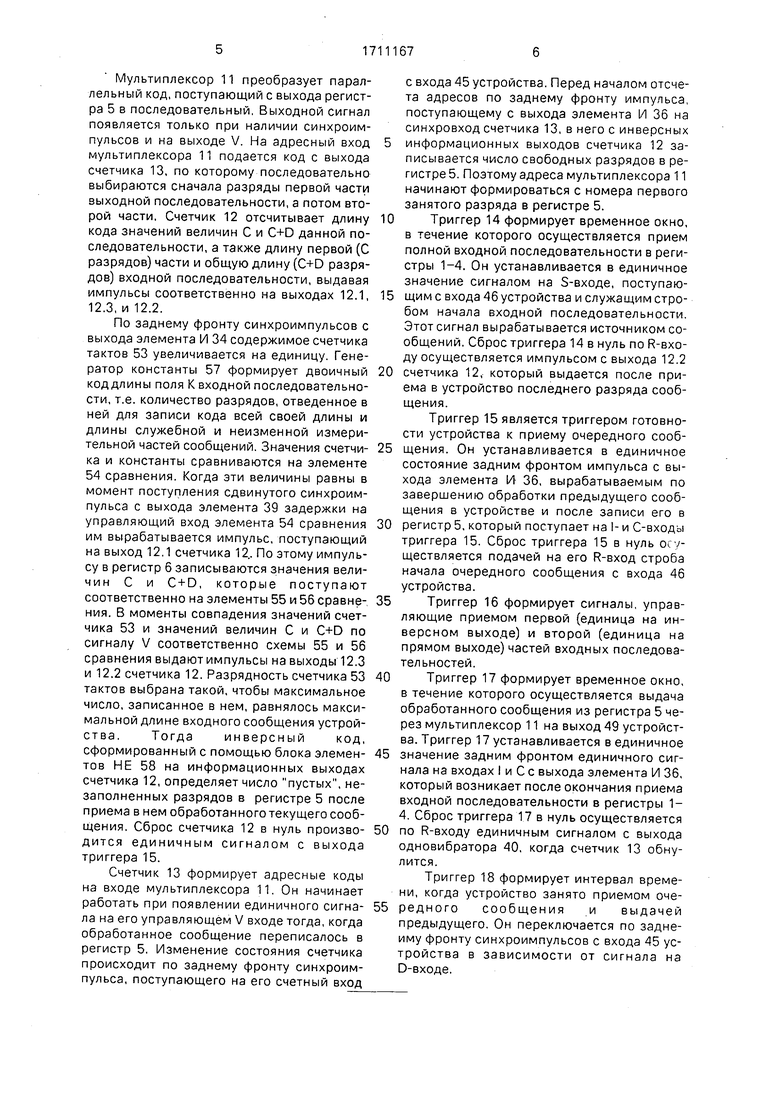

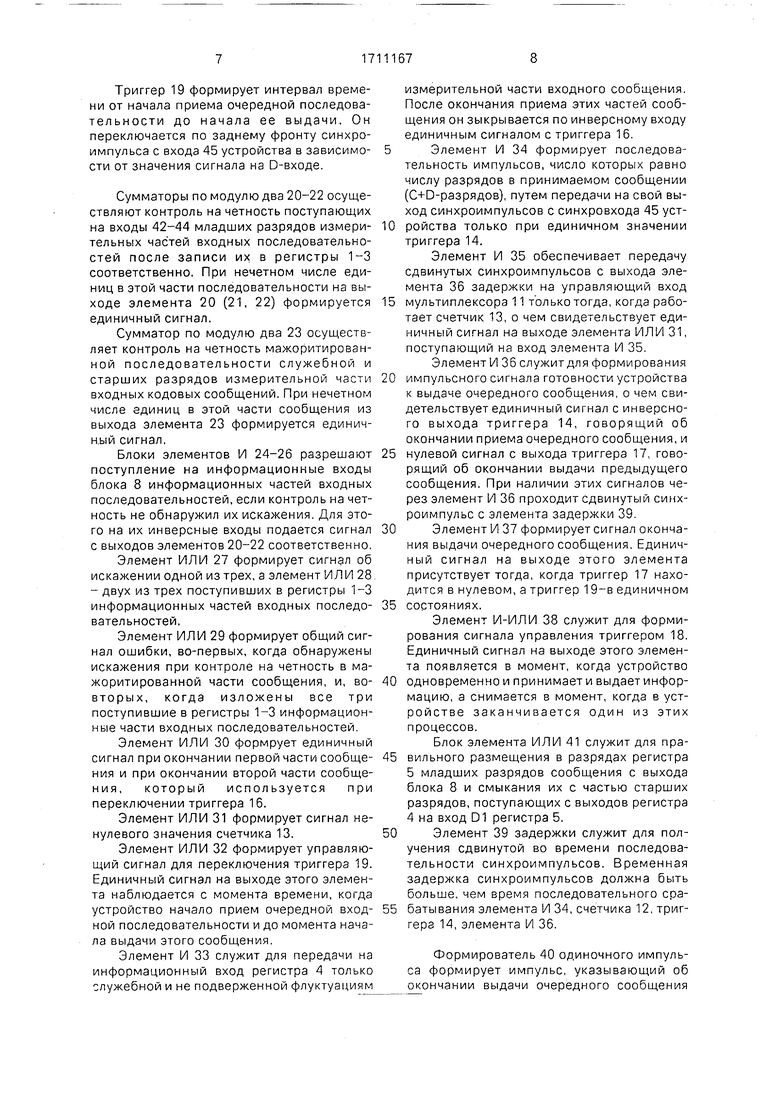

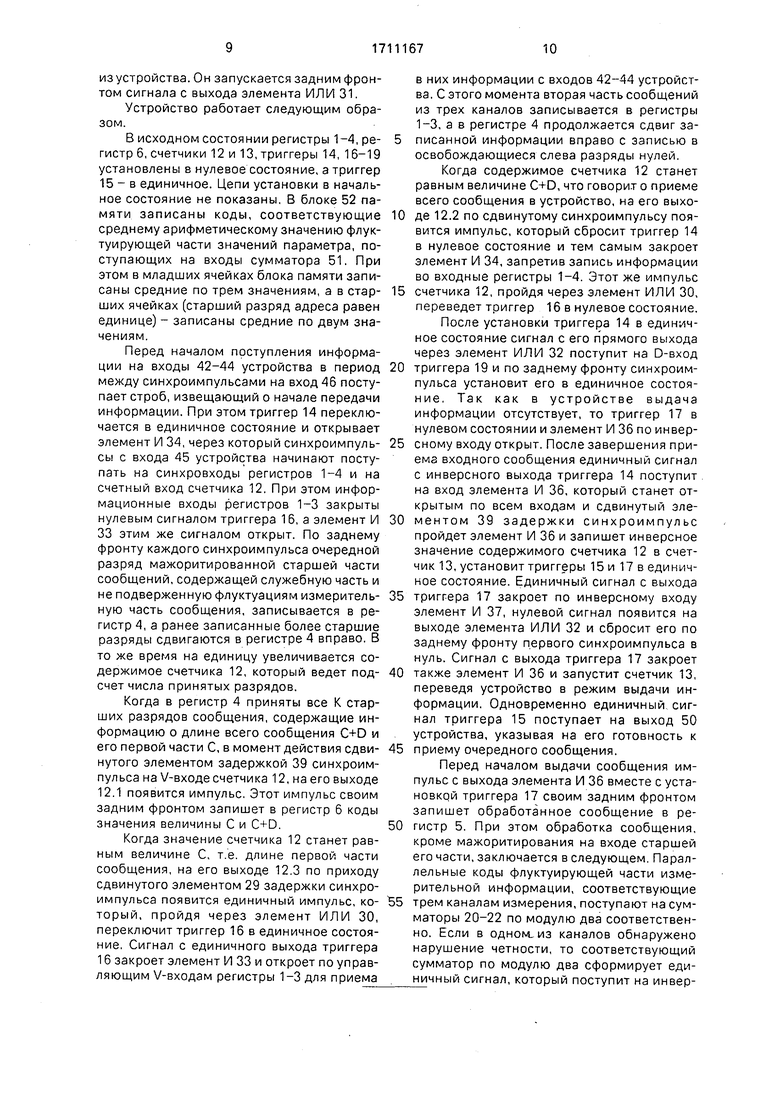

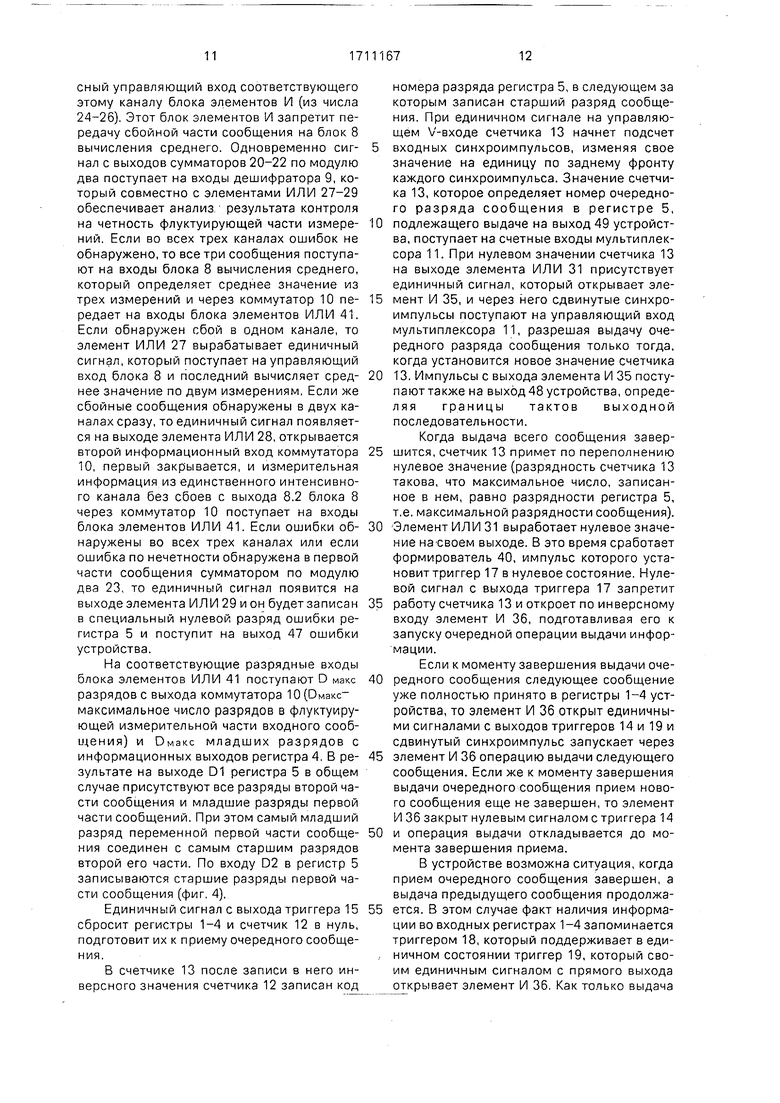

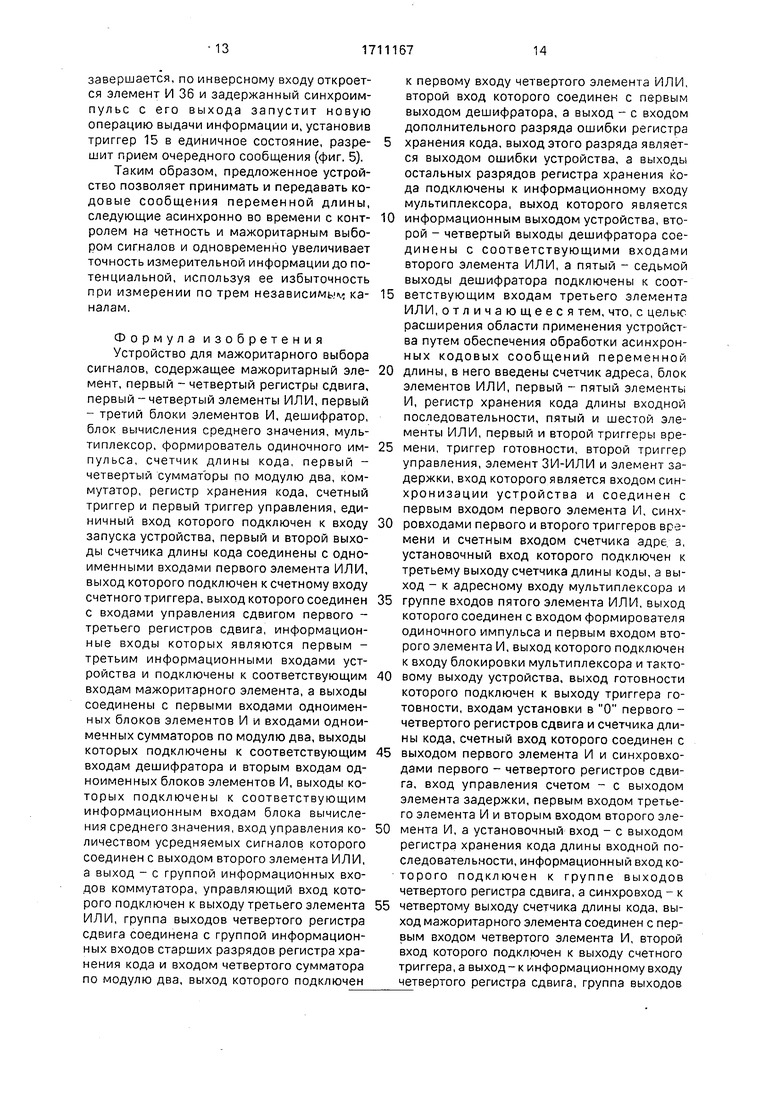

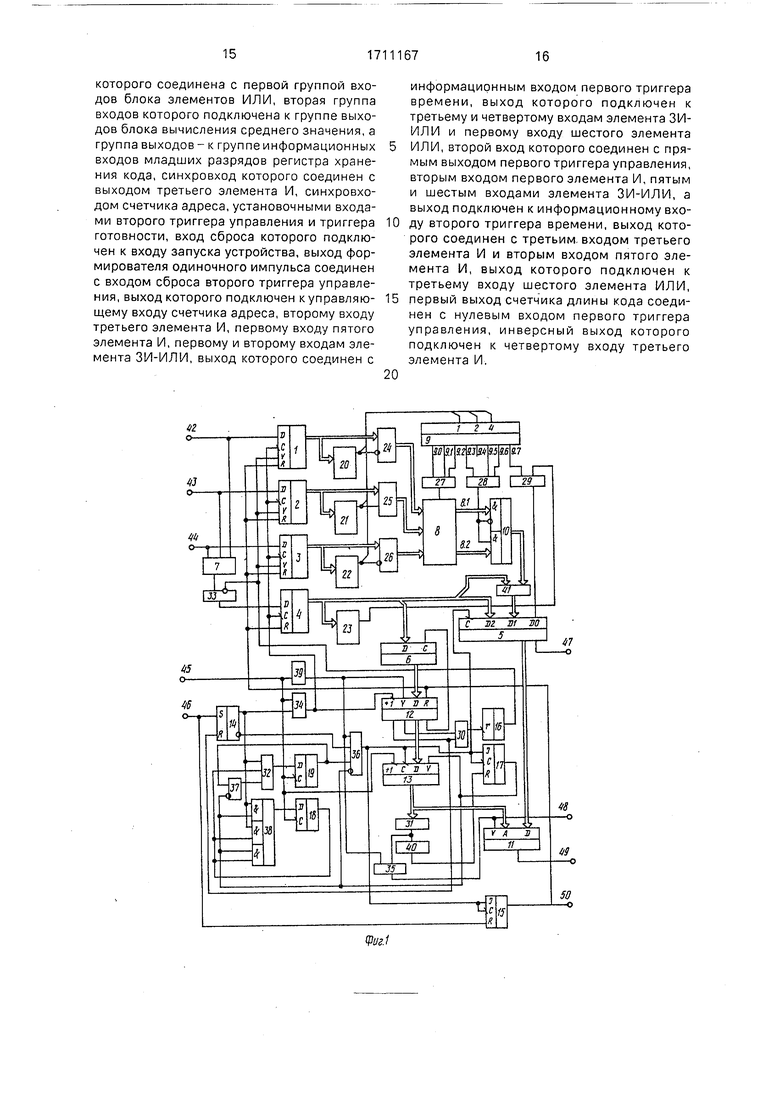

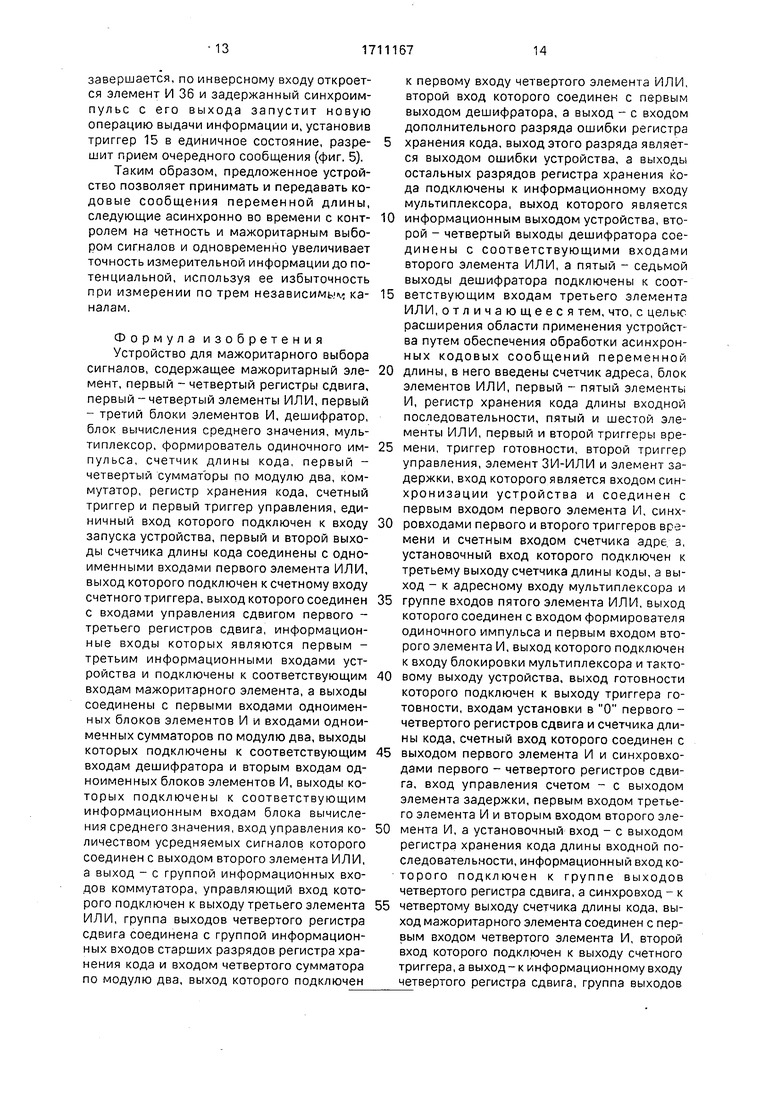

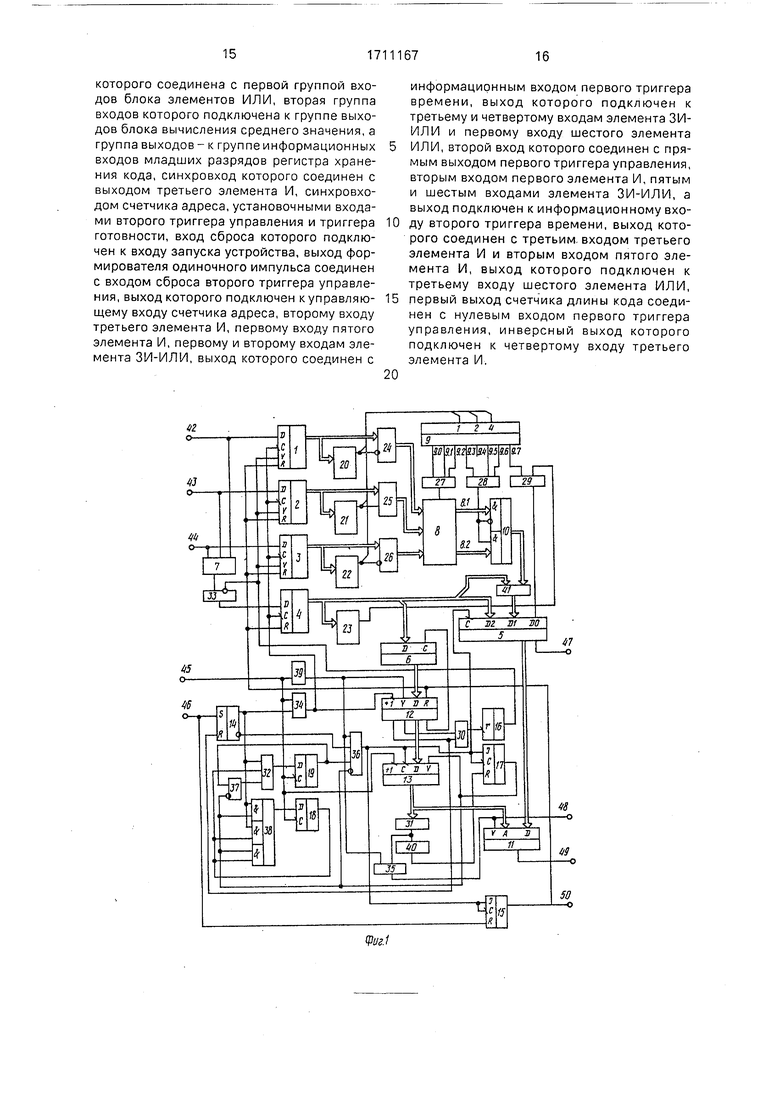

На фиг. 1 представлена структурная схема устройства для мажоритарного выбора сигналов; на фиг. 2 - структурная схема блока вычисления среднего значения; на фиг. 3 - структурная схема счетчика длины кода; на фиг. 4 - структура информации в регистре хранения кода; на фиг. 5 - граф переходов и

состояний первого и второго триггеров вре- - мени.

Устройство для мажоритарного выбора сигналов (фиг. 1) содержит первый - четвертый регистры сдвига 1-4, регистр 5 хранения кода, регистр 6 хранения кода длины входной последовательности, мажоритарный элемент 7, блок 8 вычисления среднего значения, дешифратор 9, коммутатор 10, мультиплексор 11, счетчик 12 длины кода, счетчик 13 адреса, первый триггер 14 управления, триггер 15 готовности, счетный триггер 16, второй триггер 17 управления, первый 18 и второй 19 триггеры времени, первый - четвертый сумматоры 20-23 по модулю два, первый - третий блоки элементов И 24-26, элементы ИЛИ 27-32, элементы И 33-37, элемент ЗИ-ИЛИ 38, элемент- ЗЭ

О

1

задержки, формирователь 40 одиночного импульса, блок элементов ИЛИ 41, информационные входы 42-44 устройства, вход 45 синхронизации устройства, вход 46 запуска устройства, выход 47 ошибки устройства, тактовый выход 48 устройства, информационный выход 49 устройства, выход 50 готовности устройства.

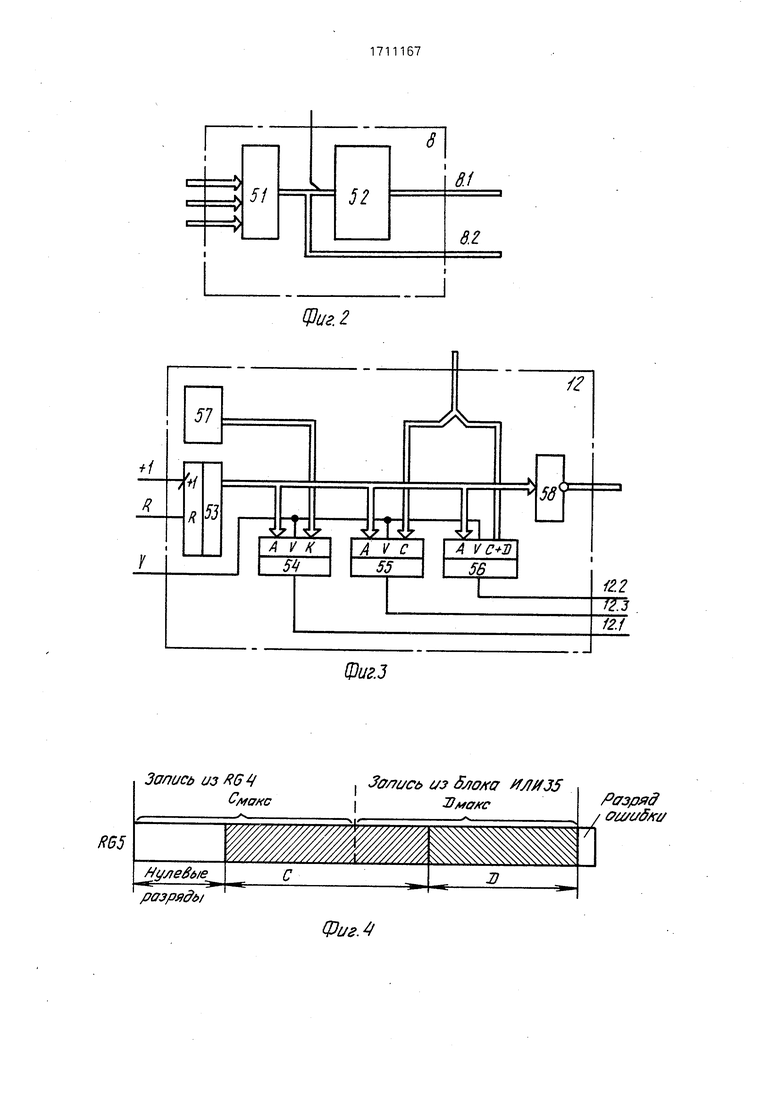

Блок 8 вычисления среднего значения (фиг. 2) содержит сумматор 51 и блок 52 постоянной памяти.

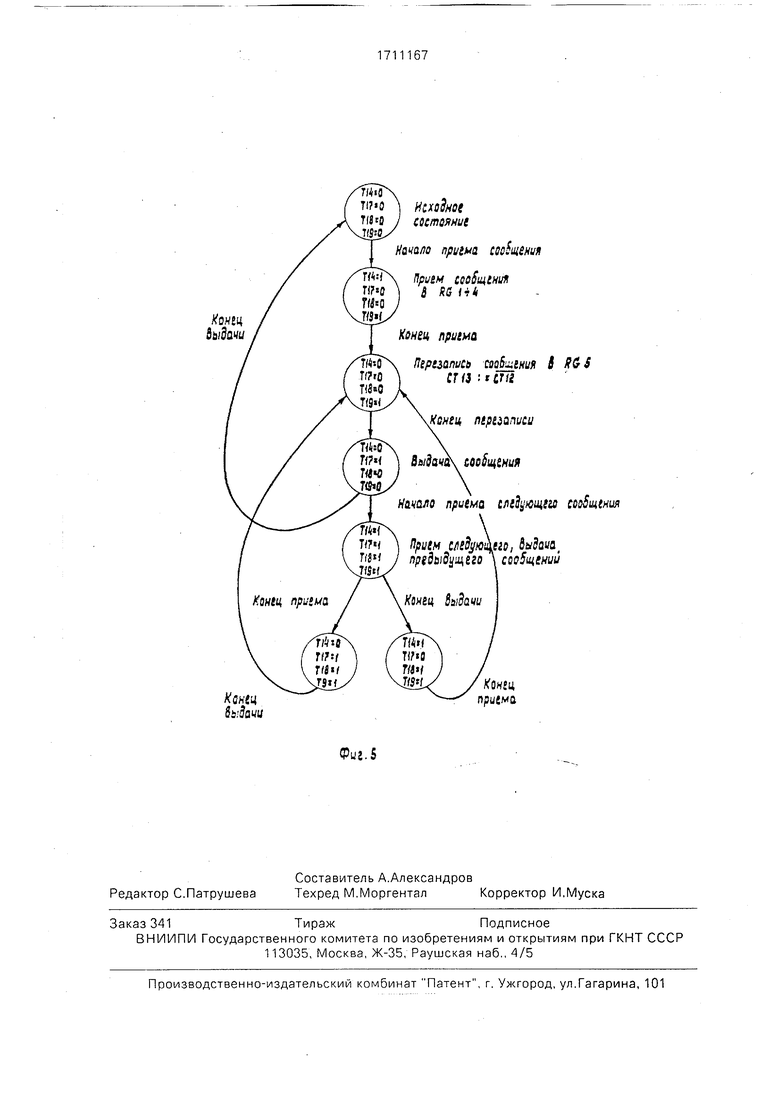

Счетчик 12 длины кода (фиг. 3) содержит счетчик 53 тактов, схемы 54-56 сравнения, генератор 57 константы, блок элементов НЕ 58.

Регистры 1-3 сдвига предназначены для приема, хранения и выдачи младших разрядов измерительных частей входных последовательностей, каждая из которых содержит D разрядов..Запись информации в регистры 1-3 осуществляется за D тактов по заднему фронту синхроимпульсов, поступающих с выхода элемента И 34 при наличии единичного сигнала на входе V (формируется на единичном выходе триггера 16). Сброс регистров в нуль осуществля- ется после окончания обработки сообщения в устройстве и записи усредненного значения измеряемого параметра в регистр 6 хра- нения сигналом с единичного выхода триггера 15.

Регистр 4 сдвига предназначен для приема, хранения и выдачи мажоритарных разрядов служебной части и старших разрядов измерительной.части входных последовательностей (с разрядов). Запись информа- ции в регистр 4 производится за С тактов синхроимпульсами, поступающими с выхода элемента И 34. При записи флуктуирующей части измеряемого параметра (D тактов) запись информации в регистр 4 не производится, так как она блокируется элементом И 33, носдвигзаписанной информации продолжается до тех пор, пока не будет принято все сообщение. Разрядность регистра 4 должна быть равна максимальному числу разрядов кода с/зобщения. Сброс регистра 4 в нуль осуществляется также, как и регистров 1-3.

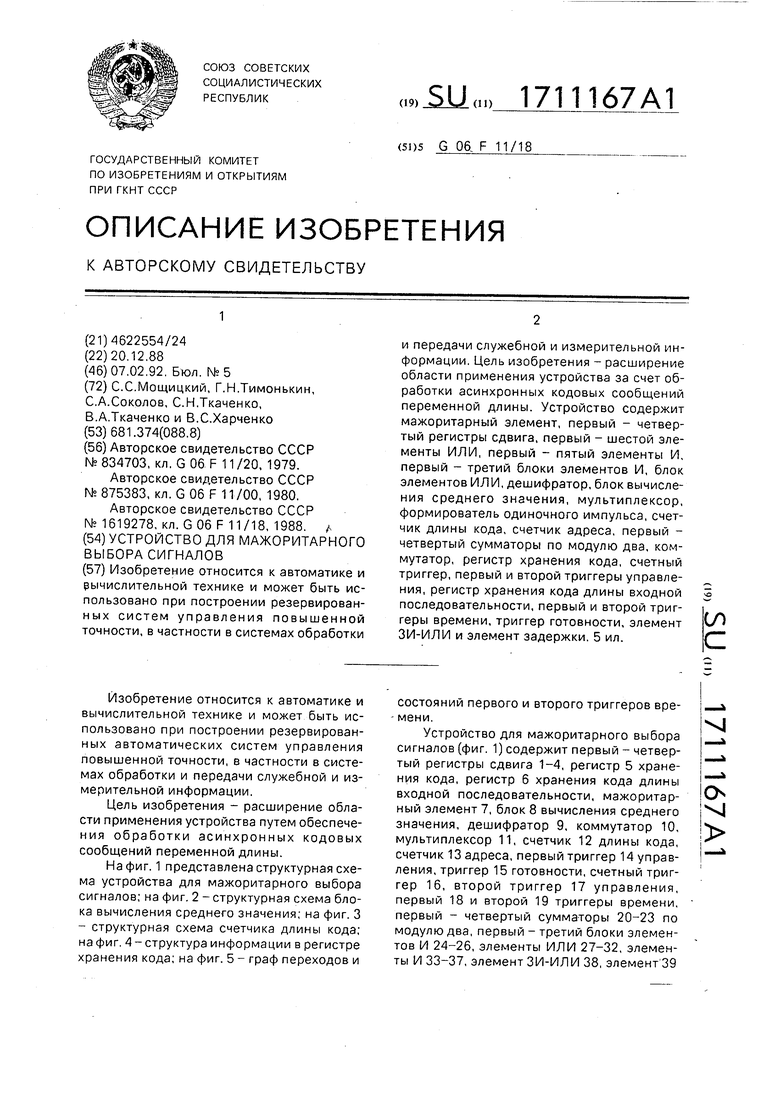

Регистр 5 предназначен для приема, хранения и выдачи сформированной выход- ной последовательности (С+ Оразрядов), а также для хранения и выдачи на выход 47 устройства сигнала ошибки об искажении выходной последовательности.

Регистр 6 предназначен для приема, хранения и выдачи кодов длины всей входной последовательности (C+D) и ее первой части С. Эти коды располагаются в старших разрядах сообщения и занимают К разрядов. Запись в регистр 6 этих кодов проходит

по К младшим информационным выходам регистра 4 после того, как они будут в него приняты задним фронтом импульса, поступающего на синхровход регистра 6 с выхода 12,1 счетчика 12.

Мажоритарный элемент 7 формирует служебную часть и старшие разряды измерительной части выходной последовательности путем поразрядного мажоритирования служебных частей входных последовательностей.

Блок 8 определяет среднее арифметическое значение флуктуирующей части параметра, записанных в регистры 1-3 и удовлетворяющих критерию четности. Значения параметра, удовлетворяющие Крите-, рию четности, поступают на входы сумматора 51. Сумма значений параметра поступает на входы младших разрядов адреса блока 52 памяти, старший разряд адреса формируется элементом ИЛИ 27. Он равен нулю, если все три значения параметра удовлетворяют критерию четности и равен единице, если одно из значений параметра не удовлетворяет критерию четности и вместо него на входы блока 8 поступает нулевой код. В этом случае из блока 52 памяти информация считывается из старших ячеек (с единичным значением старших разрядов), в которых записано среднее из двух значений измеряемой величины. Среднее значение параметра подается на выходы 8.1 блока. На выходы 9.2 блока поступает значение суммы параметров, которая равна значению параметра, если в двух каналах обнаружена ошибка.

Дешифратор 9 преобразует сигналы, формируемые сумматорами по модулю два 20-22 и свидетельствующие об искажении информационных частей входных последовательностей, и выдает сигналы, управляющие процессом их обработки. Сигнал на выходе 9.0 свидетельствует об отсутствии искажений, сигналы на выходах 9.1, 9.2 или 9.4-9.3,9.5, или 9.6 - об искажении одной из трех последовательностей, сигнал на выходе 9,7 - об искажении всех трех информационных частей входных последовательностей.

Коммутатор 10 коммутирует на информационный вход регистра 5 результат обработки информационных частей трех входных последовательностей. При нулевом сигнале на его управляющем входе на выход поступает код с выхода 8.1 блока 8, что соответствует усреднению значений неискаженных последовательностей, а при единице на управляющем входе,, на выход поступает код с выхода 8.2 блока 8, который совпадает с кодом единственной неискаженной входной последовательности.

Мультиплексор 11 преобразует параллельный код, поступающий с выхода регистра 5 в последовательный. Выходной сигнал появляется только при наличии синхроимпульсов и на выходе V. На адресный вход мультиплексора 11 подается код с выхода счетчика 13, по которому последовательно; выбираются сначала разряды первой части выходной последовательности, а потом второй части. Счетчик 12 отсчитывает длину кода значений величин С и C+D данной последовательности, а также длину первой (С разрядов) части и общую длину (C+D разрядов) входной последовательности, выдавая импульсы соответственно на выходах 12.1, 12.3, и 12.2.

По заднему фронту синхроимпульсов с выхода элемента И 34 содержимое счетчика тактов 53 увеличивается на единицу. Генератор константы 57 формирует двоичный код длины поля К входной последовательности, т.е. количество разрядов, отведенное в ней для записи кода всей своей длины и длины служебной и неизменной измерительной частей сообщений. Значения счетчика и константы сравниваются на элементе 54 сравнения. Когда эти величины равны в момент поступления сдвинутого синхроимпульса с выхода элемента 39 задержки на управляющий вход элемента 54 сравнения им вырабатывается импульс, поступающий на выход 12.1 счетчика 12.. По этому импульсу в регистр 6 записываются значения величин С и C+D, которые поступают соответственно на элементы 55 и 56 сравнения. В моменты совпадения значений счетчика 53 и значений величин С и OD по сигналу V соответственно схемы 55 и 56 сравнения выдают импульсы на выходы 12.3 и 12.2 счетчика 12. Разрядность счетчика 53 тактов выбрана такой, чтобы максимальное число, записанное в нем, равнялось максимальной длине входного сообщения устройства. Тогда инверсный код, сформированный с помощью блока элементов НЕ 58 на информационных выходах счетчика 12, определяет число пустых, незаполненных разрядов в регистре 5 после приема в нем обработанного текущего сообщения. Сброс счетчика 12 в нуль производится единичным сигналом с выхода триггера 15.

Счетчик 13 формирует адресные коды на входе мультиплексора 11. Он начинает работать при появлении единичного сигнала на его управляющем V входе тогда, когда обработанное сообщение переписалось в регистр 5. Изменение состояния счетчика происходит по заднему фронту синхроимпульса, поступающего на его счетный вход

с входа 45 устройства. Перед началом отсчета адресов по заднему фронту импульса, поступающему с выхода элемента И 36 на синхровход счетчика 13, в него с инверсных

информационных выходов счетчика 12 записывается число свободных разрядов в регистре 5. Поэтому адреса мультиплексора 11 начинают формироваться с номера первого занятого разряда в регистре 5.

Триггер 14 формирует временное окно, в течение которого осуществляется прием полной входной последовательности в регистры 1-4. Он устанавливается в единичное значение сигналом на S-входе, поступающим с входа 46 устройства и служащим стробом начала входной последовательности. Этотсигнал вырабатывается источником сообщений. Сброс триггера 14 в нуль по R-вхо- ду осуществляется импульсом с выхода 12.2

счетчика 12, который выдается после приема в устройство последнего разряда сообщения.

Триггер 15 является триггером готовности устройства к приему очередного сообщения. Он устанавливается в единичное состояние задним фронтом импульса с выхода элемента И 36, вырабатываемым по завершению обработки предыдущего сообщения в устройстве и после записи его в

регистр 5, который поступает на I- и С-входы триггера 15. Сброс триггера 15 в нуль осуществляется подачей на его R-вход строба начала очередного сообщения с входа 46 устройства.

Триггер 16 формирует сигналы, управляющие приемом первой (единица на инверсном выходе) и второй (единица на прямом выходе) частей входных последовательностей.

Триггер 17 формирует временное окно, в течение которого осуществляется выдача обработанного сообщения из регистра 5 через мультиплексор 11 на выход 49 устройства. Триггер 17 устанавливается в единичное

значение задним фронтом единичного сигнала на входах I и С с выхода элемента И 36, который возникает после окончания приема входной последовательности в регистры 1- 4. Сброс триггера 17 в нуль осуществляется

по R-входу единичным сигналом с выхода одновибратора 40, когда счетчик 13 обну- лится.

Триггер 18 формирует интервал времени, когда устройство занято приемом очередного сообщения и выдачей предыдущего. Он переключается по задне- иму фронту синхроимпульсов с входа 45 устройства в зависимости от сигнала на D-входе.

Триггер 19 формирует интервал времени от начала приема очередной последовательности до начала ее выдачи. Он переключается по заднему фронту синхроимпульса с входа 45 устройства в зависимости от значения сигнала на D-входе.

Сумматоры по модулю два 20-22 осуществляют контроль на четность поступающих на входы 42-44 младших разрядов измерительных частей входных последовательностей после записи их в регистры 1-3 соответственно. При нечетном числе единиц в этой части последовательности на выходе элемента 20 (21, 22) формируется единичный сигнал.

Сумматор по модулю два 23 осуществляет контроль на четность мажоритирован- ной последовательности служебной и старших разрядов измерительной части входных кодовых сообщений. При нечетном числе единиц в этой части сообщения из выхода элемента 23 формируется единичный сигнал.

Блоки элементов И 24-26 разрешают поступление на информационные входы блока 8 информационных частей входных последовательностей, если контроль на четность не обнаружил их искажения. Для этого на их инверсные входы подается сигнал с выходов элементов 20-22 соответственно.

Элемент ИЛИ 27 формирует сигнал об искажении одной из трех, а элемент ИЛИ 28 - двух из трех поступивших в регистры 1-3 информационных частей входных последовательностей.

Элемент ИЛИ 29 формирует общий сигнал ошибки, во-первых, когда обнаружены искажения при контроле на четность в ма- жоритированной части сообщения, и, во- вторых, когда изложены все три поступившие в регистры 1-3 информацион- HBie части входных последовательностей.

Элемент ИЛИ 30 формрует единичный сигнал при окончании первой части сообщения и при окончании второй части сообщения, который используется при переключении триггера 16.

Элемент ИЛИ 31 формирует сигнал ненулевого значения счетчика 13.

Элемент ИЛИ 32 формирует управляющий сигнал для переключения триггера 19. Единичный сигнал на выходе этого элемента наблюдается с момента времени, когда устройство начало прием очередной входной последовательности и до момента начала выдачи этого сообщения.

Элемент И 33 служит для передачи на информационный вход регистра 4 только служебной и не подверженной флуктуациям

измерительной части входного сообщения. После окончания приема этих частей сообщения он зыкрывается по инверсному входу единичным сигналом с триггера 16.

5Элемент И 34 формирует последовательность импульсов, число которых равно числу разрядов в принимаемом сообщении (C+D-разрядов), путем передачи на свой выход синхроимпульсов с синхровхода 45 уст0 ройства только при единичном значении триггера 14.

Элемент И 35 обеспечивает передачу сдвинутых синхроимпульсов с выхода элемента 36 задержки на управляющий вход

5 мультиплексора 11 только тогда, когда работает счетчик 13, о чем свидетельствует единичный сигнал на выходе элемента ИЛИ 31, поступающий на вход элемента И 35.

Элемент И 36 служит для формирования

0 импульсного сигнала готовности устройства к выдаче очередного сообщения, о чем свидетельствует единичный сигнал с инверсного выхода триггера 14, говорящий об окончании приема очередного сообщения, и

5 нулевой сигнал с выхода триггера 17, говорящий об окончании выдачи предыдущего сообщения. При наличии этих сигналов через элемент И 36 проходит сдвинутый синхроимпульс с элемента задержки 39.

0 Элемент И 37 формирует сигнал окончания выдачи очередного сообщения. Единичный сигнал на выходе этого элемента присутствует тогда, когда триггер 17 находится в нулевом, а триггер 19-в единичном

5 состояниях.

Элемент И-ИЛИ 38 служит для формирования сигнала управления триггером 18. Единичный сигнал на выходе этого элемента появляется в момент, когда устройство

0 одновременно и принимает и выдает информацию, а снимается в момент, когда в устройстве заканчивается один из этих процессов.

Блок элемента ИЛИ 41 служит для пра5 вильного размещения в разрядах регистра 5 младших разрядов сообщения с выхода блока 8 и смыкания их с частью старших разрядов, поступающих с выходов регистра 4 на вход D1 регистра 5.

0 Элемент 39 задержки служит для получения сдвинутой во времени последовательности синхроимпульсов. Временная задержка синхроимпульсов должна быть больше, чем время последовательного сра5 батывания элемента И 34, счётчика 12, триггера 14, элемента И 36.

Формирователь 40 одиночного импульса формирует импульс, указывающий об окончании выдачи очередного сообщения

из устройства. Он запускается задним фронтом сигнала с выхода элемента ИЛИ 31.

Устройство работает следующим образом.

В исходном состоянии регистры 1-4, регистр 6, счетчики 12 и 13, триггеры 14, 16-19 установлены в нулевое состояние, а триггер

15- в единичное. Цепи установки в начальное состояние не показаны, В блоке 52 памяти записаны коды, соответствующие среднему арифметическому значению флуктуирующей части значений параметра, поступающих на входы сумматора 51. При этом в младших ячейках блока памяти записаны средние по трем значениям, а в старших ячейках (старший разряд адреса равен единице) - записаны средние по двум значениям.

Перед началом поступления информации на входы 42-44 устройства в период между синхроимпульсами на вход 46 поступает строб, извещающий о начале передачи информации. При этом триггер 14 переключается в единичное состояние и открывает элемент И 34, через который синхроимпульсы с входа 45 устройства начинают поступать на синхровходы регистров 1-4 и на счетный вход счетчика 12. При этом информационные входы регистров 1-3 закрыты нулевым сигналом триггера 16, а элемент И 33 этим же ..сигналом открыт. По заднему фронту каждого синхроимпульса очередной разряд мажоритированной старшей части сообщений, содержащей служебную часть и не подверженную флуктуациям измерительную часть сообщения, записывается в регистр 4, а ранее записанные более старшие разряды сдвигаются в регистре 4 вправо. В

то же время на единицу увеличивается содержимое счетчика 12, который ведет подсчет числа принятых разрядов.

Когда в регистр 4 приняты все К старших разрядов сообщения, содержащие информацию о длине всего сообщения C+D и его первой части С, в момент действия сдвинутого элементом задержкой 39 синхроимпульса на V-входе счетчика 12, на его выходе 12.1 появится импульс. Этот импульс своим задним фронтом запишет в регистр 6 коды значения величины С и C+D.

Когда значение счетчика 12 станет равным величине С, т.е. длине первой части сообщения, на его выходе 12.3 по приходу сдвинутого элементом 29 задержки синхроимпульса появится единичный импульс, который, пройдя через элемент ИЛИ 30, переключит триггер 16 в единичное состояние. Сигнал с единичного выхода триггера

16закроет элемент И 33 и откроет по управляющим V-входам регистры 1-3 для приема

в них информации с входов 42-44 устройства. С этого момента вторая часть сообщений из трех каналов записывается в регистры 1-3, а в регистре 4 продолжается сдвиг записанной информации вправо с записью в освобождающиеся слева разряды нулей.

Когда содержимое счетчика 12 станет равным величине C+D, что говорит о приеме всего сообщения в устройство, на его выхо0 де 12.2 по сдвинутому синхроимпульсу появится импульс, который сбросит триггер 14 в нулевое состояние и тем самым закроет элемент И 34, запретив запись информации во входные регистры 1-4. Этот же импульс

5 счетчика 12, пройдя через элемент ИЛИ 30, переведет триггер 16 в нулевое состояние. После установки триггера 14 в единичное состояние сигнал с его прямого выхода через элемент ИЛИ 32 поступит на D-вход

0 триггера 19 и по заднему фронту синхроимпульса установит его в единичное состояние. Так как в устройстве выдача информации отсутствует, то триггер 17 в нулевом состоянии и элемент И 36 по инвер5 сному входу открыт. После завершения приема входного сообщения единичный сигнал с инверсного выхода триггера 14 поступит , на вход элемента И 36, который станет открытым по всем входам и сдвинутый эле0 ментом 39 задержки синхроимпульс пройдет элемент И 36 и запишет инверсное значение содержимого счетчика 12 в счетчик 13, установит триггеры 15 и 17 в единичное состояние. Единичный сигнал с выхода

5 триггера 17 закроет по инверсному входу элемент И 37, нулевой сигнал появится на выходе элемента ИЛИ 32 и сбросит его по заднему фронту первого синхроимпульса в нуль. Сигнал с выхода триггера 17 закроет

0 также элемент И 36 и запустит счетчик 13, переведя устройство в режим выдачи информации. Одйовременно единичный, сигнал триггера 15 поступает на выход 50 устройства, указывая на его готовность к

5 приему очередного сообщения.

Перед началом выдачи сообщения импульс с выхода элемента И 36 вместе с уста- новкрй триггера 17 своим задним фронтом запишет обработанное сообщение в ре0 гистр 5. При. этом обработка сообщения, кроме мажоритирования на входе старшей его части, заключается в следующем. Параллельные коды флуктуирующей части измерительной информации, соответствующие

5 трем каналам измерения, поступают на сумматоры 20-22 по модулю два соответственно. Если в одном-из каналов обнаружено нарушение четности, то соответствующий сумматор по модулю два сформирует единичный сигнал, который поступит на инверсный управляющий вход соответствующего этому каналу блока элементов И (из числа 24-26). Этот блок элементов И запретит передачу сбойной части сообщения на блок 8 вычисления среднего. Одновременно сигнал с выходов сумматоров 20-22 по модулю два поступает на входы дешифратора 9, который совместно с элементами ИЛИ 27-29 обеспечивает анализ результата контроля на четность флуктуирующей части измерений. Если во всех трех каналах ошибок не обнаружено, то все три сообщения поступают на входы блока 8 вычисления среднего, который определяет среднее значение из трех измерений и через коммутатор 10 передает на входы блока элементов ИЛИ 41. Если обнаружен сбой в одном канале, то элемент ИЛИ 27 вырабатывает единичный сигнал, который поступает на управляющий вход блока 8 и последний вычисляет среднее значение по двум измерениям. Если же сбойные сообщения обнаружены в двух каналах сразу, то единичный сигнал появляется на выходе элемента ИЛИ 28, открывается второй информационный вход коммутатора 10, первый закрывается, и измерительная информация из единственного интенсивного канала без сбоев с выхода 8.2 блока 8 через коммутатор 10 поступает на входы блока элементов ИЛИ 41. Если ошибки обнаружены во всех трех каналах или если ошибка по нечетности обнаружена в первой части сообщения сумматором по модулю два 23, то .единичный сигнал появится на выходе элемента ИЛИ 29 и он будет записан в специальный нулевой разряд ошибки регистра 5 и поступит на выход 47 ошибки устройства.

На соответствующие разрядные входы блока элементов ИЛИ 41 поступают D макс разрядов с выхода коммутатора 10 (Омакс максимальное число разрядов в флуктуирующей измерительной части входного сообщения) и Омакс младших разрядов с информационных выходов регистра 4. В результате на выходе D1 регистра 5 в общем случае присутствуют все разряды второй части сообщения и младшие разряды первой части сообщений. При этом самый младший разряд переменной первой части сообщения соединен с самым старшим разрядов второй его части. По входу D2 в регистр 5 записываются старшие разряды первой части сообщения (фиг. 4),

Единичный сигнал с выхода триггера 15 сбросит регистры 1-4 и счетчик 12 в нуль, подготовит их к приему очередного сообщения.

В счетчике 13 после записи в него инверсного значения счетчика 12 записан код

номера разряда регистра 5, в следующем за которым записан старший разряд сообщения. При единичном сигнале на управляющем V-входе счетчика 13 начнет подсчет

входных синхроимпульсов, изменяя свое значение на единицу по заднему фронту каждого синхроимпульса. Значение счетчика 13, которое определяет номер очередного разряда сообщения в регистре 5,

0 подлежащего выдаче на выход 49 устройства, поступает на счетные входы мультиплексора 11. При нулевом значении счетчика 13 на выходе элемента ИЛИ 31 присутствует единичный сигнал, который открывает эле5 мент И 35, и через него сдвинутые синхроимпульсы поступают на управляющий вход мультиплексора 11, разрешая выдачу очередного разряда сообщения только тогда, когда установится новое значение счетчика

0 13. Импульсы с выхода элемента И 35 поступают также на выход 48 устройства, определяя границы тактов выходной последовательности.

Когда выдача всего сообщения завер5 шится, счетчик 13 примет по переполнению нулевое значение (разрядность счетчика 13 такова, что максимальное число, записанное в нем, равно разрядности регистра 5, т.е. максимальной разрядности сообщения).

0 Элемент ИЛИ 31 выработает нулевое значение на-своем выходе. В это время сработает формирователь 40, импульс которого установит триггер 17 в нулевое состояние. Нулевой сигнал с выхода триггера 17 запретит

5 работу счетчика 13 и откроет по инверсному входу элемент И 36, подготавливая его к запуску очередной операции выдачи информации.

Если к моменту завершения выдачи оче0 редного сообщения следующее сообщение уже полностью принято в регистры 1-4 устройства, то элемент И 36.открыт единичными сигналами с выходов триггеров 14 и 19 и сдвинутый синхроимпульс запускает через

5 элемент И 36 операцию выдачи следующего сообщения. Если же к моменту завершения выдачи очередного сообщения прием нового сообщения еще не завершен, то элемент И 36 закрыт нулевым сигналом с триггера 14

0 и операция выдачи откладывается до момента завершения приема.

В устройстве возможна ситуация, когда прием очередного сообщения завершен, а выдача предыдущего сообщения продолжа5 ется. В этом случае факт наличия информации во входных регистрах 1-4 запоминается триггером 18, который поддерживает в еди- , ничном состоянии триггер 19, который своим единичным сигналом с прямого выхода открывает элемент И 36. Как только выдача

завершается, по инверсному входу откроется элемент И 36 и задержанный синхроимпульс с его выхода запустит новую операцию выдачи информации и, установив триггер 15 в единичное состояние, разрешит прием очередного сообщения (фиг. 5).

Таким образом, предложенное устройство позволяет принимать и передавать кодовые сообщения переменной длины, следующие асинхронно во времени с контролем на четность и мажоритарным выбором сигналов и одновременно увеличивает точность измерительной информации до потенциальной, используя ее избыточность при измерении по трем независимым каналам.

Ф о р м у л а и з о б р е т е н и я Устройство для мажоритарного выбора сигналов, содержащее мажоритарный элемент, первый - четвертый регистры сдвига, первый - четвертый элементы ИЛИ, первый - третий блоки элементов И, дешифратор, блок вычисления среднего значения, мультиплексор, формирователь одиночного им-; пульса, счетчик длины кода, первый - четвертый сумматоры по модулю два, коммутатор, регистр хранения кода, счетный триггер и первый триггер управления, единичный вход которого подключен к входу запуска устройства, первый и второй выходы счетчика длины кода соединены с одноименными входами первого элемента ИЛИ, выход которого подключен к счетному входу счетного триггера, выход которого соединен с входами управления сдвигом первого - третьего регистров сдвига, информационные входы которых являются первым - третьим информационными входами устройства и подключены к соответствующим входам мажоритарного элемента, а выходы соединены с первыми входами одноименных блоков элементов И и входами одноименных сумматоров по модулю два, выходы которых подключены к соответствующим входам дешифратора и вторым входам одноименных блоков элементов И, выходы которых подключены к соответствующим информационным входам блока вычисления среднего значения, вход управления количеством усредняемых сигналов которого соединен с выходом второго элемента ИЛИ, а выход - с группой информационных входов коммутатора, управляющий вход которого подключен к выходу третьего элемента ИЛИ, группа выходов четвертого регистра сдвига соединена с группой информационных входов старших разрядов регистра хранения кода и входом четвертого сумматора по модулю два, выход которого подключен

к первому входу четвертого элемента ИЛИ, второй вход которого соединен с первым выходом дешифратора, а выход - с входом дополнительного разряда ошибки регистра

хранения кода, выход этого разряда является выходом ошибки устройства, а выходы остальных разрядов регистра хранения кода подключены к информационному входу мультиплексора, выход которого является

0 информационным выходом устройства, второй - четвертый выходы дешифратора соединены с соответствующими входами второго элемента ИЛИ, а пятый - седьмой выходы дешифратора подключены к соот5 ветствующим входам третьего элемента ИЛИ, отличающееся тем, что, с целью расширения области применения устройства путем обеспечения обработки асинхронных кодовых сообщений переменной

0 длины, в него введены счетчик адреса, блок элементов ИЛИ, первый - пятый элементы И, регистр хранения кода длины входной последовательности, пятый и шестой элементы ИЛИ, первый и второй триггеры вре5 мени, триггер готовности, второй триггер управления, элемент ЗИ-ИЛИ и элемент задержки, вход которого,является входом синхронизации устройства и соединен с первым входом первого элемента И, синх0 ровходами первого и второго триггеров времени и счетным входом счетчика адреса, установочный вход которого подключен к третьему выходу счетчика длины коды, а выход - к адресному входу мультиплексора и

5 группе входов пятого элемента ИЛИ, выход которого соединен с входом формирователя одиночного импульса и первым входом второго элемента И, выход которого подключен к входу блокировки мультиплексора и такто0 вому выходу устройства, выход готовности которого подключен к выходу триггера готовности, входам установки в О первого - четвертого регистров сдвига и счетчика длины кода, счетный вход которого соединен с

5 выходом первого элемента И и синхровхо- дами первого - четвертого регистров сдвига, вход управления счетом - с выходом элемента задержки, первым входом третьего элемента И и вторым входом второго эле0 мента И, а установочный вход - с выходом регистра хранения кода длины входной последовательности, информационный вход ко- торого подключен к группе выходов четвертого регистра сдвига, а синхровход - к

5 четвертому выходу счетчика длины кода, выход мажоритарного элемента соединен с первым входом четвертого элемента И, второй вход которого подключен к выходу счетного триггерам выход-к информационному входу четвертого регистра сдвига, группа выходов

которого соединена с первой группой входов блока элементов ИЛИ, вторая группа входов которого подключена к группе выходов блока вычисления среднего значения, а группа выходов-к группе информационных входов младших разрядов регистра хранения кода, синхровход которого соединен с выходом третьего элемента И, синхровхо- дом счетчика адреса, установочными входами второго триггера управления и триггера готовности, вход сброса которого подключен к входу запуска устройства, выход формирователя одиночного импульса соединен с входом сброса второго триггера управления, выход которого подключен к управляющему входу счетчика адреса, второму входу третьего элемента И, первому входу пятого элемента И, первому и второму входам элемента ЗИ-ИЛИ, выход которого соединен с

0

5

информационным входом первого триггера времени, выход которого подключен к третьему и четвертому входам элемента ЗИ- ИЛИ и первому входу, шестого элемента ИЛИ, второй вход которого соединен с прямым выходом первого f риггера управления, вторым входом первого элемента И, пятым и шестым входами элемента ЗИ-ИЛИ, а выход подключен к информационному входу второго триггера времени, выход которого соединен с третьим, входом третьего элемента И и вторым входом пятого, элемента И, выход которого подключен к третьему входу шестого элемента ИЛИ, первый выход-счетчика длины ко да соединен с нулевым входом первого триггера управления, инверсный выход которого подключен к четвертому входу третьего элемента И.

20

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1495789A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Устройство для контроля и резервирования информационно-измерительной системы | 1988 |

|

SU1578723A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Устройство для контроля резервированной системы | 1984 |

|

SU1256028A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1990 |

|

SU1716628A1 |

Изобретение относится к автоматике и вычислительной технике и может быть ис пользовано при построении резервированных систем управления повышенной точности, в частности в системах обработки и передачи служебной и измерительной информации. Цель изобретения - расширение области применения устройства за счет обработки асинхронных кодовых сообщений переменной длины. Устройство содержит мажоритарный элемент, первый - четвертый регистры сдвига, первый - шестой элементы ИЛИ, первый - пятый элементы И, первый - третий блоки элементов И, блок элементов ИЛИ, дешифратор, блок вычисления среднего значения, мультиплексор, формирователь одиночного импульса, счетчик длины кода, счетчик адреса, первый - четвертый сумматоры по модулю два, коммутатор, регистр хранения кода, счетный триггер, первый и второй триггеры управления, регистр хранения кода длины входной последовательности, первый и второй триггеры времени, триггер готовности, элемент ЗИ-ИЛИ и элемент задержки. 5 ил. сл С

Щи г. 2

Запись из Я6Ц Смаке

R65

разряды

Фиг. 4

ФигЗ

Зались из 5лоха ЯЛЙ35

&Atff#C

Разряд / eti/t/fat/

Конец вь/ймц

Коны

8ыЗачи

ГЙ.О х

Ti7«o } исходное состояние

й«ш aputm сообщения

Прием со0$щения 3 RS ( + 4

K«ft /jpi/гма

iflN Перезапись снабжения Л R&5 - ЛСГ«

wf« переымси

ио$щ&ния Начало приема слгЗувщги

Прием с/ндующеи, &ыдши1 nptSuiSymezo сообщений

Kwu приема

| Устройство для мажоритарного выбораАСиНХРОННыХ СигНАлОВ | 1979 |

|

SU834703A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство мажоритарной выборки сигнала | 1980 |

|

SU875383A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-02-07—Публикация

1988-12-20—Подача