4 OD СО ts3 4

фуг.

Изобретение относится к импульсной технике и может быть использовано в различных устройствах, требующих задержки переключения логических .элементов, в частности в формирователях импульсов из перепадов напряжения, в ждущих мультивибр торах и т.д.

Известно устройство для задержки импульсов, содержащее RS -триггер на двух элементах И-НЕ, инверто выход которого подключен к одному из входов RS-триггера, интегрирующую RC -цепь, выход которой подключен к входу инвертора и к другому входу R5-триггера, входной инвертор, выход которого подключен к входу интегрирующей RCr-цепи и последовательную диодно-резистивную RC-цепь, подключенную параллельно резистору интегрирующей цепи, при этом катод диода подключен к выходу входного инвертора Cl.

Однако устройство обладает пониженной помехоустойчивостью, что объясняется падением напряжения на диоде и сопротивлении диодно-резистивной цепочки и на сопротивлении резистора интегрирующей ftC -цепи от протекания входных токов схемы И-НЕ. Другой недостаток заключается в ограничении постоянной времени RC интегрирующей цепи. Последнее объясняется возможностью самовозбуждения элементов И-НЕ при низкой скорости изменения напряжения на их входах, в частности эта скорость будет понижаться за счет закрывания диода при положительных напряжениях на входе элемента И-НЕ, близких к порогу переключения этих элементо

Наиболее близкими по технической сущности к предлагаемым являются элементы задержки, содержащие первый логический элемент, дифференцирующую или интегрирующую RC -цепь и второй логический элемент, соединенные последовательно С2.

Устройство обладает существенным недостатком, который определяется протеканием входных токов второго логического элемента .через сопротивление резистора RC-цепи. Эти токи создают на резисторе некоторое падение напряжения Ug . При увеличении номинала резистора величина UBXO также увеличивается. В результате разница между пороговым напряжением и tJex о уменьшается. Уменьшение разницы Ufipp- Ugjj - приводит к снижению помехоустойчивости элемента. Поскольку помехоустойчивость логических элементов, выполненных на микросхемах, составляет десятые доли вольта, то снижение помехоустойчивости из-за увеличения существенным образе влияет на работоспособность элемента задержки.

Повысить помехоустойчивость путе снижения величины нсяиинала резистора RC -цепи не удается по двумя причинам. Во-первых, с уменьшением номинала этого резистора уменьшаетс величина верхнего уровня входного напряжения Ug подаваемого на вход второго логического элемента. Разность (Upy -U p уменьшается, что также приводит к снижению помехоустойчивости. При величине номинала резистора меньше некоторого значения rnin устройство Становится неработоспособным Во-вторых, уменьшение номинала резистора увеличивает ток нагрузки первого логического элемента. Это может вывести иэ стро выходные транзисторы первого логического элемента.

Таким образом, при любой величине противления резистора RC-цепипомехоустойчивость элемента задержки будет снижена.

Другим недостатком элемента задержки является ограниченный диапазон реализуемых задержек. Это объясняется двумя причинами. Во-первых, ограниченностью диапазона возможных значений резистора Rc-цепи, и, как следствие, ограниченностью возможных значений постоянной времени RC -цепи, равной Т R. . Во-вторых, повышенным значением напряжения При росте счет входных токов второго логического элемента, разность UPJ, уменьшается. Поскольку разность Uf, уменьшается, то изменение напряжения на выходе RC-цепи от будет занимать меньший промежуток времени. Поэтому время задержки t реализуемое элементом задержки, сокращается.

Цель изобретения - повышение помехоустойчивости устройства для задержки импульсов и расширение диапазона реализуемых Зсщержек.

Поставленная цель достигается тем, что в устройство для задержки импульсов, содержащее соединенные последовательно первый логический элемент, времязадающую RC-цепь и второй логический элемент, введен логический элемент со свободным коллектором, причем входы логического элемента со свободным коллектором включены параллельно соответствующим входам первого логического элемента, а выход логического элемента со свободным коллектором соединен с выходом времязадакяцей RC -цепи.

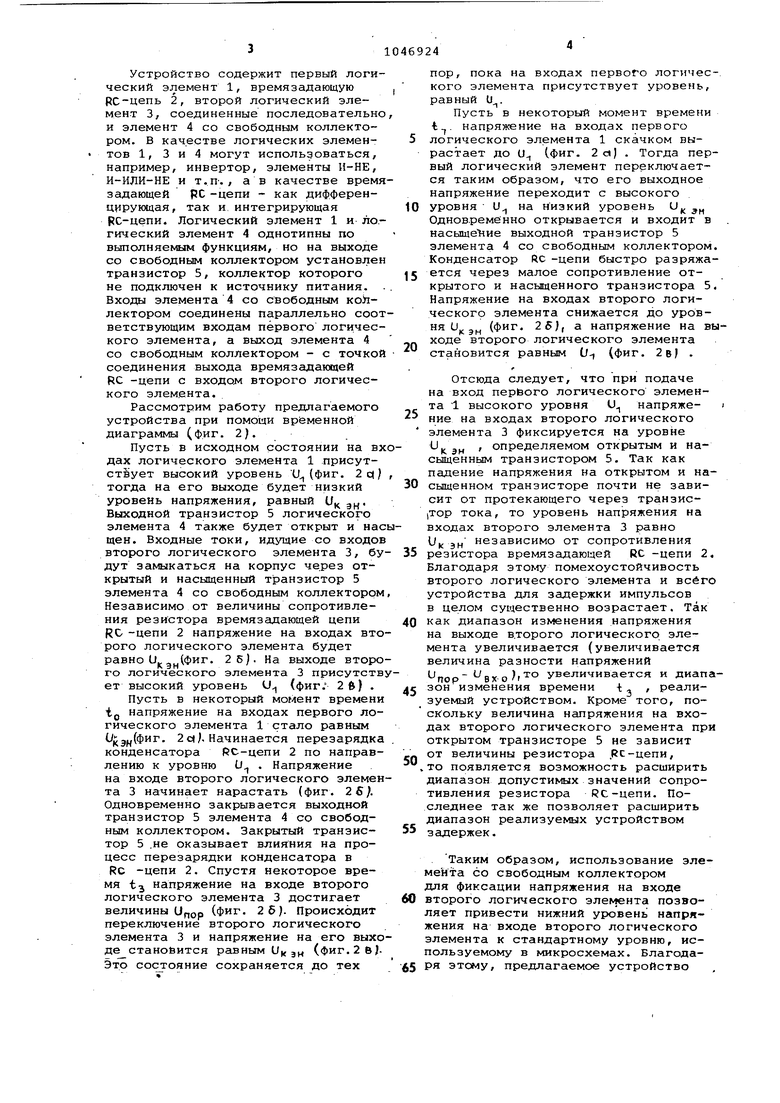

На фиг. 1 представлена функциональная схема устройства; на фиг. 2временная диаграмма ее работы для случая, когда Rt-цепь задана в виде интегрирующей Rc-цепи. Устройство содержит первый логи ческий элемент 1, времязадающую RC-цепь 2, второй логический элемент 3, соединенные последовательно и элемент 4 со свободным коллектором. В качестве логических элементов 1, 3 и 4 могут использоваться, например, инвертор, элементы Н-НЕ, И-ИЛИ-НЕ и Т.П-. , а в качестве врем задающей рС -цепи - как дифференцирующая, так и интегрирующая RC-цепи. Логический элемент 1 и ло гический элемент 4 однотипны по выполняемым функциям, но на выходе со свободным коллектором установле транзистор 5, коллектор которого не подключен к источнику питания. Входы элемента 4 со свободным Kohлектором соединены параллельно соо ветствующим входам первого логичес кого элемента, а выход элемента 4 со свободным коллектором - с точко соединения выхода времязадающей RC -цепи с входом второго логического элемента. Рассмотрим работу предлагаемого устройства при помощи временной диаграммы (фиг. 2). Пусть в исходном состоянии на в дах логического элемента 1 присутствует высокий уровень U (фиг. 2 с() тогда на его выходе будет низкий уровень напряжения, равный U , Выходной транзистор 5 логического элемента 4 также будет открыт и на щен. Входные токи, идущие со входо второго логического элемента 3, бу дут замыкаться на корпус через открытый и насыщенный транзистор 5 элемента 4 со свободным коллектором Независимо от величины сопротивления резистора времязадающей цепи RC -цепи 2 напряжение на входах вто рого логического элемента будет равно и., Дфиг. 2Б1. На выходе второ го логического элемента 3 присутств ет высокий уровень U (фиг. 26) . Пусть в некоторый момент времени tji напряжение на входах первого логического элемента 1 стало равным (фиг. 2 c( Начинается перезарядка конденсатора RC-цепи 2 по направлению к уровню и . Напряжение на входе второго логического элемен та 3 начинает нарастать (фиг. 26). Одновременно закрывается выходной транзистор 5 элемента 4 со свободным коллектором. Закрытый транзистор 5 .не оказывает влияния на процесс перезарядки конденсатора в RC -цепи 2. Спустя некоторое время t напряжение на входе второго логического элемента 3 достигает величины Uqop (фиг. 26). Происходит переключение второго логического элемента 3 и напряжение на его выхо де станобится равным U (фиг.2в} Это состояние сохраняется до тех пор, пока на входах первого логического элемента присутствует уровень, равный и. Пусть в некоторый момент времени t . напряжение на входах первого логического элемента 1 скачком вырастает до и (фиг. 2 с) . Тогда первый логический элемент переключается таким образом, что его выходное напряжение переходит с высокого уровня и на низкий уровень U Одновременно открывается и входит в насыщение выходной транзистор 5 элемента 4 со свободным коллектором. Конденсатор RC-цепи быстро разряжается через малое сопротивление открытого и насыценного транзистора 5. Напряжение на входах второго логического элемента снижается до уровня и з (фиг. 25), а напряжение на выходе второго логического элемента становится равным U-, (фиг. 2в| . Отсюда следует, что при подаче на вход перЬого логического элемента 1 высокого уровня и напряже- i ние на входах второго логического элемента 3 фиксируется на уровне кэн определяемом открытым и насыщенным транзистором 5. Так как падение напряжения на открытом и насыщенном транзисторе почти не зависит от протекающего через транзис|Тор тока, то уровень напряжения на входах второго элемента 3 равно U,( эн независимо от сопротивления резистора времязадаюцей RC -цепи 2, Благодаря этому помехоустойчивость второго логического элемента и всего устройства для задержки импульсов в целом существенно возрастает. Так как диапазон изменения напряжения на выходе второго логического элемента увеличивается (увеличивается величина разности напряжений - Ug Р ), то увеличивается и диапазон изменения времени -t , , реализуемый устройством. Кроме того, поскольку величина напряжения на входах второго логического элемента при открытом транзисторе 5 не зависит от величины резистора .RC-цепи, то появляется возможность расширить диапазон допустимых значений сопротивления резистора RC-цепи. Последнее так же позволяет расширить диапазон реализуемых устройством задержек. Таким образом, использование элемента со свободным коллектором для фиксации напряжения на входе второго логического элемента позволяет привести нижний уровень напряжения на входе второго логического элемента к стандартному уровню, используемому в микросхемах. БлагодаРя этому, предлагаемое устройство

для задержки импульсов по сравнению .с прототипом дает технико-экономи ческий эффект, заключающийся в

.повышении помехоустойчивости и расширении диапазона реализуемых устройством задержек.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМИРОВАТЕЛЬ СИГНАЛА ВКЛЮЧЕНИЯ ПОМЕХ | 1993 |

|

RU2122281C1 |

| Устройство задержки импульсов без изменения их длительности | 1991 |

|

SU1817230A1 |

| Формирователь импульсов Ларионова | 1985 |

|

SU1285567A1 |

| Устройство задержки наносекундных импульсов | 1978 |

|

SU678658A1 |

| Реле времени | 1978 |

|

SU748560A1 |

| Ждущий мультивибратор | 1978 |

|

SU782134A1 |

| Пьезополупроводниковый стабилизатор постоянного напряжения | 1987 |

|

SU1408506A2 |

| Устройство для задержки импульсов | 1986 |

|

SU1348988A1 |

| Мультивибратор | 1979 |

|

SU790122A1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 2001 |

|

RU2224355C2 |

УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ ИМПУЛЬСОВ, содержащее соединенные последовательно первый логический элемент, времязадающую RC-цепь, второй логический элемент, о-т яич ающе е с я тем, что/ с целью повышения его помехоустойчивости и расширения диапазона реализуемых задержек, в него введен логический элемент со свободным коллектором, причем входы логического элемента со свободным коллектором включены параллельно входам первого логического элемента, а выход элемента со свободным коллектором Соединен с выходом времяэадающей ЙС-цепи.

(put. г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для задержки импульсов | 1977 |

|

SU716143A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Гольденберг Л.М | |||

| Импульсные устройства | |||

| М | |||

| , | |||

| Радио и связь, 1981, с | |||

| Приспособление в центрифугах для регулирования количества жидкости или газа, оставляемых в обрабатываемом в формах материале, в особенности при пробеливании рафинада | 0 |

|

SU74A1 |

Авторы

Даты

1983-10-07—Публикация

1981-12-25—Подача