I

Изобретение относится к радйоизм итепьной технике.

наносекутвдных импульсов важна при конструировании различных цифровых устройств, в частности нового класса приборов - высокоскоростных (2О мГц) анализаторов логических сое- ТО5ШИЙ цифровых устройств, приментощюс- ся при конструировании, производстве и ремонте логических печатных плат, калькуляторов, линии ЭВМ и больших вычислительных машин.

Известно устройство временной задержки и формирования синхронизирующего импульса, содержащее интегратор, ограничитель, дифференциальный усилитель и источник опорного сигнала .

Так как в данном устройстве синхро- низирукяций импульс задерживается интегрирующей цепочкой, величина задержки зависит от амплитуды входного импульса, вследствие чего-данное устройство не может быть использовано в многосерийных приборах для получения необходимых задержек.

Известны устройства задержки, соцержащие PS -триггер, формирователь запуска, дифферешшешьный каскад на двух li-Ф-П-транзисторах, цепь смещения, источник напряжения, отсекающий Диод, интегрирующую RC-цепочку, нагрузочный резистор 23

Однако данное устройство обладает ограниченным диапазоном регулировки задержки выходного импульса, так как:

- увеличение конденсатора и интегрирукяцей RC-цепочки ведет к увеличению начальной задержки выходного импульса, а также к увеличению габаритов ковденSсатора;

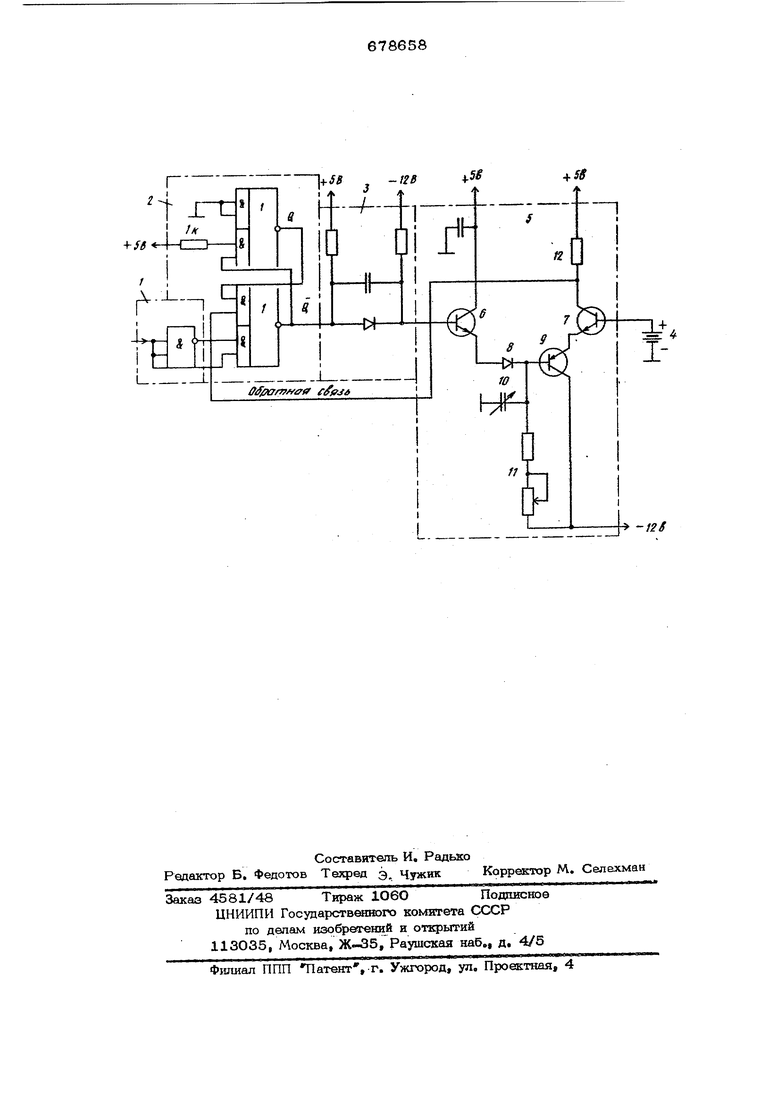

- увеличение резистора интегрирующей RC-цепочки приводит к уменьшению рабочего тока транзисторов дифференциального каскада, ухудшая фронт выходного импуль0са, а также уменьшает стабильность задержки вследствие сильного влияния токаотпирающегося транзистора на разряд конденсатора. Цель изобретения - расширение диапазона регутшровки временной задержки выходного импульсзо Достигается эта цель тем, что в уст ройстве задержки, содержащем RS-триг repj к одному из входов которого подклю чей формщюватель его запуска, дифференциальный каскад, на двух 51 -п-транзисTopaxj база одного из которых через цепь сметдения напряжения подключена к инверсному выходу RS-триггера, коллектор к источнику положительного напря- жения9 эмиттер - через соединенные последоотсекакнций диод и интегрирукицую RC-цепочку к источнику отрицательно- го напряжения, база другого транзисто- ра подключена к источнику опорного напряжепин, а коллектор - ко второму входу RS «-триггера и через нагрузочный резистор к источнику положительного напряжения; в цепь эмиттера второго И р-И-транзистора введен третий ,pтранзистор, база которого приключена ко входу интегрирующей цепочки, эмиттер к эмиттеру второго транзистора, а коллектор к источнику отрицательного напряжения, На чертеже представлена принципиальная схема устройства. Устройство содержит формирователь запуска R S -трип-ера 1, R 5 -триггер 2 цепь смещения напряжения За иоточнкк напряжения смещения 4, дифференциальный каскащ 5, включающий транзисторы 6 и Tj отсекакндий диод 8, р- п-р-транзистор 9, конденсатор Ю и резисторы 11 интегрирующей RC-цепочки, нагрузочный резистор 12, В рабочем состоянии на инверсном вы ходе (Q) RS Триггера напряжение логической 1, Конденсатор Ю заряжен, и по цепи обратной связи с дифференциального каскада 5 на один из входов R S триггера подается напряжение логической С приходом на устройство положительного перепада RS -триггера переворачивается (), транзистор 6 закрываетсЯу и конденсатор 10 начинает разряжаться через резисторы 11 и источник питания 12 до момента отпирания транзистора 7, ток которого протекает через транзистор 9 в то время как по резисторам 11 течет базовый ток транзистора 9. По цепи обратной связи R 3 -триггер 2 возвращается в исходное состояние, открывается транзистор 6, конденсатор Ю заряжается, запирая транзистор 7, на коллекторе которого заканчивается формировЕГНие эаавржанного импульса, Предложенная схема временной задержки имеет значительно больший диапазон регулировки задержки выходного импульса по сравнению с известным устройством задержки ввиду того, что ток транзистора 7 протекает через транзистор 9, в то время как по резисторам 11 течет лишь базовый ток этого транзистора, что позволяет повысить номинал резисторов 11, а следовательно расширить диапазон регул1фовки задержки выходного импульса в / 1% / раз ( 1 - коэффитшент усиления по току). Формула изобретения Устройство задержки наносекундных импульсов, содержащее RS триггер, к одному из входов которого подключен формирователь его запуска, дифференциальный каскад на двух h-p-h-транзисторах, база одного из которых через цепь смицения напряжения подключена к инверсном; выходу RS-триггера, коллектор - к источнику положительного напряжения, эмиттерчерез соединенные последовательно отсе кающий диод и интегрирующую RC-{хепоч- ку к источнику отрицательного напряжения, база другого транзистора подключена к источнику опорного напряжения, а коллектор - ко второму входу R S -триггера и через нагрузочный резистор - к источнику положительного напряжения, отличающееся тем, что, с целью расширения диапазона регулировки временной задержки, в цепь эмиттера второго п-р-П-транзистора введен третий р- п-р-транзистор, база которого подключена ко входу интегрирующей RC- цепочки, эмиттер - к эмиттеру второго транзистора, а коллектор - к источнику отрицательного напряжения. Источники информации, принятые во внимание при экспертизе 1. Патент США № 3832572, кл. 307-106, 1974. 2о Описание прибора 160ОА фирмы HeuCett-PacVard. --1...

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный генератор импульсов | 1983 |

|

SU1132345A1 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| Импульсный стабилизатор напряжения | 1985 |

|

SU1325440A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| ОДНОВИБРАТОР | 2018 |

|

RU2693182C1 |

| Устройство для стабилизации импульсного тока нагрузки | 1986 |

|

SU1352472A1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| УСТРОЙСТВО ДИФФЕРЕНЦИАЛЬНОЙ ТОКОВОЙ ФАЗОВОЙЗАЩИТЫ ШИН | 1966 |

|

SU182217A1 |

| Заторможенный релаксационный генератор | 1976 |

|

SU661724A1 |

| Формирователь импульсов | 1977 |

|

SU702499A1 |

Авторы

Даты

1979-08-05—Публикация

1978-01-05—Подача