(5) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691843A1 |

| Преобразователь двоичных кодов в двоично-десятичные | 1984 |

|

SU1200428A1 |

| Преобразователь двоичного кода в десятичный | 1976 |

|

SU691842A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1976 |

|

SU646327A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU771660A1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1977 |

|

SU898417A2 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1983 |

|

SU1149243A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1501276A1 |

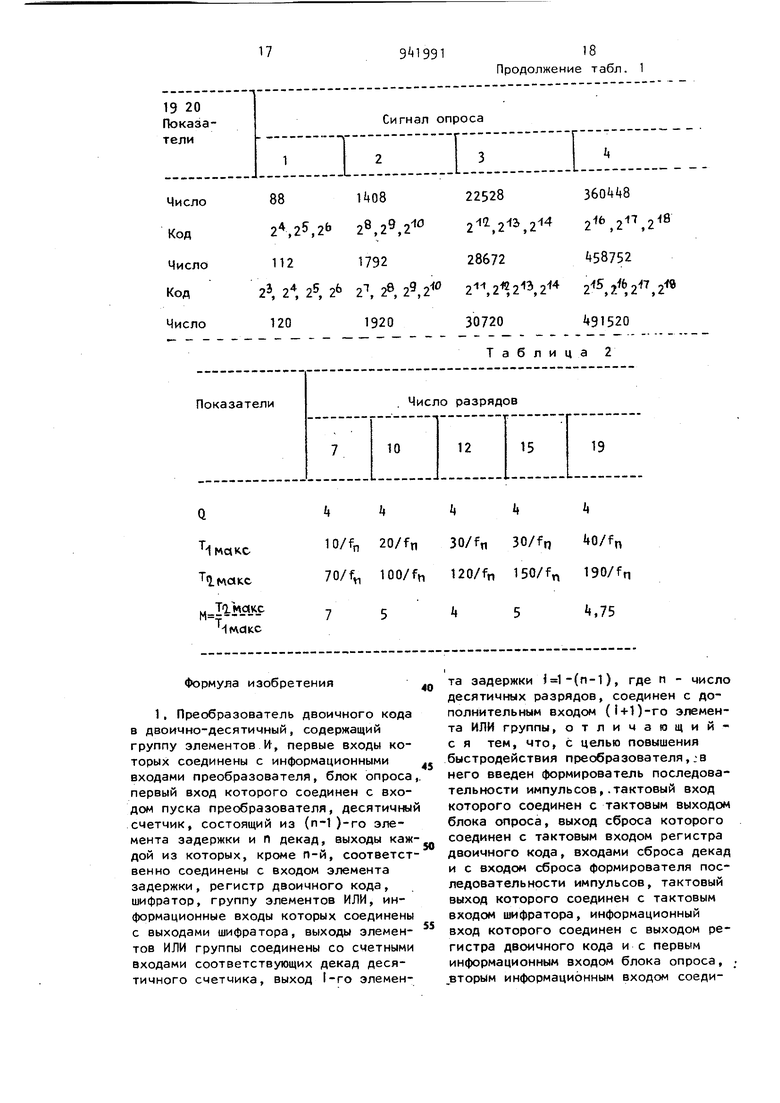

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении преобразователей, в частности в устройствах считывания графической информации.

Известен преобразователь двоичного кода в десятичный, содержащий шифратор, десятичный счетчик, двоичные счетчики, блок опроса первую и вторую группы элементов И, многовходовой эле мент И СП.

Наиболее близким к предлагаемому по технической сущности и схемному ,5 построению является преобразователь двоичного кода в двоично-десятичный, содержащий группу элементов И, входы которых соединены с информационными входами преобразователя, блок опроса,20 десятичный сметчик, состоящий из декад и последовательно соединенных с ними элементов задержки, регистр двоичного кода, шифратор, группу элементов ИЛИ, делитель, триггер, элемент И 2.

Недостаток известных преобразователей - относительно низкое быстродействие, связанное с последовательной обработкой двоичных разрядов и отсутствием учета нулевых значений двоичных разрядов.

Целью изобретения является повышение быстродействия преобразователя.

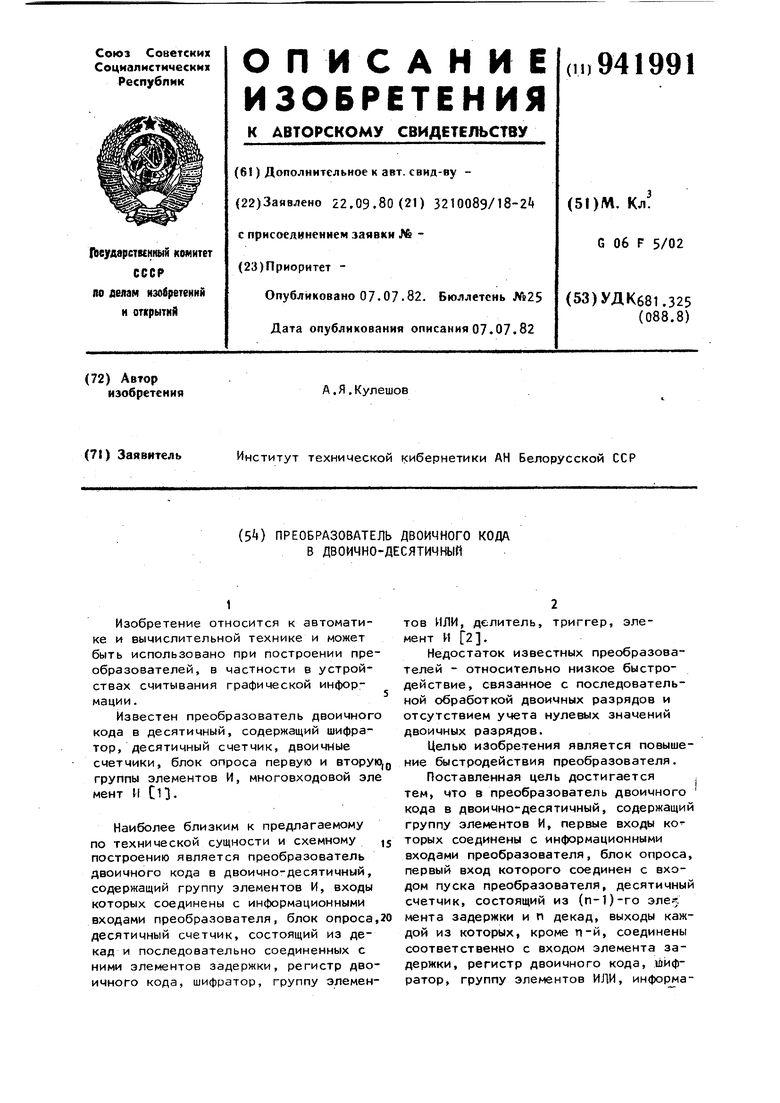

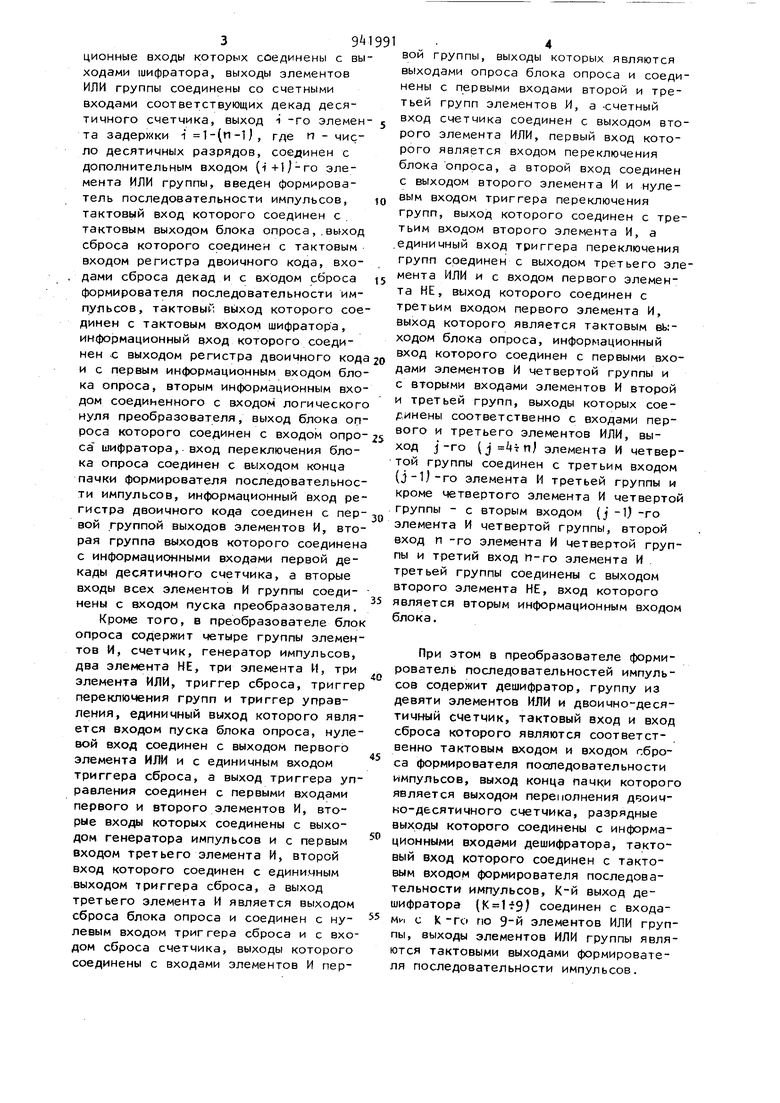

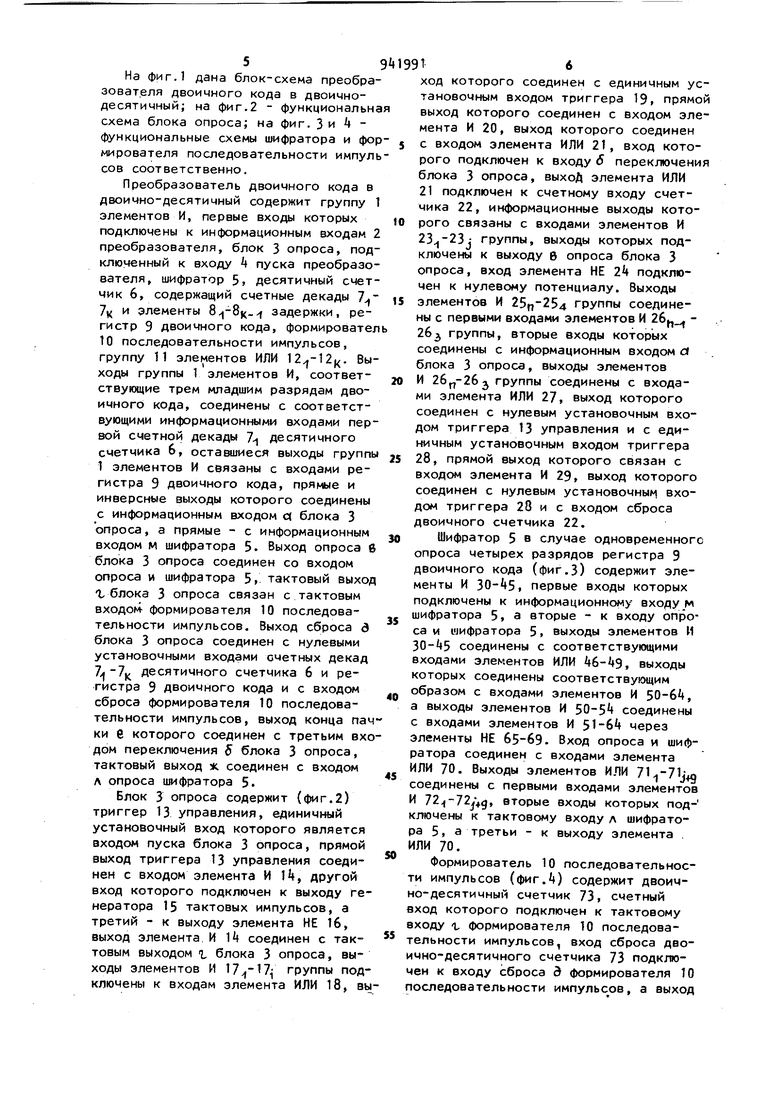

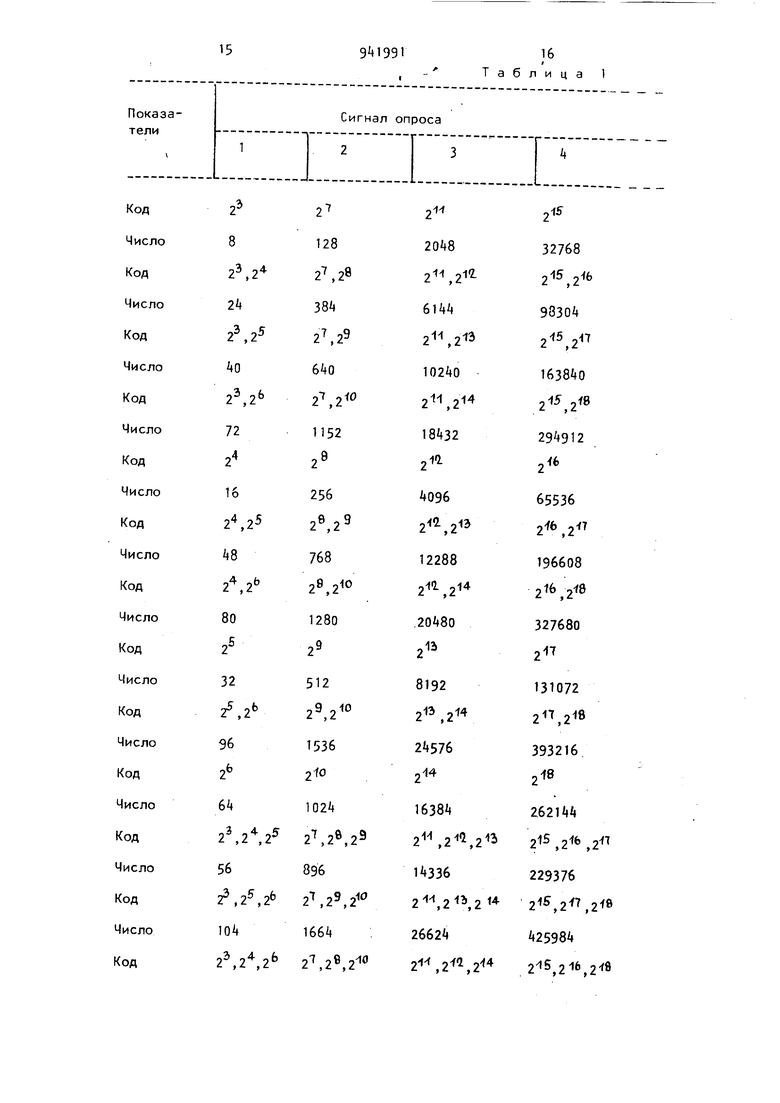

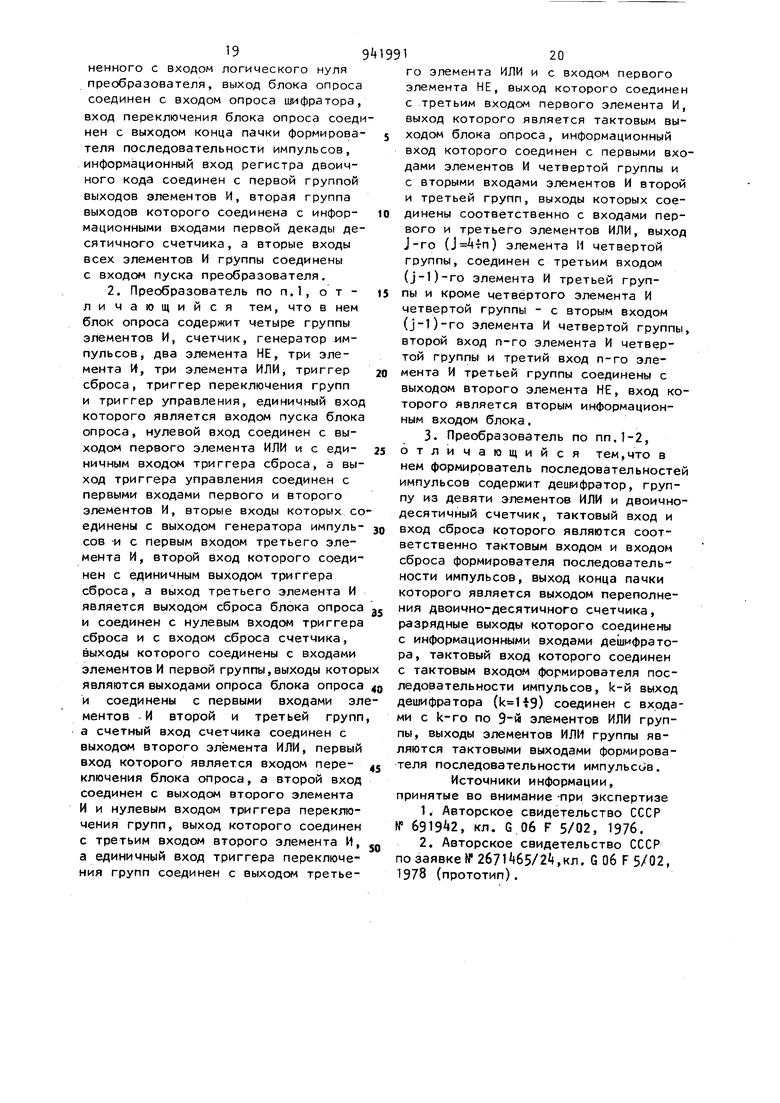

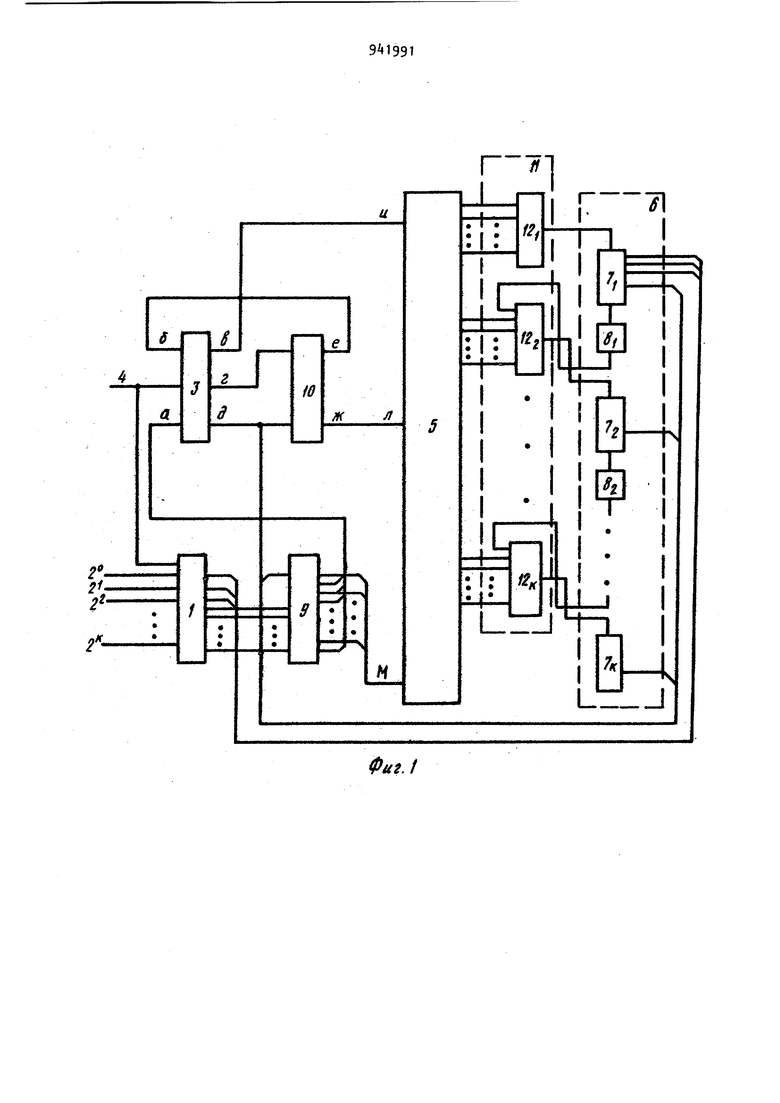

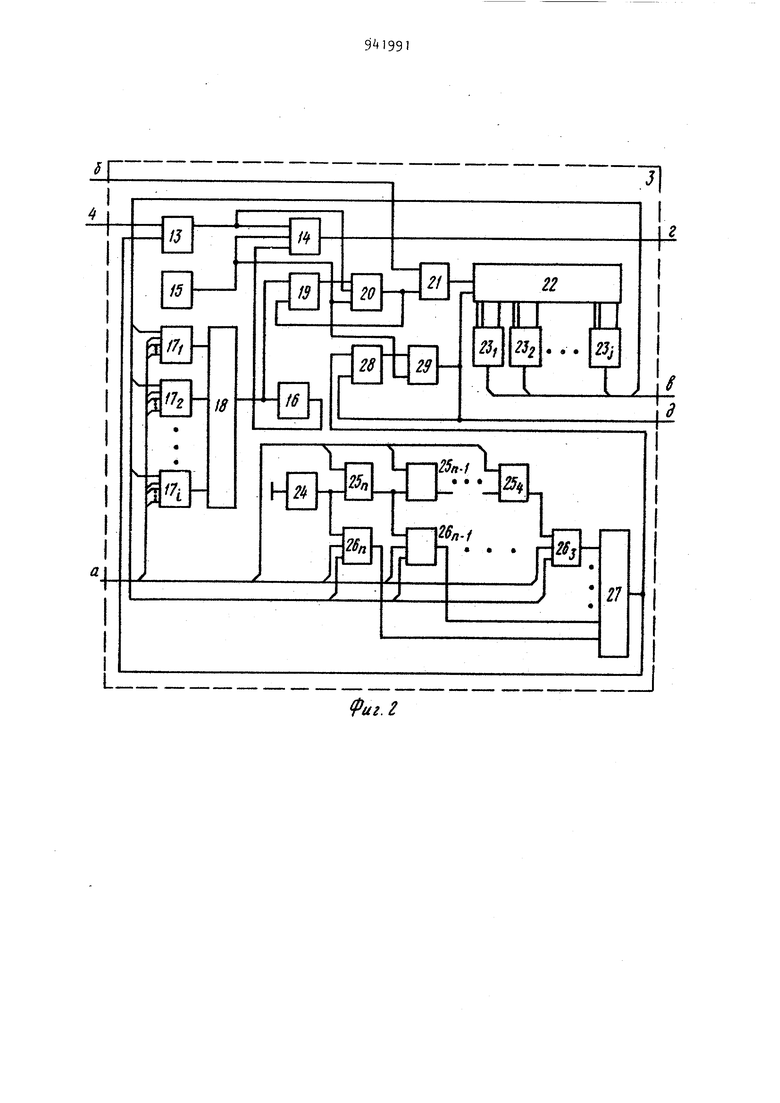

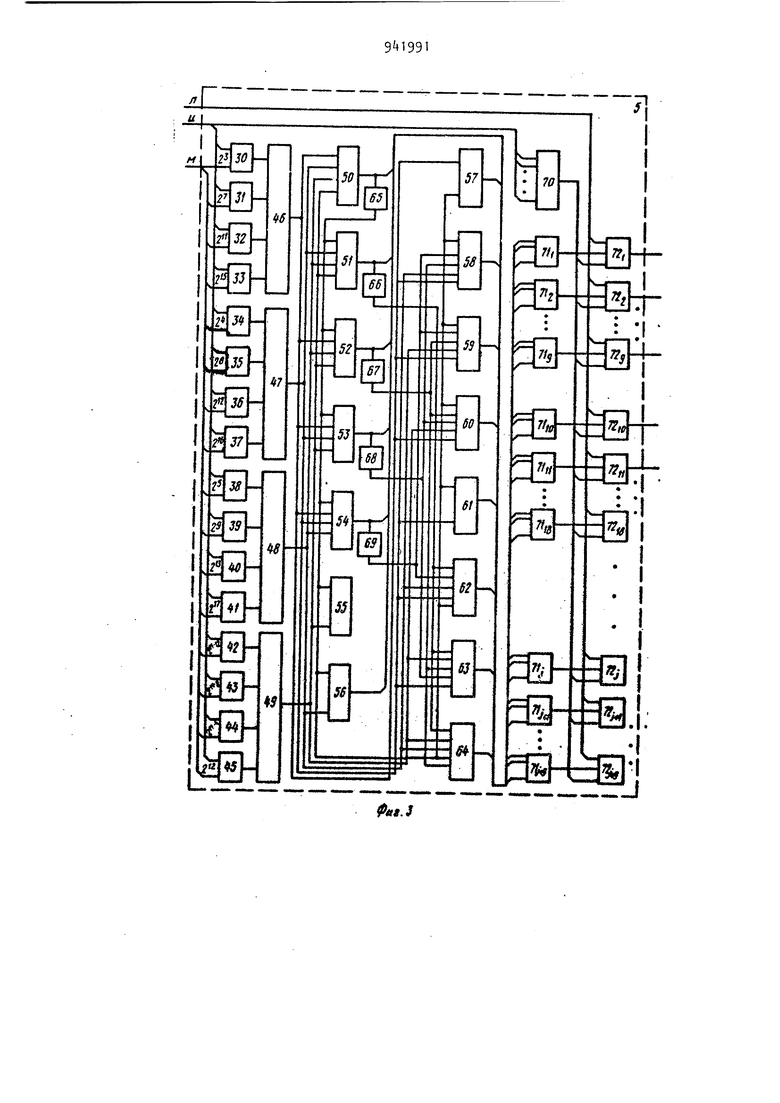

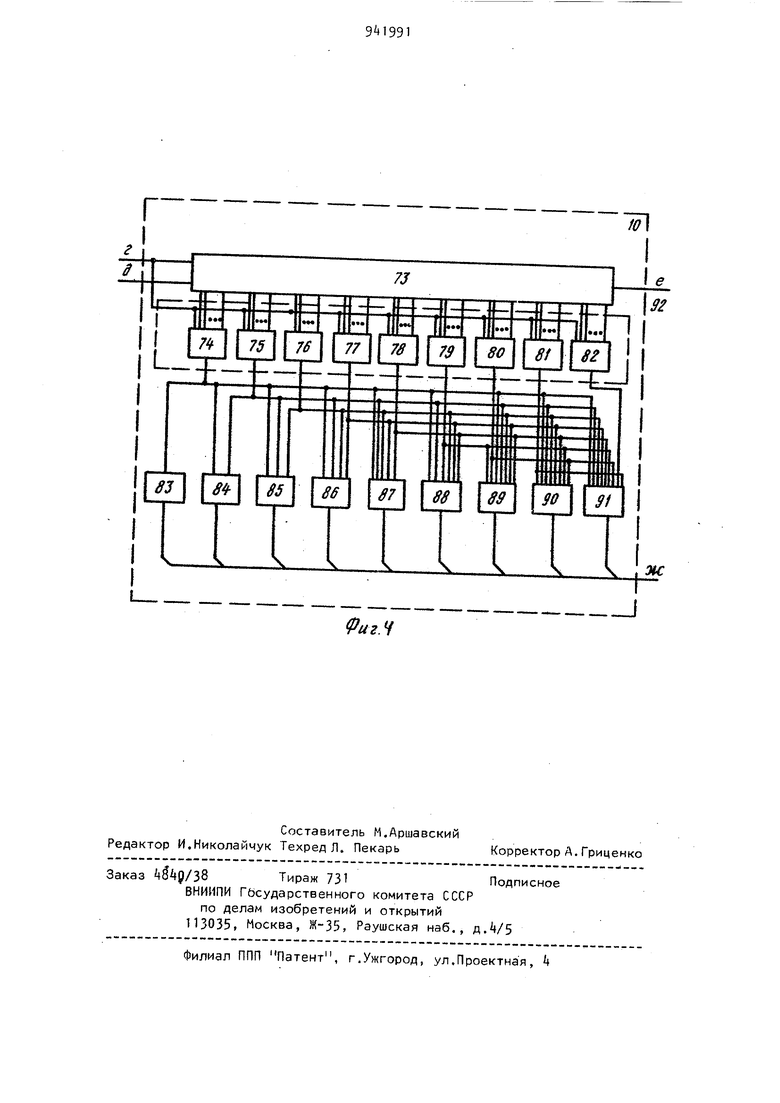

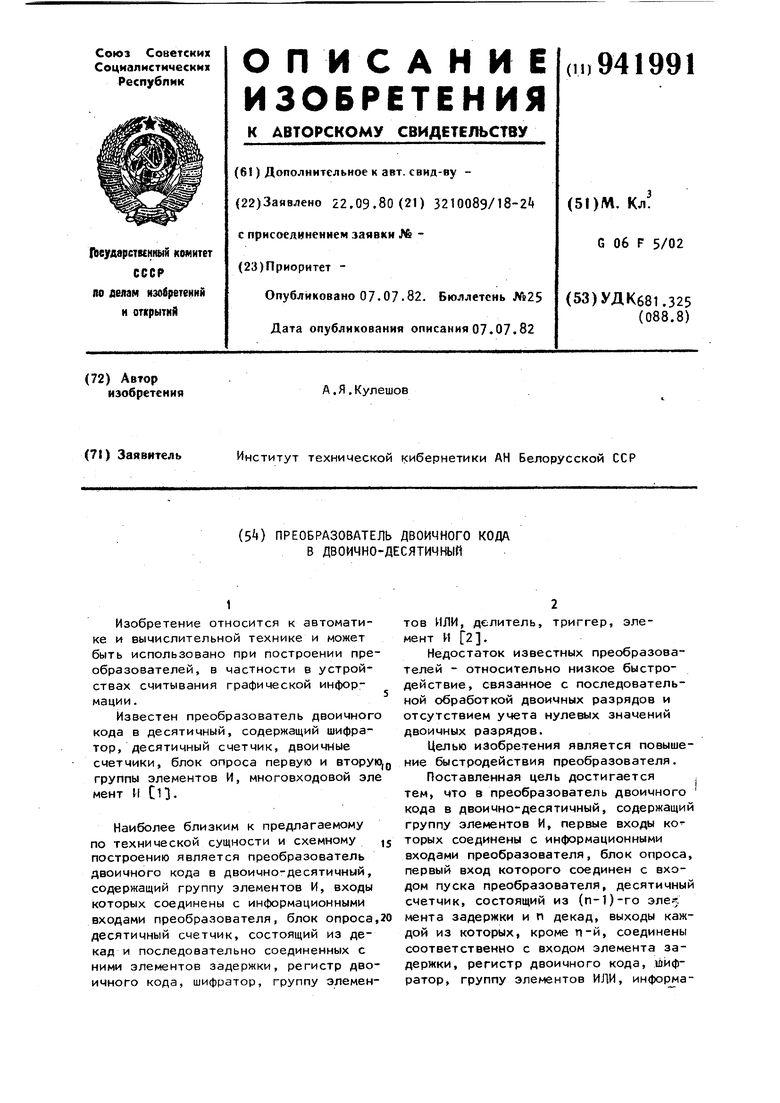

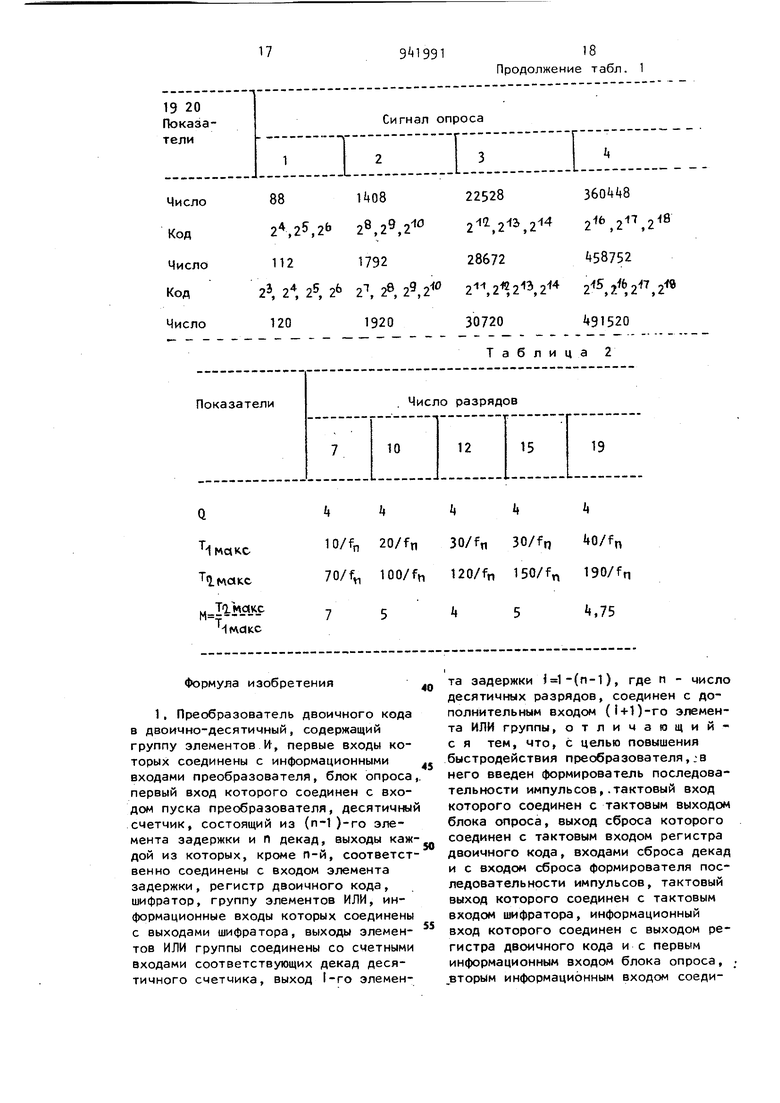

Поставленная цель достигается , тем, что 8 преобразователь двоичного кода в двоично-десятичный, содержащий группу элементов И, первые входы ко торых соединены с информационными входами преобразователя, блок опроса, первый вход которого соединен с входом пуска преобразователя, десятичный счетчик, состоящий из (п-1)-го элея, мента задержки и п декад, выходы каждой из которых, кроме п-й, соединены соответственно с входом элемента задержки, регистр двоичного кода, шифратор, группу элементов ИДИ, информа39 1ционные входы которых соединены с выходами шифратора, выходы элементов ИЛИ группы соединены со счетными входами соответствующих декад десятичного счетчика, выход -i -го элемента задержки i 1-(п-1), где п - число десятичных разрядов, соединен с дополнительным входом (i+l)-ro элемента ИЛИ группы, введен формирователь последовательности импульсов, тактовый вход которого соединен с. тактовым выходом блока опроса,.выход сброса которого соединен с тактовым входом регистра двоичного кода, входами сброса декад и с входом сброса формирователя последовательности импульсов, тактовый выход которого сое динен с тактовым входом шифратора, информационный вход которого соединен -с выходом регистра двоичного кода и с первым информационным входом блока опроса, вторым информационным входом соединенного с входом логического нуля преобразователя, выход блока опроса которого соединен с входом опроса шифратора, вход переключения блока опроса соединен с выходом конца пачки формирователя последовательности импульсов, ин }х рмационный вход регистра двоичного кода соединен с первой группой выходов элементов И, вторая группа выходов которого соединена с информационными входами первой декады десятичного счетчика, а вторые входы всех элементов И группы соединены с входом пуска преобразователя. Кроме того, в преобразователе блок опроса содержит четыре группы элементов И, счетчик, генератор импульсов, два элемента НЕ, три элемента И, три элемента ИЛИ, триггер сброса, триггер переключения групп и триггер управления, единичный выход которого является входом пуска блока опроса, нулевой вход соединен с выходом первого элемента ИЛИ и с единичным входом триггера сброса, а выход триггера управления соединен с первыми входами первого и второго элементов И, вторые входы которых соединены с выходом генератора импульсов и с первым входом третьего элемента И, второй вход которого соединен с единичным выходом триггера сброса, а выход третьего элемента И является выходом сброса блока опроса и соединен с нулевым входом триггера сброса и с входом сброса счетчика, выходы которого соединены с входами элементов И перВОЙ группы, выходы которых являются выходами опроса блока опроса и соединены с первыми входами второй и третьей групп элементов И, а -счетный вход счетчика соединен с выходом второго элемента ИЛИ, первый вход которого является входом переключения блока опроса, а второй вход соединен с выходам второго элемента И и нулевым входом триггера переключения групп, выход которого соединен с третьим входом второго элемента И, а единичный вход триггера переключения групп соединен с выходом третьего элемента ИЛИ и с входом первого элемента НЕ, выход которого соединен с третьим входом первого элемента И, выход которого является тактовым вЬ:ходом блока опроса, информационный вход которого соединен с первыми входами элементов И четвертой группы и с вторыми входами элементов И второй и третьей групп, выходы которых соединены соответственно с входами первого и третьего элементов ИЛИ, выход j-го ( элемента И четвертой группы соединен с третьим входом элемента И третьей группы и кроме четвертого элемента И четвертой группы - с вторым входом {J -1) -го элемента И четвертой группы, второй вход п -го элемента И четвертой группы и третий вход п-го элемента И . третьей группы соединены с выходом второго элемента НЕ, вход которого является вторым информационным входом блока, При этом в преобразователе формирователь последовательностей импульсов содержит дешифратор, группу из девяти элементов ИЛИ и двоично-десятичный ечетчик, тактовый вход и вход сброса которого являются соответственно тактовым входом и входом сброса формирователя последовательности импульсов, выход конца пачки которого является выходом переполнения др;оично-десятичного счетчика, разрядные выходы которого соединены с информационными входами дешифратора, тактовый вход которого соединен с тактовым входом формирователя последовательности импульсов, К-й выход дешифратора {К И9) соединен с входами с К-го по 9-й элементов ИЛИ группы, выходы элементов ИЛИ группы являются тактовыми выходами формирователя последовательности импульсов. На фиг.1 дана блок-схема преобразователя двоичного кода в двоичнодесятичный; на фиг.2 - функциональна схема блока опроса; на фиг. Зи функциональные схемы шифратора и фор мирователя последовательности импул сов соответственно. Преобразователь двоичного кода в двоично-десятичный содержит группу элементов И, первые входы которых подключены к информационным входам 2 преобразователя, блок 3 опроса, подключенный к входу 4 пуска преобразователя, шифратор 5 десятичный счет чик 6, содержащий счетные декады 7, 7к и элементы . задержки, регистр 9 двоичного кода, формировател 10 последовательности импульсов, группу 11 элементов ИЛИ . Выходы группы 1 элементов И, соответствующие трем младшим разрядам двоичного кода, соединены с соответствующими информационными входами первой счетной декады 7 десятичного счетчика 6, оставшиеся выходы группы 1 элементов И связаны с входами регистра 9 двоичного кода, прямые и инверсные выходы которого соединены с информационным входом d блока 3 опроса, а прямые - с информационным входом м шифратора 5. Выход опроса в блока 3 опроса соединен со входом опроса и шифратора 5, тактовый выход L блока 3 опроса связан с тактовым входом- формирователя 10 последовательности импульсов. Выход сброса д блока 3 опроса соединен с нулевыми установочными входами счетных декад 7л 7 десятичного счетчика 6 и регистра 9 двоичного кода и с входом сброса формирователя 10 последовательности импульсов, выход конца пач ки е которого соединен с третьим вхо дом переключения 5 блока 3 опроса, тактовый выход ж. соединен с входом л опроса шифратора 5. Блок 3 опроса содержит (фиг.2) триггер 13 управления, единичный установочный вход которого является входом пуска блока 3 опроса, прямой выход триггера 13 управления соединен с входом элемента И 1, другой вход которого подключен к выходу генератора 15 тактовых импульсов, а третий - к выходу элемента НЕ 16, выход элемента И k соединен с тактовым выходом 1 блока 3 опроса, выходы элементов И группы подключены к входам элемента ИЛИ 18, вы ход которого соединен с единичным установочным входом триггера 19, прямой выход которого соединен с входом элемента И 20, выход которого соединен с входом элемента ИЛИ 21, вход которого подключен к входу f переключения блока 3 опроса, выхоД элемента ИЛИ 21 подключен к счетному входу счетчика 22, информационные выходы которого связаны с входами элементов И группы, выходы которых подключены к выходу 6 опроса блока 3 опроса, вход элемента НЕ 2k подключен к нулевому потенциалу. Выходы элементов И группы соединены с первыми входами элементов И 2б 26 группы, вторые входы которых соединены с информационным входом d блока 3 опроса, выходы элементов И 26p-26j группы соединены с входами элемента ИЛИ 27, выход которого соединен с нулевым установочным входом триггера 13 управления и с единичным установочным входом триггера 28, прямой выход которого связан с входом элемента И 29, выход которого соединен с нулевым установочные входом триггера 28 и с входом сброса двоичного счетчика 22. Шифратор 5 в случае одновременного опроса четырех разрядов регистра 9 двоичного кода (фиг.З) содержит элементы И , первые входы которых подключены к информационному входу м шифратора 5 а вторые - к входу опроса и шифратора 5, выходы элементов И 30-45 соединены с соответствуюцими входами элементов ИЛИ 46-49, выходы которых соединены соответствующим образом с входами элементов И 50-64, а выходы элементов И 50-54 соединены с входами элементов И через элементы НЕ б5-б9. Вход опроса и шифратора соединен с входами элемента ИЛИ 70. Выходы элементов ИЛИ 71 -71j4g соединены с первыми входами элементов И 72 -72у+д, вторые входы которых подключены к тактовому входу л шифратора 5, а третьи - к выходу элемента ИЛИ 70. Формирователь 10 последовательности импульсов (фиг.4) содержит двоично-десятичный счетчик 73, счетный вход которого подключен к тактовому входу г. формирователя 10 последовательности импульсов, вход сброса двоично-десятичного счетчика 73 подключен к входу сброса Э формирователя 10 оследовательности импульсов, а выход 79 переполнения двоично-десятичного счетчика 73 к выходу 6 конца пачки формирователя 10 последовательностей импульсов, разрядные выходы двоичнодесятичного счетчика 73 соединены с соответствующими входами элементов И 74-82, первые входы которых связаны с тактовым входом/2. формирователя 10 последовательностей импульсов, выходы элементов И соединены с соответствующими входами элементов ИДИ 83-91 группы, а выходы элементов ИЛИ 83-91 подключены к тактовому выходу с формирователя 10 последовательностей импульсов. Элементы И груп пы в совокупности образуют дешифратор 92. Преобразователь двоичного кода в двоично-десятичный работает следующим образом. Перед началом работы производится начальная установка всех триггеров преобразователя двоичного кода в двоично-десятичный в нулевое состояние (цепи начальной установки на фиг.1 не показаны) После начальной установки преобразователя двоичного кода в двоичнодесятичный на выходе элемента И 23 блока 3 опроса (фиг.2) появляется сигнал (первый сигнал опроса)который Поступает на первые входы элементов И и на выход 6 блока 3 опроса. С выхода б блока 3 опроса первый сигнал опроса поступает на вход и шифратора 5 и ..далее на первые входы элементов И 30, 3, 38, 2 (фиг.З), например, в случае одновременного опроса четырех разрядов 2-2 двоичного кода. При поступлении на вход k устройства сигнала Пуск, поступающего на первые входы группы 1 элементов И, на вторые входы которых поступают информационные сигналы разрядов 2 двоичного кода, происходит запись трех нладших разрядов двоичного кода в первую счетную декаду 7 десятичного счетчика 6, остальные разряды 2 - з двоичного кода записываются в регистр 9 двоичного кода. Сигналы с прямых и инверсных выходов разрядов регистра 9 двоичного кода поступают на вход с блока 3 опроса. С входа d блока 3 опроса сигналы с инверсных выходов разрядов 2 -2 двоичного кода поступают на входы элементов И , при этом, например, в случае одновременного оп; 1 роса четырех разрядов на входы элемеМта И 17 поступают инверсные сигналы первых четырех одновременно опрашиваемых разрядов 2-2 двоичного кода. Если опрашиваемые разряды 2-2 двоичного кода находятся в нулевом состоянии, то на выходе элемента И 17, появляется сигнал, так как на первом входе есть разрешающий сигнал опроса. Если хотя бы один из опрашиваемых разрядов, например, 2 -2, находится в единичном состоянии, то на выходе элемента И 17 сигнал отсутствует. Сигнал с выхода элемента И 17-f поступает на вход элемента ИЛИ 18 и далее на единичный установочный вход триггера 19, а также на вход элемента НЕ 16, с выхода которого сигнал поступает на третий вход элемента И И. Сигнал Пуск с входа преобразователя поступает на единичный установочнь й вход триггера 13 управления (фиг.2)1 устанавливая его в единичное состояние, сигнал с прямого выхода которого поступает на входы элементов И 14 и 20, на входы которых поступают также сигналы с выхода генератора 15 тактовых импульсов. При наличии сигнала на выходе элемента НЕ 16 (если хотя §ы один из одновременно опрашиваемых разрядов, например, двоичного кода находится в единичном состоянии) сигналы с генератора 15 тактовых импульсов проходят через элемент И 14 на выход блока 3 опроса. Прямые сигналы разрядов 2 -2 двоичного кода поступают с регистра 9 двоичного кода на вход м шифратора 5. С входа м шифратора 5 (фиг.З) сигналы с прямых выходов, например,первыЗ четырех опрашиваемых разрядов 2 -2 двоичного кода поступают на входы элементов И 30, 34, ЗЗ и первых входах которых уже присутствует сигнал опроса. Сигналы с выходов этих элементов поступают на входы элементов ИЛИ 46-49 с выходов которых сигналы поступают на ёходы элементов И 50-64, с помощью которых, а также с помощью дополнительно включенных элементов НЕ б5-б9 сигналы с выходов которых поступают на входы элементов И , осуществляется шифрование опрашиваемых разрядов двоичного кода.. Сигналы с выходов элементов И 50-64 поступают на входы элементов ИЛИ 71( , с выходов 99 которых сигналы поступают на первые входы элементов И ., на вторые входы которых поступают определенные последовательности импульсов с входа л шифратора 5 а на третьи сигналы опроса с входа и шифратора 5 Тактовые импульсы с выхода t блок 3 опроса поступают на вход г формиро вателя 10 последовательности импульсов (фиг.) и далее на счетный вход двоично-десятичного счетчика 73 и на входы элементов И , с помощью которых выделяются все девять состояний двоично-десятичного счетчика 73. Тактовые импульсы с выходов этих элементов поступают на входы девяти элементов ИЛИ 83-91. На первый элемент ИЛИ 83 заводится первое состояние двоично-десятичного счетчи ка 73, на вторюй элемент ИЛИ 8 первое и второе, на третий элемент ИЛИ 85- первое, второе и третье и т.д., на девятый элемент ИЛИ 91 все девять состояний двоично-десятичного счетчика 73. Таким образом, на выходах элементов ИЛИ 83-91 выделяется соответственно от одного до девяти импульсов. Тактовые импульсы с выходов элементов ИЛИ поступают на вход ж. формирователя 10 последовательностей импульсов, на вход е которого поступает сигнал переполнения двоично-десятичного счетчика 73. Работа предлагаемого устройства основана на параллельном суммировании в счетных декадах 1 десятичного счетчика б последовательностей импульсов, которые соответствуют сумме весов одновременно опрашиваемых разрядов двоичного кода. В табл.1, поясняющей работу шифратора 5 (фиг.З) приведены различные комбинации состояний четырех од|новременно опрашиваемых разрядов дво чного кода, старший разряд которого равен, например, 2 . В графе Код указаны разряды, имеющие единичное состояние среди четырех одновременно опрашиваемых разрядов двоичного кода в графе Число - числовой эквивалент, соответствующий сумме весов од новременно опрашиваемых разрядов дво ичного кода, в графе Сигнал опроса количество сигналов опроса, необходи мых для опроса всех разрядов двоичного кода, старший разряд которого равен, например, 2 °. 1 На выходах элементов И 72 -72q шифратора 5 может появиться любая последовательность импульсов от одного до девяти, которая через группу 11 элементов ИЛИ 12 поступает на счетный вход первой счетной декады 7 десятичного счетчика 6. На выходах элементов И 72,, может появиться любая последовательность импульсов от одного до девяти, которая через элементы ИЛИ 12 поступает на счетный вход счетной декады 1 десятичного счетчика 6. При переполнении счетных декад 7-f 7j десятичного счетчика 6 перенос из предыдуи ей счетной декады в последующую осуществляется с помощью элементов задержки 8-j-8(;, сигналы с выходов которых поступают на входы группы 11 элементов ИЛИ (фиг,2) На этом преобразование первых, например, четырех разрядов двоичного кода закончено. Сигнал переполнения двоично-десятичного счетчика 73 с выхода е формирователя последовательности импульсов (фиг,) поступает на вход 5 блока 3 опроса (фиг,2) для формирования второго сигнала опроса следующих, например, четырех разрядов 2 -2° двоичного кода. Сигнал с входа б блока 3 опроса поступает на первый вход элемента ИЛИ 21, с выхода которого - на счетный вход счетчика 22, устанавлиг вая его в новое состояние. Информационные сигналы с выхода двоичного сметчика 22 поступают на входы элемента И 23i2 и на выходе этого элемента появляется второй сигнал опроса, поступающий на вход элемента И 17, на другие входы которого с входа d блока 3 опроса поступают сигналы с инверсных выходов разрядов двоичного кода. Если хотя бы один из одновременно опрашиваемых разрядов двоичного кода находится в единичном состоянии, сигнал с выхода элемента НЕ 16, поступающий на вход элемента И 1Ц,. разрешает прохождение импульсов тактовой частоты, так как триггер 13.управления находится в единичном сдстоянии. Сигнал с выхода элемента И I. поступает на выход t блока 3 опроса и далее на счетный вход двоично-десятичного счетчика 73. В дальнейшем работа преобразователя двоичного кода в двоично-десятичный аналогична описанной. Если все четыре одновременно опрашиваемые разряды, например, находятся в нулевом состоянии, си1- нал с выхода элемента ИЛИ 18 устанав ливает триггер 19 в единичное состояние, а сигнал с выхода элемента НЕ t6, поступающий на вход элемента И 1, запрещает прохождение импульсов тактовой частоты на выход t блока 3 опроса, т.е. в данном случае формирование последовательностей импульсо не происходит. Сигнал с прямого выхода триггера 19 поступает на вход элемента И 20, на другой вход которого поступает разрешающий потенциал с прямого выхода триггера 13 управления, и поэто му импульс тактовой частоты генерато (ja 15 тактовых импульсов поступает на вход элемента ИЛИ 21 и нулевой ус тановочный вход триггера 19, запреи ая дальнейшее прохождение серии импульсов через элемент И 20 (фиг.2). Тактовый импульс с выхода элемента ИЛИ 21 поступает на сметный вход двоично го счетчика 22, устанавливая его в новое состояние, и на выходе элемента И 23 появляется третий сигнал опроса разрядов двоичного кода. В дальнейшем работа преобразователя двоичного кода в двоично-десятичный происходит аналогично описанному. Таким образом, если опрашиваемые, например, четыре разряда двоичного . кода находятся в нулевом состоянии, то на выходе t блока 3 опроса сигнал поступащий на вход г блока 10 форми рования последовательностей импульсов , отсутствует, а на выходе В блока 3 опроса появляется следующий сиг нал опроса. Процесс преобразования двоичного кода в двоично-десятичный про должается до тех пор, пока не будут опрошены все разряды двоич ного кода, записанного в регистр 9. Как только произойдет преобразова ние последних, например, четырех, разрядов двоичного кода в двоичнодесятичный, процесс преобразования заканчивается. Идентификация последних, например четырех опрашиваемых разрядов двоичного кода происходит следующим образом. На.первые входы элементов И 25п 25„.,....ZS с входа d блока 3 опроса поступают сигналы с инверсных ВЫХОДОВ соответствующих разрядовj например , двоичного кода. На вторые входы элементов И 25, 25,,. ..., 25/1 поступает сигнал с выхода элемента НЕ 2 (фиг.2) поступающий также на первый вход элемента И 2(„, Сигнал с выхода элемента И 25п поступает на второй вход элемента И 25n-i на первый вход элемента И 2б,.-(фиг.2), сигнал с выхода элемента И 2Srj,a вход элемента И и на вход элемента И 26., сигнал с выхода элемента И 254 первый вход элемента И 263. На вторые входы элементов И 26, И 2бп-1 .. 2бз с входа блока 3 опроса поступают сиг- налы с прямых выходов соответствующих разрядов 2, 2,...,2 двоичного кода, на третьи входы элементов И 2б„, 26f,,,... ,262. сигналы опроса с выходов элементов И блока 3 опроса, при этом на третьи входы элементов И 26 -26 поступают сигналы опроса с выхода элемента И 23о иэ третьи входы элементов И 2б26-fo сигнал опроса с выхода элемента И 23з 43 третьи входы элементов И 2бп-з 2бо - сигнал опроса с выхода элемента И 23 блока 3 опроса. Если, например, из последней группы опрашиваемых разрядов двоичного кода разряд 2 находится в единичном состоянии, то на выходе элементов И 25 25 высокий уровень, а на выходе элементов И 2б, ,, ,..,2б низкий уровень и только на выходе элемента И сигнал высокого уровня, который поступает на вход элемента ИЛИ 27. Если, например, последний разряд двоичного кода находится в единичном состоянии, то на выходе всех элементов И сигнал отсутствует (низкий уровень) и только на выходе элемента И 2бп сигнал высокого уровня, поступающий на вход элемента ИЛИ 27. С выхода элемента ИЛИ 27 сигнал поступает на нулевой установочный вход триггера 13 управления, устанавливая его в нулевое состояние, в результате чего запрещается прохождение тактовых импульсов с генератора 15 через элементы И 1А и 20. Сигнал с выхода элемента ИЛИ 27 поступает также на единичный установочный вход триггера 28, устанавливая его в единичное состояние, и на первом входе элемента И 29 появляется разрещающий. 139 потенциал для прохождения тактовых импульсов, поступающих на второй Ёход этого элемента с генератора 15 тактовых импульсов. Сигнал с выхода элемента И 29 поступает на нулевой установочный вход триггера 28, на вход сброса счетчика 22 и на выход Э блока 3 опроса. Сигнал с выхода 3 блока 3 опроса поступает на нулевые установочные входы счетных декад 7,,-7ц десятичного счетчика 6, На нулевые установочные входы регистра 9 двоичного кода, на нулевой установочный вход двоично-десятичного счетчика 73 блок 10 формирования последовательностей импульсов, устанавливая их в нулевое состояние. После установки в нулевое состояние двоичного счетчика 22 или регистра 9 двоичного кода с выхода элемента ИЛИ 27 прекращается поступление сигнала Высокого уровня на единичный установочный вход триггера 28 и сигналом с выхода элемента И 29 он устанавливается в нулевое состоямне. На выходе элемента И 23 появля ется сигнал опроса,поступающий на вход элемента И 17 и на выход В бло ка 3 опроса. Таким образом происходит подготов ка .устройства к приему следующего сигнала Пуск и преобразования двоичного кода в двоично-десятичный. Время преобразования двоичного кода в двоично-десятичный равно T {N-J-9S)/fn. N - количество импульсов опроса S - количество групп одновремен но опрашиваемых разрядов двоичного кода, имеющих хот 1 бы один из разрядов в опрашиваемой группе, установлен-j ный в единичное состояние; частота следования тактовых импульсов. Количество импульсов опроса определяется из выражения N entler где п - число разрядов преобразуемого двоичного кода; а - количество одновременно опрашиваемых разрядов двоичного кода. Для практических целей целесообразно воспользоваться упрощенным., выражением, получаемым из выражения (t) при условии , определяющим максимальное время преобразования двоичного кода в двоично-десятичный Tl(. Максимальное время преобразования двоичного кода в двоично-десятичный известного преобразователя определяется из выражения число разрядов преобразуемогде п го двоичного кода; п частота следования тактовых импульсов. 8 табл.2 приведен коэффициент увеЛ1чения быстродействия предлагаемого устройства относительно максимального времени преобразования двоичного кода в двоично-десятичный в известном устройстве. Из табл.2 видно, что удается повысить быстродействие преобразователя не менее, чем в четыре раза.

ki

10/fn 20/fti 70/f 100/fn Формула изобретения 1, Преобразователь двоичного кода в двоично-десятичный, содержащий группу элементов Jt, первые входы которых соединены с информационными входами преобразователя, блок опроса первый вход которого соединен с входом пуска преобразователя, десятичьы счетчик, состоящий из (п-1 )-го элемента задержки и П декад, выходы каж дой из которых, кроме п-й, соответст венно соединены с входом элемента задержки, регистр двоичного кода, шифратор, группу элементов ИЛИ, информационные входы которых соединены с выходами шифратора, выходы элементов ИЛИ группы соединены со счетными входами соответствующих декад десятичного счетчика, выход 1-го элеменЦ

t

kQ/fn

30/fn

190/fn 150/f

,75 та задержки (n-1), где п - число десятичных разрядов, соединен с дополнительным входом ()-ro элемента ИЛИ группы, отличающийс я тем, что, с целью повышения быстродействия пресйразователя,:в него введен формирователь последовательности импульсов,.тактовый вход которого соединен с тактовым выходом блока опроса, выход сброса которого соединен с тактовым входом регистра двоичного кода, входами сброса декад и с входом сброса формирователя последовательности импульсов, тактовый выход которого соединен с тактовым входом шифратора, информационный вход которого соединен с выходом регистра двоичного кода и с первым информационным входом блока опроса, . втopым информационным входом соединенного с входом логического нуля преобразователя, выход блока опроса соединен с входом опроса шифратора, вход переключения блока опроса соеди нен с выходом конца пачки формирователя последовательности импульсов, информационный вход регистра двоичного кода соединен с первой группой выходов элементов И, вторая группа выходов которого соединена с информационными входами первой декады десятичного счетчика, а вторые входы всех элементов И группы соединены с входом пуска преобразователя. 2. Преобразователь по п.1, о т ли чающийся тем, что в нем блок опроса содержит четыре группы элементов И, счетчик, генератор импульсов, два элемента НЕ, три элемента И, три элемента ИЛИ, триггер сброса, триггер переключения групп и триггер управления, единичный вход которого является входом пуска блока опроса, нулевой вход соединен с выходом первого элемента ИЛИ и с единичным входом триггера сброса, а выход триггера управления соединен с первыми входами первого и второго элементов И, вторые входы которых со единены с выходом генератора импуль- зо

сов -и с первым входом третьего элемента И, второй вход которого соединен с единичным выходом триггера сброса, а выход третьего элемента И является выходом сброса блока опроса jj ния

и соединен с нулевым входом триггера сброса и с входом сброса счетчика, выходы которого соединены с входами элементов И первой группы, выходы которых являются выходами опроса блока опроса 4о и соединены с первыми входами элементов И второй и третьей групп, а счетный вход счетчика соединен с выходом второго элемента ИЛИ, первый вход которого является входом пере- 5 ключения блока опроса, а второй вход соединен с выходом второго элемента И и нулевым входом триггера переключения групп, выход которого соединен с третьим входом второго элемента И, „ а единичный вход триггера переключения групп соединен с выходом третьеветственно тактовым входом и входом сброса формирователя последовательности импульсов, выход конца пачки которого является выходом переполнеразрядные выходы которого соединены с информационными входами дешифратора , тактовый вход которого соединен с тактовым входом формирователя посми с k-ro по элементов ИЛИ группы, выходы элементов ИЛИ группы являются тактовыми выходами формирователя последовательности импульсов.

Источники информации, принятые во внимание -при экспертизе

0ui.f H

I

(fa г. г

щ

7/1

to

%

1

(PU2. У

Авторы

Даты

1982-07-07—Публикация

1980-09-22—Подача