Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах индикации.

Цель изобретения - повышение достоверности устройства за счет сохранения неизменной яркости свечения индикаторов при увеличении их числа.

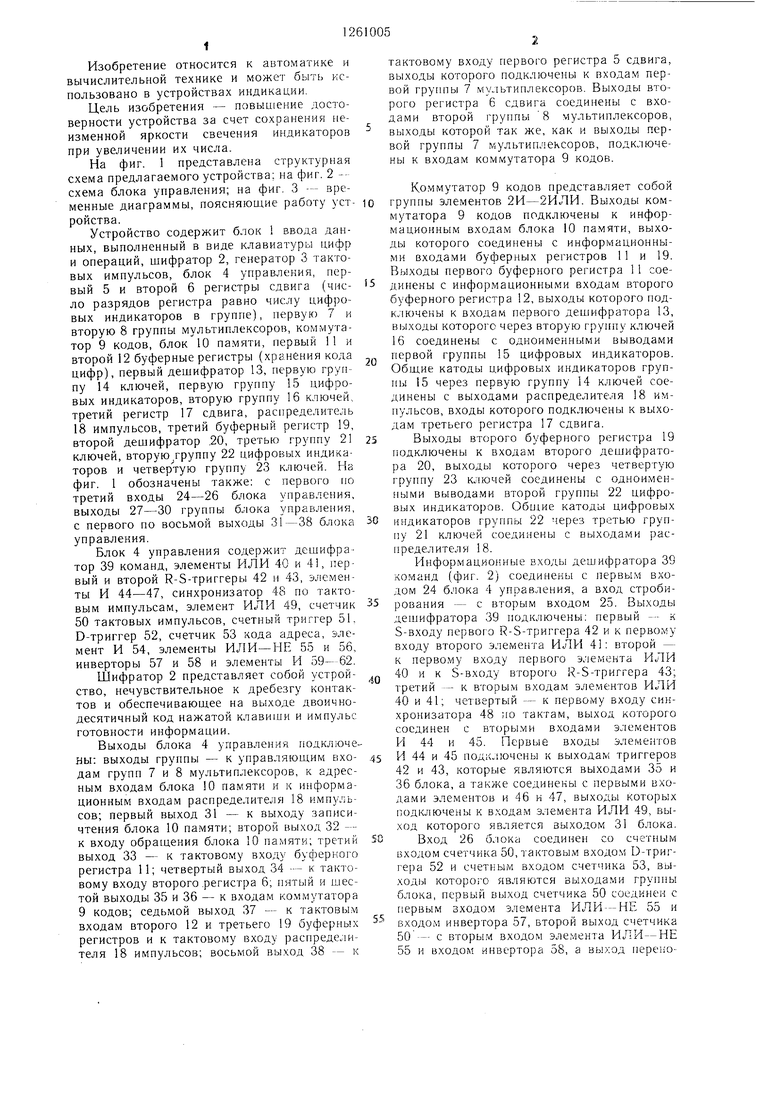

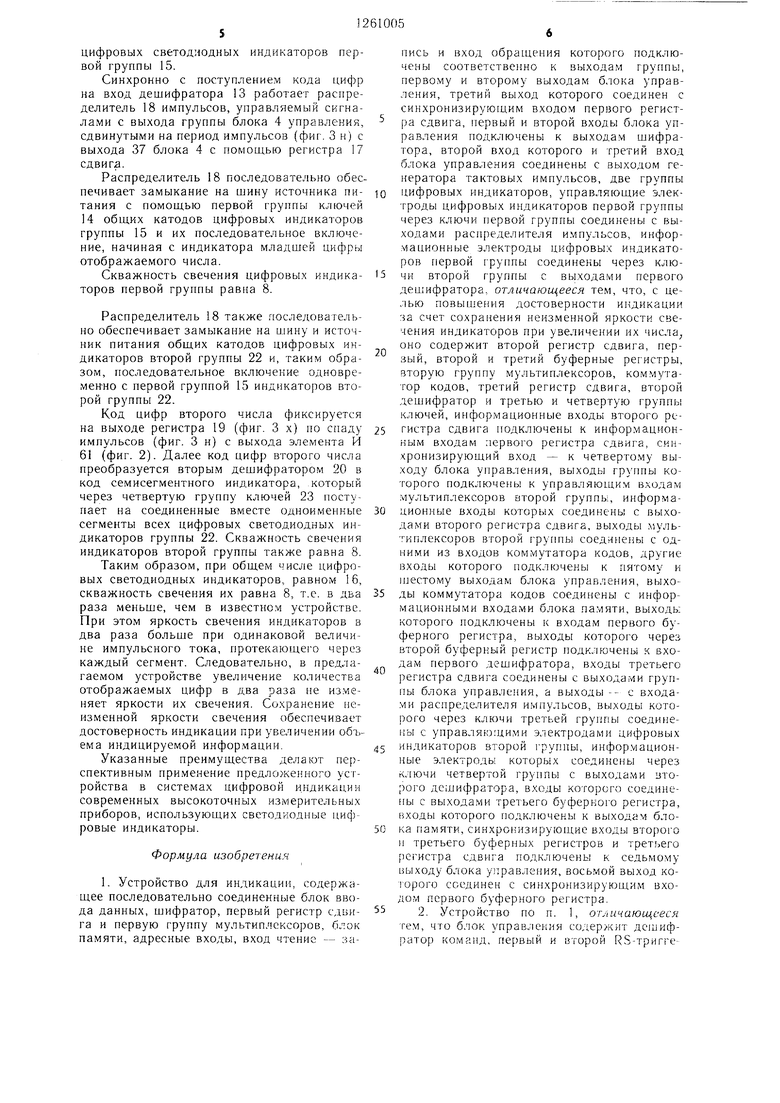

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 -- схема блока управления; на фиг. 3 -- временные диаграммы, поясняющие работу уст- ю группы элементов 2И-2ИЛИ. Выходы комтактовому входу первого регистра 5 сдвига, выходы которого подключены к входам первой группы 7 мультиплексоров. Выходы второго регистра 6 сдвига соединены с входами второй I pyrinbi 8 мультиплексоров, выходы которой так же, как и выходы первой группы 7 мультиплексоров, подключены к входам коммутатора 9 кодов.

Ко.ммутатор 9 кодов представляет собой

мутатора 9 кодов подключены к информационным входа.м блока 10 памяти, выходы которого соединены с информационными входами буферных регистров 11 и 19. Выходы первого буферного регистра I 1 сое- 5 динены с информационными входам второго буферного регистра 12, выходы которого под- к входам первого дешифратора 13, выходы которого через вторую группу ключей 16 соединены с одноименными выводами первой группы 15 цифровых индикаторов. Общие катоды цифровых индикаторов группы 15 через первую группу 14 ключей соединены с выходами распределителя 18 импульсов, входы которого подключены к выходам третьего регистра 17 сдвига.

роиства.

Устройство содержит блок ввода данных, выполненный в виде клавиатуры цифр и операций, шифратор 2, генератор 3 тактовых имнульсов, блок 4 управления, первый 5 и второй 6 регистры сдвига (число разрядов регистра равно числу цифровых индикаторов в группе), первую 7 и вторую 8 группы мультиплексоров, коммутатор 9 кодов, блок 10 памяти, первый 11 и второй 12 буферные регистры (хранения кода цифр), первый дешифратор 13, первую группу 14 ключей, первую группу 15 цифровых индикаторов, вторую группу 16 ключей, третий регистр 17 сдвига, распределитель 18 импульсов, третий буферный регистр 19, второй дешифратор .20, третью группу 2 25 ключей, вторую группу 22 цифровых индикаторов и четвертую группу 23 ключей. На фиг. 1 обозначены также: с первого по третий входы 24-26 блока управления, выходы 27-30 группы блока управления.

мутатора 9 кодов подключены к информационным входа.м блока 10 памяти, выходы которого соединены с информационными входами буферных регистров 11 и 19. Выходы первого буферного регистра I 1 сое- 5 динены с информационными входам второго буферного регистра 12, выходы которого под- к входам первого дешифратора 13, выходы которого через вторую группу ключей 16 соединены с одноименными выводами первой группы 15 цифровых индикаторов. Общие катоды цифровых индикаторов группы 15 через первую группу 14 ключей соединены с выходами распределителя 18 импульсов, входы которого подключены к выходам третьего регистра 17 сдвига.

Выходы второго буферного регистра 19 подключены к входам второго дешифратора 20, выходы которого через четвертую группу 23 Ко1ючей соединены с одноименными выводами второй группы 22 цифровых индикаторов. Обп;ие катоды цифровых

с первого по восьмой выходы 31-38 блока 30 индикаторов группы 22 через третью групIIу 21 ключей соединены пределителя 18.

управления.

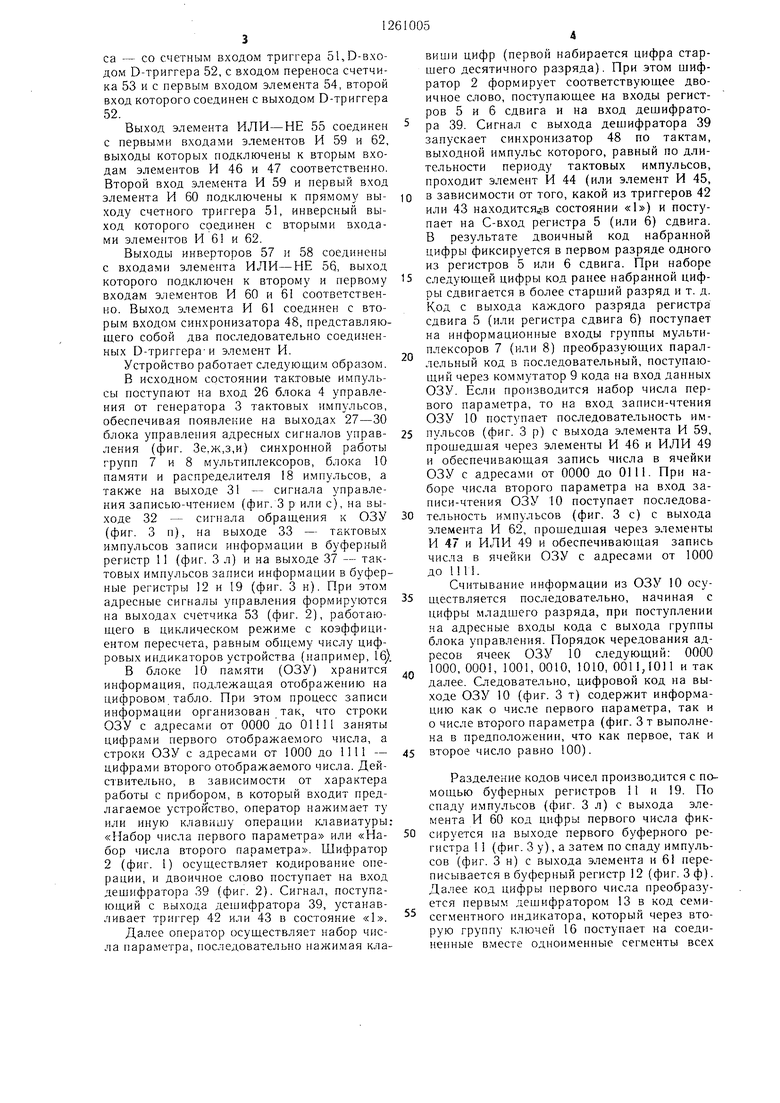

Блок 4 управления содержит дешифратор 39 команд, элементы ИЛИ 40 и 41, первый и второй R-S-триггеры 42 п 43, элементы И 44-47, синхронизатор 48 по тактовым импульсам, элемент ИЛИ 49, счетчик 50 тактовых импульсов, счетный триггер 51. D-триггер 52, счетчик 53 кода адреса, элемент И 54, элементы ИЛИ-НЕ 55 и 56, инверторы 57 и 58 и элементы И 59-62.

Шифратор 2 представляет собой устрой- ство, нечувствительное к дребезгу контактов и обеспечивающее на выходе двоично- десятичный код нажатой клавиши и импульс готовности информации.

Выходы блока 4 управлен.чя подключены: выходы группы - к управляющим входам групп 7 и 8 мультиплексоров, к адресным входам блока 10 памяти и к информационным входам распределителя 18 импульсов; первый выход 31 - к выходу записи- чтения блока 10 памяти; второй выход 32 -- к входу обращения блока 10 памяти; третий выход 33 - к тактовому входу буферного регистра 11; четвертый выход 34 -- к Tainx )- вому входу второго .регистра 6; пятый и шестой выходы 35 и 36 - к входам коммутатора 9 кодов; седьмой выход 37 -- к тактовым входам второго 12 и третьего 19 буферных регистров и к тактовому входу распределителя 18 импульсов; восьмой выход 38 - к

группы элементов 2И-2ИЛИ. Выходы комтактовому входу первого регистра 5 сдвига, выходы которого подключены к входам первой группы 7 мультиплексоров. Выходы второго регистра 6 сдвига соединены с входами второй I pyrinbi 8 мультиплексоров, выходы которой так же, как и выходы первой группы 7 мультиплексоров, подключены к входам коммутатора 9 кодов.

ппы элементов 2И-2ИЛИ. Выходы комКо.ммутатор 9 кодов представляет собой

группы элементов 2И-2ИЛИ. Выходы ком

мутатора 9 кодов подключены к информационным входа.м блока 10 памяти, выходы которого соединены с информационными входами буферных регистров 11 и 19. Выходы первого буферного регистра I 1 сое- динены с информационными входам второго буферного регистра 12, выходы которого под- к входам первого дешифратора 13, выходы которого через вторую группу ключей 16 соединены с одноименными выводами первой группы 15 цифровых индикаторов. Общие катоды цифровых индикаторов группы 15 через первую группу 14 ключей соединены с выходами распределителя 18 импульсов, входы которого подключены к выходам третьего регистра 17 сдвига.

Выходы второго буферного регистра 19 подключены к входам второго дешифратора 20, выходы которого через четвертую группу 23 Ко1ючей соединены с одноименными выводами второй группы 22 цифровых индикаторов. Обп;ие катоды цифровых

индикаторов группы 22 через третью групиндикаторов группы 22 через третью груп

выходами расIIу 21 ключей соединены пределителя 18.

Информац.иоь;ные входы дешифратора 39 команд (фиг. 2) соединены с первым входом 24 блока 4 управления, а вход строби- рования - с вторым входом 25. Выходы .дешифратора 39 подключены: первый -- к S-входу первого R-S-триггера 42 и к первому входу второго элемента ИЛИ 41: второй - к первому входу первого элемента ИЛИ 40 и к S-входу второго R-S-триггера 43; третий - к вторым входам элементов ИЛИ 40 и 41; четвертый -- к первому входу синхронизатора 48 но тактам, выход которого соединен с вторыми входами элементов И 44 и 45. Первые входы элементов И 44 и 45 подключены к выходам триггеров 42 и 43, которые являются выходами 35 и 36 блока, а также соединены с первыми входами элементов и 46 и 47, выходы которых подключены к входам .элемента ИЛИ 49, выход которого является выходом 31 блока.

Вход 26 блока соединен со счетным входом счетчика 50, тактовым входом D-триг- гера 52 и счетным входом счетчика 53, выходы которого являются выходами группы блока, первый выход счетчика 50 соединен с первым входом элемента ИЛИ - НЕ 55 и

входом инвертора 57, второй выход счетчика 50 --- с вторым входом эле.мента ИЛИ-НЕ 55 и входом инвертора 58, а вы.ход nepeiioса - со счетным входом триггера о 1,0-входом D-триггера 52, с входом переноса счетчика 53 и с первым входом элемента 54, второй вход которого соединен с выходом D-триггера 52.

Выход элемента ИЛИ-НЕ 55 соединен с первыми входами элементов И 59 и 62, выходы которых подключены к вторым входам элементов И 46 и 47 соответственно. Второй вход элемента И 59 и первый вход элемента И 60 подключены к прямому выходу счетного триггера 51, инверсный выход которого соединен с вторыми входами элементов И 61 и 62.

Выходы инверторов 57 и 58 соединены с входами элемента ИЛИ-НЕ 56, выход которого подключен к второму и первому входам элементов И 60 и 61 соответственно. Выход элемента И 6 соединен с вторым входом синхронизатора 48, представляющего собой два последовательно соединенных D-триггера-и элемент И.

Устройство работает следующим образом.

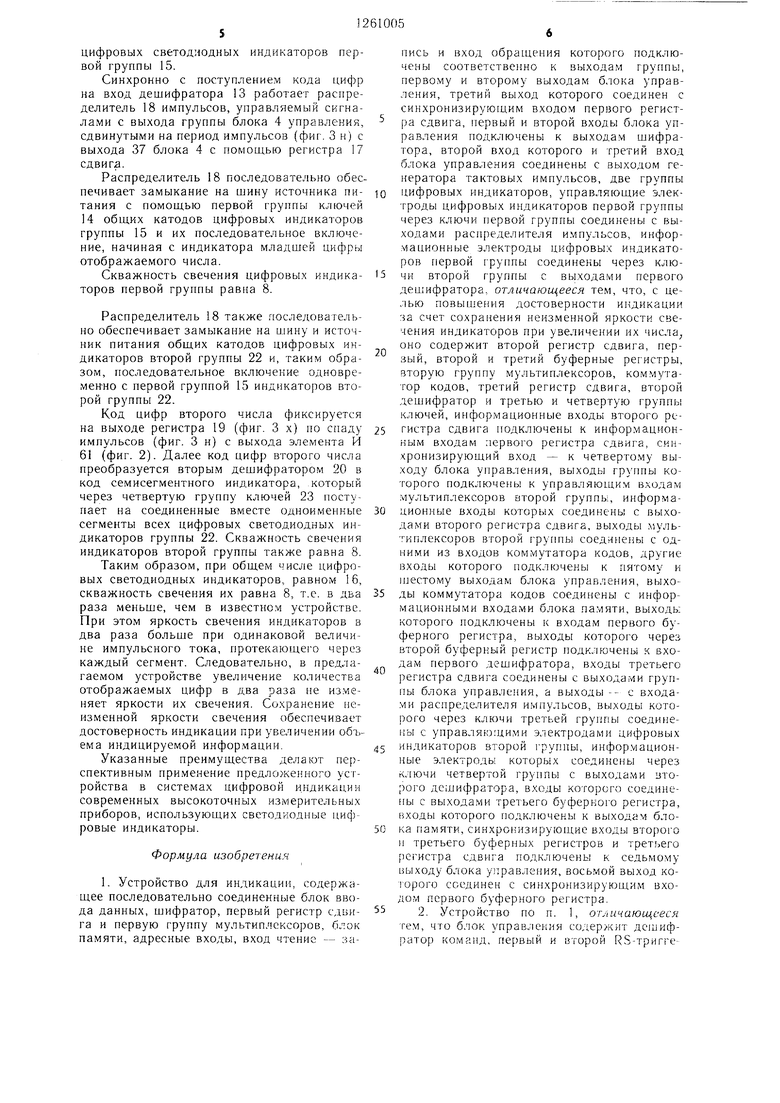

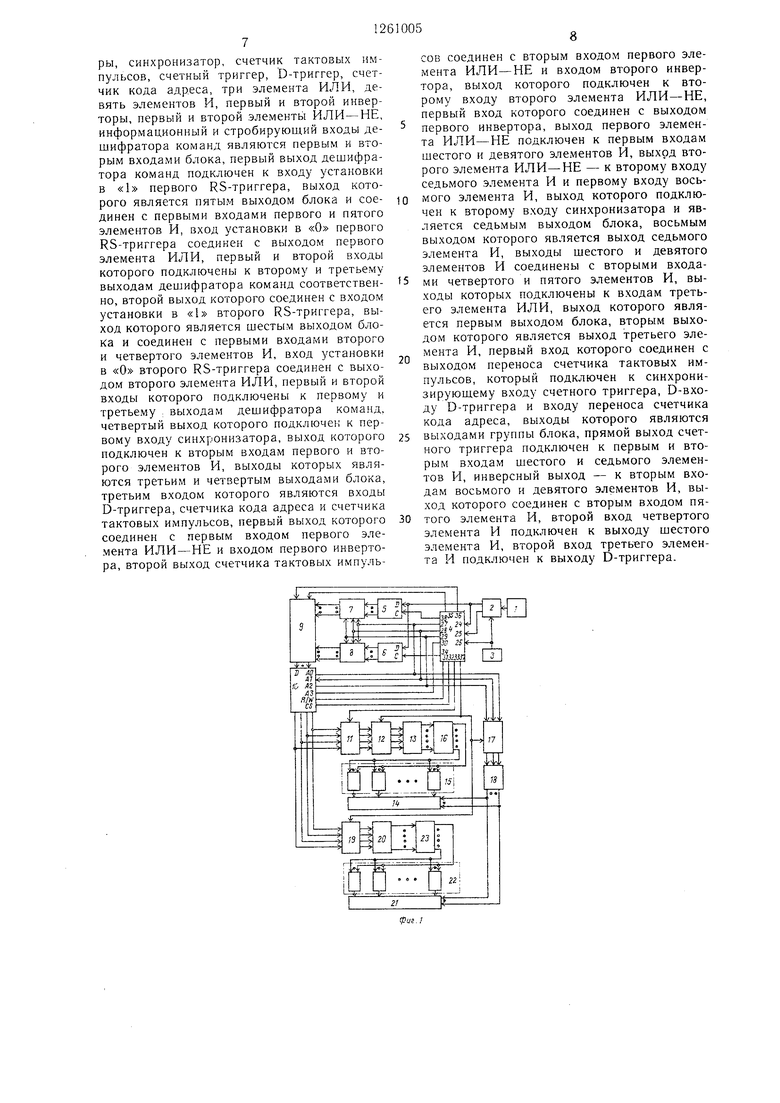

В исходном состоянии тактовые импульсы поступают на вход 26 блока 4 управления от генератора 3 тактовых импульсов, обеспечивая появление на выходах 27-30 блока управления адресных сигналов управления (фиг. Зе,ж,з,и) синхронной работы групп 7 и 8 мультиплексоров, блока Ш памяти и распределителя 18 импульсов, а также на выходе 31 - сигнала управления записью-чтением (фиг. 3 р или с), на выходе 32 - сигнала обращения к ОЗУ (фиг. 3 п), на выходе 33 - тактовых импульсов записи информации в буферный регистр 11 (фиг. 3 л) и на выходе 37 - тактовых импульсов записи информации в буферные регистры 12 и 19 (фиг. 3 и). При этом адресные сигналы управления фор.мируются на выходах счетчика 53 (фиг. 2), работающего в циклическом режиме с коэффициентом пересчета, равным общему числу цифровых индикаторов устройства (например, 16).

В блоке 10 памяти (ОЗУ) хранится информация, подлежащая отображению на цифрово.м табло. При этом процесс записи информации организован так, что строки ОЗУ с адресами от 0000 до ОНИ заняты цифрами первого отображаемого числа, а строки ОЗУ с адресами от 1000 до 1111 - цифрами второго отображаемого числа. Действительно, в зависимости от характера работы с прибором, в который входит предлагаемое устройство, оператор нажимает ту или иную клавишу операции клавиатуры: «Набор числа первого параметра или «Набор числа второго параметра. Шифратор 2 (фиг. 1) осуществляет кодирование операции, и двоичное слово поступает на вход дещифратора 39 (фиг. 2). Сигнал, поступающий с выхода дец ифратора 39, устанавливает триггер 42 или 43 в состояние «1.

Далее оператор осуществляет набор числа параметра, последовательно нажимая кла0

0

виши цифр (первой набирается цифра старшего десятичного разряда). При этом шифратор 2 формирует соответствующее двоичное слово, поступающее на входы регистров 5 и 6 сдвига и на вход дешифратора 39. Сигнал с выхода дешифратора 39 запускает синхронизатор 48 по тактам, выходной импульс которого, равный по длительности периоду тактовых импульсов, проходит элемент И 44 (или элемент И 45, в зависимости от того, какой из триггеров 42 или 43 находится в состоянии «1) и поступает на С-вход регистра 5 (или 6) сдвига. В результате двоичный код набранной цифры фиксируется в первом разряде одного из регистров 5 или 6 сдвига. При наборе 5 следующей цифры код ранее набранной цифры сдвигается в более старший разряд и т. д. Код с выхода каждого разряда регистра сдвига 5 (или регистра сдвига 6) поступает на информационные входы группы мультиплексоров 7 (или 8) преобразующих параллельный код в последовательный, поступающий через ко.ммутатор 9 кода па вход данных ОЗУ. Если производится набор числа первого параметра, то на вход записи-чтения ОЗУ 10 поступает последовательность импульсов (фиг. 3 р) с выхода элемента И 59, прошедщая через элементы И 46 и ИЛИ 49 и обеспечивающая запись числа в ячейки ОЗУ с адресами от 0000 до 0111. При наборе числа второго параметра на вход записи-чтения ОЗУ 10 поступает последовательность импульсов (фиг. 3 с) с выхода элемента И 62, прошедшая через элементы И 47 и ИЛИ 49 и обеспечивающая запись числа в ячейки ОЗУ с адресами от 1000 до 1111.

Считывание информации из ОЗУ 10 осуществляется последовательно, начиная с цифры младшего разряда, при поступлении на адресные входы кода с выхода группы блока управления. Порядок чередования адресов ячеек ОЗУ 10 следующий: 0000 1000, 0001, 1001, 0010, 1010, 0011,1011 и так далее. Следовательно, цифровой код на выходе ОЗУ 10 (фиг. 3 т) содержит информацию как о числе первого параметра, так и о числе второго параметра (фиг. 3 т выполнена в предположении, что как первое, так и второе число равно 100).

5

0

0

5

0

5

Разделение кодов чисел производится с помощью буферных регистров 11 и 19. По спаду импульсов (фиг. 3 л) с выхода элемента И 60 код цифры первого числа фиксируется на выходе первого буферного регистра 11 (фиг. 3 у), а затем по спаду импульсов (фиг. 3 н) с выхода элемента и 61 переписывается в буферный регистр 12 (фиг. Зф). Далее код цифры первого числа преобразуется первым дешифратором 13 в код семи- сегментного индикатора, который через вторую группу ключей 16 поступает на соединенные вместе одноименные сегменты всех

цифровых светодиодных индикаторов первой группы 15.

Синхронно с поступлением кода цифр на вход дешифратора 13 работает распределитель 18 импульсов, управляемый сигна- ла1ми с выхода группы блока 4 управления, 5 сдвинутыми на период импульсов (фиг. 3 н) с выхода 37 блока 4 с помощью регистра 17 сдвига.

Распределитель 18 последовательно обеспечивает замыкание на шину источника пн- ю тания с помощью первой группы ключей 14 общих катодов цифровых индикаторов группы 15 и их последовательное включение, начиная с индикатора младшей цифры отображаемого числа.

Скважность свечения цифровых индика- 5 торов первой группы равна 8.

Распределитель 18 также последовательно обеспечивает замыкание на тину и источник питания общих катодов цифровых индикаторов второй группы 22 и, таким образом, последовательное включение одновре- мен но с первой группой 15 индикаторов второй группы 22.

Код цифр второго числа фиксируется на выходе регистра 19 (фиг. 3 х) по спаду 25 импульсов (фиг. 3 н) с выхода элемента И 61 (фиг. 2). Далее код цифр второго числа преобразуется вторым дешифратором 20 в код семисегментного индикатора, который через четвертую группу ключей 23 поступает на соединенные вместе одноименные 30 сегменты всех цифровых светодиодных индикаторов группы 22. Скважность свечения индикаторов второй группы также равна 8.

Таким образом, при общем числе цифровых светодиодных индикаторов, равном 16,

20

пись и вход обра цения которого подключены соответственно к выходам группы, первому и второму выходам блока управления, третий выход которого соединен с синхронизирующим входом первого регистра сдвига, первый и второй входы блока управления подключены к выходам шифратора, второй вход которого и третий вход блока управления соединены с выходом генератора тактовых импульсов, две группы цифровых индикаторов, управляющие электроды цифровых индикаторов первой группы через ключи первой группы соединены с выходами распределителя импульсов, информационные электроды цифровых индикаторов первой группы соединены через ключи второй группы с выходами первого дешифратора, отличающееся тем, что, с целью повышения достоверности индикации за счет сохранения неизменной яркости свечения индикаторов при увеличении их числа., оно содержит второй регистр сдвига, первый, второй и третий буферные регистры, вторую группу мультиплексоров, коммутатор кодов, третий регистр сдвига, второй дешифратор и третью и четвертую группы ключей, информационные входы второго регистра сдвига подключены к информационным входам первого регистра сдвига, синхронизирующий вход - к четвертому выходу блока управления, выходы группы которого подключены к управляющим входам мультиплексоров второй группы, информационные входы которых соединены с выходами второго регистра сдвига, выходы .уль- иплексоров второй группы соединены с одними из входов коммутатора кодов, другие входы которого подключены к пятому и HjecTOMy выходам блока управления, выхоскважность свечения их равна 8, т.е. в два 35 ды коммутатора кодов соединены с инфорраза меньше, чем в известно. устройстве. При этом яркость свечения индикаторов в два раза больше при одинаковой величине импульсного тока, протекающего через каждый сегмент. Следовательно, в предлагаемом устройстве увеличение количества отображаемых цифр в два раза не изменяет яркости их свечения. Сохранение неизменной яркости свечения обеспечивает достоверность индикации при увеличении объема индицируемой информации.

Указанные преимущества делают перспективным применение предложенного устройства в системах цифровой индикации современных высокоточных измерительных приборов, использующих светодиодные цифровые индикаторы.

Формула изобретения

1. Устройство для индикации, содержащее последовательно соединенные блок ввода данных, шифратор, первый регистр сдви- га и первую группу мультиплексоров, блок памяти, адресные входы, вход чтение - за

пись и вход обра цения которого подключены соответственно к выходам группы, первому и второму выходам блока управления, третий выход которого соединен с синхронизирующим входом первого регистра сдвига, первый и второй входы блока управления подключены к выходам шифратора, второй вход которого и третий вход блока управления соединены с выходом генератора тактовых импульсов, две группы цифровых индикаторов, управляющие электроды цифровых индикаторов первой группы через ключи первой группы соединены с выходами распределителя импульсов, информационные электроды цифровых индикаторов первой группы соединены через ключи второй группы с выходами первого дешифратора, отличающееся тем, что, с целью повышения достоверности индикации за счет сохранения неизменной яркости свечения индикаторов при увеличении их числа., оно содержит второй регистр сдвига, первый, второй и третий буферные регистры, вторую группу мультиплексоров, коммутатор кодов, третий регистр сдвига, второй дешифратор и третью и четвертую группы ключей, информационные входы второго регистра сдвига подключены к информационным входам первого регистра сдвига, синхронизирующий вход - к четвертому выходу блока управления, выходы группы которого подключены к управляющим входам мультиплексоров второй группы, информационные входы которых соединены с выходами второго регистра сдвига, выходы .уль- иплексоров второй группы соединены с одними из входов коммутатора кодов, другие входы которого подключены к пятому и HjecTOMy выходам блока управления, выхо

мационными входами блока памяти, выходы которого подключены к входам первого буферного регистра, выходы которого через второй буферный регистр подключены .ч входам первого дешифратора, входы третьего регистра сдвига соединены с выхода Ми группы блока управления, а выходы -- с входами распределителя и.мпульсов, выходь которого через ключи третьей группы соединены с управляющими электродами цифровых индикаторов второй группы, инфор.мацион- ные электроды которых соединены через к, 1ючи четвертой группы с выходами второго дсчцифратора, входы которого соединены с выхода.ми третьего буферного регистра, входы которого подключены к выходам блока памяти, синхронизирующие входы второго н третьего буферных регистров и третьего регистра сдвига подключены к седьмому выходу блока у травления, восьмой выход которого соединен с синхронизирующим входом первого буферного регистра.

2. Устройство по п. 1, отличающееся тем, что блок управления содержит дешифратор команд, первый и второй RS-триггеры, синхронизатор, счетчик тактовых импульсов, счетный триггер, D-триггер, счетчик кода адреса, три элемента ИЛИ, девять элементов И, первый и второй инверторы, первый и второй элементь ИЛИ-НЕ, информационный и стробирующкй входы дешифратора команд являются первым и вторым входами блока, первый выход дешифратора команд подключен к входу установки в «1 первого RS-триггера, выход которого является пятым выходом блока и соединен с первыми входами первого и пятого элементов И, вход установки в «О первого RS-триггера соединен с выходом первого элемента ИЛИ, первый и второй входы которого подключены к второму и третьему выходам дешифратора команд соответственно, второй выход которого соединен с входом установки Б «1 второго RS-триггера, выход которого является шестым выходом блока и соединен с первыми входами второго и четвертого элементов И, вход установки в «О второго RS-триггера соединен с Bbixoj дом второго элемента ИЛИ, первый и второй входы которого подключены к первому и третьему ; выходам дешифратора команд, четвертый выход которого подключен к первому входу синхронизатора, выход которого подключен к вторым входам первого и второго элементов И, выходы которых являются третьим и четвертым выходами блока, третьим входом которого являются входы D-триггера, счетчика кода адреса и счетчика тактовых импульсов, первый выход которого соединен с первым входом первого элемента ИЛИ-НЕ и входом первого инвертора, второй выход счетчика тактовых импульсов соединен с вторым входом первого элемента ИЛИ-НЕ и входом второго инвертора, выход которого подключен к второму входу второго элемента ИЛИ-НЕ, первый вход которого соединен с выходом

первого инвертора, выход первого элемента ИЛИ-НЕ подключен к первым входам шестого и девятого элементов И, выход второго элемента ИЛИ-НЕ - к второму входу седьмого элемента И и первому входу восьмого элемента И, выход которого подключен к второму входу синхронизатора и является седьмым выходом блока, восьмым выходом которого является выход седьмого элемента И, выходы шестого и девятого элементов И соединены с вторыми входами четвертого и пятого элементов И, выходы которых подключены к входам третьего элемента ИЛИ, выход которого является первым выходом блока, вторым выходом которого является выход третьего элемента И, первый вход которого соединен с выходом переноса счетчика тактовых импульсов, который подключен к синхрони- зируюш,ему входу счетного триггера, D-BXO- ду D-триггера и входу переноса счетчика кода адреса, выходы которого являются

выходами группы блока, прямой выход счетного триггера подключен к первым и вторым входам шестого и седьмого элементов И, инверсный выход - к вторым входам восьмого и девятого элементов И, выход которого соединен с вторым входом пятого элемента И, второй вход четвертого элемента И подключен к выходу шестого элемента И, второй вход третьего элемента И подключен к выходу D-триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода и вывода информации | 1980 |

|

SU920692A1 |

| Устройство для ввода и вывода информации | 1982 |

|

SU1048466A1 |

| Программно-управляемый генератор синусоидальных колебаний | 1985 |

|

SU1451830A1 |

| Устройство для цифровой индикации | 1981 |

|

SU1045226A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для ввода и вывода информации | 1985 |

|

SU1265755A1 |

| Устройство передачи информации по волоконно-оптической линии связи | 1988 |

|

SU1675919A1 |

| Устройство для ввода информации | 1985 |

|

SU1327087A1 |

| Оптико-электронное устройство для измерения линейных перемещений | 1988 |

|

SU1620835A1 |

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах индикации. Цель изобретения - повышение достоверности устройства за счет сохранения неизменной яркости свечения индикаторов при увеличении их числа. Цель достигается введением второго и третьего регистров сдвига, трех буферных регистров, второй и третьей групп мультиплексоров, коммутатора кодов, второго дешифратора, третьей и четвертой групп ключей с соответ- ствуюш.ими функциональными связями, что позволяет индицировать информацию одновременно на обеих группах индикаторов, 1 з.п.ф-лы, 3 ил. 1C О5

ляшитл TLi, :i z z zzrz zzzraruiruL

Jl..ггrlJ J-l п.JTJПLЛJ JTJп г гL. пгтгпг и-т тогтгтгпг1гтгтгтгт- иJlJlJIjrLJl JbJ-LJl aJT j UlJIJT-JlJllJLJlJ.riJLJLJrUlJlJ JLJLJl n JLJT

U LJ

.ri JlJlJl JlJbJbJLJLJL n n ri. I ЛлП П П П n П

ЛП.IIГll rL JL-

фи.. 3

Составитель В. Сметании

Речактор М. ЦиткннаТехред И. ВересКорректор В. Езутяга

Заказ 5237/52Тираж 455Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий

113035, Москва, Ж--35, Раушская наб., д. 4/5

Филиал ППП «Патент, г. Ужгород, ул. Проектная, 4

| Устройство для цифровой индикации | 1975 |

|

SU643921A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1986-09-30—Публикация

1985-04-17—Подача