i

Изобретение относится к вычислительной технике и может Ьыть использовано в автоматизированных системах управления, диагностических системах, системах сбора и обработки информации. , .

Известно устройство для приоритетного обслуживания заявок, содержащее счетчик, дешифратор, элементы И, три элемента ИЛИ, два КЗ триггера, два элемента НЕ, элемент задержки .

Недостатком устройства является невозможность изменения порядка обсл живания поступающих на вход устройства запросов..

Наиболее близким к изобретению по технической сущности является устройство для обслуживания, запросов, содержащее блок приоритета, кодовый вход и выход которого являются соответственно запросным входом и ра решающим выходом .устройства, триггер выход которого и тактовый вход устройст-ва через элемент И соединены с счетным входом счетчика, )ратор, выход которого соединен с опросным входом блока приоритета, причем выход блока приоритета соединен с гасящим входом триггера, -установочный вход которого является первым управляющим входом устройства, а выход счетчика соединен с входом дешифратора и с выходом прерывания устройства, регистр, выход которого, соединен с установочным входом счетчика и через элемент ИЛИ с запускающим входом генератора одиночных импульсов, разрешающий вход которого через элемент НЕ соединен с выходом блока приоритета, а щторой управляющий вход устройства является входом регистраС.2. .

Однако в известном устройстве, в любом случае, производится опрос всех запросных входов и нет возможности производить опрос в произвольном порядке. Это ведет кУвеличению времени ожидания опроса групп запросов, необходимого для К-и задачи.

Цель изобретения - повышение быстродействия засчет уменьшения времени ожидания опроса групп запросов,

.Для достижения поставленной цели в устройство, содержащее блок приоритета, кодовый вход и выход которого являются соответственно запросным входом и разрешающим выходом yci

i 99112

ройствэ, триггер, выход которого и тактовый вход устройства соединены соответственно с первым и вторым входами элемента И, ыход которого сое5 динен с счетным входом счетчика, дешифратор, выход которого соединен с опросным входом блока приоритета, причем выход блока приоритета соединен с гасящим входом триггера, ус10 тановочный вход которого является разрешающим входом устройства, а выход счетчика соединен с входом дешифратора и с выходом прерывания устройства, элемент ИЛИ, введены N ком15 параторов (N - количество запросов), каждый из которых содержит два регистра, схему сравнения, элемент И и элемент ИЛИ, первый вход которого соединен с входом запуска устрой20 ства, выход элемента ИЛИ - с первым входом элемента И и с соответствующим входом элемента ИЛИ устройства, установочные входы устройства подключены к.входам соответствующих

25 регистров, выход первого регистра соединен с вторым входом элемента И, выход которого соединен с установочным входом счетчика, выход второго регистра соединён с первым

30 входом схемы сравнения, второй вход которой соединен с выходом счетчика , а выход схемы сравнения соединен с вторым входом элемента ИЛИ последующего компаратора, выход схемы сравнения последнего компаратора соединен с вторым входом элемента ИЛИ первого компаратора, выход элемента ИЛИ устройства соединен с управляющим входом счетчика,

др Схема компаратора осуществляет сравнение двух двоичных чисел, одно из которых хранится на одном из регистров компаратора, а другое подается на информационный вход компаj ратора, . .

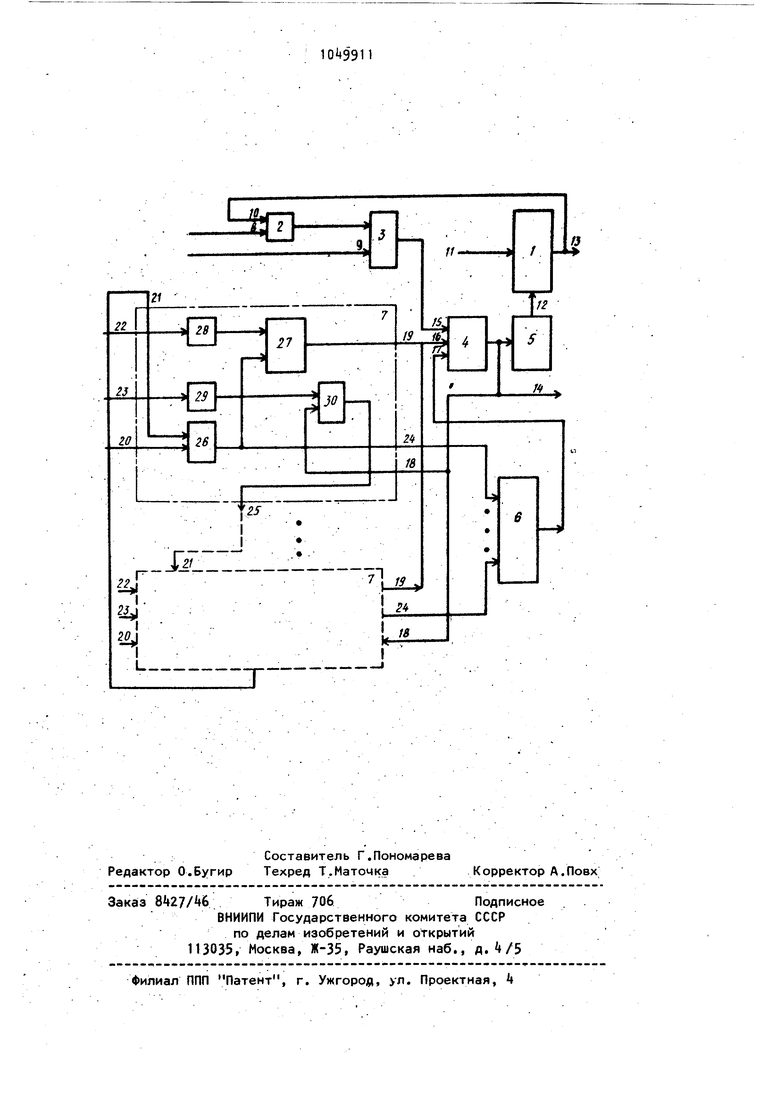

На чертеже представлена структурная схема устройства.

Устройство содержит блок 1 приоритета,, триггер 2, элемент.И 3, счетчик , дешифратор 5, элемент ИЛИ 6, N компараторов 7 и имеет разрешающий 8, тактовый 9-, гасящий 10, запросный 11, опросный 12 входы, разрешающий выход 13 и выход рываний,

метчик имеет счетный 15, установочный 16, управляющий 17 входы, а компаратор 7 - информационный

вход iSf информационный выход 19, входы 20 и 21 запуска, установочные входы 22 и 23 и управляющие выходы и 25. Компаратор 7 содержит элемент ИЛИ 26, элемент И 27, регистры 28 и 29 и схему 30 сравнения.

Блок 1 содержит элемент ИЛИ и N элементов И, первые и вторые входы которых соединены соответственно с кодовым и опросным входами блока, а выходы - с входами элемента ИЛИ, выход которого соединен с выходом блока.

Устройство работает следующим образом..

В регистры 28 и 29 М компара- торов 7 через установочные входы 22 и 23 предварительно, записываются коды начала и конца выбранных групп запросов. В предлагаемом устройстве цикл опроса запросов можно начинать с начала любой выбранной группы, для чего на вход 20 запуска соответствующего п-го компаратора 7 подается импульсный сигнал Начало опроса. Сигнал с вхоДа 20 проходит элемент ИЛИ 26 открывает . элемент И 27, при этом код начала группы с регистра 28 поступает на установочный вход 1б счетчика . Одновременно с выхода элемента ИЛИ 2б сигнал проходит через элемент ИЛИ 6 на управляющий 17 вход счетчика А. Код с регистра 28 записывается в счетчик , При поступлений на разрешающий вход В устройства сигнала Разрешение опроса триггер 2 устанавливается в единичное состояние и открывает элемент И 3. Сигналы с тактового входа 9 устройства проходят через элемент И 3 на счетный

049911 4

вход 15 счетчика . Счетчик начинает счет с установленного в него кода начала группы. Код с выхода счетчика поступает на выход И

5 прерывания устройства; через дешифра тор 5 на опросный вход 12 блока 1 приоритета (наличие Запроса на запросном 11 соответствует появлению сигнала на разрешающем выхо10 де 13 устройства который поступает на гасящий вход 10 триггера 2 и устанавливает его в нулевое состояние, прекращая тем самым дальнейший просмотр запросов, после удовлет15 ворения запроса на обслуживание источник снимает сигнал Запрос, что соответствует снятию его на разрешающем выходе 13 устройства, гасящем вЯоде 10 триггера 2 и уста20 новлению триггера 2 в единичное состояние на вход схемы сравнения 30 п-го компаратора 7, которая срав нивает текущее значение счетчика с кодом конца группы на регистре

25 29 (при совпадении кодов с вы(oдa 25 п-го компаратора выдается сигнал запуска на вход 21 (п+1)-го компаратрра; по этому сигналу с входа И О (п+1) -го компаратора 7 в счетчик Ц запи2Q :сывается новое значение кода начала груп1пы орегистра 28 (п+1)-го компаратора, после чего сигнал с входа 21 снимается, и счетчик 4 производит опрос (п+1)-й группы запросов.

В известном устройстве уменьшается время ожидания опроса групп запросов, за счет опроса только требуемых запросов и возможности произвольного размещения последовательности групп запросов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обслуживания запросов | 1978 |

|

SU728128A1 |

| Устройство переменного приоритета | 1976 |

|

SU590742A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ЗАПРОСНЫХ СИГНАЛОВ | 2014 |

|

RU2550083C1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1982 |

|

SU1072047A1 |

| Устройство переменного приоритета | 1976 |

|

SU942021A1 |

| Многоканальное устройство для обслуживания запросов | 1985 |

|

SU1290326A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Многоканальное устройство для обслуживания запросов | 1985 |

|

SU1322283A1 |

| Многоканальное устройство приоритета | 1989 |

|

SU1661765A1 |

| Устройство для обслуживания запросов | 1980 |

|

SU955065A1 |

УСТРОЙСТВО ДЛЯ ГРУППОВОГО ОБСЛУЖИВАНИЯ ЗАПРОСОВ, содержащее блок приоритета, кодовый вход и выход которого являются соответственно запросным входом и разрешающим выходом устройства, триггер, выход . которого и тактовый вход устройства соединены соответственно с первым и вторым входами элемента..И, выход которого соединен со счетным входом счетчика, дешифратор, выход которого соединен с опросным входом блока приоритета, причемвыход блока приоритета соединен с гасящим входом триггера, установочный вход которого является разрешающим входом устройства, а выход счетчика соединен с входом дешифратора vi с выходом прерывания устройства,элемент ИЛИ, отличающееся тем, что, с целью повышения быстродействия, в него введены N компараторов (N количество запросов), каждый из которых содержит два регистра, схему сравнения, элемент И и элемент ИЛИ, первый вход которого соединен с входом запуска устройства, выход элемента ИЛИ - с первым входом элемента И и с соответствующим входом элемента ИЛИ устройства, установочные входы устройства подключены к входам соответствующих регистров, выход о 9 первого регистра соединен с вторым входом элемента И, выход которого л с соединен с установочным входом счетчика, а выход второго регистра соединен с первым входом схемы сравнения, второй вход которой соединен с выходом счетчика, а выход схемы сравнения соединен с вторым входом элемента ИЛИ последующего компара тора, выход схемы сравнения послед него компаратора соединен с вторым входом элемента ИЛИ первого компасо ратора, выход элемента ИЛИ устройства соединенС управляющим входом счетчика.

Авторы

Даты

1983-10-23—Публикация

1982-05-04—Подача