Устройство для декодирования запросных сигналов относится ко вторичной радиолокации и может использоваться для радиолокационных систем с активным ответом в системах управления воздушным движением.

Известен способ защиты от внутрисистемных помех в радиолокационных системах с активным ответом [1], при котором для исключения отметок ложных целей периодически меняют величину интервалов между импульсами ответных сигналов.

Известен способ обнаружения импульсного радиосигнала на фоне мешающего радиоимпульса и белого шума [2], при котором формируют дополнительный канал обнаружения, в котором осуществляют оценку постоянной составляющей времени задержки между информационным и мешающим сигналами.

Известен ранговый адаптивный последовательный обнаружитель сигналов [3], который, как и предполагаемое устройство, содержит аналого-цифровой преобразователь и устройство обнаружения.

Существенным недостатком каждого из этих устройств является выполнение специфических задач, которые не отвечают требованиям радиолокационного ответчика. Все они имеют одноканальные дешифраторы запросных сигналов.

Наиболее близким к описываемому изобретению (прототип) является устройство для декодирования запросных сигналов, которое содержит последовательно соединенные аналого-цифровой преобразователь, блок обнаружения импульсов, блок распределения импульсов, дешифратор, который имеет многоканальную структуру и блок сравнения амплитуд сигналов [4].

Недостатком известного радиолокационного ответчика является то, что в пороговых устройствах обнаружения импульсов, запускаемых при превышении амплитудой входного сигнала некоторого порога, смыкание импульса помехи с импульсом запросного сигнала вызывает более раннее срабатывание порогового устройства, вызывающее неправильное определение амплитуды и временного положения импульса запросного сигнала.

Задачей изобретения является повышение вероятности декодирования запросного сигнала в условиях сложной помеховой обстановки.

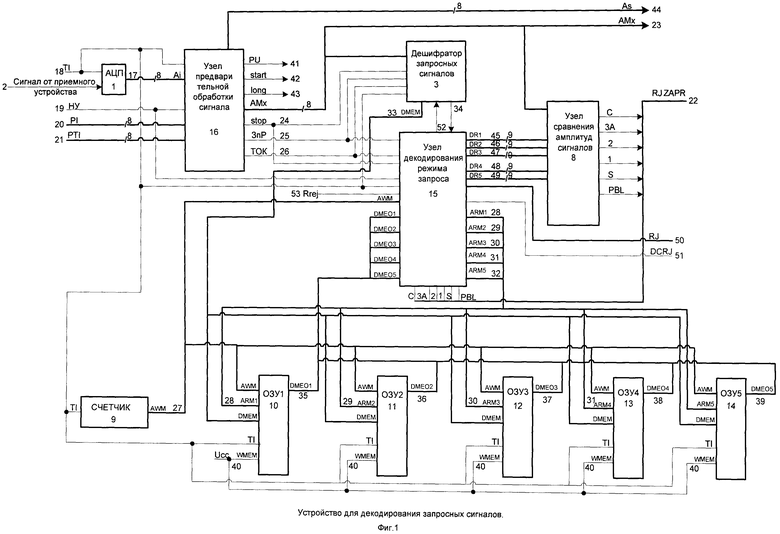

Сущность заявляемого изобретения, возможность его осуществления и промышленного использования поясняются чертежами, представленными на фиг.1-9а, где:

- на фиг.1 представлено устройство для декодирования запросных сигналов;

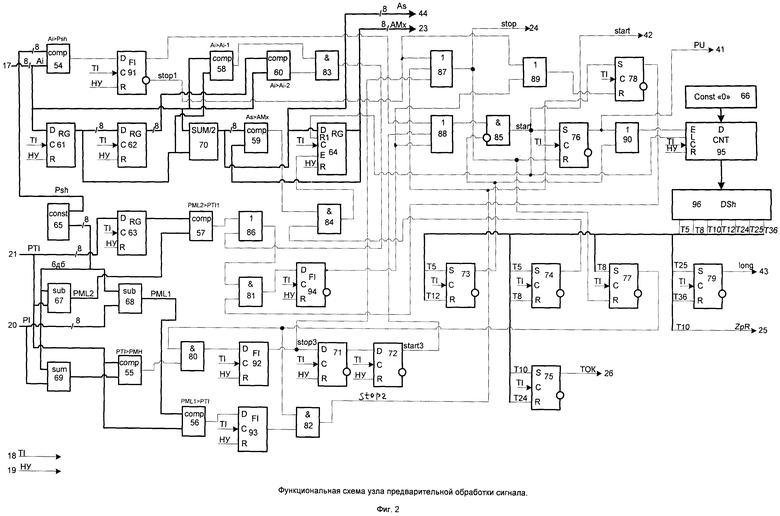

- на фиг.2 представлена функциональная схема узла предварительной обработки сигнала;

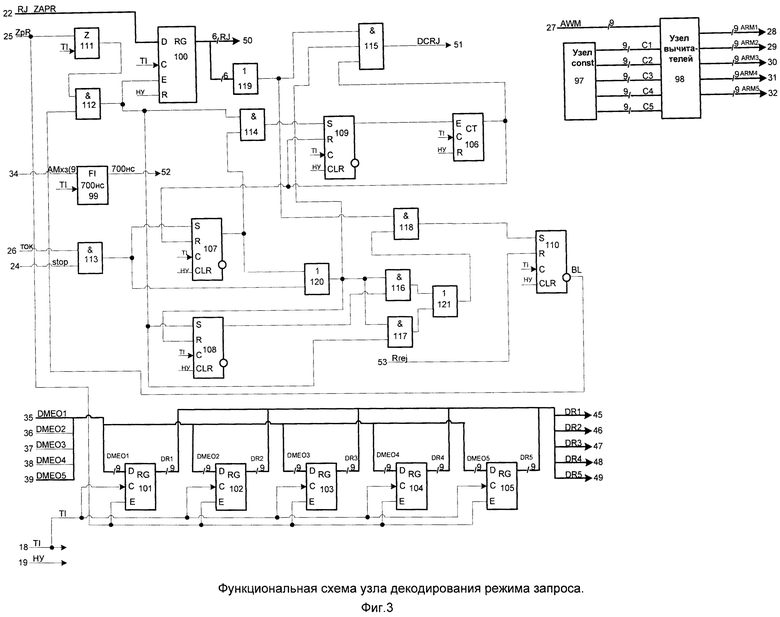

- на фиг.3 представлена функциональная схема узла декодирования режима запроса;

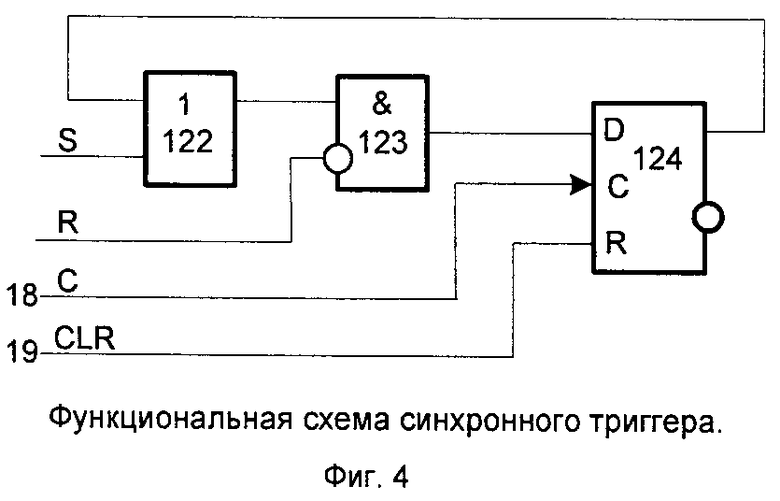

- на фиг.4 представлена функциональная схема синхронного триггера;

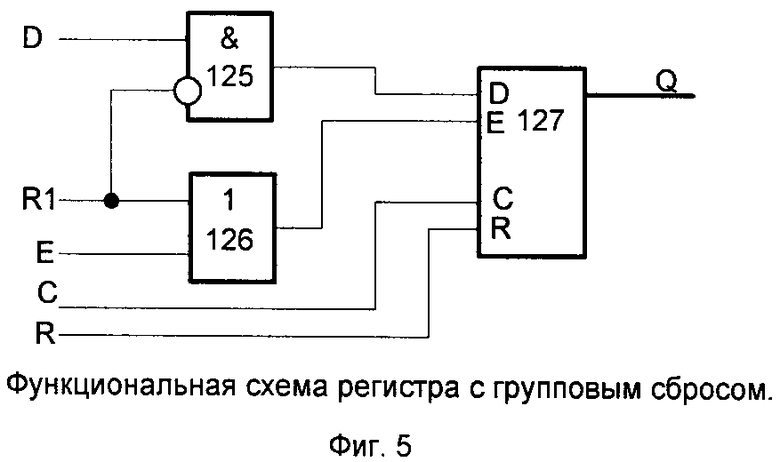

- на фиг.5 представлена функциональная схема регистра с групповым сбросом;

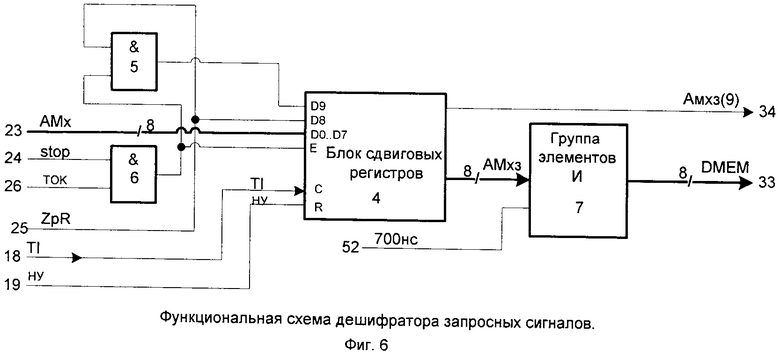

- на фиг.6 представлена функциональная схема дешифратора запросных сигналов;

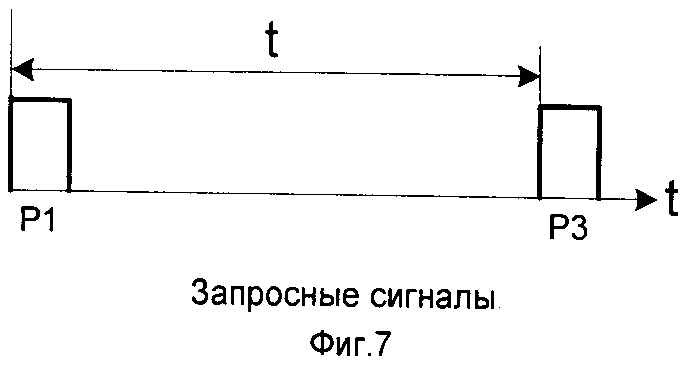

- на фиг.7 представлен запросный сигнал;

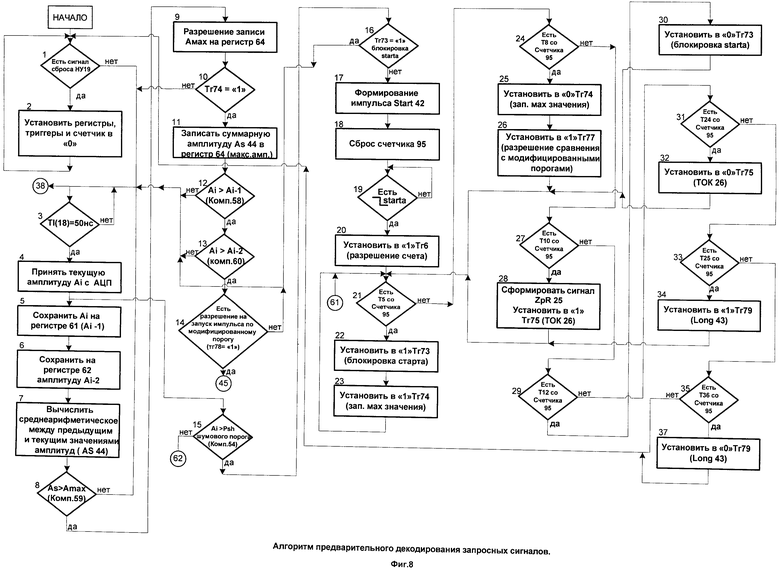

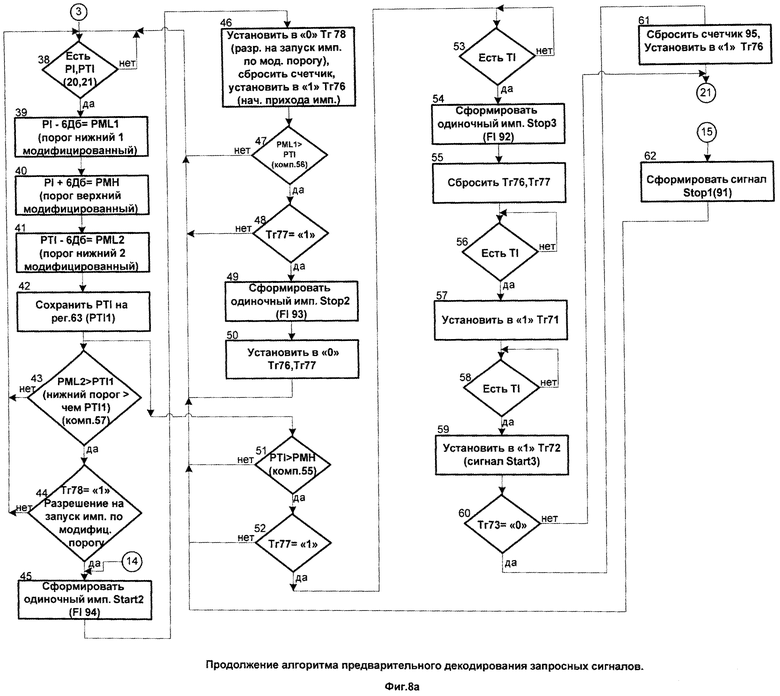

- на фиг.8, 8а представлен алгоритм предварительного декодирования запросных сигналов;

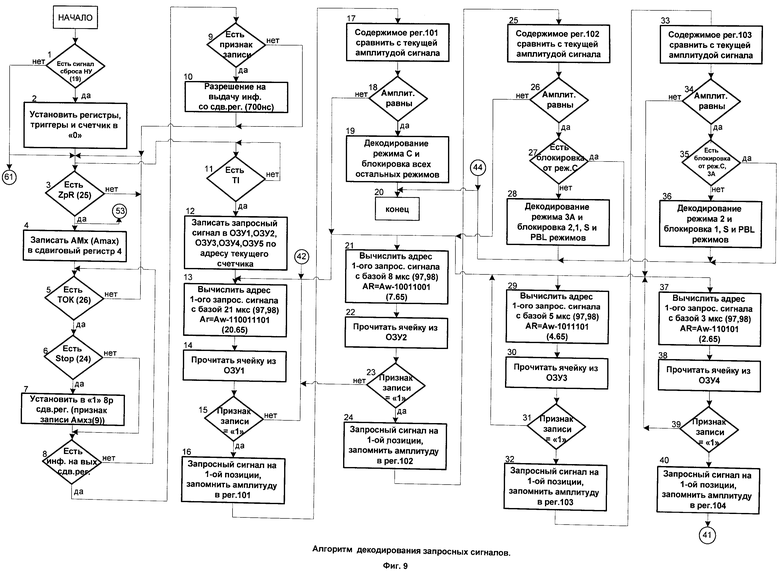

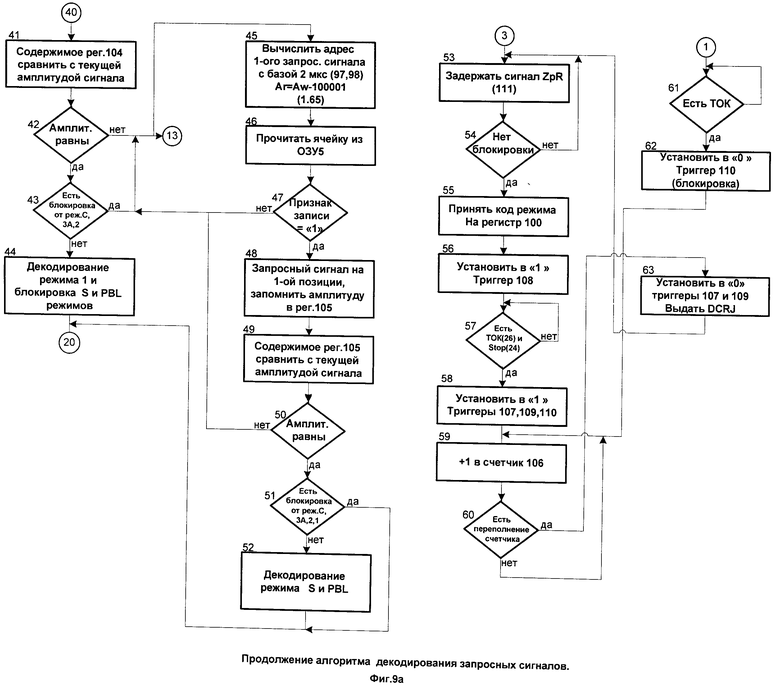

- на фиг.9, 9а представлен алгоритм декодирования запросных сигналов.

Указанные преимущества заявляемого устройства перед прототипом достигаются за счет того, что в устройство для декодирования запросных сигналов, содержащее АЦП 1, соединенное с внешним входом 2 от приемного устройства, дешифратор запросных сигналов 3, содержащий блок сдвиговых регистров 4, первый 5 элемент И, второй 6 элемент И и группу 7 элементов И, узел сравнения амплитуд сигналов 8, дополнительно введены счетчик 9, первое 10, второе 11, третье 12, четвертое 13 и пятое 14 ОЗУ, узел декодирования режима запроса 15 и узел предварительной обработки сигнала 16, первая 17 группа входов которого соединена с группой выходов АЦП 1, тактовый вход которого соединен с тактовыми входами узла предварительной обработки сигнала 16, счетчика 9, первого 10, второго 11, третьего 12, четвертого 13 и пятого 14 ОЗУ, дешифратора запросных сигналов 3, узла декодирования режима запроса 15 и является тактовым входом 18 устройства для декодирования запросных сигналов, первый 19 вход которого соединен с первыми входами узла декодирования режима запроса 15 и узла предварительной обработки сигнала 16, вторая и третья группы входов которого соединены с первой 20 и второй 21 группами входов устройства для декодирования запросных сигналов, первая 22 группа выходов которого соединена с первой группой входов узла декодирования режима запроса 15 и является первым, вторым, третьим, четвертым, пятым и шестым выходами узла сравнения амплитуд сигналов 8, первая группа входов которого соединена с первой группой входов дешифратора запросных сигналов 3, со второй 23 группой выходов устройства для декодирования запросных сигналов и группой выходов узла предварительной обработки сигнала 16, первый 24, второй 25 и третий 26 выходы которого соединены с первым входом дешифратора запросных сигналов 3 и со вторым входом узла декодирования режима запроса 15, со вторым входом дешифратора запросных сигналов 3 и третьим входом узла декодирования режима запроса 15, с третьим входом дешифратора запросных сигналов 3 и четвертым входом узла декодирования режима запроса 15 соответственно, вторая группа входов которого соединена с первыми группами входов первого 10, второго 11, третьего 12, четвертого 13 и пятого 14 ОЗУ и группой выходов 27 счетчика 9, причем первая 28, вторая 29, третья 30, четвертая 31 и пятая 32 группы выходов узла декодирования режима запроса 15 соединены со вторыми группами входов первого 10, второго 11, третьего 12, четвертого 13 и пятого 14 ОЗУ, третьи группы входов которых соединены с первой 33 группой выходов дешифратора запросных сигналов 3, первый 34 выход которого соединен с пятым входом узла декодирования режима запроса 15, третья, четвертая, пятая, шестая и седьмая группы входов которого соединены с группами выходов 35, 36, 37, 38, 39 первого 10, второго 11, третьего 12, четвертого 13 и пятого 14 ОЗУ, входы 40 которых соединены между собой и с UCC (питание), причем четвертый, пятый, шестой выходы и вторая группа выходов узла предварительной обработки сигнала 16 соединены с первым 41, вторым 42, третьим 43 выходами и третьей 44 группой выходов устройства для декодирования запросных сигналов соответственно, причем вторая, третья, четвертая, пятая и шестая группы входов узла сравнения амплитуд сигналов 8 соединены с шестой 45, седьмой 46, восьмой 47, девятой 48 и десятой 49 группами выходов узла декодирования режима запроса 15, одиннадцатая группа выходов которого соединена с четвертой 50 группой выходов устройства для декодирования запросных сигналов, четвертый 51 выход которого соединен с первым выходом узла декодирования режима запроса 15, второй 52 выход которого соединен с четвертым входом дешифратора запросных сигналов 3, причем второй 53 вход устройства для декодирования запросных сигналов соединен с шестым входом узла декодирования режима запроса 15.

Узел предварительной обработки сигнала 16 содержит первый 54 компаратор, второй 55 компаратор, третий 56 компаратор, четвертый 57 компаратор, пятый 58 компаратор, шестой 59 компаратор и седьмой 60 компаратор, первый 61 регистр, второй 62 регистр, третий 63 регистр и четвертый 64 регистр с групповым сбросом, первый блок 65 констант, вторую 66 константу, первый 67 вычитатель, второй 68 вычитатель, первый 69 сумматор, второй 70 сумматор, первый 71 триггер, второй 72 триггер, третий 73 синхронный триггер, четвертый 74 синхронный триггер, пятый 75 синхронный триггер, шестой 76 синхронный триггер, седьмой 77 синхронный триггер, восьмой 78 синхронный триггер, девятый 79 синхронный триггер, первый 80 элемент И, второй 81 элемент И, третий 82 элемент И, четвертый 83 элемент И, пятый элемент 84 И, шестой 85 элемент И, первый 86 элемент ИЛИ, второй 87 элемент ИЛИ, третий 88 элемент ИЛИ, четвертый 89 элемент ИЛИ, пятый 90 элемент ИЛИ, первый 91 формирователь импульса, второй 92 формирователь импульса, третий 93 формирователь импульса, четвертый 94 формирователь импульса, счетчик 95, дешифратор 96, первый выход которого соединен с установочными входами третьего 73 и четвертого 74 синхронных триггеров, выход четвертого 74 синхронного триггера соединен с первым входом пятого 84 элемента И, выход которого соединен с разрешающим входом четвертого 64 регистра с групповым сбросом, группа выходов которого соединена с первой группой входов шестого 59 компаратора и является первой 23 группой выходов узла предварительной обработки сигнала 16, первый 24 выход которого соединен с синхронными сбросами шестого 76 и седьмого 77 синхронных триггеров и выходом второго 87 элемента ИЛИ, первый вход которого соединен с первым входом четвертого 89 элемента ИЛИ и инверсным выходом первого 91 формирователя импульса, прямой выход которого соединен с первым входом третьего 88 элемента ИЛИ, выход которого соединен с первым входом шестого 85 элемента И, выход которого соединен с пятым 42 выходом узла предварительной обработки сигнала 16, с первым входом счетчика 95 и с установочным входом шестого 76 синхронного триггера, выход которого соединен с первым входом пятого 90 элемента ИЛИ и является четвертым 41 выходом узла предварительной обработки сигнала 16, второй 25 выход которого соединен со вторым выходом дешифратора 96 и с установочным входом пятого 75 синхронного триггера, выход которого является третьим 26 выходом узла предварительной обработки сигнала 16, шестой 43 выход которого соединен с выходом девятого 79 синхронного триггера, установочный вход которого соединен с третьим выходом дешифратора 96, четвертый выход которого соединен с синхронным сбросом четвертого 74 синхронного триггера и установочным входом седьмого 77 синхронного триггера, выход которого соединен с первыми входами первого 80 и третьего 82 элементов И, выход третьего 82 элемента И соединен со вторым входом второго 87 элемента ИЛИ и с установочным входом восьмого 78 синхронного триггера, выход которого соединен с первым входом второго 81 элемента И, выход которого соединен с информационным входом четвертого 94 формирователя импульса, выход которого соединен со вторыми входами третьего 88 и четвертого 89 элементов ИЛИ, выход четвертого 89 элемента ИЛИ соединен с синхронным сбросом восьмого 78 синхронного триггера, причем тактовый вход 18 устройства для декодирования запросных сигналов соединен с тактовыми входами первого 61, второго 62, третьего 63 и четвертого с групповым сбросом 64 регистров, первого 91, второго 92, третьего 93 и четвертого 94 формирователей импульса, первого 71, второго 72, третьего 73, четвертого 74, пятого 75, шестого 76, седьмого 77, восьмого 78 и девятого 79 синхронных триггеров и счетчика 95, сбросовый вход которого соединен со сбросовыми входами первого 61, второго 62, третьего 63 и четвертого 64 регистров, первого 91, второго 92, третьего 93 и четвертого 94 формирователей импульса, первого 71 и второго 72 триггеров и является первым 19 входом устройства для декодирования запросных сигналов, первая 17 группа входов которого соединена с информационными входами первого 61 регистра, с первыми группами входов первого 54, пятого 58 и седьмого 60 компараторов и второго 70 сумматора, группа выходов которого является второй 44 группой выходов узла предварительной обработки сигнала 16 и соединена с информационной группой входов четвертого с групповым сбросом 64 регистра и второй группой входов шестого 59 компаратора, выход которого соединен со вторым входом пятого 84 элемента И, причем первая группа выходов первого 65 блока констант соединена со второй группой входов первого 54 компаратора, выход которого соединен с информационным входом первого 91 формирователя импульса, причем группа выходов первого 61 регистра соединена с информационной группой входов второго 62 регистра и со вторыми группами входов второго 70 сумматора и пятого 58 компаратора, выход которого соединен с первым входом четвертого 83 элемента И, выход которого соединен с первым входом первого 86 элемента ИЛИ, выход которого соединен со вторым входом второго 81 элемента И, вторая группа выходов первого 65 блока констант соединена с первыми группами входов первого 67 и второго 68 вычитателей и первого 69 сумматора, группа выходов которого соединена с первой группой входов второго 55 компаратора, выход которого соединен со вторым входом первого 80 элемента И, выход которого соединен с информационным входом второго 92 формирователя импульса, выход которого соединен с третьим входом второго 87 элемента ИЛИ и с информационным входом первого 71 триггера, выход которого соединен с информационным входом второго 72 триггера, выход которого соединен с третьим входом третьего 88 элемента ИЛИ, вторая 20 группа входов устройства для декодирования запросных сигналов соединена со вторыми группами входов первого 69 сумматора и второго 68 вычитателя, группа выходов которого соединена с первой группой входов третьего 56 компаратора, выход которого соединен с информационным входом третьего 93 формирователя импульса, выход которого соединен со вторым входом третьего 82 элемента И, третья 21 группа входов устройства для декодирования запросных сигналов соединена со вторыми группами входов второго 55 и третьего 56 компараторов, с информационной группой входов третьего 63 регистра и второй группой входов первого 67 вычитателя, группа выходов которого соединена с первой группой входов четвертого 57 компаратора, выход которого соединен со вторым входом первого 86 элемента ИЛИ, причем группа выходов второго 62 регистра соединена со второй группой входов седьмого 60 компаратора, выход которого соединен со вторым входом четвертого 83 элемента И, причем пятый выход дешифратора 96 соединен с синхронным сбросом третьего 73 синхронного триггера, выход которого соединен с инверсным входом шестого 85 элемента И и со вторым входом пятого 90 элемента ИЛИ, выход которого соединен с разрешающим входом счетчика 95, группа выходов которого соединена с группой входов дешифратора 96, шестой и седьмой выходы которого соединены с синхронными сбросами пятого 75 и девятого 79 синхронных триггеров, причем группа выходов второй 66 константы соединена с информационной группой входов счетчика 95, группа выходов третьего 63 регистра соединена со второй группой входов четвертого 57 компаратора, причем выход шестого элемента И 85 соединен с первым сбросовым входом четвертого регистра с групповым сбросом 64.

Узел декодирования режима запроса 15 содержит узел констант 97, узел вычитателей 98, формирователь импульса 99, первый 100 регистр, второй 101 регистр, третий 102 регистр, четвертый 103 регистр, пятый 104 регистр и шестой 105 регистр, счетчик 106, первый 107 синхронный триггер, второй 108 синхронный триггер, третий 109 синхронный триггер и четвертый 110 синхронный триггер, элемент задержки 111, первый 112 элемент И, второй 113 элемент И, третий 114 элемент И, четвертый 115 элемент И, пятый 116 элемент И, шестой 117 элемент И и седьмой 118 элемент И, первый 119 элемент ИЛИ, второй 120 элемент ИЛИ и третий 121 элемент ИЛИ, выход которого соединен с первым входом седьмого 118 элемента И, выход которого соединен с установочным входом четвертого 110 синхронного триггера, инверсный выход которого соединен с первым входом первого 112 элемента И, выход которого соединен с разрешающим входом первого 100 регистра, с первыми входами третьего 114 и шестого 117 элементов И и с установочным входом второго 108 синхронного триггера, выход которого соединен с первым входом пятого 116 элемента И, выход которого соединен с первым входом третьего 121 элемента ИЛИ, второй вход седьмого 118 элемента И соединен с первым входом четвертого 115 элемента И и выходом первого 119 элемента ИЛИ, группа входов которого соединена с группой выходов первого 100 регистра и является одиннадцатой 50 группой выходов узла декодирования режима запроса 15, первая 28, вторая 29, третья 30, четвертая 31 и пятая 32 группы выходов которого соединены с первой, второй, третьей, четвертой и пятой группами выходов узла вычитателей 98, первая группа входов которого является второй 27 группой входов узла декодирования режима запроса 15, шестая 45, седьмая 46, восьмая 47, девятая 48 и десятая 49 группы выходов которого соединены с группами выходов второго 101, третьего 102, четвертого 103, пятого 104 и шестого 105 регистров, информационные группы входов которых являются третьей 35, четвертой 36, пятой 37, шестой 38 и седьмой 39 группами входов узла декодирования режима запроса 15 соответственно, первый 51 выход которого соединен с выходом четвертого 115 элемента И, второй вход которого соединен со вторыми входами пятого 116 и шестого 117 элементов И, с синхронным сбросом второго 108 синхронного триггера и с выходом второго 120 элемента ИЛИ, первый вход которого соединен со вторым входом третьего 114 элемента И, с выходом первого 107 синхронного триггера, установочный вход которого соединен со вторым входом второго 120 элемента ИЛИ и с выходом второго 113 элемента И, первый вход которого является четвертым 26 входом узла декодирования режима запроса 15, второй 52 выход которого соединен с выходом формирователя импульса 99, вход которого является пятым 34 входом узла декодирования режима запроса 15, первая 22 группа входов которого соединена с информационной группой входов первого 100 регистра, тактовый вход которого соединен с тактовыми входами элемента задержки 111, формирователя импульса 99, первого 107, второго 108, третьего 109 и четвертого 110 синхронных триггеров, второго 101, третьего 102, четвертого 103, пятого 104 и шестого 105 регистров, счетчика 106 и является тактовым входом 18 узла декодирования режима запроса 15, первый 19 вход которого соединен со сбросовыми входами регистра 100, первого 107, второго 108, третьего 109 и четвертого 110 синхронных триггеров и счетчика 106, выход которого соединен с третьим входом четвертого 115 элемента И и с синхронными сбросами первого 107 и третьего 109 синхронных триггеров, выход третьего 109 синхронного триггера соединен с разрешающим входом счетчика 106, причем третий 25 вход узла декодирования режима запроса 15 соединен с разрешающими входами второго 101, третьего 102, четвертого 103, пятого 104 и шестого 105 регистров и с входом элемента задержки 111, выход которой соединен со вторым входом первого 112 элемента И, второй 24 вход узла декодирования режима запроса 15 соединен со вторым входом второго 113 элемента И, выход третьего 114 элемента И соединен с установочным входом третьего 109 синхронного триггера, шестой 53 вход узла декодирования режима запроса 15 соединен с синхронным сбросом четвертого 110 синхронного триггера, причем выход шестого 117 элемента И соединен со вторым входом четвертого 121 элемента ИЛИ, первая, вторая, третья, четвертая и пятая группы выходов узла констант 97 соединены со второй, третий, четвертой, пятой и шестой группами входов узла вычитателей 98.

Синхронный триггер содержит элемент ИЛИ 122, элемент И 123 и триггер 124, выход которого соединен с первым входом элемента ИЛИ 122, выход которого соединен с прямым входом элемента И 123, выход которого соединен с информационным входом триггера 124, тактовый вход которого соединен с тактовым входом 18 синхронного триггера, установочный вход которого соединен со вторым входом элемента ИЛИ 122, причем синхронный сброс синхронного триггера соединен с инверсным входом элемента И 123, сбросовый вход 19 синхронного триггера соединен со сбросовым входом триггера 124.

Регистр с групповым сбросом содержит элемент И 125, элемент ИЛИ 126 и регистр 127, группа выходов которого является группой выходов регистра с групповым сбросом 64, информационный вход которого соединен с прямым входом элемента И 125, выход которого соединен с информационным входом регистра 127, разрешающий вход которого соединен с выходом элемента ИЛИ 126, первый вход которого соединен с инверсным входом элемента И 125 и является первым сбросовым входом регистра с групповым сбросом 64, разрешающий вход которого соединен со вторым входом элемента ИЛИ 126, причем тактовый и сбросовый входы регистра с групповым сбросом 64 соединены с тактовым и сбросовым входами регистра 127.

Устройство для декодирования запросных сигналов работает следующим образом.

Запросные сигналы системы опознования NATO типа Мк-ХА и международной системы вторичной радиолокации для управления воздушным движением (АТС RBS) представляют собой двухимпульсный код, который представлен на фиг.7. Код запроса определяется интервалом времени между передними фронтами импульсов Р1 и Р3.

Аналогичная двухимпульсная структура запросных кодов принята и в отечественной системе радиолокации для УВД (ГОСТ 21800-89).

И в международной и отечественной системах вторичной радиолокации дешифрация запроса осуществляется, в том числе при условии, что амплитуда импульса Р3 отличается от амплитуды импульса Р1 не более чем на (+3,-1) Р. Следовательно, для достоверного обнаружения сигнала запроса необходимо запоминать амплитуду импульса Р1 для последующего сравнения с ней амплитуды импульса Р3. В условиях воздействия импульсных помех каждый импульс, поступивший на вход устройства для декодирования запросных сигналов, как первый импульс (Р1) запросного сигнала. Так как максимальный интервал между импульсами 21 мкс, соответствующий запросу режима С международной системы АТС RBS, то запоминающее устройство должно хранить информацию об амплитуде импульса в течение этого времени, поэтому объем ОЗУ составляет 512 девяти разрядных слов, что соответствует 25 мкс.

Устройство для декодирования запросных сигналов (УДЗС) предназначено для выделения принимаемого сигнала с запросчика из совокупности помех с высокой достоверностью в любой момент времени.

Структурная схема УДЗС представлена на фиг.1.

Устройство для декодирования запросных сигналов состоит из:

аналогоцифрового преобразователя АЦП 1, соединенного с внешним входом 2 от приемного устройства,

дешифратора запросных сигналов 3,

узла сравнения амплитуд сигналов 8,

счетчика 9,

первого 10, второго 11, третьего 12, четвертого 13 и пятого 14 ОЗУ,

узла декодирования режима запроса 15,

узла предварительной обработки сигнала 16.

Алгоритм предварительного декодирования запросных сигналов представлен на фиг.8 и фиг.8а.

Алгоритм декодирования запросных сигналов представлен на фиг.9 и фиг.9а.

АЦП 1 предназначен для преобразования аналогового сигнала в 8-разрядный цифровой код. Дешифратор запросных сигналов 3 предназначен для декодирования сигнала заданной длительности. Узел сравнения амплитуд сигналов 8 предназначен для амплитудной селекции. Узел предварительной обработки сигнала 16 предназначен для выделения сигнала на фоне шумов и определения мощности сигнала. Узел декодирования режима запроса 15 предназначен для распознавания запросных сигналов. ОЗУ 10, 11, 12, 13 и 14 предназначены для хранения запросных сигналов. Счетчик 9 предназначен для формирования адреса ячеек ОЗУ.

Функциональная схема узла предварительной обработки сигнала 16 представлена на фиг.1.

Принятые антенной (не показанной на фиг.1) сигналы с выхода приемного устройства поступают на вход от приемного устройства 2 АЦП 1 далее на узел предварительной обработки сигнала 16 на компараторы 54,58, 60, регистр 61 и сумматор 70. На регистре 61 хранится амплитуда (Ai-1), на регистре 62 хранится амплитуда (Ai-2), затем вычисляется на сумматоре 70 среднеарифметическое значение As 44 между предыдущим и текущим значениями амплитуд для уменьшения шума.

Если входной сигнал превышает уровень шумового порога, то компаратор 54 и формирователь 91 генерируют сигнал, поступающий на элемент ИЛИ 88 и если нет сигнала блокировки starta, т.е.триггер 73 равен «0», формирует на элементе И 85 сигнал start 42, по которому выполняется сброс счетчика 95 и регистра максимальной амплитуды 64, а по заднему фронту сигнала start устанавливает триггер 76 в «1», разрешая счет счетчику 95 и формируя сигнал PU 41. По сигналу Т5 с дешифратора 96 устанавливаются в «1» триггера 73 и 74, блокируя start и разрешая запись максимальной амплитуды на регистр 64, если суммарная амплитуда больше предыдущей максимальной амплитуды (компаратор 59). Максимальное значение амплитуды определяется с 5 по 9 отсчеты.

При калибровке в ответчике составляется таблица зависимости мощности сигнала от амплитуды, которая хранится в ОЗУ ответчика. По входной амплитуде из ОЗУ выбирается мощность сигнала и поступает на вход PTI, на вход PI поступает максимальная мощность сигнала.

Для более точного определения длительности импульса необходимо сформировать новые пороги из максимальной амплитуды. Экспериментально определено, что оптимальными порогами являются максимальная амплитуда с Δ=±6дб. На вычитателях 67 и 68 вычисляются нижние пороги для PTI (PML2) и PI (PML1), на сумматоре 69 вычисляется верхний порог для PI (РМН).

По сигналу Т8 с дешифратора 96 устанавливается в «1» триггер 77, а триггер 74 устанавливается в «0», запрещая прием максимальной амплитуды на регистр 64. Если PML1>PTI, то срабатывает компаратор 56 и формирователь 93 вырабатывает импульс, который через элемент И 82 устанавливает в «1» триггер 78, а через элемент ИЛИ 87 формирует сигнал stop. Если PML2 > содержимого регистра 63 (PTI1), то срабатывает компаратор 57 и через элементы ИЛИ 86 и И 81 запускает формирователь 94, сбрасывая триггер 78 в «0» и вырабатывая импульс start (ИЛИ 88 и И 85).

Если PTI > РМН, то срабатывает компаратор 55 и через элемент И 80 запускает формирователь 92, импульс с которого устанавливает в «1» триггер 71 и формирует сигнал stop 3, который через элемент ИЛИ 87 поступает на выход 24 узла предварительной обработки сигнала 16. На следующим такте устанавливается в «1» триггер 72, формируя сигнал start3.

Если текущая амплитуда Ai > амплитуд на регистрах 61 и 62, то сигналы с компараторов 58 и 60, совпадая на элементе И83, устанавливают разрешение на формирование импульса start2.

По сигналу Т10 с дешифратора 96 устанавливается в «1» триггер 75 ТОК (интервал времени длительности импульса, который удовтворяет требования (0.5-1.2 мкс)) и формируется сигнал записи в сдвиговый регистр - ZpR 25.

По сигналу Т12 с дешифратора 96 устанавливается в «0» триггер 73.

По сигналу Т24 с дешифратора 96 устанавливается в «0» триггер 75.

По сигналу Т25 с дешифратора 96 устанавливается в «1» триггер 79.

По сигналу Т36 с дешифратора 96 устанавливается в «0» триггер 79.

Время занятости каждого канала не более 21 мкс с момента поступления на его вход первого импульса. Амплитуда, поступившего с узла предварительной обработки сигнала 16, запоминается и хранится в ОЗУ в течение времени цикла работы узла декодирования режима запроса 15. Декодируется пять режимов запроса, поэтому используются 5 ОЗУ с организацией 512×9. Запись производится постоянно и во все ОЗУ одновременно. Пока нет амплитуды с выхода сдвигового регистра в ОЗУ пишутся все нули, адрес для записи определяется состоянием счетчика 9.

Функциональная схема дешифратора запросных сигналов представлена на фиг.6.

Функциональная схема узла декодирования режима запроса представлена на фиг.3.

Если поступает сигнал ZpR 25, то максимальная амплитуда заносится в блок сдвиговых регистров 4, а в D8 заносится признак записи, если в интервал времени ТОК (триггер 75 находится в «1») 26 поступает окончание сигнала (stop 24), то на элементе И 6 формируется сигнал, разрешающий сдвиг блоку сдвиговых регистров 4 и если он совпадает с синалом ZpR 25, то в D9 заносится «1». Когда на выходе блока сдвиговых регистров 4 появится сигнал Амхз(9) 34, по которому в узле декодирования режима запроса 15 на формирователе 99 вырабатывается сигнал 700 нс, разрешающий выдачу информации с блока сдвиговых регистров 4. Таким образом запросный сигнал запишется в ОЗУ1, ОЗУ2, ОЗУЗ, ОЗУ4 и ОЗУ5 по текущему адресу счетчика 9.

Режим С вторичного радиолокатора (ВРЛ) применяется для автоматического сообщения о высоте.

Режимы 1, 2, 3 используются для идентификации цели. Режим 1 является постоянно используемым, так как это общий режим работы для идентификации любой цели. Обозначение режима 3/А используется с тех пор, как режим 3 IFF (свой- чужой) стал совместимым с режимом А ВРЛ.

Режим опроса будет определяться интервалом между двумя импульсами режима, обозначенными Р1 и Р3.

Интервал между импульсами Р1 и РЗ, соответствующий каждому режиму опроса, должен быть следующим:

Режим 1: 3,0±0,1/-0.05 мкс

Режим 2: 5,0±0,1 мкс

Режим 3/А: 8,0±0,1 мкс

Режим С: 21,0±0,1 мкс

Опросы, сделанные в Режимах 1, 2 и 3, и соответствующие ответы являются кодированными группами импульсов и имеют следующее возможное число кодов:

Режим 1 - 32 кода

Режим 2 - 4096 кодов

Режим 3 - 4096 кодов

Режим S - обозначение международной организации гражданской авиации (IKAO), относящееся к следующему поколению системы УВД для всемирного использования. Это - селективная адресная система, которая обеспечивает наземные сетевые станции и дает возможность объединения данных.

Режим ограничивает использование канала при обеспечении повышенной пропускной способности системы УВД и разработан для эффективной поддержки планируемого роста требований УВД.

Импульс ПБЛ (2 мкс) используется для декодирования запроса, полученного от бокового лепестка диаграммы направленности антенны. Также расстановка импульсов 2 мкс используется в качестве преамбулы запроса S-режима. При этом в течение 30 мкс блокируется декодирование запросов 1, 2, 3 / А, С режимов.

Далее узел вычитателей 98 вычисляет адрес первого запросного сигнала с базой 21 мкс (Ar(адрес чтения)=Aw(адрес записи) - 110011101), по данному адресу из ОЗУ1 считывается амплитуда запросного сигнала и если признак записи = «1», то амплитуда запоминается на регистре 101 DR1 45. Сигнал DR1 45 из блока декодирования режима запроса 15 поступает на узел сравнения амплитуд сигналов 8, где выполняется сравнение с текущей амплитудой сигнала. Если содержимое регистра 101 равно текущей амплитуде сигнала, то декодируется режим С и блокируются все остальные режимы.

Одновременно узел вычитателей 98 вычисляет адрес первого запросного сигнала с базой 8 мкс (Ar=Aw-10011001), с базой 5 мкс (Ar=Aw-1011101), с базой 3 мкс (Ar=Aw-110101), с базой 2 мкс (Ar=Aw-100001),по данному адресу из ОЗУ2, ОЗУ3, ОЗУ4 или ОЗУ5 соответственно считывается амплитуда запросного сигнала и если признак записи = «1», то амплитуда запоминается на регистре 102 DR2 46, 103 DR3 47, 104 DR4 48, 105 DR5 49. Сигналы DR2 46, DR3 47, DR4 48, DR5 49 из блока декодирования режима запроса 15 поступает на узел сравнения амплитуд сигналов 8, где выполняется сравнение с текущей амплитудой сигнала. Если содержимое регистра 102 равно текущей амплитуде сигнала, то декодируется режим 3А и блокируются режимы 2, 1, S и PBL. Если содержимое регистра 103 равно текущей амплитуде сигнала, то декодируется режим 2 и блокируются режимы 1,S и PBL. Если содержимое регистра 104 равно текущей амплитуде сигнала, то декодируется режим 1 и блокируются режимы S и PBL. Если содержимое регистра 105 равно текущей амплитуде сигнала, то декодируется режим S и PBL.

По задержанному сигналу ZpR и если нет блокировки код режима заносится в регистр 100 и выдается на группу выходов RJ 50. Одновременно устанавливается в «1» триггер 108. По сигналу stop 24, поступающему из узла предварительной обработки, при наличии временного интервала ТОК устанавливается в «1» триггер 107, а затем триггер 109, разрешающий работу счетчику 106, и затем триггер 110, блокирующий прием следующего режима на регистр 100.

По переполнению счетчика устанавливаются в «0» триггера 107 и 109 и формируется сигнал DCRJ.

Амплитуда, поступившего с дешифратора запросных сигналов, запоминается и хранится в ОЗУ в течение времени цикла работы узла декодирования режима запроса 15 21 мкс. Если амплитуда в кодовой комбинации не соответствует ни одному из значений амплитуд ранее поступивших импульсов, отличие должно быть не более чем на (+3, -1)Р, то декодирования не происходит. При наличии совпадения по времени, по амплитуде и длительности импульса декодированный запросный сигнал с выхода RJZAPR 22 узла сравнения амплитуд сигналов 8 поступает для дальнейшей обработки на схемы анализа радиолокационного ответчика.

Источники информации, принятые во внимание при экспертизе.

[1] Патент РФ 1290879, G01S 13/76, опубликован 20.10.1999 г.

[2] Патент РФ 2160905, G01S 7/292, опубликован 20.12.2000 г.

[3] Патент РФ 2100822, G01S 7/292, опубликован 27.10.1997 г.

[4] Патент RU №2206103 С2, G01S 13/78. Бюл. №16, 10.06.2003 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обслуживания запросов | 1987 |

|

SU1444768A1 |

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

| Устройство для сопряжения разнотипных вычислительных машин | 1984 |

|

SU1257651A1 |

| Устройство для обслуживания запросов | 1990 |

|

SU1777140A1 |

| Устройство для формирования сигнала прерывания | 1984 |

|

SU1241242A1 |

| Устройство для обслуживания сообщений | 1983 |

|

SU1128256A1 |

| Устройство для обмена информацией | 1979 |

|

SU826330A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2015 |

|

RU2589317C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ПЕРЕДАЧИ ПОСЛЕДОВАТЕЛЬНОСТИ СИГНАЛОВ | 2005 |

|

RU2299474C2 |

| Устройство формирования сигнала прерывания | 1985 |

|

SU1290327A1 |

Изобретение относится ко вторичной радиолокации и может использоваться для радиолокационных систем с активным ответом в системах управления воздушным движением. Техническим результатом является повышение вероятности декодирования запросного сигнала в условиях сложной помеховой обстановки. Устройство для декодирования запросных сигналов, содержащее АЦП, дешифратор запросных сигналов, содержащий блок сдвиговых регистров, первый элемент И, второй элемент И и группу элементов И, узел сравнения амплитуд сигналов, отличающееся тем, что, с целью повышения вероятности декодирования запросного сигнала в условиях сложной помеховой обстановки, в него дополнительно введены счетчик, первое, второе, третье, четвертое и пятое ОЗУ, узел декодирования режима запроса и узел предварительной обработки сигнала с соответствующими связями. Узел предварительной обработки сигнала содержит первый, второй, третий, четвертый, пятый, шестой и седьмой компараторы, первый, второй, третий и четвертый регистры, первый блок констант, вторую константу, первый и второй вычитатели, первый и второй сумматоры, первый и второй триггеры, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый синхронные триггеры, первый, второй, третий, четвертый, пятый и шестой элементы И, первый, второй, третий, четвертый и пятый элементы ИЛИ, первый, второй, третий и четвертый формирователи импульса, счетчик, дешифратор. Узел декодирования режима запроса содержит узел констант, узел вычитателей, формирователь импульса, первый, второй, третий, четвертый, пятый и шестой регистры, счетчик, первый, второй, третий и четвертый синхронные триггеры, элемент задержки, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И, первый, второй и третий элементы ИЛИ. 4 з.п. ф-лы, 11 ил.

1. Устройство для декодирования запросных сигналов, содержащее АЦП, соединенное с внешним входом от приемного устройства, дешифратор запросных сигналов, содержащий блок сдвиговых регистров, первый элемент И, второй элемент И и группу элементов И, узел сравнения амплитуд сигналов, отличающееся тем, что, с целью повышения вероятности декодирования запросного сигнала в условиях сложной помеховой обстановки, в него дополнительно введены счетчик, первое, второе, третье, четвертое и пятое ОЗУ, узел декодирования режима запроса и узел предварительной обработки сигнала, первая группа входов которого соединена с группой выходов АЦП, тактовый вход которого соединен с тактовыми входами узла предварительной обработки сигнала, счетчика, первого, второго, третьего, четвертого и пятого ОЗУ, дешифратора запросных сигналов, узла декодирования режима запроса и является тактовым входом устройства для декодирования запросных сигналов, первый вход которого соединен с первыми входами узла декодирования режима запроса и узла предварительной обработки сигнала, вторая и третья группы входов которого соединены с первой и второй группами входов устройства для декодирования запросных сигналов, первая группа выходов которого соединена с первой группой входов узла декодирования режима запроса и является первым, вторым, третьим, четвертым, пятым и шестым выходами узла сравнения амплитуд сигналов, первая группа входов которого соединена с первой группой входов дешифратора запросных сигналов, с первой группой выходов устройства для декодирования запросных сигналов и группой выходов узла предварительной обработки сигнала, первый, второй и третий выходы которого соединены с первым входом дешифратора запросных сигналов и со вторым входом узла декодирования режима запроса, со вторым входом дешифратора запросных сигналов и третьим входом узла декодирования режима запроса, с третьим входом дешифратора запросных сигналов и четвертым входом узла декодирования режима запроса соответственно, вторая группа входов которого соединена с первыми группами входов первого, второго, третьего, четвертого и пятого ОЗУ и группой выходов счетчика, причем первая, вторая, третья, четвертая и пятая группы выходов узла декодирования режима запроса соединены со вторыми группами входов первого, второго, третьего, четвертого и пятого ОЗУ, третьи группы входов которых соединены с первой группой выходов дешифратора запросных сигналов, первый выход которого соединен с пятым входом узла декодирования режима запроса, третья, четвертая, пятая, шестая и седьмая группы входов которого соединены с группами выходов первого, второго, третьего, четвертого и пятого ОЗУ, входы которых соединены между собой и с Ucc (питание), причем четвертый, пятый, шестой выходы и вторая группа выходов узла предварительной обработки сигнала соединены с первым, вторым, третьим выходами и третьей группой выходов устройства для декодирования запросных сигналов соответственно, причем вторая, третья, четвертая, пятая и шестая группы входов узла сравнения амплитуд сигналов соединены с шестой, седьмой, восьмой, девятой и десятой группами выходов узла декодирования режима запроса, одиннадцатая группа выходов которого соединена с четвертой группой выходов устройства для декодирования запросных сигналов, четвертый выход которого соединен с первым выходом узла декодирования режима запроса, второй выход которого соединен с четвертым входом дешифратора запросных сигналов, причем второй вход устройства для декодирования запросных сигналов соединен с шестым входом узла декодирования режима запроса.

2. Устройство для декодирования запросных сигналов по п.1, отличающееся тем, что узел предварительной обработки сигнала содержит первый компаратор, второй компаратор, третий компаратор, четвертый компаратор, пятый компаратор, шестой компаратор и седьмой компаратор, первый регистр, второй регистр, третий регистр и четвертый регистр с групповым сбросом, первый блок констант, вторую константу, первый вычитатель, второй вычитатель, первый сумматор, второй сумматор, первый триггер, второй триггер, третий синхронный триггер, четвертый синхронный триггер, пятый синхронный триггер, шестой синхронный триггер, седьмой синхронный триггер, восьмой синхронный триггер, девятый синхронный триггер, первый элемент И, второй элемент И, третий элемент И, четвертый элемент И, пятый элемент И, шестой элемент И, первый элемент ИЛИ, второй элемент ИЛИ, третий элемент ИЛИ, четвертый элемент ИЛИ, пятый элемент ИЛИ, первый формирователь импульса, второй формирователь импульса, третий формирователь импульса, четвертый формирователь импульса, счетчик, дешифратор, первый выход которого соединен с установочными входами третьего и четвертого синхронных триггеров, выход четвертого синхронного триггера соединен с первым входом пятого элемента И, выход которого соединен с разрешающим входом четвертого регистра с групповым сбросом, группа выходов которого соединена с первой группой входов шестого компаратора и является первой группой выходов узла предварительной обработки сигнала, первый выход которого соединен с синхронными сбросами шестого и седьмого синхронных триггеров и выходом второго элемента ИЛИ, первый вход которого соединен с первым входом четвертого элемента ИЛИ и инверсным выходом первого формирователя импульса, прямой выход которого соединен с первым входом третьего элемента ИЛИ, выход которого соединен с первым входом шестого элемента И, выход которого соединен с пятым выходом узла предварительной обработки сигнала, с первым входом счетчика и с установочным входом шестого синхронного триггера, выход которого соединен с первым входом пятого элемента ИЛИ и является четвертым выходом узла предварительной обработки сигнала, второй выход которого соединен со вторым выходом дешифратора и с установочным входом пятого синхронного триггера, выход которого является третьим выходом узла предварительной обработки сигнала, шестой выход которого соединен с выходом девятого синхронного триггера, установочный вход которого соединен с третьим выходом дешифратора, четвертый выход которого соединен с синхронным сбросом четвертого синхронного триггера и установочным входом седьмого синхронного триггера, выход которого соединен с первыми входами первого и третьего элементов И, выход третьего элемента И соединен со вторым входом второго элемента ИЛИ и установочным входом восьмого синхронного триггера, выход которого соединен с первым входом второго элемента И, выход которого соединен с информационным входом четвертого формирователя импульса, выход которого соединен со вторыми входами третьего и четвертого элементов ИЛИ, выход четвертого элемента ИЛИ соединен с синхронным сбросом восьмого синхронного триггера, причем тактовый вход устройства для декодирования запросных сигналов соединен с тактовыми входами первого, второго, третьего и четвертого с групповым сбросом регистров, первого, второго, третьего и четвертого формирователей импульса, первого, второго и третьего, четвертого, пятого, шестого, седьмого, восьмого, девятого синхронных триггеров и счетчика, сбросовый вход которого соединен со сбросовыми входами первого, второго, третьего и четвертого с групповым сбросом регистров, первого, второго, третьего и четвертого формирователей импульса, первого и второго триггеров и является первым входом устройства для декодирования запросных сигналов, первая группа входов которого соединена с информационными входами первого регистра, с первыми группами входов первого, пятого и седьмого компараторов и второго сумматора, группа выходов которого является второй группой выходов узла предварительной обработки сигнала и соединена с информационной группой входов четвертого регистра с групповым сбросом и второй группой входов шестого компаратора, выход которого соединен со вторым входом пятого элемента И, причем первая группа выходов первого блока констант соединена со второй группой входов первого компаратора, выход которого соединен с информационным входом первого формирователя импульса, причем группа выходов первого регистра соединена с информационной группой входов второго регистра и со вторыми группами входов второго сумматора и пятого компаратора, выход которого соединен с первым входом четвертого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен со вторым входом второго элемента И, вторая группа выходов первого блока констант соединена с первыми группами входов первого и второго вычитателя и первого сумматора, группа выходов которого соединена с первой группой входов второго компаратора, выход которого соединен со вторым входом первого элемента И, выход которого соединен с информационным входом второго формирователя импульса, выход которого соединен с третьим входом второго элемента ИЛИ и информационным входом первого триггера, выход которого соединен с информационным входом второго триггера, выход которого соединен с третьим входом третьего элемента ИЛИ, вторая группа входов устройства для декодирования запросных сигналов соединена со вторыми группами входов первого сумматора и второго вычитателя, группа выходов которого соединена с первой группой входов третьего компаратора, выход которого соединен с информационным входом третьего формирователя импульса, выход которого соединен со вторым входом третьего элемента И, третья группа входов устройства для декодирования запросных сигналов соединена со вторыми группами входов второго и третьего компараторов, с информационной группой входов третьего регистра и второй группой входов первого вычитателя, группа выходов которого соединена с первой группой входов четвертого компаратора, выход которого соединен со вторым входом первого элемента ИЛИ, причем группа выходов второго регистра соединена со второй группой входов седьмого компаратора, выход которого соединен со вторым входом четвертого элемента И, причем пятый выход дешифратора соединен с синхронным сбросом третьего синхронного триггера, выход которого соединен с инверсным входом шестого элемента И и со вторым входом пятого элемента ИЛИ, выход которого соединен с разрешающим входом счетчика, группа выходов которого соединена с группой входов дешифратора, шестой и седьмой выходы которого соединены с синхронными сбросами пятого и девятого синхронных триггеров, причем группа выходов второй константы соединена с информационной группой входов счетчика, группа выходов третьего регистра соединена со второй группой входов четвертого компаратора, причем выход шестого элемента И соединен с первым сбросовым входом четвертого регистра с групповым сбросом.

3. Устройство для декодирования запросных сигналов по п.1, отличающееся тем, что узел декодирования режима запроса содержит узел констант, узел вычитателей, формирователь импульса, первый регистр, второй регистр, третий регистр, четвертый регистр, пятый регистр и шестой регистр, счетчик, первый синхронный триггер, второй синхронный триггер, третий синхронный триггер и четвертый синхронный триггер, элемент задержки, первый элемент И, второй элемент И, третий элемент И, четвертый элемент И, пятый элемент И и шестой элемент И и седьмой элемент И, первый элемент ИЛИ, второй элемент ИЛИ и третий элемент ИЛИ, выход которого соединен с первым входом седьмого элемента И, выход которого соединен с установочным входом четвертого триггера, инверсный выход которого соединен с первым входом первого элемента И, выход которого соединен с разрешающим входом первого регистра, с первыми входами третьего и шестого элементов И и с установочным входом второго синхронного триггера, выход которого соединен с первым входом пятого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход седьмого элемента И соединен с первым входом четвертого элемента И и выходом первого элемента ИЛИ, группа входов которого соединена с группой выходов первого регистра и является одиннадцатой группой выходов узла декодирования режима запроса, первая, вторая, третья, четвертая и пятая группы выходов которого соединены с первой, второй, третьей, четвертой и пятой группами выходов узла вычитателей, первая группа входов которого является второй группой входов узла декодирования режима запроса, шестая, седьмая, восьмая, девятая и десятая группы выходов которого соединены с группами выходов второго, третьего, четвертого, пятого и шестого регистров, информационные группы входов которых являются третьей, четвертой, пятой, шестой и седьмой группами входов узла декодирования режима запроса соответственно, первый выход которого соединен с выходом четвертого элемента И, второй вход которого соединен со вторыми входами пятого и шестого элементов И, с синхронным сбросом второго синхронного триггера и выходом второго элемента ИЛИ, первый вход которого соединен со вторым входом третьего элемента И и с выходом первого синхронного триггера, установочный вход которого соединен со вторым входом второго элемента ИЛИ и с выходом второго элемента И, первый вход которого является четвертым входом узла декодирования режима запроса, второй выход которого соединен с выходом формирователя импульса, вход которого является пятым входом узла декодирования режима запроса, первая группа входов которого соединена с информационной группой входов первого регистра, тактовый вход которого соединен тактовыми входами элемента задержки, формирователя импульса, первого, второго, третьего и четвертого синхронных триггеров, второго, третьего, четвертого, пятого и шестого регистров, счетчика и является тактовым входом узла декодирования режима запроса, первый вход которого соединен со сбросовыми входами регистра, первого, второго, третьего и четвертого синхронных триггеров и счетчика, выход которого соединен с третьим входом четвертого элемента И и с синхронными сбросами первого и третьего синхронных триггеров, выход третьего синхронного триггера соединен с разрешающим входом счетчика, причем третий вход узла декодирования режима запроса соединен с разрешающими входами второго, третьего, четвертого, пятого и шестого регистров и с входом элемента задержки, выход которой соединен со вторым входом первого элемента И, второй вход узла декодирования режима запроса соединен со вторым входом второго элемента И, выход третьего элемента И соединен с установочным входом третьего синхронного триггера, шестой вход узла декодирования режима запроса соединен с синхронным сбросом четвертого синхронного триггера, причем выход шестого элемента И соединен со вторым входом четвертого элемента ИЛИ, первая, вторая, третья, четвертая и пятая группы выходов узла констант соединены со второй, третьей, четвертой, пятой и шестой группами входов узла вычитателей.

4. Устройство для декодирования запросных сигналов по п.1, отличающееся тем, что синхронный триггер содержит элемент ИЛИ, элемент И и триггер, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с прямым входом элемента И, выход которого соединен с информационным входом триггера, тактовый вход которого соединен с тактовым входом синхронного триггера, установочный вход которого соединен со вторым входом элемента ИЛИ, причем синхронный сброс синхронного триггера соединен с инверсным входом элемента И, сбросовый вход синхронного триггера соединен со сбросовым входом триггера.

5. Устройство для декодирования запросных сигналов по п.1, отличающееся тем, что регистр с групповым сбросом содержит элемент И, элемент ИЛИ и регистр, группа выходов которого является группой выходов регистра с групповым сбросом, информационный вход которого соединен с прямым входом элемента И, выход которого соединен с информационным входом регистра, разрешающий вход которого соединен с выходом элемента ИЛИ, первый вход которого соединен с инверсным входом элемента И и является первым сбросовым входом регистра с групповым сбросом, разрешающий вход которого соединен со вторым входом элемента ИЛИ, причем тактовый и сбросовый входы регистра с групповым сбросом соединены с тактовым и сбросовым входами регистра.

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ЗАПРОСНЫХ СИГНАЛОВ | 2001 |

|

RU2206103C2 |

| УСТРОЙСТВО ДЛЯ ПОДАЧИ КОЛЕЦ К МЕТАЛЛОРЕЖУЩИМ СТАНКАМ | 1950 |

|

SU87542A1 |

| СПОСОБ ДЕКОДИРОВАНИЯ ЗАПРОСНЫХ СИГНАЛОВ И РАДИОЛОКАЦИОННЫЙ ОТВЕТЧИК ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2420759C1 |

| US2010026553 A1, 04.02.2010 | |||

| US6784787 B1, 31.08.2004 | |||

Авторы

Даты

2015-05-10—Публикация

2014-02-12—Подача