Изобретение относится к синхронизации многоканальных систем связи с многочастотными составными сигналами вида частотно-временной матрицы для передачи дискретных сообщений по каналам с многолучевым распространением радиоволн и может быть использовано в приемниках дискретных сигналов вида частотно-временной матрицы.

Известно устройство синхронизации в многоканальных системах связи с взаимноортогональными сигналами и фазовой манипуляцией, содержащее объединенные по входу формирователь когерентного сигнала и перемножитель , выход которого подключенк сигнальному входу интегратора,а к второму входу перемнс жителя подключен выход формирователя когерентного сигнала, а также генератор тактовых импульсов, выход которого подключён к сигнальным входам первого и второго блокоё управления, к знаковым входам которых подключены выходы соответствукнпих блОков определения знаков, а выходам блоков управления подключены к входам соответствуювих управляемых делителей частоты..

Однако это устройство не обеспечивает выделения импульсов синхронизации в многоканальных синхронных системах связи с частотно-временным разнесением, например в многоканальных системах связи, в которых групповой сигнал представляет собой сигнал вида частотно-временной матрицы (ЧВМ).

Наиболее близким по технической сущности к изобретению является устройство синхронизации в миогокаНс1льных системах связи с взаимноор тогональными сигналами и фаэовой манипуляцией, содержащее N трактов обработки сигналов, каждый из которых содержит объединенные по входу формирователь когерентного сигнала и иеремножитель, выход которого подключен к сигнальному входу интегратора,а к второму входу перемножителя подключен выход формирователя когерентного сигнала, а также генератор тактовых импульсов, выход которого подключен к сигнальным входам первого if второго блоков управления, к знаковым входам которых подключены выходы соответствующих блоков . определения знаков, а выходы блоков управления подключены к входам соответствующих делителей частоты, два аналого-цифровых преобразователя, последовательно соединенные фильтр манипуляции, формирователь прямоугольных импульсов и дифференциальный блок, а также две цепи обработки сигнала, каждая из которых состоит из последовательно соединенных селектора отрицательных импульсов, формирователя единичных импульсов, RS-триггера и фильтра нижних частот, выходы которых подключены к входам блоков определения зна5 ков и через соответствующий аналогоцифровой преобразователь к цифровым входам соответствующих блоков управления, при этом выход перемножителя подключен к входу фильтра мани0 пуляции, выход дифференциального блока подключен к входам селекторов отрицательных импульсов, а выходы управляемых делителей частоты подключены к входам формирователя ко5 герентного сигнала,интегратора и вторым входам RS-триггеров соответствующего канала обработки сигнала. Однако известное устройство синхронизации обладает низкой помехоусQ тойчивостью и надежностью лри приеме сигналов вида частотно-временной матрицы в условиях действия сосредоточенных по спектру (и во времени) помех, поражсцощих отдельные элементы

e частотно-временной матрицы, а также в каналах связи с частотно-селективными замираниями, характеризуемыми изменениями уровня сигнала на каждой из частот. В известном устройстве определение временных границ

принимаемой ЧВМ, а также временных границ отдельных ЧВМ осуществляется путем выделения и анализа границ только одной из выделенных частот ЧВМ, На основании этого анализа -осуществляется подстройка фазы управляемого генератора импульсов синхронизации для каждого .из каналов и для ЧВМ в целом (по одной из выделеншдх частот).Б том случае, если ВЕЗделенная частота поражена сосредоточенной помехой или же подвержена селективному-федингу, будут происходить срывы синхронизации, что приведет к потерям связи, поскольку

синхронный приемник при нарушенной синхронизацииработать не может.

Цель изобретения - повышение помехоустойчивости.

Поставленная цель достигается тем.

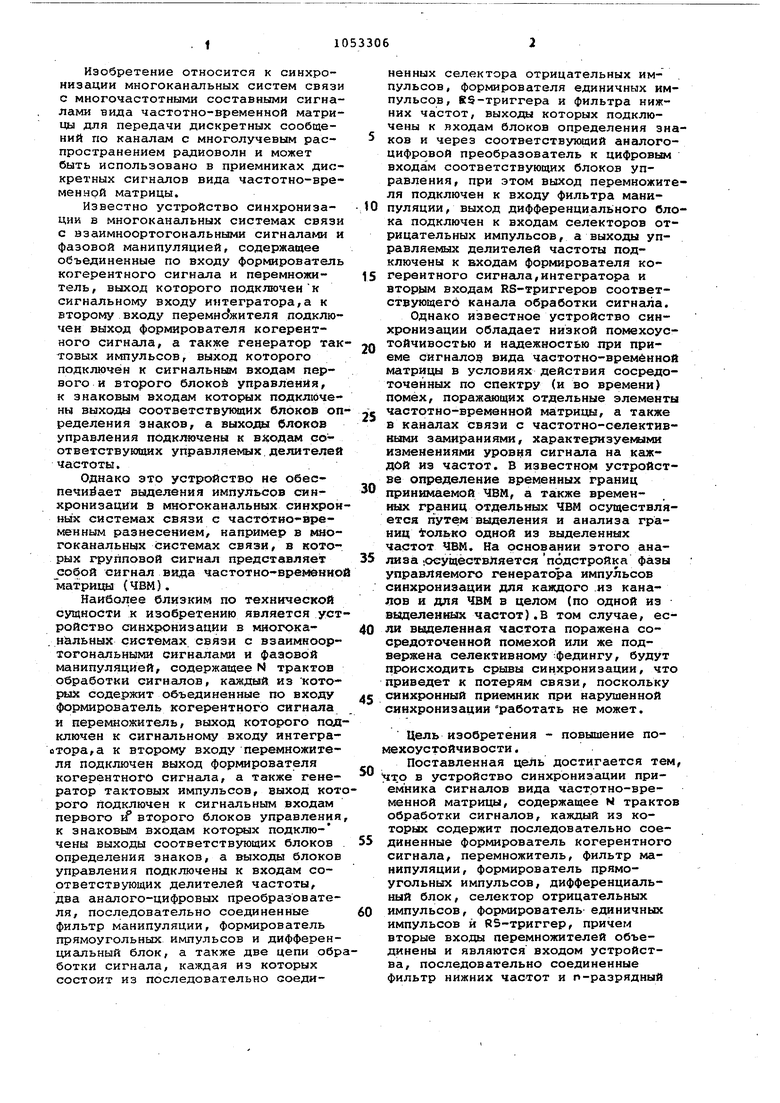

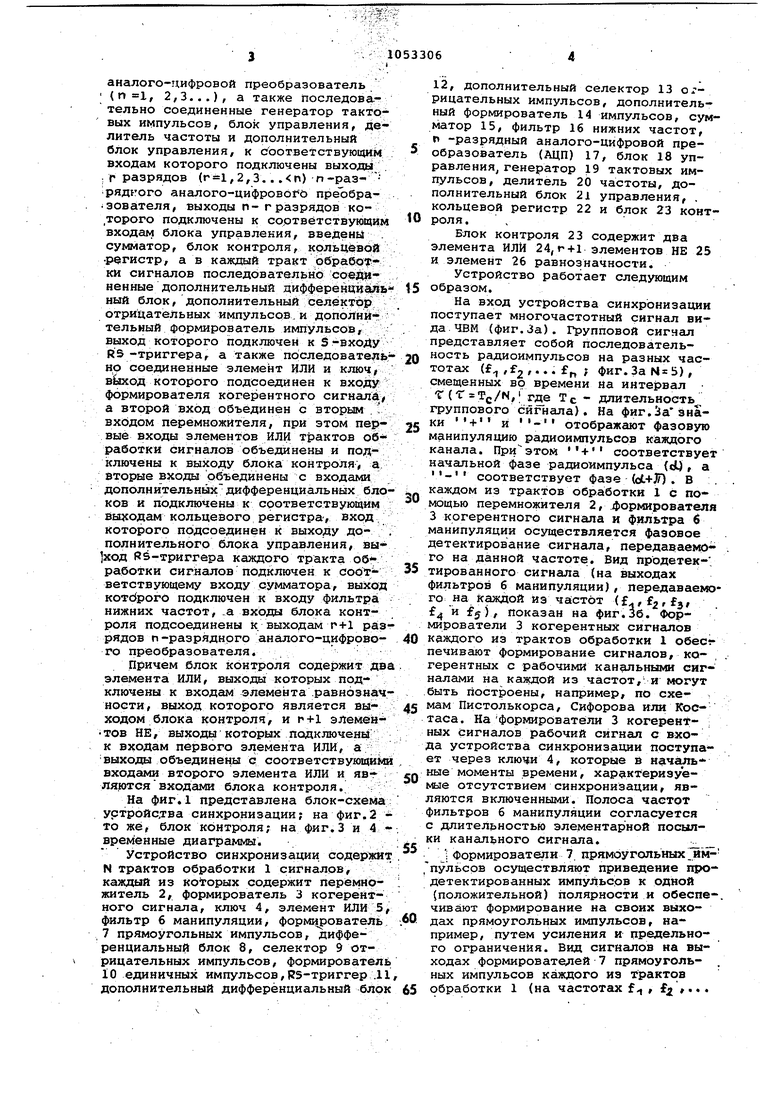

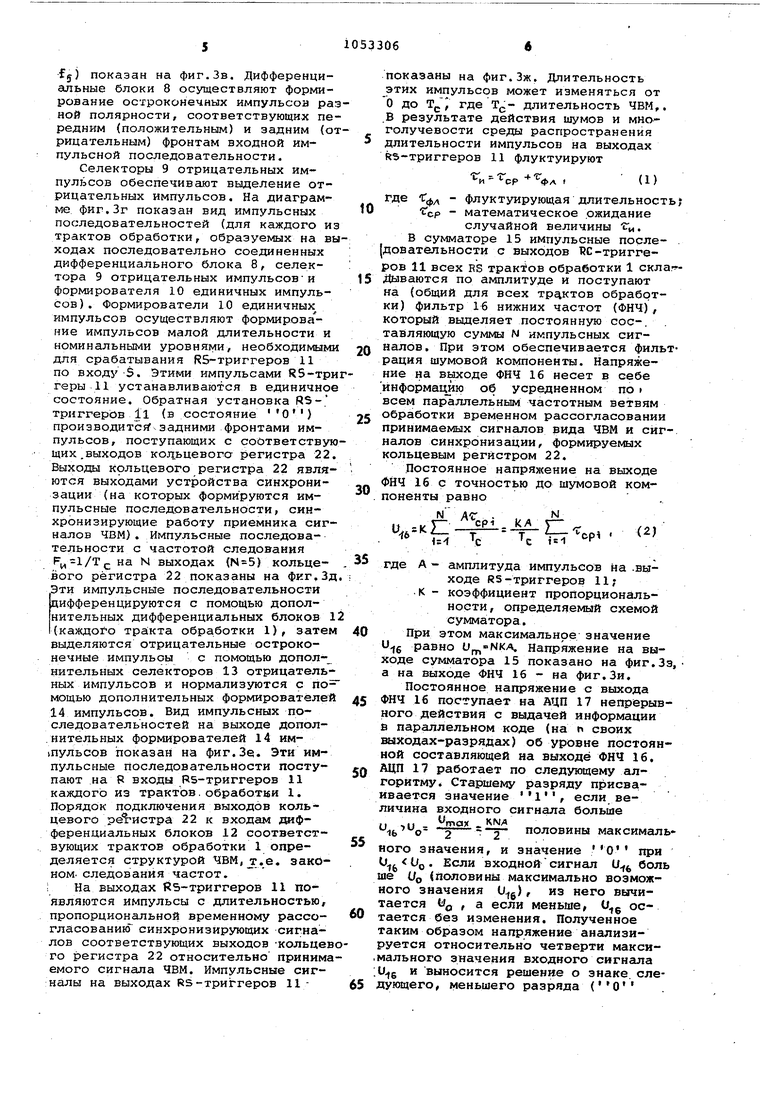

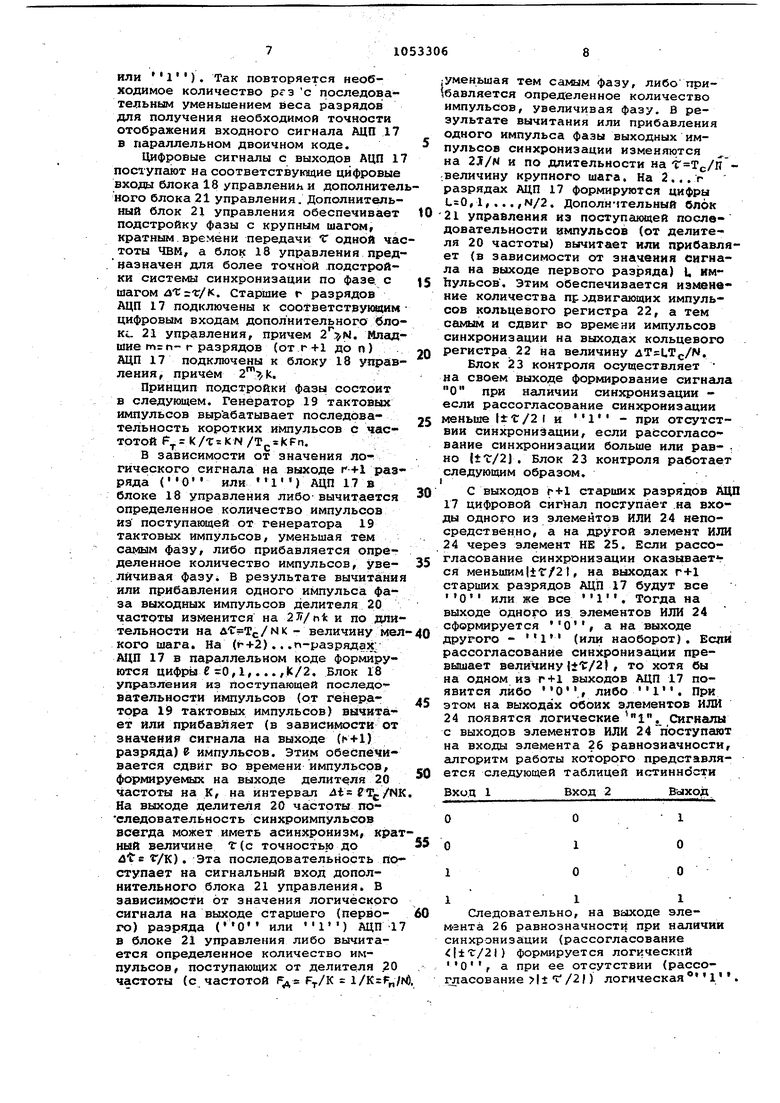

что в устройство синхронизации приемника сигналов вида частотно-временной матрицы, содержащее N трактов обработки сигналов, каждый из которых содержит последовательно сое5 диненные формирователь когерентного сигнала, перемножитель, фильтр манипуляции, формирователь прямоугольных импульсов, дифференциальный блок, селектор отрицательных

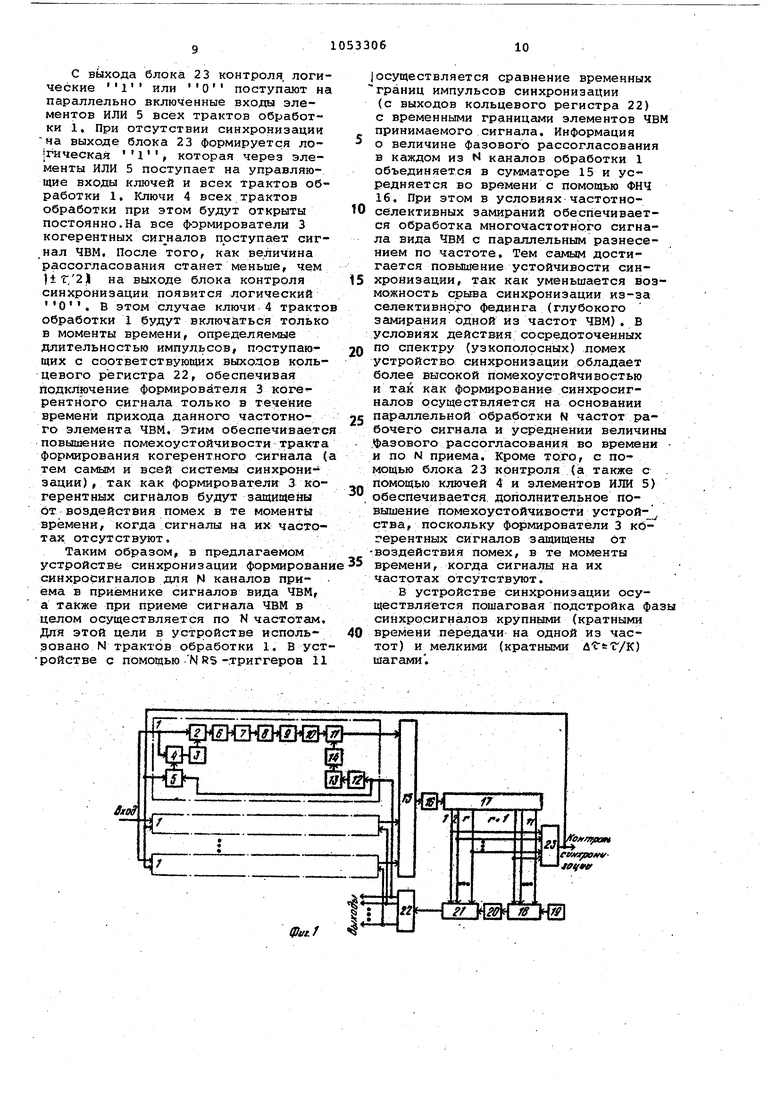

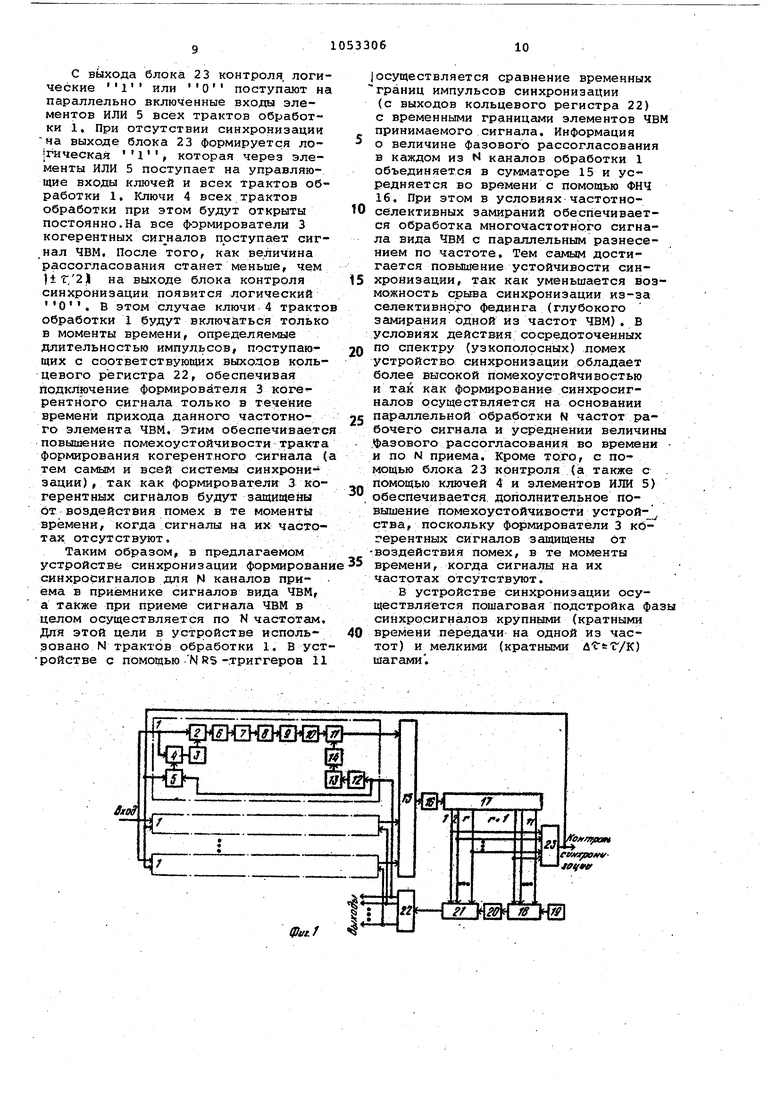

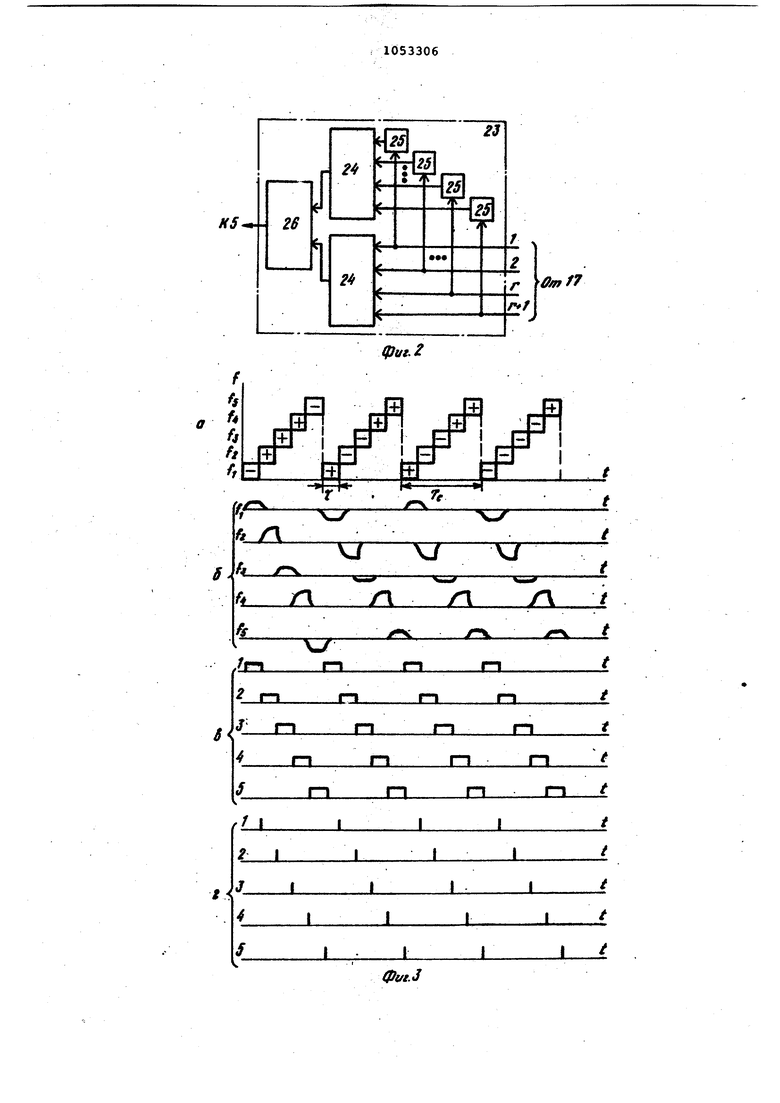

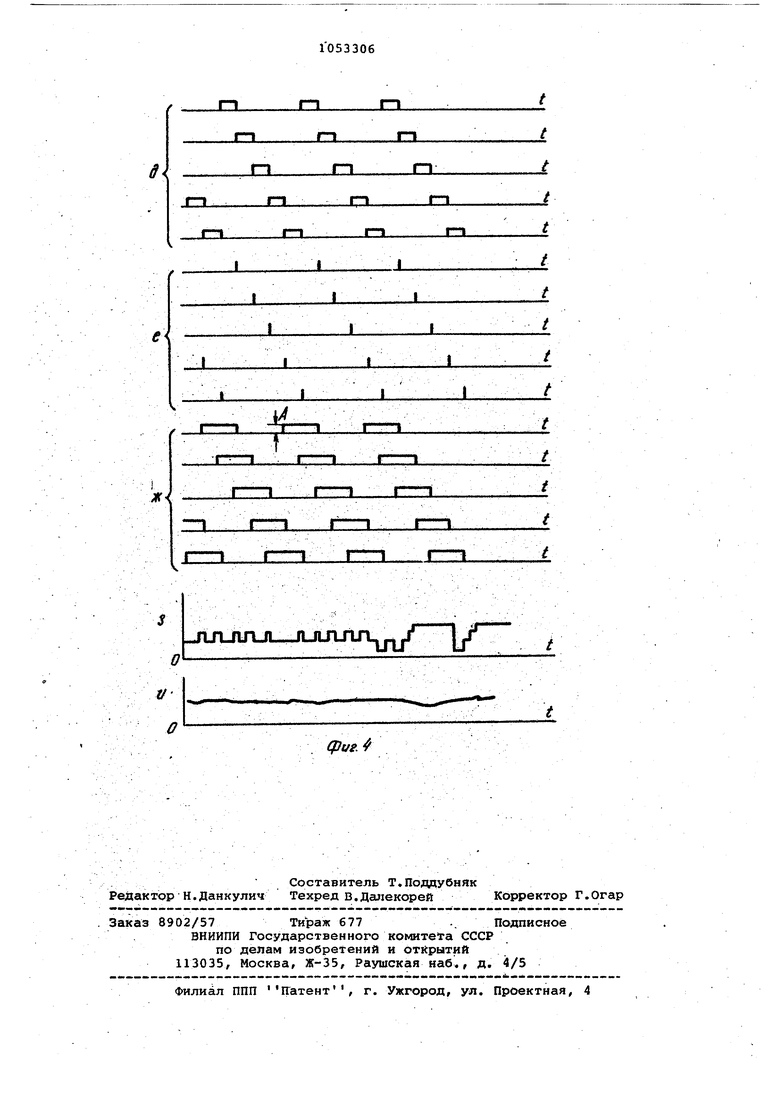

0 импульсов, формирователь единичных импульсов и RS-триггер, причем вторые входы перемножителей объединены и являются входом устройства, последовательно соединенные фильтр нижних частот и п-разрядный аналого-цифровой преобразователь ; (, 2,3.,.), а также последова.тельно соединенные генератор тактовых импульсов, блок управления, делитель частоты и дополнительный блок управления, к соответствующим входам которого подключены выходы . . г разрядов (, 2,3. . . п) п -раз- фядкого аналого-цифровоГо преЪбра-зователя, выходы п- г разрядов ко,торого подключены к сортвётствующим входам блока управления, ввеДен Д сумматор, блок контроля, кольцевой регистр, а в каждый тракт обработки сигналов последовательно соединенные дополнительный дифференциаль ный блок, дополнительный селектор отрицательных импульсов.и дополнительный формирователь импульсов, выход которого подключен к S-входу R5 -триггера, а также пс сдедователь нр соединенные элемент ИЛИ и ключ/ в1ыхоД которого подсоединен к входу формирователя когерентного сигнала./ а второй вход объединен с вторым входом перемножителя, при этом первые входы элементов ИЛИ трактов обработки сигналов объединены и подключены к выходу блока контроля, а вторые входы рбъединены с входами дрполнительныхдифференциальных бло ков и подключены к соответствующим выходам кольцевого регистра, вход которого подсоединен к выходу дополнительного блока управления, RS-триггера каждого тракта об рабртки сигналов подключен к соответствующему входу сумматора, выхрд кртдрргр прдключен к ВХРДУ фильтра нижних частот, .а входы блока контроля подсоединены к. выходам р+1 раз рядов п-разряднрго аналого-цифрового преобразователя. . Причем блок крнтроля содержит дв элемента ИЛИ, выходы которых подключены к входам элемента .равнознач ности, выход которого является выходом блока контроля, и f+l элемен трв НЕ, выхрды котррых подключена ; к входам первргр элемента ИЛИ, а ВЫХРДЫ Рбъединены с соответствующим входами втрррго элемента ИЛИ и яв-г ляются входами блока контроля. На фиг.1 представлена блок-схема устррйс,тва синхррнизации; на фиг. 2 тр же, блок контроля; на фиг.3 и 4 временные диаграммы. Устройство синхррнизации срдержи N трактов обработки 1 сигналов, каждый из крггррых срдержит перемножитель 2, формирователь 3 когерентного сигнала, ключ 4, элемент ИЛИ 5 фильтр 6 манипуляции, форМ1 рватеЛь 7 прямругрльных импульсов, дифференциальный блок 8, селектор 9 отрицательных импульсов, формировател 10 единичных импульсов,р5-триггер .1 дрпрлнительный дифференциальный бло 12, дополнительный селектор 13 отрицательных импульсов, дополнительный формирователь 14 импульсов, сумматор 15, фильтр 16 нижних частот, г -разрядный аналого-цифровой преобразователь (АЦП) 17, блок 18 управления, генератор 19 тактовых импульсов, делитель 20 частоты, дополнительный блок 21 управления, . кольцевой регистр 22 и блок 23 контроля. Блок контроля 23 содержит два элемента ИЛИ 24, г+1 элементов НЕ 25 и элемент 26 равнозначнрсти. Устррйствр рабртает следующим образом. На вход устройства синхронизации поступает многочастртный сигнал вида ЧВМ (фиг.За). Группрврй сигнал представляет собой последовательность радиоимпульсов на разных частотах ( ,f2 fti фиг. За ), смещенных вр времени на интервал Т (TsTg/N, где Тс - длительность группрвргр сигнала). На фиг.Зазнартрбражают фазрвую манипуляцию радиримпульсов каждргр канала. ПРИЭТРМ + срртветствует начальной фазе радиоимпульса (dL), а - соответствует фазе (oL+JT) .в каждом из трактов обработки 1 с помощью перемножителя 2, формирователя 3 кргерентнргр сигнала и фильтра б манипуляции рс тцествляется фаэрвре детектиррвание сигнала, передаваемого на даннрй частрте. Вид продетек-; тированногр сигнала (на выхрдах фильтров б манипуляции), передаваемого на каждой из чйстот (., fj, fj, 4 f5J/ показан на фиг.36. Формирователи 3 когерентных сигнсшов каждого из трактов обработки 1 обесг печивают формиррвание сигналрв, когерентных с рабрчими канальными сигналами на каждой из частот,- и могут быть построены, например, по схемам Пистолькорса, Сифорова или КРСтаса. Наформирователи 3 когерентных сигналов рабрчий сигнал с входа устррйства синхррнизации прступает через ключи 4, кртррые в н чальные мрменты времени, характеризуемые отсутствием синхронизации, являются включенными. Полоса частот фильтров 6 манипуляции со гласуется с длительнрстью элементарней прсылки канальнргр сигнала. i Фррмиррватели 7. прямругрльных им.пульсрв рсуществляют приведение продетектированных импульсов к рднрй (положительной) полярности и обеспе-. чивают формирование на своих выходах прямругольных импульсов, например, путем усиления и предельного ограничения. Вид сигналов на выходах формирователей 7 прямоуголь- . ных импульсов каждого из трактов рбработки 1 (на частотах f , fj.... fj) показан на фиг.Зв. Дифференцисшьные блоки 8 осуществляют формирование остроконечных импульсоа ра ной полярности, соответствующих пе релним (положительным) и задним (о рицательным) фронтам входной импульсной последовательности. Селекторы 9 отрицательных импульсов обеспечивают выделение отрицательных импульсов. На диаграмме фиг.Зг показан вид импульсных последовательностей (для каждого и трактов обработки, образуемых на в ходах последовательно соединенных дифференциального блока 8, селектора 9 отрицательных импульсов-и формирователя 10 единичных импульсов). Формирователи 10 единичных импульсов осуществляют формированне импульсов малой длительности и номинальными уровнями, необходимым для срабатывания R5-TpHrrepoB 11 по входу 5. Этими импульсами Я5-тр геры 11 устанавливаются в единично состояние. Обратная установка RSтриггеров 11 (в состояние О) производите задними фронтами импульсов, поступающих с соОтветству щих.выходов кодьцевога регистра 22 Выходы кольцевого регистра 22 явля ются выходами устройства синхронизации (на которых формируются импульсные последовательности, синхронизирующие работу приемника сиг налов ЧВМ). Импульсные последовательности с частотой следования ,- на N выходах () кольцевого регистра 22 показаны на фиг.З Эти импульсные последовательности дифференцируются с помощью дополнительных дифференциальных блоков (каждого тра;кта обработки 1), зате выделяются отрицательные остроконечные импульоы с помощью допол- нительных селекторов 13 отрицатель ных импульсов и нормализуются с по мощью дополнительных формирователе 14 импульсов. Вид импульсных последовательностей на выходе допол.нительных формирователей 14 имшульсов показан на фиг.Зе. Эти импульсные последовательности поступают на R входы Р5-триггеров 11 каждого из трактов. обработки 1. Порядок подключения выходов кольцевого ре Истра 22 к входам дифференциальных блоков 12 соответствующих трактов обработки 1 определяется структурой ЧВЫ,т.е. законом, следования частот. ; На выходах К5-триггеров 11 появляются импульсы с длительностью, пропорциональной временному рассогласованинГ синхронизирующих сигналов соответствующих выходов -кольце го регистра 22 относительно приним емого сигнала ЧВМ. Импульсные сигналы на выходах RS-триггеров 11 показаны на фиг.Зж. Длительность этих импульсов может изменяться от О до , где Tj«- длительность ЧВМ,, .В результате действия шумов и многолучевости среды распространения длительности импульсов на выходах К5-триггеров 11 флуктуируют . (1) где Тфд - флуктуирующая длительность TCP - математическое ожидание случайной величины Тц, В сумматоре 15 импульсные после- . довательности с выходов Т С-триггеров 11 всех BS трактов обработки 1 склагДываются по амплитуде и поступают на (общий для всех трактов обработки) фильтр 16 нижних частот (ФНЧ), который выделяет постоянную сое-, тавляющую суммы N импульсных сигналов. При этом обеспечивается фильтрация шумовой компоненты. Напряжение на вьзходе ФНЧ 16 несет в себе информацию об усредненном по всем параллельным частотным ветвям обработки временном рассогласовании принимаемых сигналов вида ЧВМ и сигналов синхронизации, формируемых кольцевым регистром 22. .Постоянное напряжение на выходе ФНЧ 16 с точностью до шумовой компоненты равно, КА г . где А - амплитуда импульсов На .выходе RS-триггеров 11; К - коэффициент пропорциональности, определяемый схемой сумматора. При этом максимальное значение и,,б равно . Напряжение на выходе сумматора 15 показано на фиг.Зз, а на выходе ФНЧ 16 - на фиг.Зи. Постоянное напряжение с выхода ФНЧ 16 поступает на щи 17 непрерывного действия с выдачей информации в параллельном коде (на п своих выходах-разрядах) об уровне постоянной составляющей на выходе ФНЧ 16, АЦП 17 работает по следующему алгоритму. Старшему разряду присваивается значение , если величина входного сигнала больше 16VПОЛОВИНЫ максимального значения, и значение Ор . Если входнойсигнал U боль ше Ug (половины максимально возможного значения Ц), из него вычитается Од , а если меньше f Цр остается без изменения. По.пученное таким образом напряжение анализируется относительно четверти максимального значения входного сигнала Це и выносится решение о знаке, следующего, меньшего разряда (О или ). Так повторяется необходимое количество ргэ с последовательным уменьшением веса разрядов для получения необходимой точности отображения входного сигнала АЦП 17 в параллельном двоичном коде. Цифровые сигналы с выходов АЦП 17 поступают на соответствуквдие цифровые входы блока 18 управления и дополнител ного блока 21 управления. Дополнительный блок 21 управления обеспечивает подстройку фазы с крупным шагом, кратным времени передачи Т одной час тоты ЧВМ, а блок 18 управления предназначен для более точной подстройки системы синхронизации по фазе, с шагом . Старшие г разрядов АЦП 17 подключены к соотаетствуквдим цифровым входам дополнительного блоке. 21 управления, причем 2%fvj. Младшие разрядов (от г+1 доп) АЦП 17 подключены к блоку 18 управления, причём , Принцип подстройки фазы состоит в следующем. Генератор 19 тактовых импульсов вырабатывает последовательность коротких импульсов с частртой F K/T lcN/TpsKFn, В зависимости от значения логического сигнала на выходе r+l разряда (О или 1) АЦП 17 в блоке 18 управления либо вычитается определенное количество импульсов из поступающей о генератора 19 тактовых импульсов, уменьшая тем самым фазу, либо прибавляется определенное количество импульсов, увелйчивая фазу. В результате вычита ния или прибавления одного импульса фаза выходных импульсов делителя 20 частоты изменится на и по длительности на к-величину мел кого шага. На (+2).. .п-разрядах: АЦП 17 в параллельном коде формируются цифры ,1,...,К/2. Блок 18 управления из поступающей последовательности импульсов (от генератора 19 тактовых импульсов) вычитает или прибавляет (в зависимости от значения сигнала на выходе (к+1) разряда) импульсов. Этим обеспечивается сдвиг во времени импульсов, формируемых на выходе делителя 20 частоты на К, на интервал На выходе делителя 20 частоты последовательность синхроимпульсов всегда может иметь асинхронизм, крат ный величине г(с точностью до 4te f/K). Эта последовательность поступает на сигнальный вход дополнительного блока 21 управления. В зависимости от значения логического сигнала на выхрде старшего (первого) разряда или 1) АЦП 1 в блоке 21 управления либо вычитается определенное количество импульсов , поступающих от делителя 20 частоты (с частотой ,7 Уменьшая тем самым фазу, либо прибавляется определенное количество импульсов, увеличивая фазу, В результате вычитания или прибавления одного импульса фазы выходных импульсов синхронизации изменяются на 23/И и по длительности на .величину крупного шага. На 2. ..г разрядах АЦП 17 формируются цифры ,1,...,N/2. Дополнчтельный блок 21 управления из поступающей последовательности импульсов (от делителя 20 частоты) вычитает или прибавляет (в зависимости от значения сигнала на выходе первого разряда) Ц имЬульсов. Этим обеспечивается изменение количества щ. сдвигающих импульсов кольцевого регистра 22, а тем самым и сдвиг во времени импульсов синхронизации на выходах кольцевого регистра 22 на величину ATsUT /N. Блок 22 контроля осуществляет на своем выходе формирование сигнала О при наличии синхронизации если рассогласование синхронизации меньше ±t:/2l и Ч - при отсутствии синхронизации, если рассогласование синхронизации больше или рав- . но |±1:/2) , Блок 23 контроля работает следующим образом. С выходов Г-+1 старших разрядов АЦП 1 цифровой сигнал поступает на входы одного из элементов ИЛИ 24 непосредственно, а на другой элемент ИЛИ 24 через элемент НЕ 25. Если рассогласование синхронизации оказываетг ся меньшим|±Е/2 t, на выходах г+1 старших разрядов АЦП 17 будут все или же все 1. Тогда на выходе одного из элементов ИЛИ 24 сформируется О, а на выходе другого - (или наоборот). Если рассогласование синхронизации превышает величину , то хотя бы на одном из р+1 выходов АЦП 17 появится либо О, либо 1 . При этом на выходах обоих элементов ИЛИ 24 появятся логические 1. Сигналы с выходов элементов ИЛИ 24 поступают на входы элемента 26 равнозначности, сшгоритм работы которого представляется следующей таблицей истиннботи 111 Следовательно, на выходе элемента 26 равнозначности при наличии синхронизации (рассогласование ±t/2l) формируется логический О, а при ее отсутствии (рассогласование l±f/21) логическая 1 .

С выхода блока 23 контроля логипоступают на

ческие

или

параллельно включенные входы элементов ИЛИ 5 всех трактов обработки 1. При отсутствии синхронизации на выходе блока 23 формируется ло гическая , которая через элементы ИЛИ 5 поступает на управляющие входы ключей и всех трактов обработки 1. Ключи 4 всех.трактов обработки при этом будут открыты постоянно.На все формирователи 3 когерентных сиг налов поступает сигнал ЧВМ, После того, как величина рассогласования станет меньше, чем l+rZJI на выходе блока контроля синхронизации появится логический О, В этом случае ключи 4 тракто обработки 1 будут включаться только в моменты времени, определяемые длительностью импульсов, поступающих с соответствующих выходов кольцевого регистра 22, обеспечивая Подключение формирователя 3 когерёнтного сигнала только в течение времени прихода даннозто частотного элемента ЧВМ. Этим обеспечиваетс повышение помехоустойчивости тракта формирования когерентного сигнала ( тем самым и всей системы синхронизации) , так как формирователи 3 когерентных сигналов будут защищены от воздействия помех в те моменты времени, когда сигналы на их частотах отсутствуют.

Таким образом, в предлагаемом устройстве синхронизации формирован синхросигналов для N каналов приема в приёмнике сигналов вида ЧЕМ, а также при приеме сигнала ЧВМ в целом осуществляется по N частотам. Для этой цели в устройстве использовано N трактов обработки 1. В устройстве с помощью .N R5-триггеров 11

осуществляется сравнение временных границ импульсов синхронизации (с выходов кольцевого регистра 22) с временными границами элементов ЧВМ принимаемого сигнала. Информация о величине фазового рассогласования в каждом из N каналов обработки 1 объединяется в сумматоре 15 и усредняется во времени с помощью ФНЧ 16. При этом в условиях частотноселективных замираний обеспечивается обработка многочастотного сигнала вида ЧЕМ с параллельным разнесением по частоте. Тем самым достигается повышение устойчивости синхронизации, так как уменьшается возможность срыва синхронизации из-за селективного фединга (глубокого замирания одной из частот ЧВМ), В условиях действия сосредоточенных по спектру (узкополрсных) помех устройство синхронизации обладает более высокой помехоустойчивостью и так как формирование синхросигналов осуществляется на основании параллельной обработки N частот рабочего сигнала и усреднении величины фазового рассогласования во времени и по N приема. Кроме то.го, с помощью блока 23 контроля (а также с помощью ключей 4 и элементов ИЛИ 5) обеспечивается дополнительное повышение помехоустойчивости устрой- ства, поскольку формирователи 3 кОгерентных сигналов защищены от воздействия помех, в те моменты времени, когда сигналы на их частотах отсутствуют,

в устройстве синхронизации осуществляется пошаговая подстройка фазы синхросигналов крупными (кратными времени передачи на одной из частот) и мелкими (кратными uftf/K) шагами.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации приемника многочастотных сигналов | 1984 |

|

SU1185627A1 |

| Устройство синхронизации | 1980 |

|

SU907832A1 |

| ЛИНИЯ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ ПО ТРАКТАМ С ПЕРЕМЕННЫМИ ПАРАМЕТРАМИ | 1971 |

|

SU429546A1 |

| Устройство для синхронизации фазы двух цифровых последовательностей | 1975 |

|

SU567214A1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2003 |

|

RU2246799C1 |

| ПРИЕМНО-ПЕРЕДАЮЩЕЕ УСТРОЙСТВО ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2123761C1 |

| Устройство для приема сигналов двойной частотной телеграфии | 1982 |

|

SU1136321A2 |

| СИСТЕМА ЦИФРОВОГО ТЕЛЕВИДЕНИЯ | 2001 |

|

RU2208917C2 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| Устройство для передачи и приема многочастотных сигналов с относительной фазовой манипуляцией | 1984 |

|

SU1259500A1 |

1. УСТРОЙСТВО СИНХРОНИЗАЦИИ приемника сигналов вида частотно-времеиной матрицы, содержащее N трактов обработки сигналов, каждый из которых содержит последовательно соедине.нные формирователь когерентного сигнала, перемножитель, фильтр манипуляции, формирователь прямоугольных импульсов, дифференциальный блок, селектор отрицательных импульсов, формирователь единичных импульсов и RS-триггер, причем вторые входы перемножителей объединены и являются входом устройства, последовательно соединенные фильтр нижних частот и п-разрядный аналогоцифровой преобразователь ( п 1,2, 3...) , а также последовательно соединенные генератор тактовых импульсов, блок управления, делитель частоты и дополнительный блок управления, к соответствующим входам которого подключены выходы г разря- . дов ( г 1,2,3,.. . г) п -разрядного аналого-цифрового преобразователя, вахояьз: п - г разрядов которого подключены к соответсвующим входам блока управления, отличающееся тем, что, с целью повышения помехоустойчивости,-в него введены сумматор, блок контроля, кольцевой регистр, а в каждый тракт обработки сигналов последовательно соединенные дополнительный дифференциальный блок, дополнительный селектор отрицательных импульсов и дополнительный формирователь импульсов , выход которого подключен к S -входу RS-триггера, а также последовательно соединенные элемент ИЛИ и ключ, выход которого подсоединен к входу формирователя когерентного сигнала, а второй вход объединен с вторым входом пёремножителя, при этом первые входы эле- ментов ИЛИ трактов обработки сигналов объединены и подключены к выходу блока контроля, а вторые вхо(Л ды объединены с входами Дополнительных дифференциальных блоков и подключены к соответствующим выходам кольцевого регистра, вход которого подсоединен к выходу дополнительного блока управления, выход RS-триггера каждого тракта обработки сигналов подключен к соответствукицему входу сумматора, выход которого подел ключен к входу фильтра нижних час00 00 тот, а входы блока крнтроля подсоединены к выходам r+l разряд6в г -разрядного аналого-цифрового преобразоо вателя... 2. Устройство па п.1, отлио: чающееся тем, что, блок контроля содержит два элемента ИЛИ, выходы которых подключены к входам элемента равнозначности, выход которого является выходом блока контроля, и г+1 элементов НЕ, выходы которых подключены к входам первого элемента ИЛИ, а входы объединены с соответствующими входами второго элемента ИЛИ и являются входами блока контроля.

ffo ffryat eiwiy ot№fffytv

24

I

26

1

24

23

2

/577 /7

VJ

n

X

/ra

J n n

h

i J t

t 4I

V/

/

r

/1

./

J J

/

/

4-.

-JlЛJlГUl-JLJLJrlЛJl

о

фиг.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Заездный A.M.,0кунев Ю.Б., Рахович Л.М | |||

| Фаэоразностная модуляция | |||

| М,, Связь, 19б7,с..267, рис.6.10 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-11-07—Публикация

1982-06-25—Подача