чепы к соответствуюпц-1м выходам кольиевото регистра, выходы дополнительных фильтров нижних частот подсоединны к соответствующим входам формирователя сигнала рассогласования, выходы которого подсоединены к соответствующим управляющим входам второго блока добавления-исключения импульсов, а выход сумматора подсоединен к входу дополнительного порогового блока.

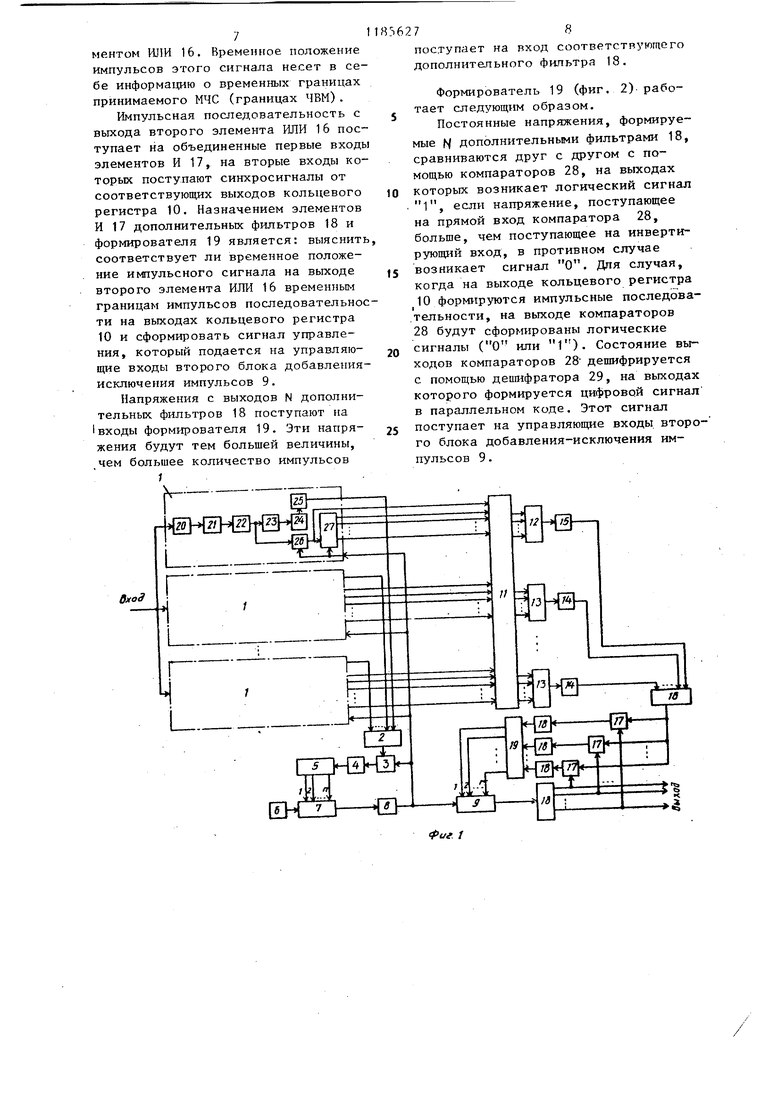

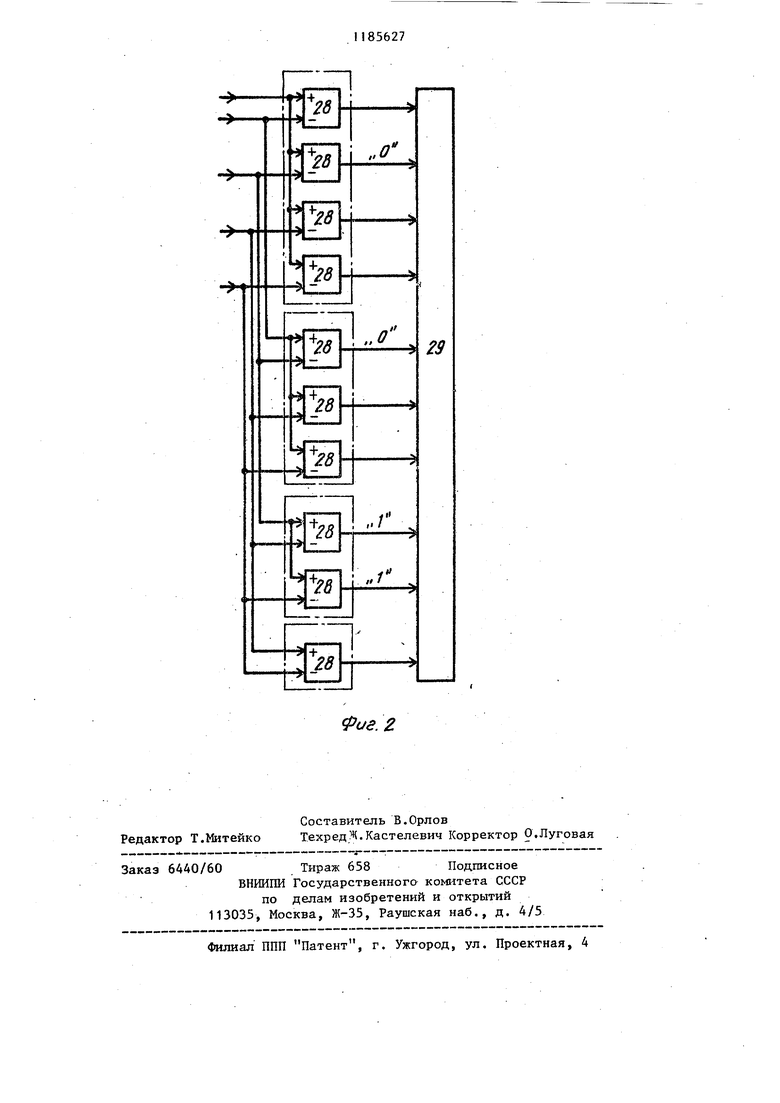

2. Устройство по п. 1, отличающееся тем, что формирователь сигнала рассогласования выполнен в виде дешифратора N - 1 блоков

компараторов, при этом каждьп j-ый блок компараторов ( J 1, 2, ... N- 1) состоит из N - j компараторов, выходы которых подсоединены к соответствующим входам дешифратора, прямые входы компараторов каждого j-ro блока компараторов объединены и подключены к инвертирующим входам соответствующих компараторов j- 1 блоков компараторов,причем объединенные прямые входы компараторов каждого j-го блока компараторов являются входами формирователя сигнала рассогласования, а выходы дешифраторов являются выходами формирователя сигнала рассогласования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации | 1982 |

|

SU1053306A1 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА СИГНАЛОВ РАДИОСТАНЦИЙ | 1998 |

|

RU2132111C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Устройство синхронизации | 1980 |

|

SU907832A1 |

| СПОСОБ И УСТРОЙСТВО СЕЛЕКЦИИ СИГНАЛОВ НАДВОДНОЙ ЦЕЛИ В МОНОИМПУЛЬСНОЙ РЛС | 2004 |

|

RU2278397C2 |

| Устройство кодовой синхронизации | 1990 |

|

SU1774512A1 |

| РАДИОЛОКАЦИОННОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДАЛЬНОСТИ (ВАРИАНТЫ) | 1999 |

|

RU2154285C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА СИГНАЛОВ РАДИОСТАНЦИИ | 2005 |

|

RU2292641C2 |

1. УСТРОЙСТВО СИНХРОНИЗАЦИИ ПРИЕМНИКА МНОГОЧАСТОТНЫХ СИГНАЛОВ, содержащее последовательно соединенные генератор тактовых импульсов, первый блок добавления-исключения импульсов, делитель частоты, второй блок добавления-исключения импульсов и кольцевой регистр, последовательно соединенные фильтр нижних частот и аналого-цифровой преобразователь, а также сумматор, и N каналов обработки сигналов, каждый из которых состоит из последовательно соединенных демодулятора, фильтра приема, формирователя прямоугольных импульсов, дифференцирующего блока, селектора отрицательных импульсов и формирователя единичных импульсов, выходы аналого-цифрового преобразователя подсоединены к соответствующим управляющим входам первого блока добавленияисключения импульсов, причем объединенные входы демодуляторов я-вляются входом устройства, а выходы кольцевого регистра являются выходами устройства, отличающеес я тем, что, с целью расширения функциональных возможностей путем обеспечения синхронизации в многоканальных системах связи с многопозиционными сигналами, введены последовательно соединенные первый элемент ИЛИ и RS-триггер, а также второй элемент ИЛИ, М-1 цепей, каж- . дая из которых состоит из последовательно соединенных дополнительного сумматора и порогового блока,допол|нительньй пороговый блок, формирователь сигнала рассогласования и Н цепей, каждая из которых состоит из последовательно соединенных элемента И и дополнительного фильтра нижних частот, а в каждый из кана. лов обработки сигналов введены цос- ледовательно соединенные обнаружитель сигнала и регистр сдвига, при (Л этом выход RS -триггера подсоединен к входу фильтра нижних частот, выход делителя частоты подсоединен к R-входу RS-триггера и объединенным тактовым входам регистров сдвига и обнаружителей сигнала N каналов, обработки сигналов, в каждом из кото-. рых информационньп вход обнаружите00 ля сигнала подсоединен к выходу форел мирователя прямоугольных импульсов, Од выходы формирователей единичных имto пульсов N каналов обработки сигналов sl подсоединены к входам первого элемента ИШ, выходы обнаружителей сигнала и регистров сдвига N каналов обработки сигналов подсоединены к соответствующим входам коммутатора, выходы которого подсоединены к входам сумматора и дополнительных сумматоров, выходы пороговых блоков и дополнительного порогового блока подсоединены к входам второго элемента ИЛИ, выход которого подсоединен к объединенным первым входам элементов И, вторые входы элементов И подклю

Изобретение относится к синхрони ации мно1оканальных систем связи с многочастотными составными сигналами Бида частотно-временной матрицы для передачи дискретных сообщений по каналам с многолучевым распространением радиоволн и может быть использовано в приемниках дискретных сигналов вида частотно-временной матрицы.

Целью изобретения является расширение функциональных возможностей путем обеспечения синхронизации в многоканальных системах связи с многопозиционными сигналамиi

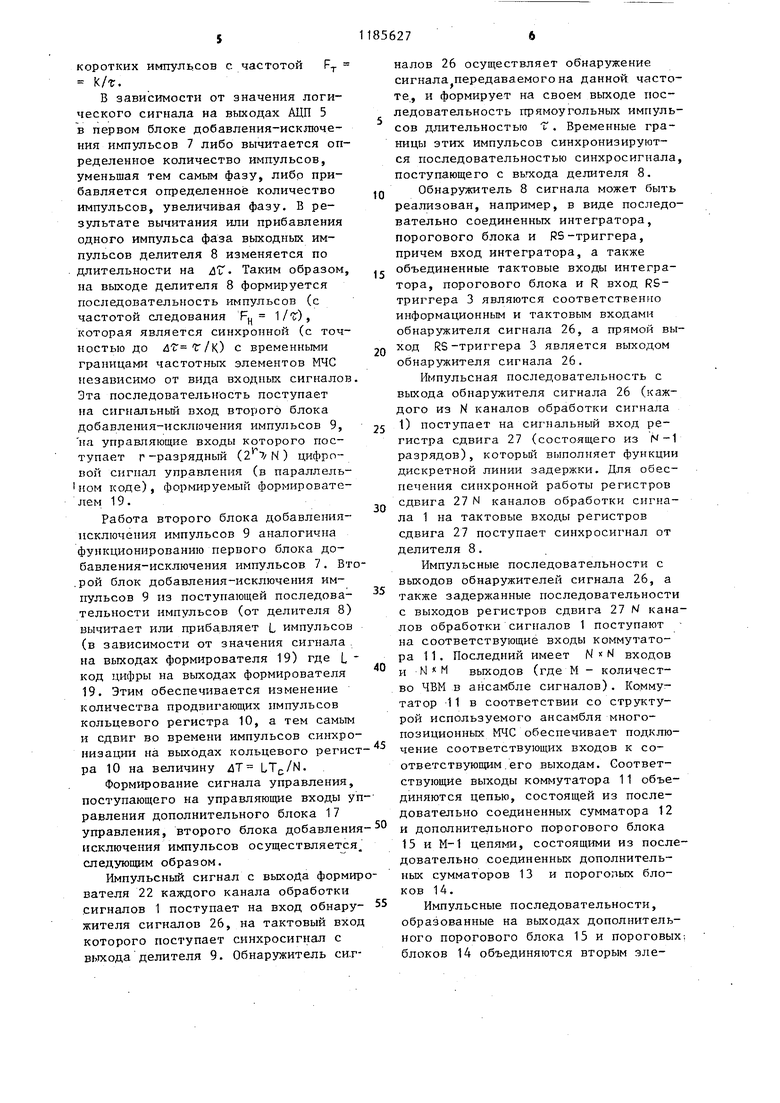

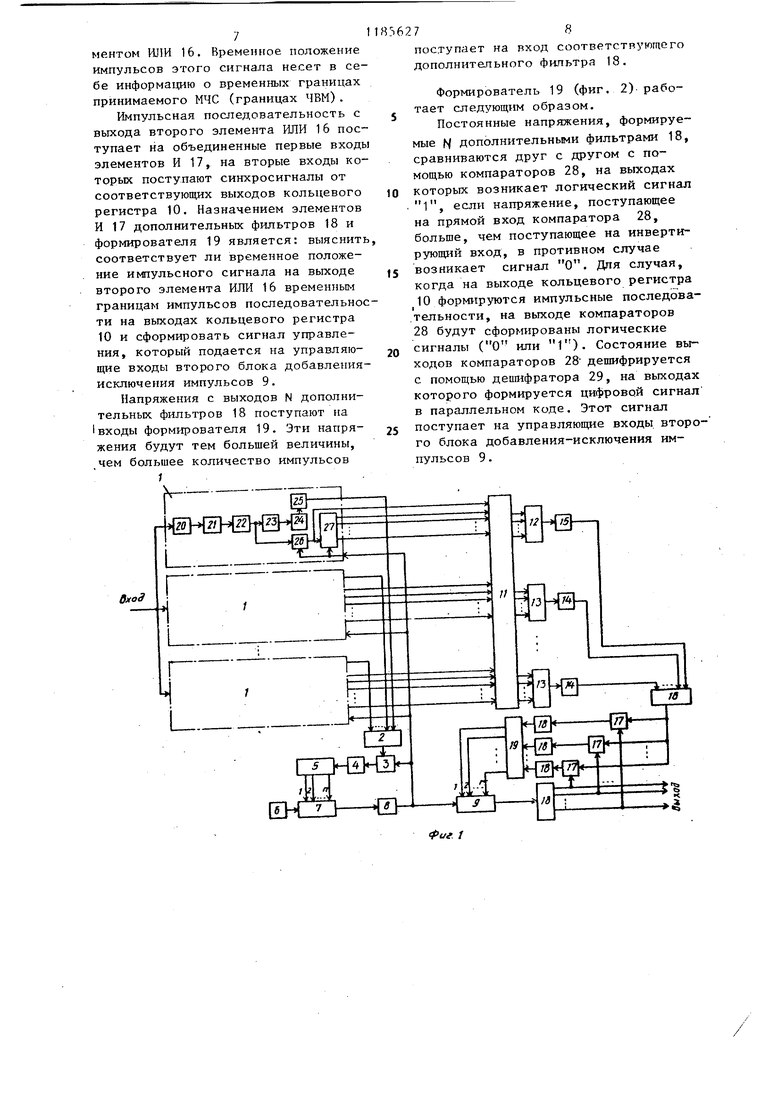

На фиг. 1 представлена структурная электрическая схема устройства синхронизации приемника многочастотных сигналов; на фиг. 2 - структурная электрическая схема формирователя сигнала рассогласования.

Устройство синхронизации приемника многочастотных сигналов содержит N каналов обработки сигнала 1, первьй элемент ИЛИ 2, R5-триггер 3, фильтр 4 нижних частот, аналого-цифровой преобразователь (АЦП) 5, генератор 6 тактовых импульсов, первыу блок добавления-исключения импульсов 7, делитель 8 частоты, второй блок добавления-исключения импульсов 9, кольцевой регистр 10, коммутатор 11, сумматор 12, М-1 дополнительных сумматоров 13, М-1 пороговых блоков 14, догтопнительный пороговый блок 15,

второй элемент ИЛИ 16, N элементов И 17,N дополнительных фильтров 18 нижних частот, формирователь 19 сигнала рассогласования.

Каждый из N каналов обработки сигнала 1 содержит демодулятор 20, фильтр 21 приема, формирователь 22 прямоугольных импульсов, дифференцирующий блок 23, селектор 24 отрицательных импульсов, формирователь

25 единичных импульсов, обнаружитель сигнала 26, регистр 27 сдвига.

Формирователь 19 сигнала рассогласования содержит N(N- 1)/2 компараторов 28 и дешифратор 29.

Устройство синхронизации приемника многочастотных сигналов работает следующим образом.

На вход устройства синхронизации приемника многочастотных сигналов поступает многочастотньм многопозиционный сигнал вида последовательности частотно-временных матриц (ЧВМ)

(фиг. 1). Групповой сигнал представляет собой последовательность радиоимпульсов на разных частотах ( , fjj J п ), смещенных во времени на интервал t (t ),

где Т - длительность группового сигнала. В рассматриваемом примере технической реализации предлагаемого устройства синхронизации приемника многочастотных сигналов используется оптимальный ансамбль много3позиционных многочастотных сигналов (МЧС) с количеством элементов (частот) , равных N 5, и включающий в себя М 4 частотно-временных матриц. Начальная фаза каждого из канальных радиоимпульсов ЧВМ может манипулироваться (по фазе) на Ji . В каждом из N каналов обработки сиг нала с помощью демодулятора 20 и фильтра 21 осуществляется либо амплитудное (в этом случае демодулятор 20 реализуется в виде амплитудного детектора), либо фазовое (в этом случае демодулятор 20 реализуется в виде перемиожителя и фop mpoвaтeля когерентного сигнала) детектирование сигнала, передаваемого по данной частоте. Полоса частот фильтра 21 согласуется с длительностью V элементарной посьшки канального сигнала Формирователь 22 осуществляет приведение продетектированных импуль сов к одной (положительной) полярности (если канальные сигналы являются фазоманипулированными) и обеспечивает формирование прямоугольных импульсов, длительность которых равна длительности соответствующих радиоимпульсов. Дифференцирующий блок 23 осуществляет формирование остроконечных импульсов разной полярности, соответствующих передним и задним фронтам входной импульсной последовательности. . Селектор 24 обеспечивает выделени отрицательных импульсов. Импульсные последовательности, формируемые формирователями 25 N каналов обработки сигналов 1, объединяются с помощью первого элемента ИЛИ 2. Формирователи 25 осуществляют формирование импульсов малой длительности и с номинальными уровнями, необходимыми для срабатывания R5-триггера 3 и по 5 входу. Импульсы этой последовательности устанавливают R5 -триггер 3 в состояние 1. Установка КЗ-триггера 3 в состояние О производится последовательностью импульсов с частотой следования Рц 1/f, поступающих с выхода делителя 8 частоты. Эта импульсная последовательность поступает на R-вход RS-триггера 3. На выходе RS-триггера 3 появляются импульсы с длительностью, пропорциональной временному рассогласованию импульсного сигнала на выходе делителя частоты 8 относительно вход ного сигнала ЧВМ. Длительность этих 274 импульсов может изменяться от О до t, где длительность одного частотного элемента ЧВМ. В результате Действия шумов и многолучевой среды распространения длительность импульсов на выходе RS-триггера 3 принимает значение и V V , где 1Гфд - флуктуирующая длительность; TCP - математическое ожидание случайной величины Tf, . С помощью фильтра 4 осуществляется выделение постоянной составляющей импульсного сигнала. При этом обеспечивается фильтрация шумовой компоненты. Напряжение на выходе фильтра 4 несет в себе информацию об усредненном (по всем параллельным частотным i ветвям обработки) временном рассогласовании входных сигналов ЧВМ (моментов времени смены частот) относительно импульсного сигнала, формируемого на выходе делителя частоты 8. Постоянное напряжение на выходе фипьтра 4 с точностью до щумовой компоненты равно где А - амплитуда импульсов на выходе 5 .-триггера 3. При этом максимальное значение Ц, равно А-(при tcp f) минимальное значение И равно U/ (при Т,- О, т.е. при отсутствии асинхронизма двумя сравниваемыми импульсами сигнала). Постоянное напряжение с выхода фильтра 4 поступает на АЩ1 5 непрерывного действия с вьщачей информации в параллельном коде об уровне постоянной составляющей на выходе фильтра 4. Цифровые сигналы с выходов АЦП 5 поступают на соответствующие управляющие входы первого блока добавления-исключения импульсов 7, который предназначен для точной подстройки системы синхронизашш по фазе с шагом ЛТ Т/К, причем 2 7 k , где п- число выходов (разрядов) АЦП 5, а V - коэффициент деления делитея 8. Принцип подстройки фазы состоит в следующем. Генератор 6 вьфабатывает последовательность коротких импульсов с частотой F. k/t. в зависимости от значения логического сигнала на выходах АЦП 5 в первом блоке добавления-исключения импульсов 7 либо вычитается определенное количество импульсов, уменьшая тем самым фазу, либр прибавляется определенное количество импульсов, увеличи вая фазу. В результате вычитания или прибавления одного импульса фаза выходных импульсов делителя 8 изменяется по длительности на лТ Таким образом на выходе делителя 8 формируется последовательность импульсов (с частотой следования F, 1 /jr) , которая является синхронной (с точностью до ) с временными границами частотных элементов МЧС независимо от вида входных сигналов Эта последовательность поступает на сигнальньй вход второго блока добавления-исключения импульсов 9, на управляющие входы которого поступает г-разрядный () цифровой сигнал управления (в параллельI ном коде), формируемый формирователем 19. Работа второго блока добавленияисключения импульсов 9 аналогична функционированию первого блока добавления-исключения импульсов 7. Вт .рой блок добавления-исключения импульсов 9 из поступающей последовательности импульсов (от делителя 8) вычитает или прибавляет L импульсов (в зависимости от значения сигнала на выходах формирователя 19) где L код цифры на выходах формирователя 19. Этим обеспечивается изменение количества продвигающих импульсов кольцевого регистра 10, а тем самым и сдвиг во времени импульсов синхро низации на выходах кольцевого регис ра 10 на величину 4Т . Формирование сигнала управления поступающего на управляющие входы у равления дополнительного блока 17 управления, второго блока добавлени исключения импульсов осуществляетс следующим образом. Импульсный сигнал с выхода форми вателя 22 каждого канала обработки сигналов 1 поступает на вход обнару жителя сигналов 26, на тактовый вхо которого поступает синхросигнал с вькода делителя 9. Обнаружитель си. налов 26 осуществляет обнаружение сигнала передаваемогона данной частоте, и формирует на своем выходе последовательность прямоугольных импульсов длительностью Т. Временные границы этих импульсов синхронизируются последовательностью синхросигнала, поступающего с выхода делителя 8, Обнаружитель 8 сигнала может быть реализован, например, в виде последовательно соединенных интегратора, порогового блока и RS-триггера, причем вход интегратора, а также объединенные тактовые входы интегратора, порогового блока и R вход RSтриггера 3 являются соответственно информационным и тактовым входами обнаружителя сигнала 26, а прямой выход RS-триггера 3 является выходом обнаружителя сигнала 26, Импульсная последовательность с выхода обнаружителя сигнала 26 (каждого из N каналов обработки сигнала 1) поступает на сигнальный вход регистра сдвига 27 (состоящего из N-1 разрядов), который выполняет функции дискретной линии задержки. Для обеспечения синхронной работы регистров сдвига 27 N каналов обработки сигнала 1 на тактовые входы регистров сдвига 27 поступает синхросигнал от делителя 8. Импульсные последовательности с выходов обнаружителей сигнаша 26, а также задержанные последовательности с выходов регистров сдвига 27 Ы каналов обработки сигналов 1 поступают на соответствующие входы коммутатора 11. Последний имеет N N входов и выходов (где М - количество ЧВМ в ансамбле сигналов). Коммутатор 11 в соответствии со структурой используемого ансамбля многопозиционных МЧС обеспечивает подключение соответствующих входов к соответствующим .его выходам. Соответствующие выходы коммутатора 11 объединяются цепью, состоящей из последовательно соединенных сумматора 12 и дополнительного порогового блока 15 и М-1 цепями, состоящими из последовательно соединенных дополнительных сумматоров 13 и порогопых блоков 14. Импульсные последовательности, образованные на выходах дополнительного порогового блока 15 и пороговых-, блоков 14 объединяются вторым эле7ментом ИЛИ 16. Временное положение импульсов этого сигнала несет в се бе информацию о временных границах принимаемого МЧС (границах ЧВМ). Импульсная последовательность с выхода второго элемента ИЛИ 16 пос тупает на объединенные первые входы элементов И 17, на вторые входы которых поступают синхросигналы от соответствующих выходов кольцевого регистра 10. Назначением элементов И 17 дополнительных фильтров 18 и формирователя 19 является: выяснить соответствует ли временное положение импульсного сигнала на выходе второго элемента ИЛИ 16 временным границам импульсов последовательнос ти на выходах кольцевого регистра 10 и сформировать сигнал управления, который подается на управляющие входы второго блока добавленияисключения импульсов 9. Напряжения с выходов N дополнительных: фильтров 18 поступают на входы формирователя 19. Эти напряжения будут тем большей величины, .чем большее количество импульсов 27 поступает на вход соответствующего дополнитепьного фильтра 18. Формирователь 19 (фиг. 2) работает следующим образом. Постоянные напряжения, формируемые 1 дополнительными фильтрами 18, сравниваются друг с другом с помощью компараторов 28, на выходах которых возникает логический сигнал .1, если напряжение, поступающее на прямой вход компаратора 28, больше, чем поступающее на инвертирующий вход, в противном случае возникает сигнал О. Для случая, когда на выходе кольцевого регистра 10 формируются импульсные последова.тельности, на выходе компараторов 28 будут сформированы логические сигналы (О или Г ). Состояние выходов компараторов 28 дешифрируется с помощью дешифратора 29, на выходах которого формируется цифровой сигнал в параллельном коде. Этот сигнал поступает на управляющие входы, второго блока добавления-исключения импульсов 9.

Фиг. Z

| Устройство синхронизации | 1980 |

|

SU907832A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство синхронизации | 1982 |

|

SU1053306A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-10-15—Публикация

1984-05-25—Подача