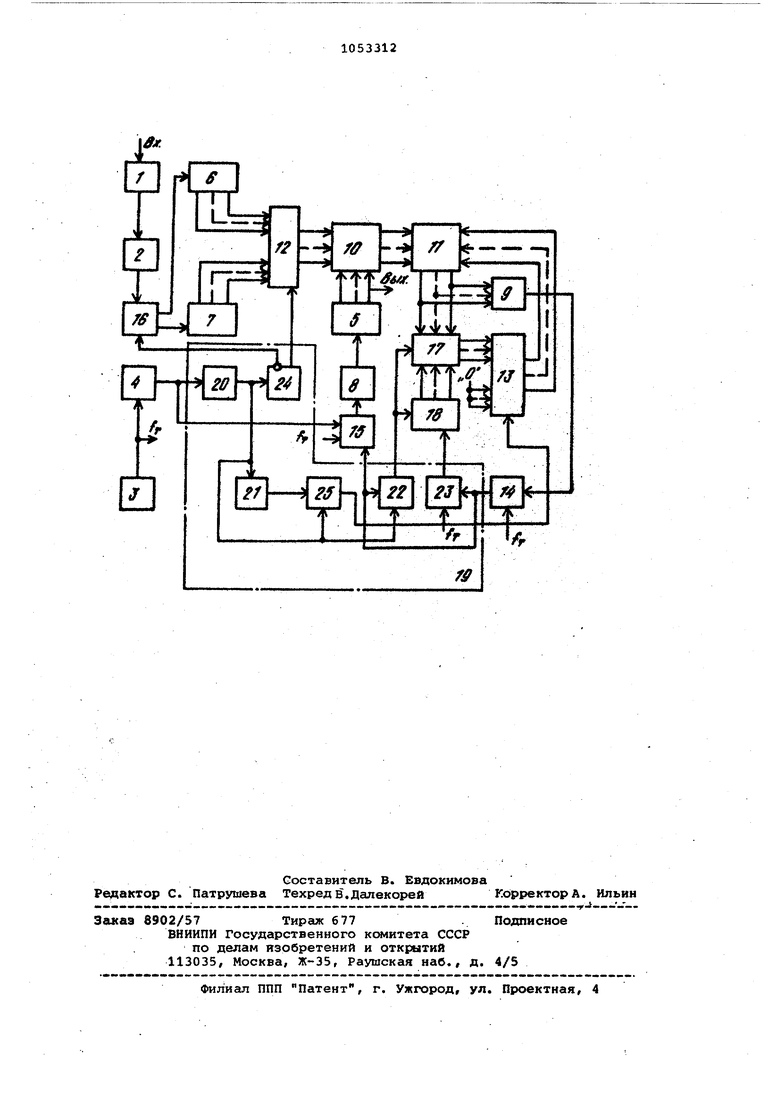

Изобретение относится к раднотехнике и может найти применение в радиотехнических системах, исполь зующих псевдослучайные последовательности в качестве сигналов синх- ронизации.. Известно устройство синхронизаци М-последовательности, содержащее последовательно соедине-шые фильтр нижних частот, перемножитель, первый ключ, детектор определения синх рониэма и блок управления вхождением в синхронизм к другому входу ко торого подключен фильтр нижних частот через последовательно соединенные блок поэлементного приема, регистр сдвига, сумматор совпадений, пороговый блок, а также последовательно соединенные генератор тактовых импульсов, второй ключ, делигтель частоты, третий ключ, регистр сдвига е обратными связями и формирователь местной прследоваталь кости выходы которого подключены к другим входам суглматора совпадений, а выход управления вхождением в синхронизм подключен к управляюцдам входам первого, второго и третьего ключей Cl3. недостатком известного устройств является большое время вхождения в синхронизм Наиболее близким техническим решением к изоО|ретению является устройство синхронизации, содержащее послодрвательно соединенные Фильтр нижних частот и блок поэлементного приема, последовательно соединенные генератор тактовых импульсов, делитель частоты, первый переключател регистр сдвига с обратными связями и первый регистр сдвига, выходы которого подключены к одним входам сумматора совпадений, последовательно соединенные пороговый блок и блок управления вхождением в синх ронизм,.к тактовому входу которого и к тактовому входу первого переклю чателя подключен выход генератора тактовых импульсов, а также второй регистр сдвига и второй переключатель кроме того, выход фильтра нижних частот через последовательно соединенные перемножитель, второй переключатель и детектор определения синхронизма подключен к соот вётствующим входам блока управления вхождением в синхронизм 2. Однако известное устройство имее сравнительно большое время вхождени в синхронизм при малых отношениях сигнал/шум. Цель,изобретения - уменьшение времени вхождения в синхронизм при малых отношениях сигнал/шум. Цель да стигается тем, что в уст ройство синхронизации М-последовате ности, содержащее последовательно соединенные фильтр нижних частот и блок поэлементного приема, последовательно соединенные генератор тактовых импульсов, делитель частоты, первый переключатель, регистр сдвига с обратными связями и первый регистр сдвига, выходы которого подключены к однИм входам суммат ора совпадений, последовательно соединенные пороговый блок и блок управления вхождением в синхронизм, к тактовому входу которого и к тактовому входу первого переключателя подключен выход генератора тактовых импульсов, а также второй регистр сдвига и второй переключатель, введены сумматор, адресный запоминающий блок, адресный счетчик, коммутаторы кода, блок управления релшмом работы и третий регИ;СТр сдвига, при этом выход блрtea поэлементного -Приема через второй переключатель подключен к входам второго и третьего регистров сдвига,: выходы разрядов которых через первый коммутатор кода подключены к соответствующим входам сумматора совпадений, выходы которого через сумматор подключены к входам пррЬгового бло ка и к одним из входов адресного за- . поминающего блока, к другим входам которого подключены выхрды адресного счетчика, а выходя адресного запоминающего блока прдключе ны- к дру- . гим входам сумматора через второй коммутатор кода, арутие объединенные входы котррого являются в {рдамн сигнала нулевого потешшал.а, выход делителя частоты подключен к входу блока управления режимом, работы, выходы которРго подключены соответственно к управляющим входам второго переключателя, первого и второго коммутаторов кода и к объединённым управляющим входам адресного запоминающего: блока и адресного счётчика, к тактовому входу которого прдключен соответствующий выход блока управления, режимрм работы. На чертеже представлена блок- . схема устройства синхронизации М-последовательности. Устройство содержит фильтр 1 нижних частот, блок 2 поэлег ентного приема, генератор 3 тактовых импульсов, делитель 4 частоты, первый, второй и третий регистры 5-7 сдвига, регистр 8 сдвига с обратными связями, пороговый блок 9, сумматор 10 совпадений, сумматор 11, первый и второй коммутаторы 12 и 13 кода, блок 14 управления вхождением в синхронизм, первый и второй переключатели 15 и 16, адресный запоминающий блок 17, адресный счетчик 18 и блок 19 управления режимом работы, состоящий из делителей 20-22 частоты, переклю чателя 23 и триггеров 24 и 25. Устройство синхронизации М-после довательности работает следующим об разом. Сигнал принимаемой М-последовательности через фильтр 1поступа- ет на вход блока 2 поэлементного приема, с выхода которого сигнал, преобразованный в двоичную последовательность импульсов, подается на второй переключатель 16, который через равные промежутки времени t Uf , где Ui - число разрядов регистров 5 И б сдвига, а t - длительность одного элемента принимаемой М-последовательности, поочередно переключает входы регистров 6 и 7 сдвига. Когда за вре.мя t один из регистров б (7) сдвига заполнится выборкой ялины L , взятой из при нимаемой М-последовательности, коммутатор 12 (КОДа:подключит его выходил к входам-сумматора 10 совпадений, а входная М-последовательность начнет поступать на другой регистр 7(6) сдвига. Управляющие сигналы на коммутатор 12 кода и переключатель 16 снимаются с прбтивоположшх плеч триггера 24 блока 19 управле-, ния, который работает в счетном режиме. На тактовый вход триггера 24 поступает сигнал с выхода генератор 3 через делители 4 и 20, причем коэффициент деления делителя 4 выби раётся равным к f f, где | - ча стота генератора 3, а коэффициент Д|аления делителя 20 равен L. В сумматоре 10 совпадений элементы выборки длины 1, , взятые при принимаемой М-последовательности, суглм фуются с элементом выборки та:КОЙ же длины, снимаемой с выходов регистра 5 и взятой из местной М-пс следовательности, генерируемой с кратной скоростью к принимаемой такой, что за время-t LT на выходе сумматора 10 совпадений успевает вычисляться сумма количества совпадающих разрядов для всех временных задержек местной М-последовательнос ти, Результаты суммирования поступают на входы сумматора 11, на вторые входы которого через KONiMy- . татор 13 кода подается двоичный код с выходов адресного запоминающего блока 17. Первоначально коммутатор 13 кода установлен в положени при котором на вторые входы суммато ра 11 поступают нули, и поэтому результаты суммирования полученные для первой обработки, переписываются в адресный запогл{нающий блок 17, где для каждой временной задержки естной М-последовательности по тношению к принимаемой отводится свой адрес адресного счетчика 18. Через время ,f , когда суммирование первой выборки закончится,.выходной импульс делителя 20 переключит триггер 25 в противоположное состояние и его выходной сигнал через коммутатор 13 кода подключит выходы адресного запоминающего блока 17 к вторым входам. cyfiMaTopa 11. Выходной импул1 с делителя 20 длитель,, 1 . ностью dt , поступает на адресный запоминающий блок 17 и на адресный счетчик 18, запрещая на время At перед началом суммирования очередной выборки из входного сигнала запись информации и переключение адреса. За время д1 действия импульса делителя 20 М-последовательность, генерируемая с кратной скоростью до начала сумгдарованИя значений, относящихся к следукидей выборке, успевает дополнительно продвинуться в регистре сдвига 5 на L элементов. Это позволяет, результаты .суммирования, полученные в сумматоре 11 Для последующих выборок, добавлять к результатам, хранящимся для предыдущих выборок, взятых из принима1емой M-rhoследовательности. Выходное число, полученное в cy мaтope 11, сравнивается с порогом, устанавливаемым в пороговом блоке 9. Превышение порога соответствует моменту синхронизма. Если порог превышен, устройство управления 14 вхождением в синхронизм переключает переключателями 15 и 23 feicTpble тактовые импульсы на медленные, а также запрещает прохождение выходных импульсов делителя 20 через делитель 22. В этом режиме скорость формирования и фазы у местной и принимаемой последовательностей совпадают.. Данное устройство принимает решение о наличии синхронизма с использованием полной базы входного сигнала. Это позволяет при низких соотношениях сигнал/шум исключить затраты времени, обусловленные пропуском сигнала и ложной тревогой. Принятые решения обладают высокой достоверностью и не требуют дополнительных проверок, что при низких соотношениях сигнал/шум позволяет зна- . чительно уменьшить время вхождения в синхронизм.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации М-последовательности | 1989 |

|

SU1748274A1 |

| Устройство поиска псевдослучайных последовательностей | 1981 |

|

SU1042199A1 |

| Устройство синхронизации с М-последовательностью | 1981 |

|

SU1003371A2 |

| Устройство синхроназции с -последовательностью | 1974 |

|

SU464981A1 |

| Устройство синхронизации источников сейсмических сигналов | 1981 |

|

SU972428A1 |

| Устройство синхронизации М-последовательности | 1990 |

|

SU1734226A1 |

| Устройство синхронизации с -последовательностью | 1976 |

|

SU585619A2 |

| Устройство синхронизации с м-последовательностью | 1975 |

|

SU534879A2 |

| Устройство синхронизации м-последовательности | 1975 |

|

SU566377A1 |

| Генератор сигналов сложной формы | 1980 |

|

SU983692A1 |

УСТРОПСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ, содержащее последовательно соединенные фильтр нижних частот и блок поэлементного приема, последовательно, соедннеииые генератор тактовых импульсов, делитель частоты, первый переключатель, регистр сдвига с обратными связями и перш:3й регистр сдвига, выходал которого подключены к одним входам cyjitttaTopa совпадений, последовательно соединенные пороговый блок и блок управления вхождением в синхронизм, к тактовому входу которого и к тактовому входу первого переключателя подключен выход генератора тактовых импульсов, а также второй регистр сдвига и второй переключатель , отличающееся тем, что, с целью уменьшения времени вхождения в синхронизм при малых отношениях сигнал/шум, в него введены суадлатор, адресный агшоминаюаий блок, адресный счетчик,. коммутаторы кода, блок управления реяшмом работы и третий регистр сдвига, при этом шлход блока поэлементного приема через второй переключатель подкл1эчен к входгш второго и третьего регистров сдвига, выходы разрядов которых через первый коммутатор кода подключены к соответствую1цим входам суглматора совпскде- НИИ, выходы которого через сумматор подключены к входам порогового блока и к одним из входов адресного запоминакяаего блока, к другим входам которого подключены выходы адресного счетчика, а выходы адресного запоминающего блока подключены . к другим входам сумматора через второй коммутатор кода, другие объединенные входы которого являются входами сигнала нулевого потенциала, выход делителя частоты подключен к входу блока управления режимом работы, выходы которого подключены соответственно к управляющим входам второго переключателя, первого и второго коАФ1утаторов кода и к объединенным управляющим входам адресного запоминаюлего блока и адресного счетчика, к тактовому входу которого подключен соответствующий выход блока управления режимом работы.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство синхронизации м-последовательности | 1975 |

|

SU566377A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ с т-ПОСЛЕДОВАТЕЛЬНОСТЬЮ | 0 |

|

SU347941A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-11-07—Публикация

1981-08-26—Подача