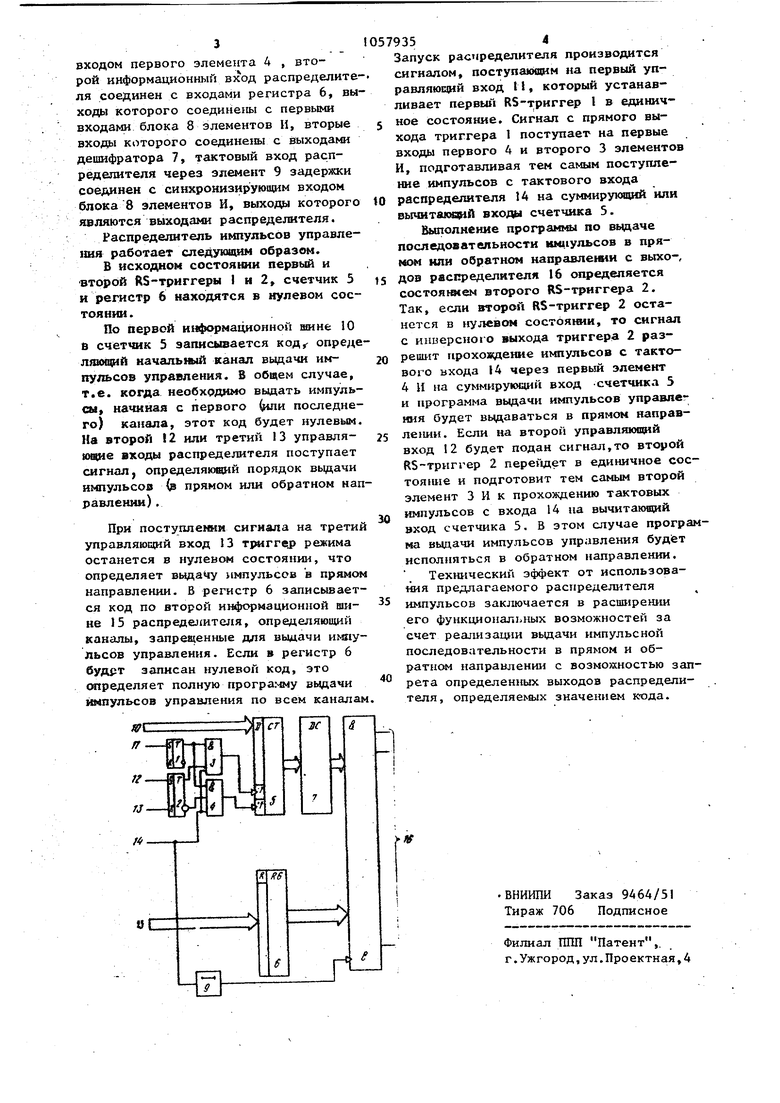

Изобретение относится к электрон(ной коммутационной технике, в частнести к устройствам распределения им пульсных сигналов и может быть испсхпьэовано в устройствах обработки и формации, в синхронизаторах и других дискретных устройствах. Известен распределитель импульсов содержащий счетчик, регистр, дешифра тор l . Недостатками этого устройства являются его сложность и узкие функци ональные возможности. Известен распределитель импульсов, содержащий счетчик,дешифратор, элемент И и первый RS-триггер, S-вхо которого является первым управляи)П5им входа распределителя, прямой выход первого КЗ-триггера соединен с первым входом элемента И, второй вход которого соединен с тактовым входом, выход элемента И соединен с суммиру ющим входом счетчика, выходы которог соединены со входами дешифратора Недостатком такого распределителя являются ограниченные функциональ ные возможности в связи с последова телыым формированием импульсов управле1шя по всем каналам, и отсутствием возмохсности. запрета выдачи управляк р-1Х импульсов в определенные к налы . Цель изобретения - расширение фун циональных возможностей. I Поставленная цель достигается тем, что в распределитель импульсов, содержащий счетчик, дешифратор, элемент, И и первый RS-триггер, S-вхбд которого является первым управляюи м входом распределителя, прямой выход первого RS-триггера соединен с первым входом элемента И, второй вход которого соединен с тактовым входом, выход элемента И соединен с суммирующим входом счетчика , выходы которого соединены с входами дешифратора, введены второй RS-триггер, . регистр, второй элемент И, элемент задерлски и блок элементов И,при чем первая информационная шина расп ределителя соединена с информацией- ными входами счетчика, вычитающий вход которого соединен с выходом вто рого элемента И, первый §ход которого соединен U прямым выходом первого . RS-триггера, второй вход второго элемента И соединен с тактовым входом распределителя, второй управляющий вход которого соединен с S-входом второго RS-триггера, прямой выход которого соединен с третьим входом второго элемента Hj третий управляющий вход соединен с R-входом второго RS-триггера, инверсный выход которого/ соединен с третьим входом первого элемента И, вторая информационная шина распределителя соединена с входом регистра, выходы которого соединены с первыми входами блока элементов И , вторые входы которого соединены с выходами дешифратора, тактовый вход распределителя через элемент задержки соединен с синхронизирующим входом блока элементов И,выходы которого являются выкодами распределителя. На чертеже представлена функциональная схема распределителя импульсов управления./ Распределитель импульсов содерямт первый RS-триггер 1, втор RS-триггер 2, второй элемент 3 И, первый элемент 4 Н, счетчик 5 , регистр 6,дешифратор 7, блок 8 элементов И,элемент 9 задерхски. На функциональной схеме обозначены также первая ин рмационная шина 10, первый управляющий вход II, второй управляющи вход 12, третий управляющий вход 13, тактовый вход 14, вторая информационная Ш1на 15 и выходы 16 распределителя. S-вход первого RS-триггера является первым управляющим входом распределителя, прямой выход первого RS-триггера соединен с первьв4 входом элемента И, второй вход которого соединен с тактовьм входом, выход элемента И соединен с суммирующим входом счетчика, Ш|1хЬды которого соединены с входами дсашфратора.Первая информационная шика 10 распределителя соединена с ин1{юрмациошвами входами счетчика 5, вычитакшшй вход (соторого соединен с выходом второго элемента 3 Н, первый вход которого соединен с выходом первого RS-триггера I,второй вход второго элемента ЭЙ соединен с тактоиым входом распределителя, второй управляющий вход которого соединен с входом второго RS-триггера 2, прямой выход которого соединен с третьш входом второго элемента 3 И, третий управляюие1Й вход соединен с R-входом триггера 2, инверсный выход которого соединен с третьим

входом первого элемента А , второй информационный вход распределителя соединен с входами регистра 6, выходы которого соединены с первыми входаш блока 8 элементов И, вторые входы которого соединены с выходами дешифратора 7, тактовый вход рас.пределителя через элемент 9 задержки соединен с синхронизирующим входом блока 8 элементов И, выходы которого являются выходами распределителя.

Распределитель импульсов управле1ШЯ работает следующим образом.

В исходном СОСТОЯ1ШИ первьШ и второй RS-триггеры 1 и 2, счетчик 5 и регистр 6 находятся в нулевом состоянии.

По первой и{|ф(фмационной шине 10 в счетчик 5 эаписьюается код определяющий начальный канал выдачи импульсов управления. В общем случае, т.е. когда необходимо выдать импульсы, начиная с первого и последнего) канала, этот код будет нулевым. На второй 12 или третий 13 управляющие входы распределителя поступает сигнал, определяющий порядок выдачи импульсов (в прямом или обратном направлении) .

При поступлении сигнала на третий управляюшзий вход 13 триггер режима останется в нулевом состоян ш, что определяет выдачу импульсов в прямом направлении. В регистр 6 записывается код по второй информационной шине 15 распределителя, определяющий каналы, запрещенные для выдачи amiyльсов управления. Если в регистр 6 будрт записан нулевой код, это определяет полную програ- шу выдачи импульсов управления по всем каналам

579354

Запуск расчределителя производится сигналом, поступающим на первый управляющий вход I, который устанавливает первый RS-триггер I в единич5 ное состояние. Сигнал с прямого выхода триггера 1 поступает на первые входы первого 4 и второго 3 элементов И, подготавливая тем самым поступление импульсов с тактового входа распределителя 14 на суммирующий или вьгчитаю 1й входы счетчика 5.

Вьтолнение пpoгpaм a t по вцдаче последовательности luuiynbcoB в прямом или обратном направле1в1И с выхо-, дов распределителя 16 определяется состоягесем второго RS-триггера 2. Так, если второй RS-триггер 2 останется в нулевом состЬя1ши, то сигнал с инверсного выхода триггера 2 разрешит ирохозкдение импульсов с тактового входа 14 через первый элемент 4 И на суммирующий вход -счетчика 5 и программа выдачи импульсов управлвг иия будет выдаваться в прямом направле1ши. Если на второй управляюо гй вход 12 будет подан сигнал,то второй RS-триггер 2 перейдет в единичное состояние и подготовит тем самым второй элемент 3 И к прохождению тактовых импульсов с входа 14 на вычитающий вход счетчика 5, В этом случае программа выдачи импульсов управления будет исполниться в обратном направлении.

Технический эффект от использования предлагаемого распределителя и шульсав заключается в расширении его функциональных возможностей за счет реализации выдачи импульсной последовательности в прямом и обратном направлении с возможностью запрета определенных выходов распределителя, определяемых значением кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределитель импульсов | 1983 |

|

SU1148022A2 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| Распределитель импульсов | 1984 |

|

SU1241220A1 |

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

| Позиционный дискретный электропривод | 1985 |

|

SU1352474A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| Устройство для моделирования поглощающих цепей Маркова | 1989 |

|

SU1810888A1 |

| Преобразователь частоты в код | 1985 |

|

SU1356207A1 |

| Устройство для контроля срабатывания клавиш наборного поля | 1986 |

|

SU1432524A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ, содержащий счетчик, дешифратор, элемент И и первый RS-триггер, 5-вход которого является первым управляющим входом распределителя, прямой выход первого RS-триггера соединен с перBbw входом элемента И, второй вход которого соединен с тактовым входом, выход элемента И соединен с суммирующим входом счетчика, выходы которого соединены с входами дешифратора, отличающийся тем, что,с целью расширения функциональных возможностей, введены второй RS-триггер, регистр, второй элемент И, элемент задержки и блок элементов И, причем первая информационная шина распределителя соединена с информационными входами счетчика, вычитающий вход которого соединен с выходом второго элемента И, первый вход которого соединен с прямым выходом первого RS-триггера, второй вход второго элемента И соединен с тактовым входом распределителя, второй управляющий вход которого соединен с Sвходом второго RS-триггера, прямой выход которого соединен с третьим входом второго элемента И, третий управляю1;1лй вход соединен с R-входом второго RS-триггера, инверсный выi ход которого соединен с третьим вхо(Л дом первого элемента И, вторая информационная шина распределителя соединена с входом регистра, выходы которого соединены с первыми входами блока элементов И , вторые входы которого соединены с выходами дешифратора, тактовый вход распределителя череэ элемент задержки соединен с синхронизирующим входом блока . СП элементов. И, выходы которого являvj ются выходами распределителя. ОО ел

Авторы

Даты

1983-11-30—Публикация

1982-06-11—Подача