Устройство относится к цифровой вычислительной технике и может быть использовано для контроля быстродействующих цифровых логических блоков.

Целью изобретения является повышение быстродействия тестирования и экономия объема памяти устройства.

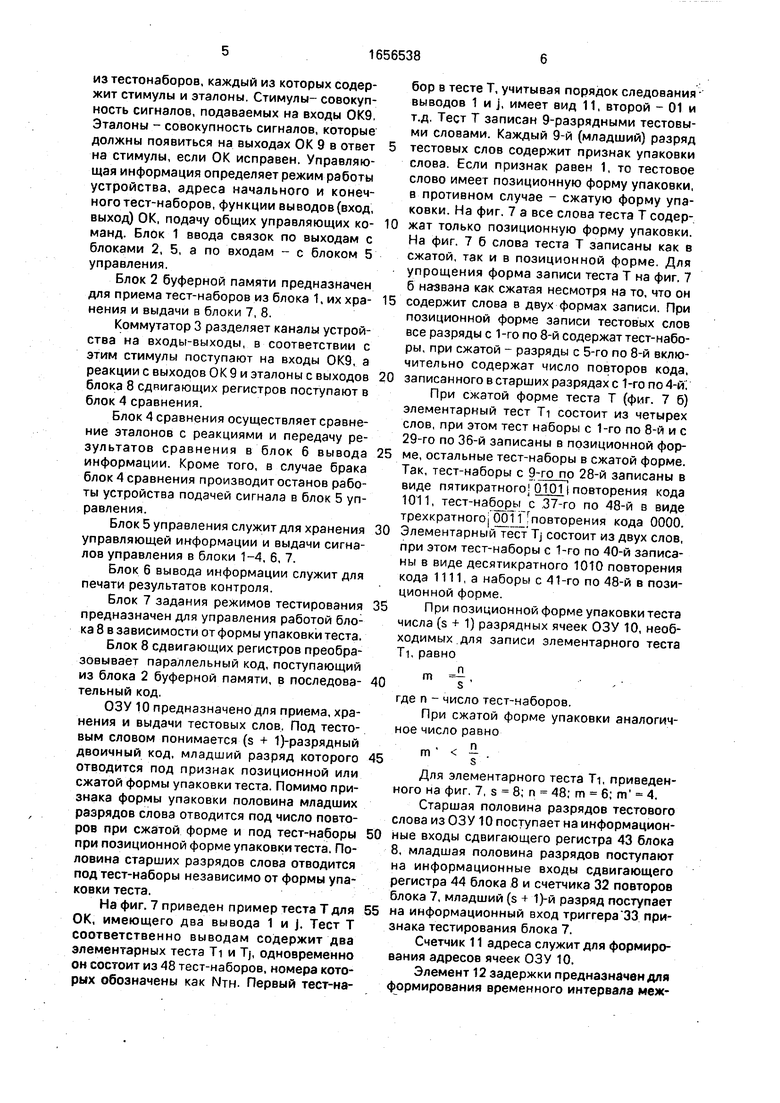

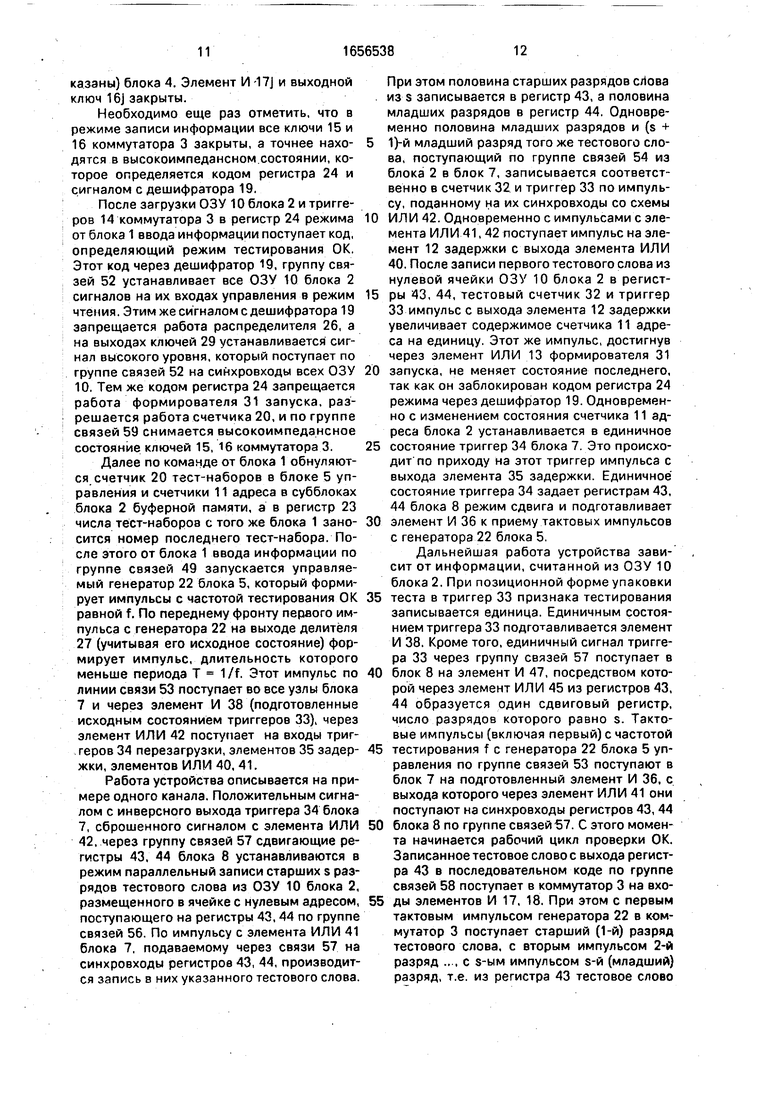

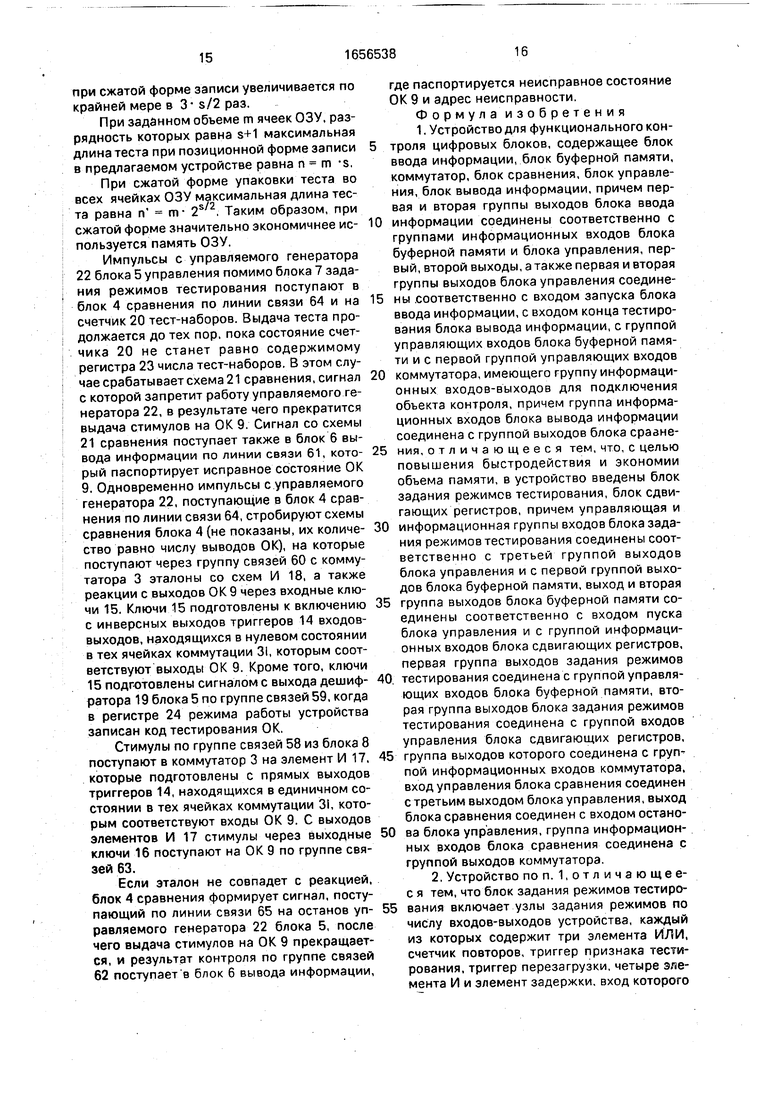

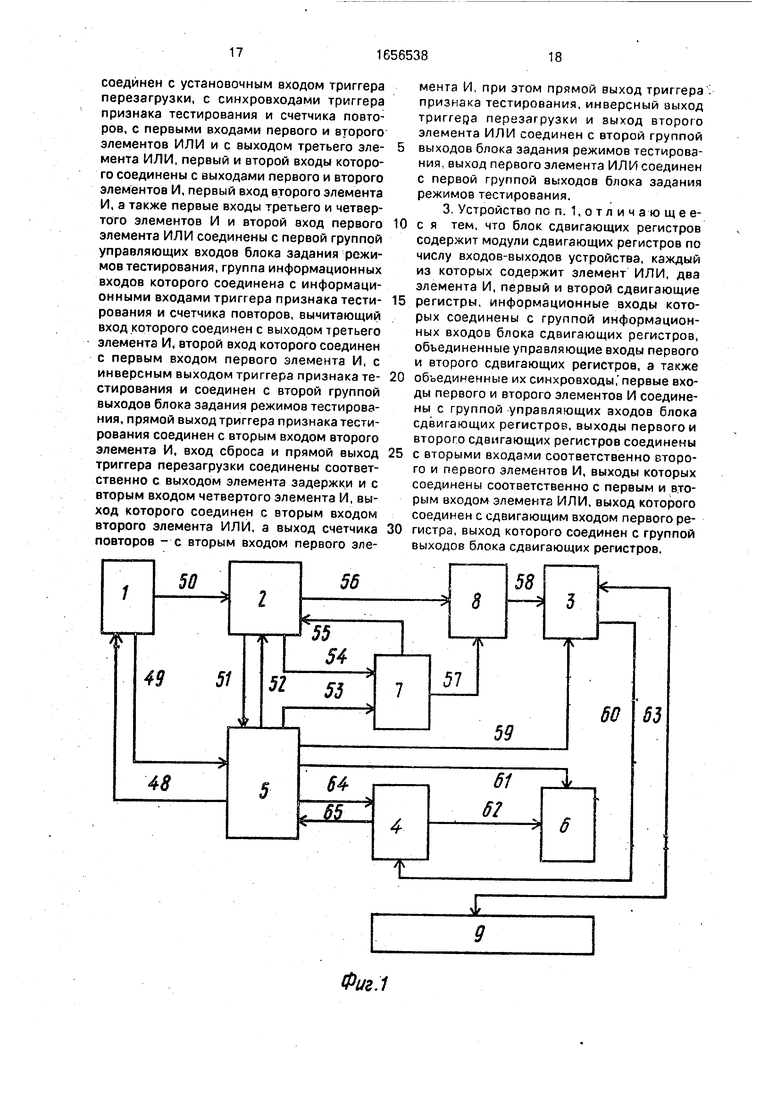

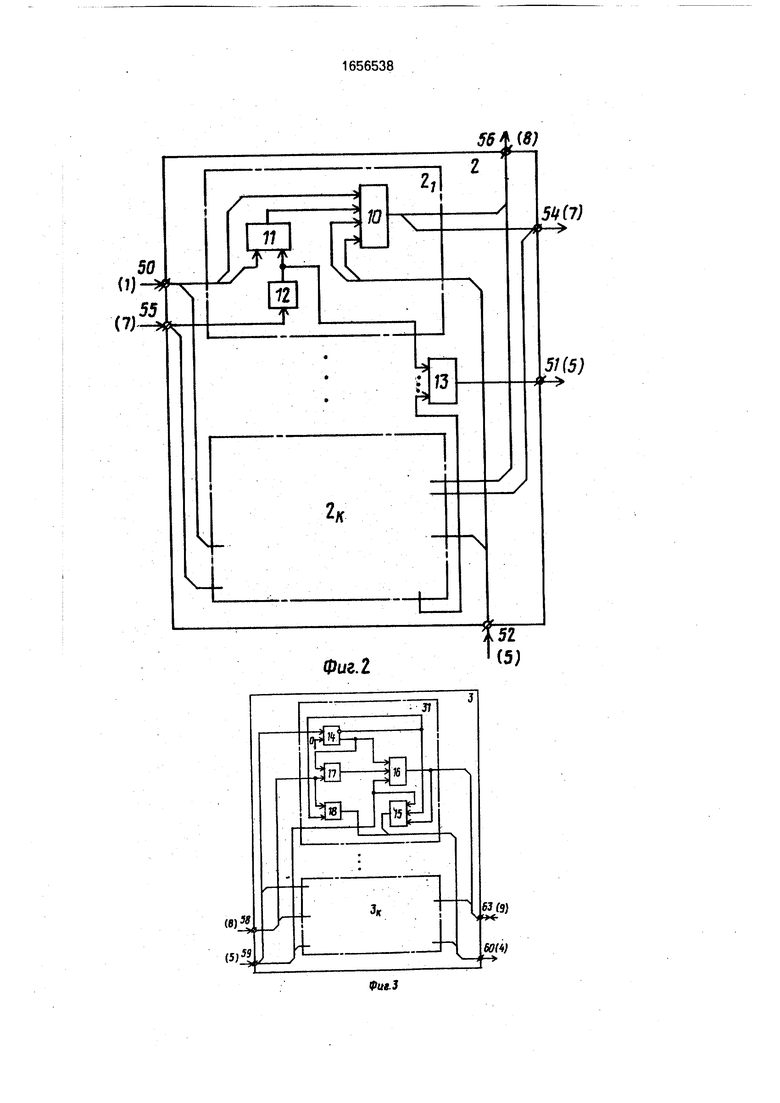

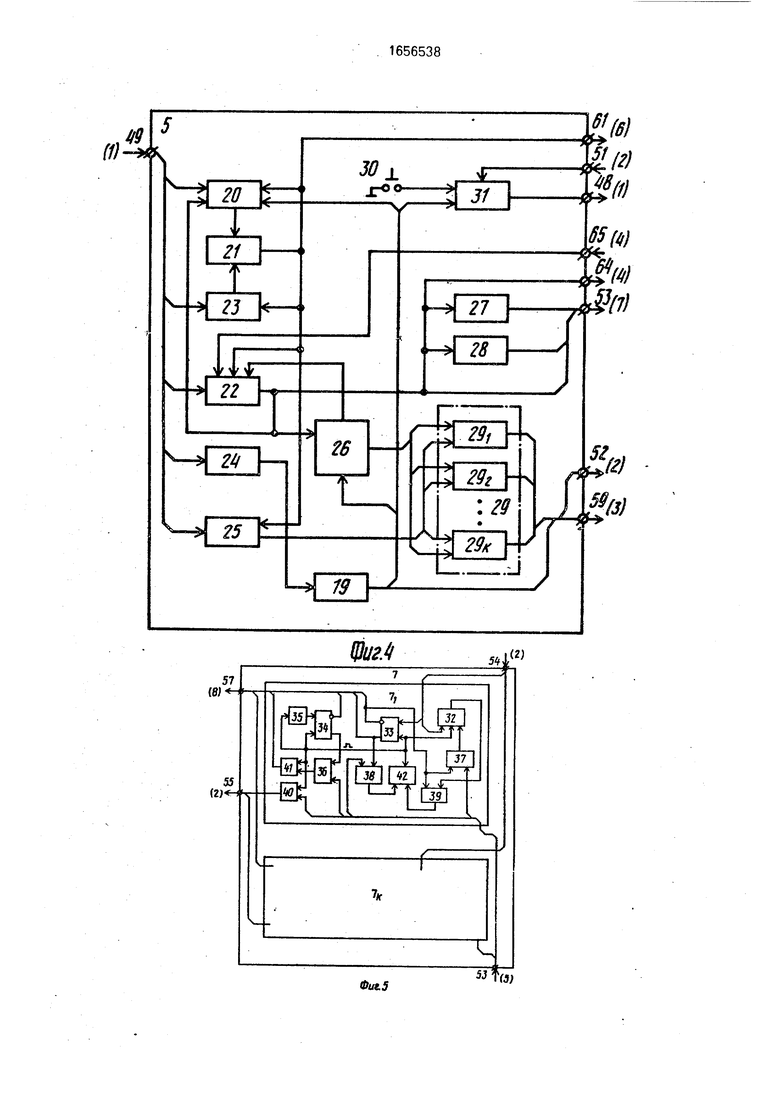

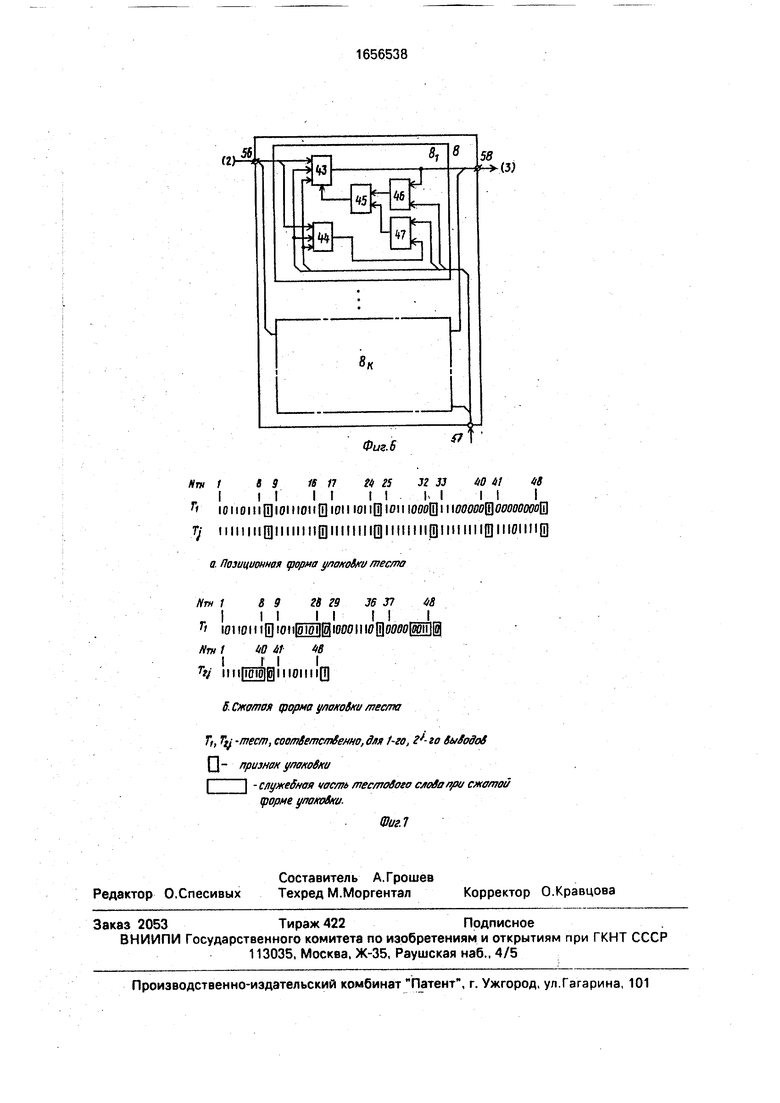

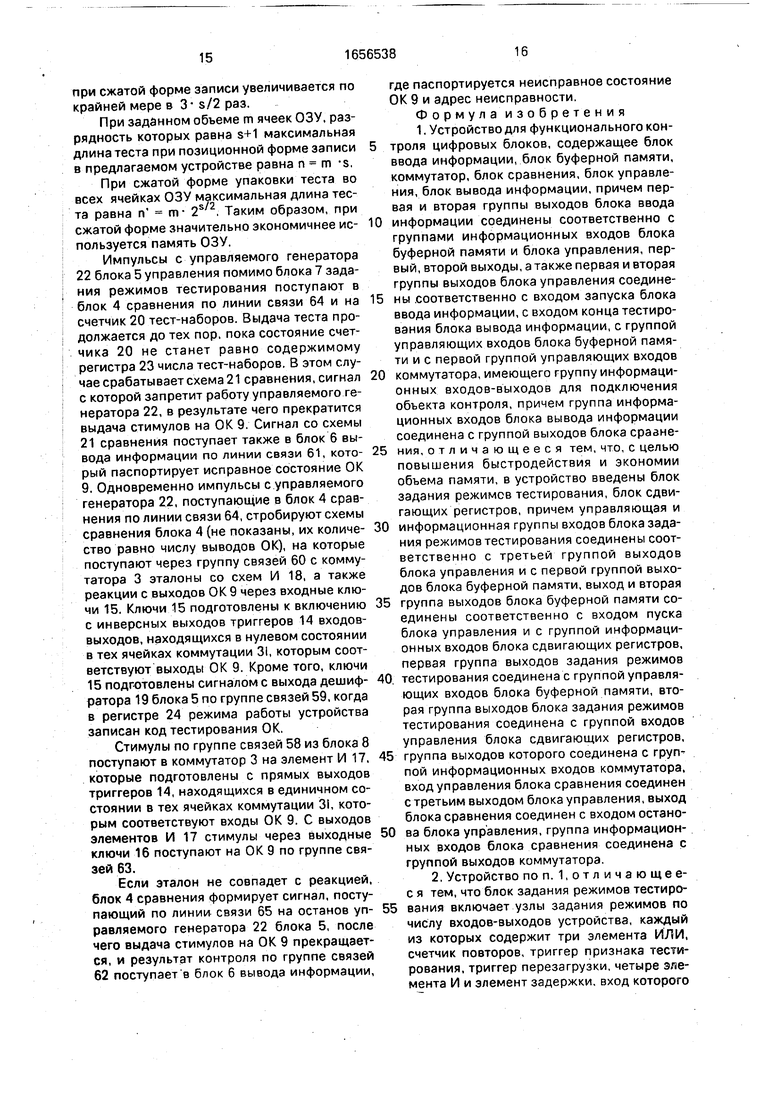

На фиг. 1 приведена блок-схема устройства; на фиг. 2 - схема блока буферной памяти; на фиг. 3 - схема коммутатора; на фиг. 4 - схема блока управления; на фиг.5 - схема блока задания режима тестирования; на фиг. 6 - схема блока сдвигающих регистров; на фиг. 7 - схема, поясняющая принцип позиционной и сжатой форм упаковки тестов.

Устройство (фиг. 1) содержит блок 1 ввода информации, блок 2 буферной памяти, коммутатор 3, блок 4 сравнения, блокбуправ- ления, блок 6 вывода информации, блок 7 задания режимов тестирования, блок 8 сдвигающих регистров, объект 9 контроля (ОК).

Блок 2 буферной памяти (фиг. 2) содержит субблоки 21...2к памяти, число которых равно числу К входов-выходов (каналов) устройства. Каждый субблок содержит ОЗУ 10, счетчик 11 адреса, элемент 12 задержки. Кроме того, блок 2 содержит элемент ИЛИ 13.

Коммутатор 3 (фиг. 3) содержит ячейки 3i...3 коммутации, число которых равно числу каналов устройства. Каждая ячейка содержит триггер 14 входа-выхода, входной ключ 15, выходной ключ 16, элементы И 17 и 18.

Блок 5 управления (фиг. 4) содержит дешифратор 19, счетчик 20 тестнаборов, схему 21 сравнения, управляемый генератор 22, регистр 23 числа тест-наборов, регистр 24 режима работы устройства, регистр 25 адреса канала, распределитель 26, первый делитель 27 частоты, второй делитель 28 частоты, группу переключателей 29, кнопку 30 пуска, формирователь 31 запуска.

Блок 7 задания режимов тестирования (фиг. 5) содержит узлы 71...7к задания режимов, число которых равно числу каналов устройства. Каждый узел содержит счетчик 32 повторов, триггер 33 признака тестирования, триггер 34 перезагрузки, элемент 35 задержки, элементы И 36 - 39. элементы ИЛИ 40-42.

Ё

0

ел о ел

00 00

Блок 8 сдвигающих регистров (фиг. 6) содержит модули сдвигающих регистров 81...8к, число которых равно числу каналов устройства. Каждый модуль содержит сдвигающие регистры 43, 44 элемент ИЛИ 45, элементы И 46, 47.

На фиг. 1-6 изображены линии и группы связей.

Линия 48 связи между первым выходом блока 5 управления и входом запуска блока

1ввода информации для передачи с формирователя 31 запуска команды Пуск.

Группа связей 49 между второй группой выходов блока 1 ввода и группой информационных входов блока 5 управления для передачи команд управления в счетчик 20 тест-наборов, регистр 23 числа тест-наборов, управляемый генератор 22, регистр 24 режима, регистр 25 адреса.

Группа связей 50 между первой группой выходов блока 1 ввода и группой информационных входов блока 2 буферной памяти, по которой передаются команды обнуления счетчика 11 адреса и тестовые слова для записи и ячейку ОЗУ 10.

Линия 51 связи между выходом блока 2 буферной памяти и входом пуска блока 5 управления для передачи команды Пуск с выхода элемента ИЛИ 13 на формирователь 31 запуска.

Группа связей 52, управляющих между первой группой выходов блока 5 управления и группой управляющих входов блока 2 буферной памяти для передачи с дешифратора 19 и группы переключателей 29 на ОЗУ 10 команды Запись - чтение и сигнала Запись соответственно.

Группа связей 53 между третьей группой выходов блока 5 управления и управляющей группой входов блока 7 задания режимов тестирования. В режиме тестирования передается сигнал тактовой частоты с выхода управляемого генератора 2 на элемент И 36, сигнал с делителя 27 на элемент И 38 при позиционной форме упаковки тестов, сигнал с делителя 28 на элемент И 37 при сжатой форме упаковки тестов.

Группа связей 54 между первой группой выходов блока 2 буферной памяти и группой информационных входов блока 7 задания режимов тестирования для передачи тестовой информации из ОЗУ 10 в счетчик 32 повторов и триггер 33 признака тестирования.

Группа связей 55 между первой группой выходов блока 7 задания режимов тестирования и группой управляющих входов блока

2буферной памяти для передачи сигнала Увеличение адреса с элемента ИЛИ 40 на элемент 12 задержки.

Группа связей 56 между второй группой выходов блока 2 буферной памяти и группой информационных входов блока 8 сдвигающих регистров для передачи тестовой информации

из ОЗУ 10 в сдвигающие регистры 43 и 44.

Группа связей 57 между второй группой выходов блока 7 задания режимов тестирования и группой управляющих входов блока 8 сдвигающих регистров для передачи сигнала Запись с инверсного выхода триггера 34 перезагрузки на управляющие входы регистров 43, 44. сигнала Сдвиг с элемента ИЛИ 41 на синхровходы регистров 43, 44, признаков позиционной и сжатой форм упаковки теста с прямого и инверсного выходов триггера 33 на входы элементов И 47 и 46 соответственно.

Группа связей 58 между группой выходов блока 8 сдвигающих регистров и группой информационных входов коммутатора 3 для передачи тестов (эталонов и стимулов) с выхода регистра 43 на элементы И 17, 18. Группа связей 59 между второй группой

выходов блока 5 управления и группой управляющих входов коммутатора 3 для передачи сигнала записи с группы переключателей 29 на входы соответствующих триггеров 14, а также для передачи сигнала запрета на ключи 15, 16 с дешифратора 19.

Группа связей 60 между группой выходов коммутатора 3 и группой информационных входов блока 4 сравнения для передачи эталонов с элементов И 16 и реакцией ОК с

выходов ключей 15 на соответствующие каналам элементы сравнения блока 4.

Линия связи 61 между вторым выходом блока 5 управления и входом конец тестирования блока 6 вывода информации для

передачи сигнала Конец тестирования со схемы 21 сравнения.

Группа связей 62 между группой выходов блока 4 сравнения и группой информационных входов блока 6 вывода информации для передачи сигнала результатов сравнения эталонов и реакций ОК.

Каналы 63 устройства для связи с выводами (входами, выходами) ОК.

Линия связи 64 между третьим выходом блока 5 управления и входом управления блока 4 сравнения для передачи сигнала Опрос результата с генератора 22 на элементы сравнения блока 4.

Линия связи 65 с выхода блока 4 сравнения на вход останова блока 5 управления для передачи сигнала останова генератора 22. Блок 1 ввода информации предназначен для ввода, например, с перфоленты тестовой м управляющей информации. Тест состоит

из тестонаборов, каждый из которых содержит стимулы и эталоны. Стимулы- совокупность сигналов, подаваемых на входы ОК9. Эталоны - совокупность сигналов, которые должны появиться на выходах ОК 9 в ответ на стимулы, если ОК исправен. Управляющая информация определяет режим работы устройства, адреса начального и конечного тест-наборов, функции выводов (вход, выход) ОК, подачу общих управляющих команд. Блок 1 ввода связок по выходам с блоками 2, 5, а по входам - с блоком 5 управления.

Блок 2 буферной памяти предназначен для приема тест-наборов из блока 1, их хранения и выдачи в блоки 7, 8.

Коммутатор 3 разделяет каналы устройства на входы-выходы, в соответствии с этим стимулы поступают на входы ОК9, а реакции с выходов ОК 9 и эталоны с выходов блока 8 сдвигающих регистров поступают в блок 4 сравнения.

Блок 4 сравнения осуществляет сравнение эталонов с реакциями и передачу результатов сравнения в блок 6 вывода информации. Кроме того, в случае брака блок 4 сравнения производит останов работы устройства подачей сигнала в блок 5 управления.

Блок 5 управления служит для хранения управляющей информации и выдачи сигналов управления в блоки 1-4, 6, 7.

Блок 6 вывода информации служит для печати результатов контроля.

Блок 7 задания режимов тестирования предназначен для управления работой блока 8 в зависимости от формы упаковки теста.

Блок 8 сдвигающих регистров преобразовывает параллельный код, поступающий из блока 2 буферной памяти, в последовательный код.

ОЗУ 10 предназначено для приема, хранения и выдачи тестовых слов. Под тестовым словом понимается (s + 1)-разрядный двоичный код, младший разряд которого отводится под признак позиционной или сжатой формы упаковки теста. Помимо признака формы упаковки половина младших разрядов слова отводится под число повторов при сжатой форме и под тест-наборы при позиционной форме упаковки теста. Половина старших разрядов слова отводится под тест-наборы независимо от формы упаковки теста.

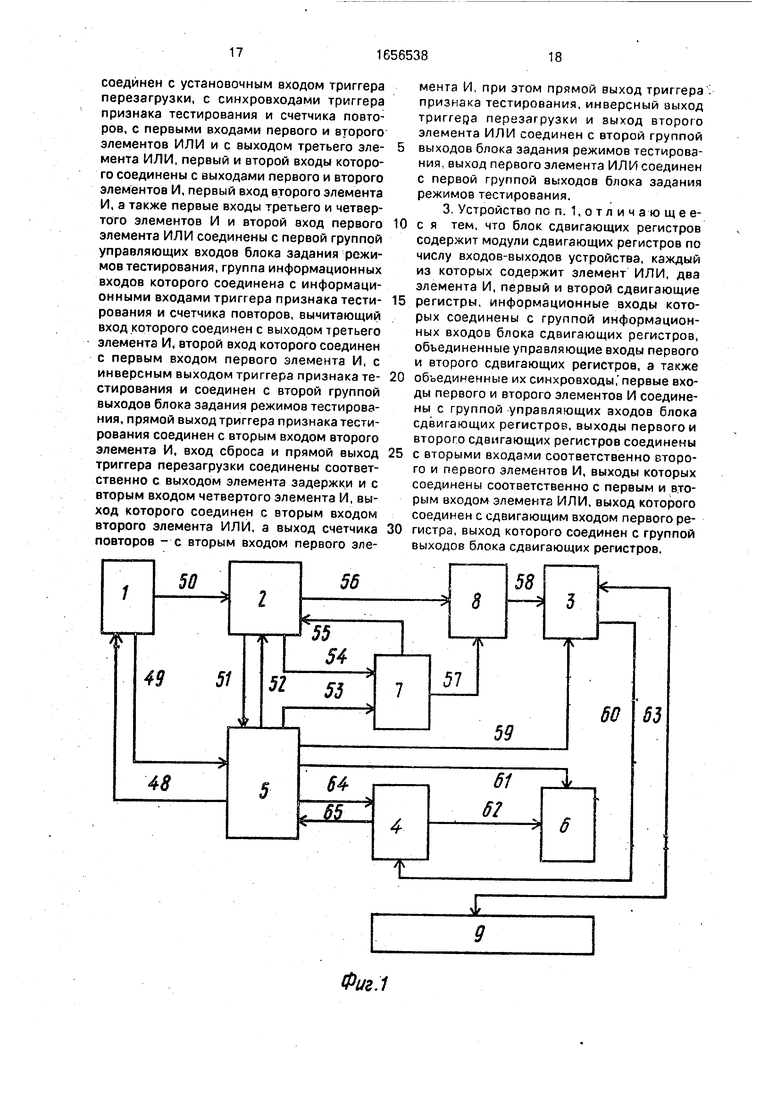

На фиг. 7 приведен пример теста Т для ОК, имеющего два вывода 1 и J. Тест Т соответственно выводам содержит два элементарных теста Ti и Tj, одновременно он состоит из 48 тест-наборов, номера которых обозначены как NTH. Первый тест-на0

5

бор в тесте Т, учитывая порядок следования- выводов 1 и J, имеет вид 11, второй - 01 и т.д. Тест Т записан 9-разрядными тестовыми словами. Каждый 9-й (младший) разряд тестовых слов содержит признак упаковки слова. Если признак равен 1, тс тестовое слово имеет позиционную форму упаковки, в противном случае - сжатую форму упаковки. На фиг. 7 а все слова теста Т содержат только позиционную форму упаковки. На фиг. 7 б слова теста Т записаны как в сжатой, так и в позиционной форме. Для упрощения форма записи теста Т на фиг. 7 б названа как сжатая несмотря на то, что он содержит слова в двух формах записи. При позиционной форме записи тестовых слов все разряды с 1-го по 8-й содержат тест-наборы, при сжатой - разряды с 5-го по 8-й включительно содержат число повторов кода, записанного в старших разрядах с 1-го по 4-й

При сжатой форме теста Т (фиг. 7 б) элементарный тест TI состоит из четырех слов, при этом тест наборы с 1-го по 8-й и с 29-го по 36-й записаны в позиционной форме, остальные тест-наборы в сжатой форме. Так, тест-наборы с 9-грпо 28-й записаны в виде пятикратного ОНИ) повторения кода 1011, тест-наборы с 37-го по 48-й в виде трехкратногО| 00 1 гповторения кода 0000. Элементарный тест Tj состоит из двух слов, при этом тест-наборы с 1-го по 40-й записаны в виде десятикратного 1010 повторения кода 1111. а наборы с 41-го по 48-й в позиционной форме.

При позиционной форме упаковки теста числа (s + 1) разрядных ячеек ОЗУ 10, необходимых для записи элементарного теста Ti, равно

п

m -, s

где п - число тест-наборов.

При сжатой форме упаковки аналогичное число равно

m П . s

Для элементарного теста Ti, приведенного на фиг. 7, s 8; п 48; m 6; m 4.

Старшая половина разрядов тестового слова из ОЗУ 10 поступает на информационные входы сдвигающего регистра 43 блока 8, младшая половина разрядов поступают на информационные входы сдвигающего регистра 44 блока 8 и счетчика 32 повторов блока 7, младший (s + 1)-й разряд поступает 5 на информационный вход триггера ЗЗ признака тестирования блока 7.

Счетчик 11 адреса служит для формирования адресов ячеек ОЗУ 10.

Элемент 12 задержки предназначен для формирования временного интервала меж0

5

0

5

0

5

0

ду записью-считыванием информации из ОЗУ 10 и увеличением кода в счетчике 11 адреса.

Триггеры 14 входа-выхода осуществляют разделение считываемой тестовой информации из блока 8 на стимулы и эталоны и идентифицируют выводы ОК 9 на входы и выходы.

Входные ключи 15 предназначены для передачи реакций с выходов ОК 9 на входы блока 4 сравнения.

Выходные ключи 16 предназначены для передачи стимулов на входы Т ОК 9.

Дешифратор 19 блока 5 управления предназначен для формирования команд управления в блоки 2, 3, счетчик 20, распределитель 26, формирователь 31 запуска.

Счетчик 20 тест-наборов осуществляет подсчет тест-наборов в режиме тестирования и тестовых слов в режиме записи.

Схема 21 сравнения сравнивает содержимое счетчика 20 тест-наборов и регистра 23 числа тест-наборов, куда заносится либо номер последнего тест-набора (режим тестирования), либо номер последнего тестового слова (режим записи).

Управляемый генератор 22 предназначен для формирования одиночных импульсов в режиме записи, поступающих на распределитель 26, и серии тактовых импульсов в режиме тестирования, поступающих на входы делителей 27, 28 частоты, на счетчик 20 и входы блока 4 сравнения, блока 7 задания режимов тестирования.

Регистр 24 режима работы устройства предназначен для приема кода режима работы от блока 1 ввода информации. Код режима управляет дешифратором 19.

В регистр 25 адреса канала из блока 1 заносится позиционный код вывода ОК. Число разрядов регистра 25 равно числу каналов устройства.

Распределитель 26 предназначен для формирования в режиме записи одиночных импульсов в блок 2 буферной памяти, в блок 7 задания режимов тестирования, в коммутатор 3.

Первый и второй делитель 27, 28 частоты предназначен для формирования сигналов соответственно с частотами f/s и 2f/s в режиме тестирования, где f - частота выдачи стимулов на ОК.

Группа 29 переключателей коммутирует импульсы в режиме записи в соответствии с содержимым регистра 25 адреса канала. Число переключателей 29 равно числу каналов устройства. Выход каждого переключателя 29 соединен с входами соответствующих субблоков 21 (ОЗУ 101) блока 2, ячейки 31 (триггер 141) коммутатора 3, узлы 71 (схема

ИЛИ 401) блока 7 задания режимов тестирования.

Кнопка 30 пуска формирует команду Пуск устройства.

Формирователь 31 запуска предназначен для запуска блока 1 на ввод информации. Счетчик 32 повторов блока 7 предназначен для приема служебной части (кода числа повторов) из ОЗУ 10 блока 2 при сжатой

0 форме упаковки теста.

Триггер 33 признака тестирования является триггером D-типа, предназначен для приема (s + 1)-го младшего разряда (признака упаковки) из ОЗУ 10 блока 2, осуществля5 ет управление в блоках 7 и 8 организацией тестирования при позиционной и сжатой формах упаковки теста.

Триггер 34 перезагрузки является триггером RS-типа, управляет режимом работы

0 сдвигающих регистров 43, 44 в блоке 8.

Нулевое состояние триггера 34 соответствует режиму параллельной записи, единичное состояние - режиму сдвига.

Элемент 35 задержки предназначен

5 для формирования временного интервала, во время которого происходит параллельная запись тестового слова в сдвигающие регистры 43, 44, счетчик 32 повторов и триггер 33. Регистры 43, 44 блока 8 представляют

0 сдвиговые регистры с параллельной записью информации, предназначены для приема тестовой информации из ОЗУ 10 и выдачи ее в коммутатор 3.

Устройство работает следующим образом.

5При включении питания триггеры 14

входов-выходов в ячейках коммутации блока 3 устанавливаются в исходное (нулевое) состояние, триггеры 33 признака тестирования и триггеры 34 перезагрузки в узлах 71

0 блока 7 задания режимов тестирования - в единичное состояние, первый 27 и второй 28 делители частоты в состояние 11...1. Установочные входы не показаны. При нажатии кнопки 30 в блоке 5 управления сигналом с

5 выхода формирователя 31 запуска по линии связи 48 запускается блок 1 ввода информации, В регистр 24 режима блока 5 по группе связей 49 поступает код, при котором сигнал с выхода дешифратора 19 поступает по

0 группе связей 52 на входы управления всех ОЗУ 10 блока 2 буферной памяти и устанавливает их в режим записи. Этим же сигналом с дешифратора 19 в распределителе 26 устанавливается прямая связь между его

5 выходами и выходом управляемого генератора 22, разрешается работы счетчика 20, формирователя 31 и через линию связи 59 входные ключи 15, выходные ключи 16 коммутатора 3 устанавливаются в вы- сокоимпедансное (третье) состояние, что

обеспечивает развязку OK и устройства во время режима записи. Продолжающая поступать из блока 1 информация через группу связей 49 обнуляет счетчик 20 тест-наборов и регистры 23, 25, а через группу связей 50 обнуляет счетчики 11 адреса всех субблоков блока 2 буферной памяти. Затем из блока 1 по группе связей 49 в соответствующий разряд регистра 25 адреса заносится единица. По единичному состоянию этого разряда замыкается соответствующий переключатель 29 из группы переключателей 29, а в регистр 23 заносится номер последнего загружаемого тестового слова, соответствующего заданному в регистре 25 каналу, следовательно и субблоку 21 в блоке 2 памяти. После этого от блока 1 по группе связей 49 запускается управляемый генератор 22. Импульс с генератора 22 увеличивает содержимое счетчика 20 тест-наборов на единицу, а через распределитель 26 поступает одновременно на все входы группы переключателей 29. Этот импульс через переключатель 29i подготовленный содержимым регистра 25 через группу связей 42 поступает на синхровход ОЗУ 101 блока 2. К этому моменту по информационной шине группы связей 50 с блока 1 выставлено первое тестовое слово, которое заносится в ОЗУ 10 по нулевому адресу счетчиков 11. Одновременно с переключателями 29 импульс с генератора 22 поступает по группе связей 53 на элементы ИЛИ 40 блока 7, а с их выходов по группе связей 55 - на элементы 12 задержек блока 2. Импульсы с выходов элементов 12 задержек увеличивают содержимое счетчиков 11 адреса на единицу и одновременно через элемент ИЛИ 13 блока 2 по линии связи 51 поступает пусковой сигнал в блок 5 управления на формирователь 31 запуска. Снова с выхода формирователя 31 запуска по линии связи 48 в блок 1 поступает пусковой сигнал, по которому на информационной шине группы связей 50 выставляется очередное второе тестовое слово, а. по группе связей 49 от блока 1 запускается управляемый генератор 22. Вторым импульсом с управляемого генератора 22 блока 5 это слово запишется в ОЗУ 101 субблока 21 по очередному адресу и т.д. Запись информации в субблок 21 блока 2 буферной памяти продолжается до тех пор, пока состояние счетчика 20 тест-наборов не станет равно содержимому регистра 23. В случае равенства на выходе схемы 21 сравнения блока 5 появится импульс, который запретит работу генератора 22 и установит счетчик 20, регистр 25 и регистр 23 в нулевое состояние. Далее в регистр 25 от блока 1 заносится

адрес очередного канала, а в регистр 23 -. номер последнего загружаемого тестового слова в субблок блока 2 выбранного канала. Загрузка очередного субблока блока 2 происходит аналогично предыдущему и т.д., пока не загрузятся все необходимые для данного ОК субблоки блока 2 буферной памяти. После загрузки блока 2 тестом в регистр 24 блока 5 от блока 1 по группе

связей 49 запишется код, который через дешифратор 19 и линию связи 59 подтверждает высокоимпедансное состояние ключей 16, 15 коммутатора 2. Тем же сигналом с дешифратора 19 распределитель 26 переводится в режим последовательного обегания, а выход управляемого генератора 22 соединяется с входом первой ячейки распределителя. Одновременно сигнал с выхода дешифратора 19 запрещает работу счетчика

20. Затем из блока 1 ввода информации в регистр 25 блока 5 управления записывается информация о том, какие триггеры 14 коммутатора 3 должны быть установлены в единичное состояние. Тем самым

включаются соответствующие переключатели 29i из группы 29. В дальнейшем от блока 1 запускается управляемый генератор 22. Каждый очередной импульс с генератора 22 поступает на распределитель 26 и появляется на его очередном выходе. Этот импульс по группе связей 59 поступит или не поступит в данную ячейку 3i на установочный вход триггера 141 в зависимости от того, включен или выключен соответствующий

переключатель 291, состояние которого определяется информацией регистра 25 адреса канала. Запись информации в коммутатор 3 прекращается после появления сигнала на последнем выходе распределителя 26, этим сигналом запрещается работа управляемого генератора 22.

В ячейках 31 коммутации, где триггер 141 установлен в единичное состояние сигналов с его прямого выхода, элемент И 17 и выходной ключ 161 подготовлены к пропуску двоичной последовательности (стимулов) на вход ОК 9 с выхода соответствующего сдвигающего регистра 431 блока 8. Сигналом с инверсного выхода того же триггера 141 закрыты

второй элемент И 181 и входной ключ 151.

Во всех других ячейках коммутатора 3, где триггер 14j установлен в нулевое состояние, наоборот, подготовлены к пропуску двоичных последовательностей элемент И 18j и входной ключ 15j. Первая из них пропускает эталоны теста с выхода соответствующего сдвигающего регистра 43J блока 8, а второй - реакции с выхода ОК 9 на входы соответствующей схемы сравнения (не показаны) блока 4. Элемент И 17J и выходной ключ 16 закрыты.

Необходимо еще раз отметить, что в режиме записи информации все ключи 15 и 16 коммутатора 3 закрыты, а точнее находятся в высокоимпедансном состоянии, которое определяется кодом регистра 24 и сигналом с дешифратора 19.

После загрузки ОЗУ 10 блока 2 и триггеров 14 коммутатора 3 в регистр 24 режима от блока 1 ввода информации поступает код, определяющий режим тестирования ОК. Этот код через дешифратор 19, группу связей 52 устанавливает все ОЗУ 10 блока 2 сигналов на их входах управления в режим чтения. Этим же сигналом с дешифратора 19 запрещается работа распределителя 26. а на выходах ключей 29 устанавливается сигнал высокого уровня, который поступает по группе связей 52 на синхровходы всех ОЗУ 10. Тем же кодом регистра 24 запрещается работа формирователя 31 запуска, разрешается работа счетчика 20, и по группе связей 59 снимается высокоимпедансное состояние ключей 15, 16 коммутатора 3.

Далее по команде от блока 1 обнуляются счетчик 20 тест-наборов в блоке 5 управления и счетчики 11 адреса в субблоках блока 2 буферной памяти, а в регистр 23 числа тест-наборов с того же блока 1 заносится номер последнего тест-набора. После этого от блока 1 ввода информации по группе связей 49 запускается управляемый генератор 22 блока 5, который формирует импульсы с частотой тестирования ОК. равной f. По переднему фронту первого импульса с генератора 22 на выходе делителя 27 (учитывая его исходное состояние) формирует импульс, длительность которого меньше периода Т 1/f. Этот импульс по линии связи 53 поступает во все узлы блока 7 и через элемент И 38 (подготовленные исходным состоянием триггеров 33), через элемент ИЛИ 42 поступает на входы триггеров 34 перезагрузки, элементов 35 задержки, элементов ИЛИ 40. 41.

Работа устройства описывается на примере одного канала. Положительным сигналом с инверсного выхода триггера 34 блока 7, сброшенного сигналом с элемента ИЛИ 42, через группу связей 57 сдвигающие регистры 43, 44 блока 8 устанавливаются в режим параллельный записи старших s разрядов тестового слова из ОЗУ 10 блока 2. размещенного в ячейке с нулевым адресом, поступающего на регистры 43. 44 по группе связей 56. По импульсу с элемента ИЛИ 41 блока 7, подаваемому через связи 57 на синхровходы регистров 43, 44. производится запись в них указанного тестового слова.

При этом половина старших разрядов слова из s записывается в регистр 43, а половина младших разрядов в регистр 44. Одновременно половина младших разрядов и (s +

1)-й младший разряд того же тестового слова, поступающий по группе связей 54 из блока 2 в блок 7, записывается соответственно в счетчик 32 и триггер 33 по импульсу, поданному на их синхровходы со схемы

0 ИЛИ 42. Одновременно с импульсами с элемента ИЛИ 41, 42 поступает импульс на элемент 12 задержки с выхода элемента ИЛИ 40. После записи первого тестового слова из нулевой ячейки ОЗУ 10 блока 2 в регист5 ры 43, 44. тестовый счетчик 32 и триггер 33 импульс с выхода элемента 12 задержки увеличивает содержимое счетчика 11 адреса на единицу. Этот же импульс, достигнув через элемент ИЛИ 13 формирователя 31

0 запуска, не меняет состояние последнего, так как он заблокирован кодом регистра 24 режима через дешифратор 19. Одновременно с изменением состояния счетчика 11 адреса блока 2 устанавливается в единичное

5 состояние триггер 34 блока 7. Это происходит по приходу на этот триггер импульса с выхода элемента 35 задержки. Единичное состояние триггера 34 задает регистрам 43, 44 блока 8 режим сдвига и подготавливает

0 элемент И 36 к приему тактовых импульсов с генератора 22 блока 5.

Дальнейшая работа устройства зависит от информации, считанной из ОЗУ 10 блока 2. При позиционной форме упаковки

5 теста в триггер 33 признака тестирования записывается единица. Единичным состоянием триггера 33 подготавливается элемент И 38. Кроме того, единичный сигнал триггера 33 через группу связей 57 поступает в

0 блок 8 на элемент И 47, посредством которой через элемент ИЛИ 45 из регистров 43, 44 образуется один сдвиговый регистр, число разрядов которого равно s. Тактовые импульсы (включая первый) с частотой

5 тестирования f с генератора 22 блока 5 управления по группе связей 53 поступают в блок 7 на подготовленный элемент И 36, с выхода которого через элемент ИЛИ 41 они поступают на синхровходы регистров 43, 44

0 блока 8 по группе связей 57. С этого момента начинается рабочий цикл проверки ОК. Записанное тестовое слово с выхода регистра 43 в последовательном коде по группе связей 58 поступает в коммутатор 3 на вхо5 ды элементов И 17, 18. При этом с первым тактовым импульсом генератора 22 в коммутатор 3 поступает старший (1-й) разряд тестового слова, с вторым импульсом 2-й разряд ... с s-ым импульсом s-й (младший) разряд, т.е. из регистра 43 тестовое слово

проталкивается головою вперед, В за висимости от того, какая информация записана в триггера 141 данной ячейки 3i коммутации, тестовое слово поступает либо через элемент И 171 и выходной ключ 161 на 1-й вывод ОК 9, являющийся выходом ОК, либо через элемент И 181 по группе связей 60 в блок 4 сравнения, если 1-й вывод (Заявляется выходом. По переднему фронту (i + 1)-го импульса генератора 22, когда первое тестовое слово из регистров 43, 44 уже полностью передано в коммутатор 3, с делителя 27 частоты снова поступает импульс по группе связей 53 в блок 7 на вход элемента И 38. По этому импульсу произойдет запись очередного 2-го тестового слова из ОЗУ 10 блока 2 в регистры 43, 44 блока 8, в счетчик 32 и триггер 33 блока 7. Продолжающие поступать тактовые импульсы с генератора 22 на элемент И 36 блока 7 (включая (s + 1)-й) обеспечивают процесс выдачи теста в коммутатор 3 и т.д.

При позиционной форме упаковки тестового слова сигналом с инверсного выхода триггера 33 через элементы И 39, 37 работа счетчика 32 блокируется.

При позиционной форме упаковки тестового слова частота обращения к ОЗУ 10 в s раз меньше тактовой частоты тестирования f, таким образом в предлагаемом устройстве можно или применять низкочастотные ОЗУ, или по сравнению с аналогами, использующими буферное ОЗУ в качестве непосредственного источника тестовой информации, повысить частоту тестирования в s раз,

При сжатой форме упаковки теста в триггер 33 блока 7 из ОЗУ 10 блока 2 записывается О, в результате чего подготавливаются элементы И 37, 39 и через них счетчик 32 готов к работе, блокируется элемент И 38. Высокий уровень с инверсного выхода триггера 33 через группу связей 57 поступает в блок 8 на элемент И 46, в результате чего последовательный выход регистра 43 блока 8 через элемент И 46 и элемент ИЛИ 45 подключается к своему последовательному входу. Записанный в счетчике 32 блока 7 код означает число повторов теста, записанного в регистре 43. Регистр 44 и записанный в него код (такой же, как в счетчике 32) при сжатой форме упаковки в работе не участвуют, поскольку его выход заблокирован нулевым состоянием триггера 33 блока 7. Тактовые импульсы (включая первый) с генератора 22 блока 5 через элемент И 36 и через элемент ИЛИ 41 блока 7 по группе связей 57 поступают в блок 8 на синхровходы регистра 43, в результате чего записанная в нем тестовая информация в

последовательном коде по группе связей 58 поступает в коммутатор 3,

После каждых s/2 сдвигов в регистре 43 повторяется тест, начально записанный из ОЗУ 10 блока 2, поскольку он закомьцован через элемент И 46 и элемент ИЛИ 45. В эти моменты с второго делителя 28 частоты блока 5 управления по группе связей 53 в блок 7 на подготовленный элемент И 37

поступает импульс, который из счетчика 32 повторов вычитает единицу. Процесс продолжается до тех пор, пока состояние счетчика 32 не станет равным нулю. В этом случае на выходе счетчика 32 формируется

импульс, длительностью меньшей периода Т - 1/f, который проходит через подготовленную схему И 39 и через элемент ИЛИ 42 сбрасывает триггер 34 перезагрузки, подготавливая тем самым регистры 43, 44

блока 8 к записи очередного тестового слова, считанного из ОЗУ 10 блока 2. Этот же импульс поступает на синхровход параллельной записи в счетчик 32 повторов и синхровход триггера 33. Кроме того через

схему ИЛИ 42 этот импульс поступает по группе связей 57 в блок 8 на синхровходы регистров 43, 44, в результате чего соответствующие разряды следующего тестового слова из ОЗУ 10 блока 2 по группе связей 56

записывается в регистры 43, 44 блока 8, по группе связей 54 в счетчик 32 повторов, триггер 33 блока 7. Через элемент ИЛИ 40 по группе связей 55 этот же импульс поступает в блок 2 буферной памяти на элемент

12 задержки, через который в счетчик 11 адреса добавляется единица. Через элемент 35 задержки блока 7 триггер 34 устанавливается в единицу, подготавливая регистры 43. 44 блока 8 к сдвигу записанной

тестовой информации.

Далее снова поступают тактовые импульсы с генератора 22 блока 5 с частотой f на элемент И 36. и процесс выдачи теста продолжается.

При сжатой форме упаковки теста частота обращения к ОЗУ 10 в К Ц- -I раз

меньше частоты тестирования f, где L - число повторов в счетчике 32. Физический смысл сжатая форма записи имеет при L 2, так как в противном случае она эквивалентна по эффективности позиционной форме. Таким образом, минимальное значение К - 3 s/2. Следовательно, по сравнению с аналогичными устройствами, использующими одноразрядные буферные ОЗУ в качестве источника тестовой информации, быстродействие предлагаемого устройства

при сжатой форме записи увеличивается по крайней мере в 3- s/2 раз.

При заданном объеме m ячеек ОЗУ, разрядность которых равна s+1 максимальная длина теста при позиционной форме записи в предлагаемом устройстве равна п m -s.

При сжатой форме упаковки теста во всех ячейках ОЗУ максимальная длина теста равна п т- 2 . Таким образом, при сжатой форме значительно экономичнее используется память ОЗУ.

Импульсы с управляемого генератора 22 блока 5 управления помимо блока 7 задания режимов тестирования поступают в блок 4 сравнения по линии связи 64 и на счетчик 20 тест-наборов. Выдача теста продолжается до тех пор, пока состояние счетчика 20 не станет равно содержимому регистра 23 числа тест-наборов. В этом случае срабатывает схема 21 сравнения, сигнал с которой запретит работу управляемого генератора 22, в результате чего прекратится выдача стимулов на ОК 9. Сигнал со схемы 21 сравнения поступает также в блок 6 вывода информации по линии связи 61, который паспортирует исправное состояние ОК 9. Одновременно импульсы с управляемого генератора 22, поступающие в блок 4 сравнения по линии связи 64, стробируют схемы сравнения блока 4 (не показаны, их количество равно числу выводов ОК), на которые поступают через группу связей 60 с коммутатора 3 эталоны со схем И 18, а также реакции с выходов ОК 9 через входные ключи 15. Ключи 15 подготовлены к включению с инверсных выходов триггеров 14 входов- выходов, находящихся в нулевом состоянии в тех ячейках коммутации 31, которым соответствуют выходы ОК 9. Кроме того, ключи 15 подготовлены сигналом с выхода дешифратора 19 блока 5 по группе связей 59, когда в регистре 24 режима работы устройства записан код тестирования ОК.

Стимулы по группе связей 58 из блока 8 поступают в коммутатор 3 на элемент И 17, которые подготовлены с прямых выходов триггеров 14, находящихся в единичном состоянии в тех ячейках коммутации 31, которым соответствуют входы ОК 9. С выходов элементов И 17 стимулы через выходные ключи 16 поступают на ОК 9 по группе связей 63.

Если эталон не совпадет с реакцией, блок 4 сравнения формирует сигнал, поступающий по линии связи 65 на останов управляемого генератора 22 блока 5, после чего выдача стимулов на ОК 9 прекращается, и результат контроля по группе связей 62 поступает в блок 6 вывода информации.

где паспортируется неисправное состояние ОК 9 и адрес неисправности.

Формула изобретения

1.Устройство для функционального кон- троля цифровых блоков, содержащее блок

ввода информации, блок буферной памяти, коммутатор, блок сравнения, блок управления, блок вывода информации, причем первая и вторая группы выходов блока ввода

0 информации соединены соответственно с группами информационных входов блока буферной памяти и блока управления, первый, второй выходы, а также первая и вторая группы выходов блока управления соедине5 ны соответственно с входом запуска блока ввода информации, с входом конца тестирования блока вывода информации, с группой управляющих входов блока буферной памяти и с первой группой управляющих входов

0 коммутатора, имеющего группу информационных входов-выходов для подключения объекта контроля, причем группа информационных входов блока вывода информации соединена с группой выходов блока сраане5 ния, отличающееся тем, что, с целью повышения быстродействия и экономии объема памяти, в устройство введены блок задания режимов тестирования, блок сдвигающих регистров, причем управляющая и

0 информационная группы входов блока задания режимов тестирования соединены соответственно с третьей группой выходов блока управления и с первой группой выходов блока буферной памяти, выход и вторая

5 группа выходов блока буферной памяти соединены соответственно с входом пуска блока управления и с группой информационных входов блока сдвигающих регистров, первая группа выходов задания режимов

0 тестирования соединена с группой управляющих входов блока буферной памяти, вторая группа выходов блока задания режимов тестирования соединена с группой входов управления блока сдвигающих регистров,

5 группа выходов которого соединена с группой информационных входов коммутатора, вход управления блока сравнения соединен с третьим выходом блока управления, выход блока сравнения соединен с входом остано0 ва блока управления, группа информационных входов блока сравнения соединена с группой выходов коммутатора.

2.Устройство по п. 1,отличающее- с я тем, что блок задания режимов тестиро5 вания включает узлы задания режимов по числу входов-выходов устройства, каждый из которых содержит три элемента ИЛИ, счетчик повторов, триггер признака тестирования, триггер перезагрузки, четыре элемента И и элемент задержки, вход которого

соединен с установочным входом триггера перезагрузки, с синхровходами триггера признака тестирования и счетчика повторов, с первыми входами первого и второго элементов ИЛИ и с выходом третьего эле- мента ИЛИ. первый и второй входы которого соединены с выходами первого и второго элементов И, первый вход второго элемента И, а также первые входы третьего и четвертого элементов И и второй вход первого элемента ИЛИ соединены с первой группой управляющих входов блока задания режимов тестирования, группа информационных входов которого соединена с информационными входами триггера признака тести- рования и счетчика повторов, вычитающий вход которого соединен с выходом третьего элемента И, второй вход которого соединен с первым входом первого элемента И, с инверсным выходом триггера признака те- стирования и соединен с второй группой выходов блока задания режимов тестирования, прямой выход триггера признака тестирования соединен с вторым входом второго элемента И, вход сброса и прямой выход триггера перезагрузки соединены соответственно с выходом элемента задержки и с вторым входом четвертого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, а выход счетчика повторов - с вторым входом первого элемента И. при этом прямой выход триггера признака тестирования, инверсный выход триггера перезагрузки и выход второго элемента ИЛИ соединен с второй группой выходов блока задания режимов тестирования, выход первого элемента ИЛИ соединен с первой группой выходов блока задания режимов тестирования,

3. Устройство по п. 1, о т л и ч а ю щ е е- с я тем, что блок сдвигающих регистров содержит модули сдвигающих регистров по числу входов-выходов устройства, каждый из которых содержит элемент ИЛИ, два элемента И, первый и второй сдвигающие регистры, информационные входы которых соединены с группой информационных входов блока сдвигающих регистров, объединенные управляющие входы первого и второго сдвигающих регистров, а также объединенные их синхровходы, первые входы первого и второю элементов И соединены с группой управляющих входов блока сдвигающих регистров, выходы первого и второго сдвигающих регистров соединены с вторыми входами соответственно второго и первого элементов И, выходы которых соединены соответственно с первым и вторым входом элемента ИЛИ, выход которого соединен с сдвигающим входом первого регистра, выход которого соединен с группой выходов блока сдвигающих регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для контроля цифровых интегральных схем | 1978 |

|

SU943747A1 |

| Многоканальное устройство для контроля систем управления | 1985 |

|

SU1345200A1 |

| Устройство для тестового контроля цифровых узлов | 1980 |

|

SU918949A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1386999A1 |

Изобретение относится к цифровой вычислительной технике и может быть исполь- зовано для контроля быстродействующих цифровых логических блоков. Целью изобретения является повышение быстродействия тестирования и экономия объема памяти устройства за счет использования сжатой формы упаковки теста. Устройство содержит блок ввода информации, блок управления, блок буферной памяти, коммутатор, блок сравнения, блок вывода информации, блок задания режимов тестирования, блок сдвигающих регистров. 2 з.п. ф-лы, 7 ил.

Фиг.1

ffl

M

Фиг. 5

1

I

« 9

i I

16 П

I

U 15

I I

И 33

I I

liO 4/ I I

US

I II II II II II I

IOIIOIII QJlOl IIOIIQ I0IIIOI101011 lOOflffll I WOOMftOOOOOOOO®

iilii|il T llllllll i llimilQ IIIIMII llllllll(Qlll0l IIQ а Позиционная po/var ynoxobni mec/na

NTH 189 26 Z9 36 31 48

r IIIIIIII

r loiioni i1ion|oio11lo|ioooiiig ilogflo|jpinia

NTH 1 W 4f 48

Ttj иирщйпюппР

TI, fy -тест, счответстбенно, для 1-го, Zf-zo выводов

(J - признан упаковки

| -служебная vac/ль /пес/пового слаба при сжат

форме упаковки

ФигЛ

Фиг. 6

(1

U 15

I I

И 33

I I

liO 4/ I I

US

II II II I

I101011 lOOflffll I WOOMftOOOOOOOO®

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для функционального контроля цифровых блоков | 1983 |

|

SU1196875A1 |

Авторы

Даты

1991-06-15—Публикация

1989-02-22—Подача