Предлагаемое изобретение относится к области техники связи и может быть использовано в телемеханике, телеметрии, при передаче данных по каналам связи кодами различной корректирующей способности, что отвечает выполнению различных требований по уровням достоверности передачи сообщений от различных источников.

Известна система для передачи и приема информации кодом переменной длины (см. авт. свид. СССР N 824464, М. кл. 3 H 04 J 3/16, H 04 L 5/22, опубликованное в офиц. бюлл. ОИПОТЭ N 15 от 23.04.81), содержащая на передающей стороне формирователь сигналов, элемент И, элемент ИЛИ, распределитель, шифратор, блок кодирования, блок управления, генератор тактовых импульсов, блок согласования, при этом входы формирователей сигналов являются входами системы, выходы формирователей сигналов соединены с первыми входами элементов И, выходы распределителя соединены с входами шифратора, блока управления и со вторыми входами элементов И, выходы которых соединены со входами элемента ИЛИ, выход которого соединен с информационным входом блока кодирования, выход генератора тактовых импульсов соединен с тактовыми входами блока управления и блока кодирования, выходы шифратора соединены с группой управляющих входов блока кодирования, первый выход блока управления соединен с управляющим входом распределителя и с первым управляющим входом блока кодирования, второй выход блока управления соединен со вторым управляющим входом блока кодирования, выход которого соединен с входом согласующего блока, выход которого соединен с входом канала связи, а на приемной стороне - согласующий блок, блок управления, распределитель, элементы И, блоки декодирования, решающий блок, при этом выход канала связи соединен с входом согласующего блока, информационный выход которого соединен с информационным входом решающего блока и первыми входами элементов И, тактовый выход согласующего блока соединен с тактовыми входами блока управления, решающего блока и блоков декодирования, выходы распределителя соединены со входами блока управления, с группой управляющих входов решающего блока и вторыми входами элементов И, выходы которых соединены с соответствующими группами входов решающего блока, выход блока управления соединен с управляющим входом распределителя и управляющим входом решающего блока, выходы которого являются выходами системы.

Недостатком данной системы является то, что она не обеспечивает адаптации к изменяющимся характеристикам канала связи, а также может быть применена только при циклическом режиме передачи информации.

Признаками аналога, совпадающими с признаками заявляемого технического решения, на передающей стороне являются шифратор полинома, блок кодирования, генератор тактовых импульсов, блок согласования а на приемной стороне - блок согласования, элементы И, декодирующие блоки, решающий блок.

Причины, препятствующие достижению требуемого технического результата, состоят в особенностях реализации известной системы, не позволяющих изменять корректирующую способность и длину кода в зависимости от состояния канала, а также обеспечить в спорадическом режиме синхронную работу передающего и приемного устройств и определить номер источника, передающего сообщение.

Известна система передачи и приема информации кодом переменной длины (см. авт. свид. СССР N 1124436, М. кл. 3 H 04 L 1/10, опубликованное в офиц. бюлл. БИ N 42 от 15.11.84), содержащая на передающей стороне преобразователи кода, элементы И, распределитель сигналов, элемент ИЛИ, кодирующий блок, генератор тактовых импульсов, перестраиваемый распределитель, блок оценки состояния канала связи, шифратор полиномов, блок генераторов частот, дешифратор сигналов управления, блок преобразования сигналов, при этом входы преобразователей кода являются входами системы, выходы преобразователей кода соединены с первыми входами элементов И, выходы распределителя соединены со вторыми входами элементов И, выходы которых соединены с входами элемента ИЛИ, выход которого соединен с информационным входом кодирующего блока, выход генератора тактовых импульсов соединен с тактовыми входами перестраиваемого распределителя и кодирующего блока, первый выход перестраиваемого распределителя соединен с входами блока оценки состояния канала, распределителя и первым управляющим входом кодирующего блока, второй выход перестраиваемого распределителя соединен с вторым управляющим входом кодирующего блока, выходы блока оценки состояния канала связи соединены с входами перестраиваемого распределителя, блока генераторов частот и шифратора полиномов, выходы которого соединены с группой управляющих входов кодирующего блока, выход которого соединен с первым входом блока преобразования сигналов, второй вход которого соединен с выходом обратного канала, выход блока генератора частот соединен с третьим входом блока преобразования сигналов, первый выход которого соединен с входом прямого канала, второй выход блока преобразования сигналов соединен с входом дешифратора сигналов управления, выходы которого соединены с входами блока оценки состояния канала, а на приемной стороне - блок преобразования сигналов, дешифратор номера кода, элементы И, декодеры, перестраиваемый распределитель, распределитель приема, блок выдачи данных, формирователь сигналов управления, при этом выход прямого канала соединен с первым входом блока преобразования сигналов, первый выход которого соединен с входом обратного канала, второй выход блока преобразования сигналов соединен с информационным входом блока выдачи данных и первыми входами элементов И, третий выход блока преобразования сигналов соединен с тактовыми входами перестраиваемого распределителя, блока выдачи данных и декодеров, группа выходов блока преобразования сигналов соединена с входами дешифратора номера кода, выходы которого соединены с входами перестраиваемого распределителя и вторыми входами элементов И, выходы которых соединены с информационными входами декодеров, группы выходов которых соединены с соответствующими группами входов блока выдачи данных и формирователя сигнала управления, выход которого соединен с вторым входом блока преобразования сигналов, выход перестраиваемого распределителя соединен с управляющим входом блока выдачи данных и входом распределителя приема, выходы которого соединены с группой управляющих входов блока выдачи данных, выходы которого являются выходами системы.

Однако в данной системе при выборе кодов не учитываются различные требования к верности передачи сообщений от различных источников, кроме того затруднено применение системы при наиболее экономичном спорадическом режиме передачи информации.

Признаками аналога, совпадающими с признаками заявляемого технического решения, на передающей стороне являются блок оценки состояния канала, генератор тактовых импульсов, перестраиваемый распределитель шифратор полинома, блок кодирования, блок генераторов частот, блок преобразования сигналов, а на приемной стороне - блок преобразования сигналов, дешифратор номера кода, перестраиваемый распределитель, элементы И, декодирующие блоки, блок выдачи данных.

Причины, препятствующие достижению требуемого технического результата, состоят в особенностях реализации известной системы, не позволяющих изменить корректирующую способность и длину кода в зависимости от важности передаваемого сообщения, а также обеспечить в спорадическом режиме синхронную работу передающего и приемного устройств и определить номер источника, передающего сообщение.

Наиболее близкой к предлагаемой по совокупности функциональных и конструктивных признаков является адаптивная система передачи информации (см. авт. свид. СССР N 1109927, М. кл. 3 H 04 L 5/22, опубликованное в офиц. бюлл. БИ N 31 от 23.08.84), содержащая на передающей стороне формирователя сигналов, элементы И, элемент ИЛИ, распределитель сигналов, блок оценки состояний канала, блок кодирования, перестраиваемый распределитель, генератор тактовой частоты, шифратор, блок генераторов частот, согласующий блок, при этом входы формирователей сигналов являются входами системы, выходы формирователей сигналов соединены с первыми входами элементов И, выходы распределителя соединены с входами блока оценки состояний канала и вторыми входами элементов И, выходы которых соединены с входами элемента ИЛИ, выход которого соединен с информационным входом блока кодирования, выход генератора тактовой частоты соединен с тактовыми входами перестраиваемого распределителя и блока кодирования, выходы блока оценки состояний канала соединены с входами блока генераторов частот, перестраиваемого распределителя и шифратора, выходы которого соединены с группой управляющих входов блока кодирования, первый выход перестраиваемого распределителя соединен с входом распределителя сигналов и первым управляющим входом блока кодирования, второй выход перестраиваемого распределителя соединен с вторым управляющим входом блока кодирования, выход которого соединен с первым входом согласующего блока, выход блока генераторов частот соединен с вторым входом согласующего блока, выход которого соединен с входом канала связи, а на приемной стороне - согласующий блок, дешифратор, элементы И, блок выдачи данных, перестраиваемый распределитель, декодирующие блоки, распределитель сигналов, при этом выход канала связи соединен с входом согласующего блока, информационный выход которого соединен с информационным входом блока выдачи данных и первыми входами элементов И, тактовый выход согласующего блока соединен с тактовыми входами блока выдачи данных, перестраиваемого распределителя и декодирующих блоков, управляющие выходы согласующего блока соединены с входами дешифратора, выходы которого соединены с входами перестраиваемого распределителя и вторыми входами элементов И, выходы которых соединены с информационными входами декодирующих блоков, группы выходов которых соединены с соответствующими группами входов блока выдачи данных, выход перестраиваемого распределителя соединен с управляющим входом блока выдачи данных и входом распределителя, выходы которого соединены с группой управляющих входов блока выдачи данных, выходы которого являются выходами системы.

В данной системе при выборе корректирующей способности кода учитываются как важность передаваемого сообщения, так и помеховая обстановка в канале.

Однако известная система не может быть применена при наиболее эффективном с точки зрения использования канала спорадическом режиме передачи информации, при котором сообщения передаются в канал по мере возникновения, что является существенным недостатком системы.

Признаками аналога, совпадающими с признаками заявляемого технического решения, на передающей стороне являются блок оценки состояния канала, генератор тактовых импульсов, перестраиваемый распределитель, шифратор полинома, блок кодирования, блок генераторов частот, блок согласования, а на приемной стороне - блок согласования, дешифратор, перестраиваемый распределитель, элементы И, декодирующие блоки, блок выдачи данных.

Причины, препятствующие достижению требуемого технического результата, состоят в особенностях реализации известной системы, не позволяющих обеспечить в спорадическом режиме синхронную работу передающего и приемного устройств и определить номер источника, передающего сообщение.

Задача, на решение которой направлено предлагаемое изобретение, заключается в повышении эффективности использования канала связи за счет уменьшения времени, затрачиваемого на передачу сообщений.

Технический результат от применения предлагаемого изобретения заключается в уменьшении коэффициента использования канала связи за счет перехода от циклического к спорадическому режиму передачи информации от источников кодами переменной длины. Это позволяет увеличить количество пользователей (источников и получателей сообщений), передающих информацию по выделенному каналу.

Для достижения технического результата в систему для передачи и приема информации кодом переменной длины, содержащую на передающей стороне коммутатор, блок оценки состояний канала, блок кодирования, перестраиваемый распределитель, генератор тактовых импульсов, шифратор полинома, блок генераторов частот, блок согласования, при этом группа информационных входов коммутатора является группой информационных входов системы, информационный выход коммутатора соединен с первым информационным входом блока кодирования, выход генератора тактовых импульсов соединен с тактовыми входами перестраиваемого распределителя и блока кодирования, группа управляющих выходов блока оценки состояний канала соединена с группой управляющих входов блока генераторов частот, перестраиваемого распределителя и шифратора полинома, группа управляющих выходов которого соединена с группой управляющих входов блока кодирования, первый управляющий выход перестраиваемого распределителя соединен с первым управляющим входом блока кодирования, второй управляющий выход перестраиваемого распределителя соединен с вторым управляющим входом блока кодирования, информационный выход которого соединен с первым информационным входом блока согласования, управляющий выход блока генераторов частот соединен с управляющим входом блока согласования, канальный выход которого соединен с входом канала связи, а на приемной стороне - блок согласования, дешифратор частот, элементы И, блок выдачи данных, перестраиваемый распределитель, декодирующие блоки, при этом выход канала связи соединен с канальными входами дешифратора частот и блока согласования, информационный выход которого соединен с первыми входами элементов И, группа управляющих выходов дешифратора частот соединена с группой управляющих входов перестраиваемого распределителя и вторыми входами элементов И, выходы которых соединены с информационными входами декодирующих блоков, выходы первой группы управляющих выходов перестраиваемого распределителя соединены соответственно с первыми управляющими входами декодирующих блоков, выходы второй группы управляющих выходов перестраиваемого распределителя соединены соответственно с вторыми управляющими входами декодирующих блоков, управляющий выход перестраиваемого распределителя соединен с управляющим входом дешифратора частот и третьими управляющими входами декодирующих блоков, первые группы информационных выходов которых соединены с соответствующими группами информационных блоков блока выдачи данных, группы информационных выходов которого являются группами информационных выходов системы, дополнительно введены на передающей стороне пусконачинающий блок, формирователь адреса и формирователь синхросигнала, при этом группа управляющих входов пусконачинающего блока является группой управляющих входов системы, а группа управляющих выходов коммутатора - группой управляющих выходов системы, группа управляющих выходов пусконачинающего блока соединена с группами управляющих входов блока оценки состояний канала, коммутатора и первой группой управляющих входов формирователя адреса, информационный выход которого соединен с вторым информационным входом блока кодирования, первый и второй управляющие входы коммутатора соединены соответственно с третьим и вторым управляющим выходами перестраиваемого распределителя, управляющие выход и вход пусконачинающего блока соединены соответственно с управляющим входом и первым выходом перестраиваемого распределителя, группа управляющих выходов которого соединена с второй группой управляющих входов формирователя адреса, четвертый и пятый управляющие выходы перестраиваемого распределителя соединены соответственно с первым и вторым управляющими входами формирователя синхросигнала, информационный выход которого соединен с вторым информационным входом блока согласования, а на приемной стороне - селектор синхросигнала, блок генератора тактовых импульсов, дешифратор адреса, при этом информационный вход селектора синхросигнала соединен с информационным выходом блока согласования, управляющий выход селектора синхросигнала соединен с управляющим входом перестраиваемого распределителя и первым управляющим входом блока генератора тактовых импульсов, второй управляющий вход которого соединен с управляющим выходом перестраиваемого распределителя, выход блока генератора тактовых импульсов соединен с тактовыми входами перестраиваемого распределителя и декодирующих блоков, вторые группы информационных выходов декодирующих блоков соединены с соответствующими группами информационных входов дешифратора адреса, управляющие выходы декодирующих блоков соединены с соответствующими входами группы управляющих входов дешифратора адреса, группа управляющих выходов которого соединена с группой управляющих входов блока выдачи данных.

Наличие причинно-следственной связи между техническим результатом и признаками заявляемого изобретения доказывается следующими логическими посылками.

Наиболее дорогой частью всякой системы передачи информации является канал связи, поэтому эффективность системы определяется в первую очередь эффективностью использования канала. Наиболее эффективное использование канала имеет место при спорадическом режиме передачи информации, когда источники не опрашиваются циклически, а сообщения передаются в канал связи и по мере их возникновения. В этом случае в систему необходимо ввести на передающей стороне пусконачинающий узел, который обеспечивал бы запуск системы при возникновении сообщений, а также был арбитром при одновременном возникновении сообщений от нескольких источников. Кроме того, для обеспечения синхронной работы передающего и приемного устройств системы необходимо на передающей стороне ввести формирователь синхросигнала, а на приемной стороне - селектор синхросигнала, а также генератор тактовых импульсов, работающий в стартстопном режиме. Наконец, для идентификации источников и получателей сообщений в систему необходимо ввести формирователь адреса источника (на передающей стороне) и дешифратор адреса (на приемной стороне).

В дальнейшем для определенности будем считать, что в качестве синхросигнала используется импульс, длительность которого в U раз превышает длительность элементарного сигнала; применяется последовательный режим декодирования по синдрому корректирующего кода (см. Дмитриев В.И. Прикладная теория информации. - М.: Высшая школа, 1989), при котором время декодирования составляет 2N тактов, где N - длина кода.

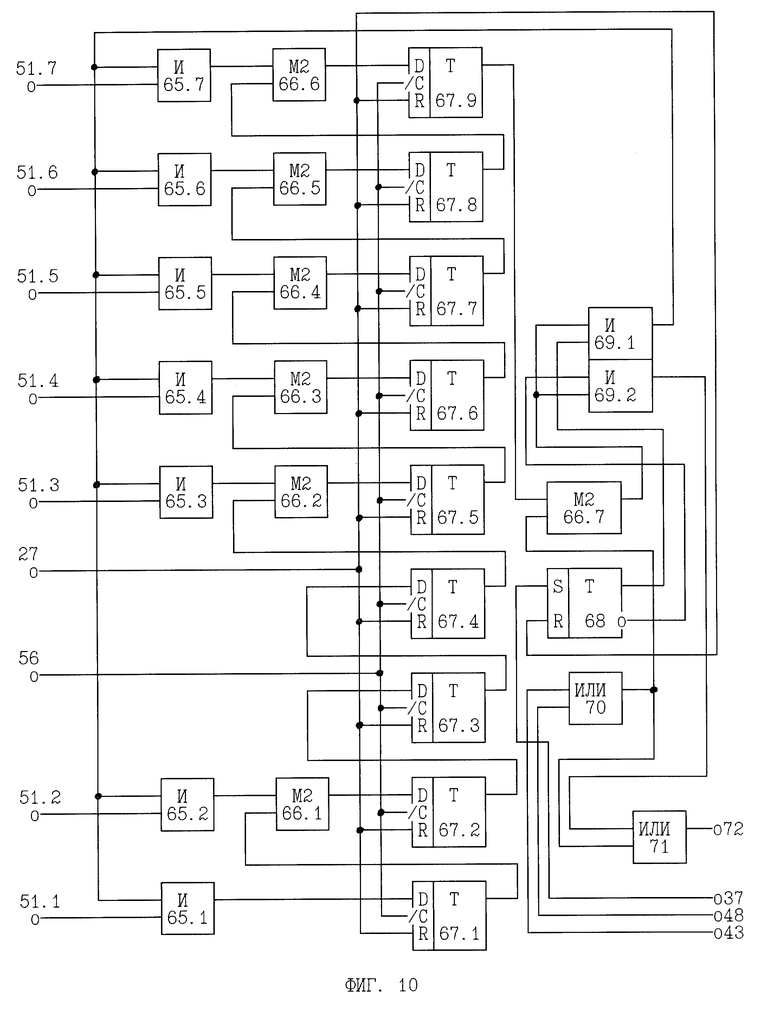

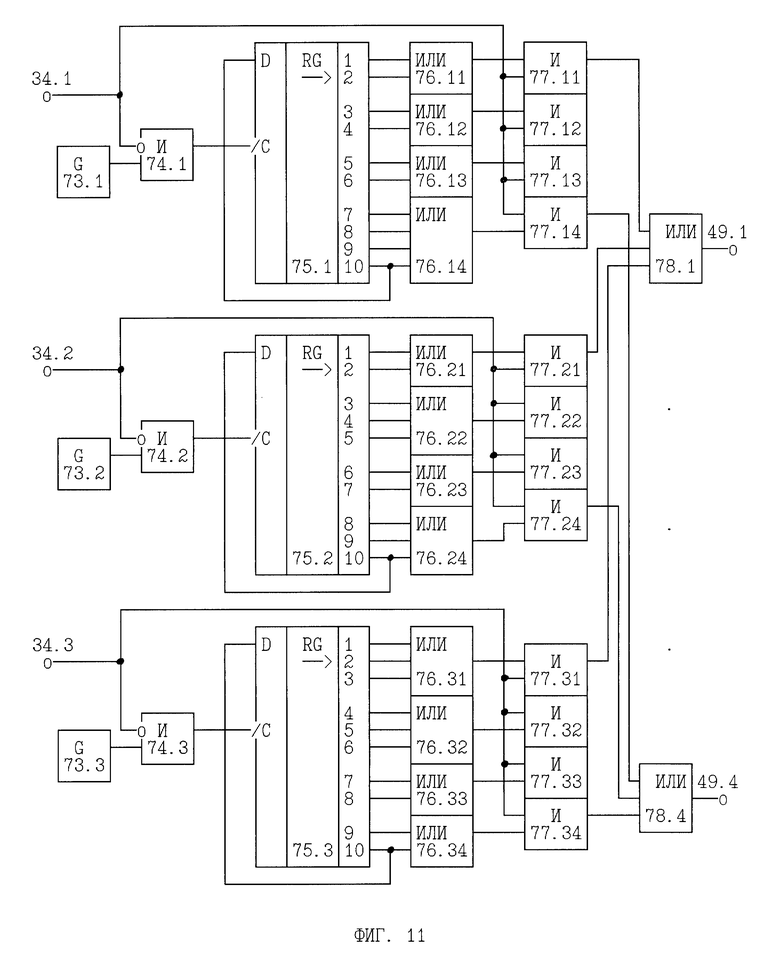

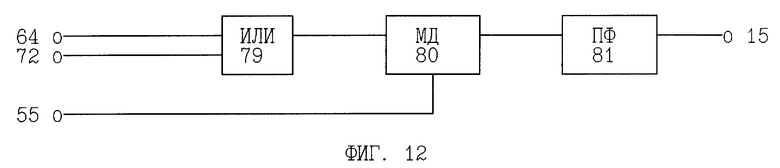

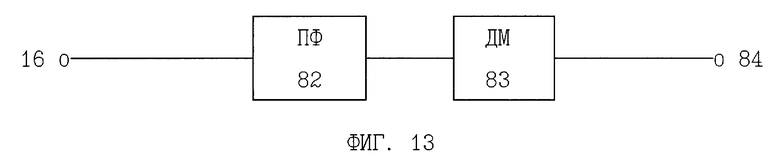

Сущность предлагаемого варианта реализации изобретения поясняется чертежами. На фиг.1 приведена структурная схема передающего устройства системы, на фиг.2 - структурная схема приемного устройства системы, на фиг.3 - функциональная схема пусконачинающего блока 4, на фиг.4 - функциональная схема коммутатора 5, на фиг. 5 - функциональная схема формирователя 6 адреса, на фиг.6 - функциональная схема шифратора 8 полинома, на фиг.7 - функциональная схема блока 9 генератора частот, на фиг. 8 функциональная схема перестраиваемого распределителя 10 передающего устройства, на фиг. 9 - функциональная схема формирователя 11 синхросигнала, на фиг. 10 - функциональная схема блока 12 кодирования, на фиг. 11 - функциональная схема блока 13 оценки состояний канала, на фиг. 12 - функциональная схема блока 14 согласования передающего устройства, на фиг. 13 - функциональная схема блока 17 согласования приемного устройства, на фиг. 14 - функциональная схема дешифратора 18 частот, на фиг. 15 - функциональная схема селектора 19 синхросигнала, на фиг. 16 - функциональная схема блока 20 генератора тактовых импульсов приемного устройства, на фиг. 17 - функциональная схема перестраиваемого распределителя 21 приемного устройства, на фиг. 18 - функциональная схема декодирующего блока 232, на фиг. 19 - функциональная схема дешифратора 24 адреса, на фиг. 20 - функциональная схема блока 25 выдачи данных, на фиг. 21 - временные диаграммы, поясняющие работу системы.

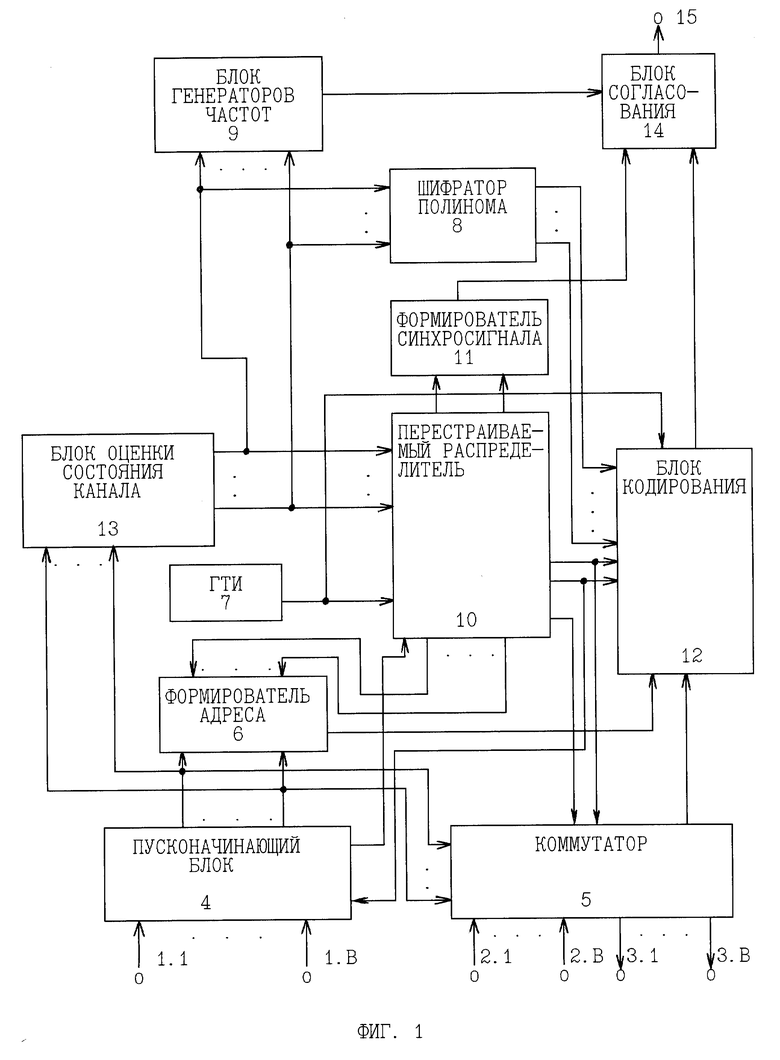

Структурная схема передающего устройства системы (см. фиг.1) содержит: 11-1B -группу управляющих входов; 21-2B - группу информационных входов; 31-3B - группу управляющих выходов; 4 - пусконачинающий блок; 5 - коммутатор; 6 - формирователь адреса; 7 - генератор тактовых импульсов; 8 - шифратор полинома; 9 - блок генераторов частот; 10 - перестраиваемый распределитель; 11 - формирователь синхросигнала; 12 - блок кодирования; 13 - блок оценки состояний канала; 14 - блок согласования; 15 - канальный выход.

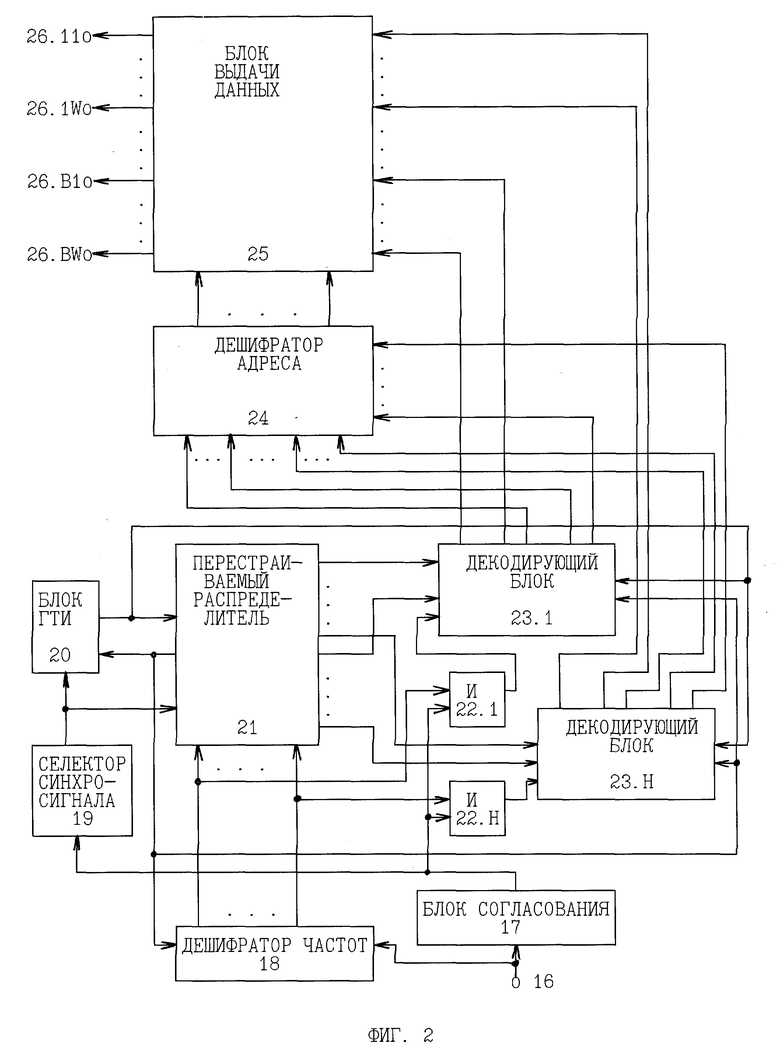

Структурная схема приемного устройства системы (см. фиг.2) содержит: 16 - канальный вход; 17 - блок согласования; 18 - дешифратор частот; 19 - селектор синхросигнала; 20 - блок генератора тактовых импульсов; 21 - перестраиваемый распределитель; 221-22H - элементы И; 231-23H - декодирующие блоки; 24 - дешифратор адреса; 25 - блок выдачи данных; 25I1-26IW, I=1,B,-B групп информационных выходов системы.

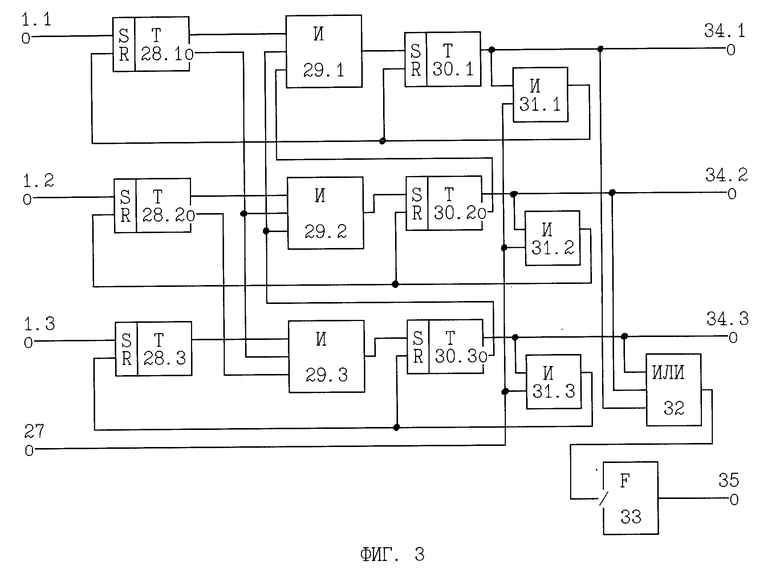

Функциональная схема пусконачинающего блока 4 (см. фиг.3) содержит: 11-13 - группу управляющих входов; 27 - управляющий вход; 281-283, 301-303 - соответственно первую и вторую группы RS-триггеров; 291-293, 311-313 - соответственно первую и вторую группы элементов И; 32 - элемент ИЛИ; 33 - формирователь сигналов переднего фронта импульсов; 341-343 - группу управляющих выходов; 35 - управляющий выход.

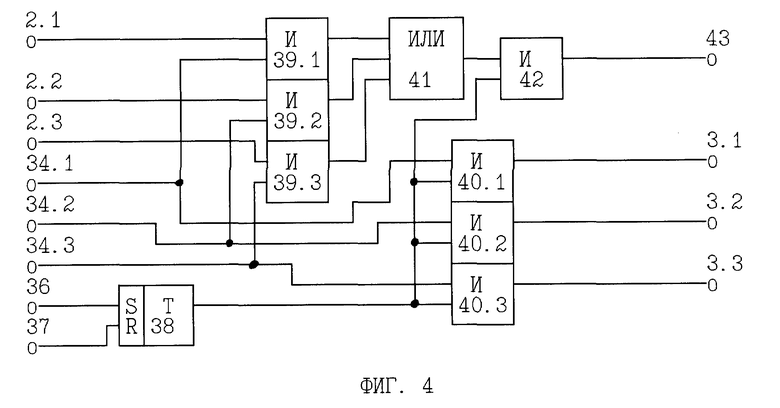

Функциональная схема коммутатора 5 (см. фиг. 4) содержит: 21-23 - группу информационных входов; 31-33 - группу управляющих выходов; 341-343 - группу управляющих входов; 36, 37 - соответственно первый и второй управляющие входы; 38 - RS - триггер; 391-393, 401-403 - соответственно первую и вторую группы элементов И; 41 - элемент ИЛИ; 42 - элемент И; 43 - информационный выход.

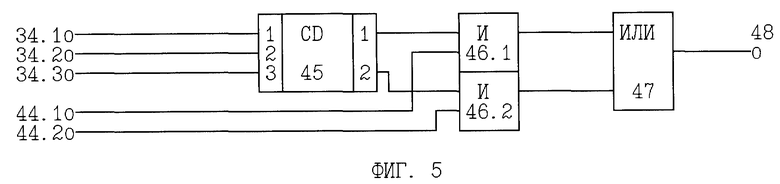

Функциональная схема формирователя 6 адреса (см. фиг. 5) содержит: 341-343, 441-442-соответственно первую и вторую группы управляющих входов; 45 - шифратор двоичного кода; 461-462-группу элементов И; 47 - элемент ИЛИ; 48 - информационный выход.

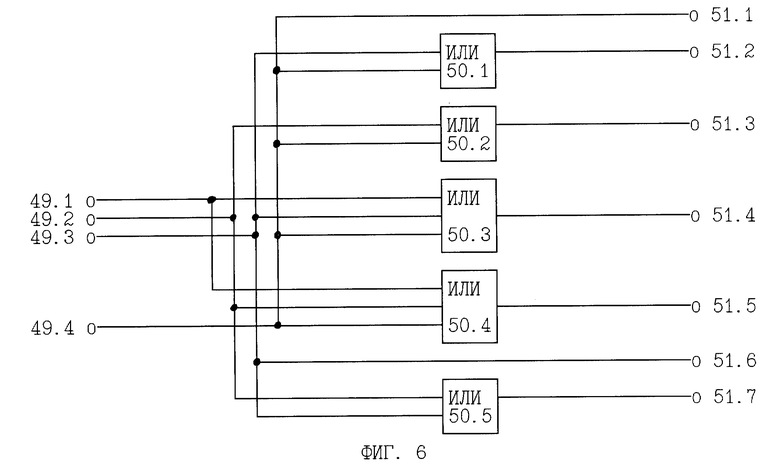

Функциональная схема шифратора 8 полинома (см. фиг. 6) содержит: 491-494 - группу управляющих входов; 501-505 - группу элементов ИЛИ; 511-517 - группу управляющих выходов.

Функциональная схема блока 9 генераторов частот (см. фиг.7) содержит: 491-494- группу управляющих входов; 521-524- группу генераторов гармонических колебаний (несущих частот); 531-534-группу элементов Монтажное И (ключей); 54 - элемент Монтажное ИЛИ (схема сборки); 55 - управляющий выход.

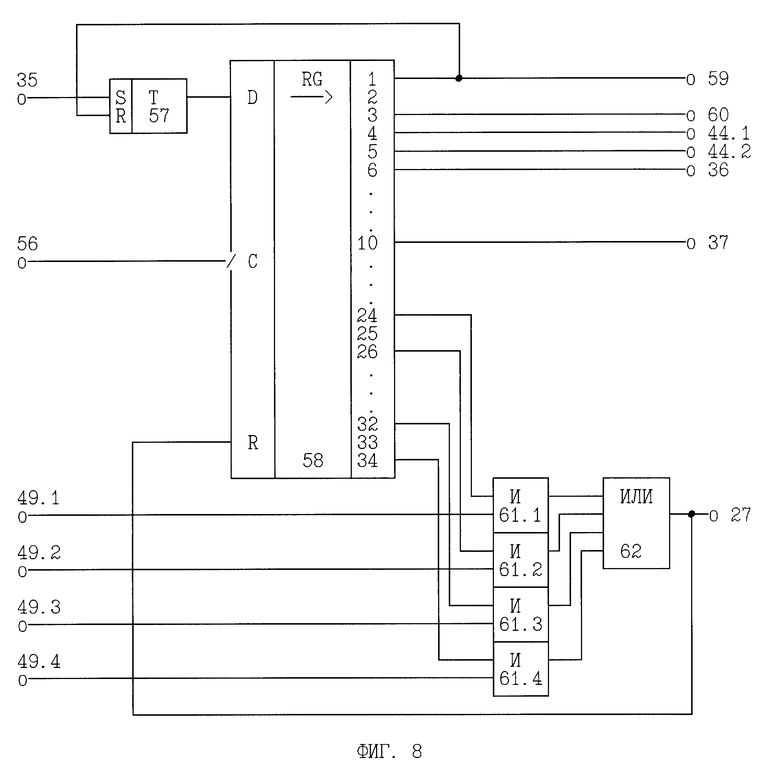

Функциональная схема перестраиваемого распределителя 10 передающего устройства (см. фиг.8) содержит: 27 - первый управляющий выход; 35 - управляющий вход; 36, 37 - соответственно третий и второй управляющие выходы; 441-442-группу управляющих выходов; 491-494 -группу управляющих входов; 56 - тактовый вход; 57- RS-триггер; 58 - регистр сдвига; 59,60 - соответственно четвертый и пятый управляющие выходы; 611-614 - группу элементов И; 62 - элемент ИЛИ.

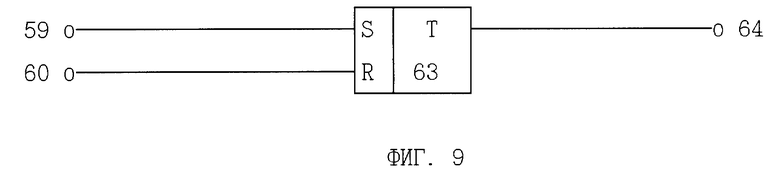

Функциональная схема формирователя 11 синхросигнала (см. фиг. 9) содержит: 59,60 - соответственно первый и второй управляющие входы; 63 - RS-триггер; 64 - информационный выход.

Функциональная схема блока 12 кодирования (см. фиг. 10) содержит: 27,37 - соответственно первый и второй управляющие входы; 43, 48 -соответственно первый и второй информационные входы; 511-517- группу управляющих входов; 56 - тактовый вход; 651-657 - группу элементов И; 661-667 - группу сумматоров по модулю два; 671-679 - группу D-триггеров; 691, 692 - элементы И; 70,71 - элементы ИЛИ; 72 - информационный выход.

Функциональная схема блока 13 оценки состояний канала (см. фиг.11) содержит: 341-343 - группу управляющих входов; 491-494 - группу управляющих выходов; 731-733 - группу генераторов пуассоновской последовательности импульсов; 741-743- группу элементов И; 751-753 - группу регистров сдвига; 7611-7614, I=1,3, - три группу элементов ИЛИ; 7711-7714, I=1,3 - три группы элементов И; 781-784 -группу элементов ИЛИ.

Функциональная схема блока 14 согласования передающего устройства (см. фиг. 12) содержит: 15 - канальный выход; 55 - управляющий вход; 64,72 - соответственно второй и первый информационные входы; 79 - элемент ИЛИ; 80 - модулятор; 81 - полосовой фильтр.

Функциональная схема блока 17 согласования приемного устройства (см. фиг. 13) содержит: 16 - канальный вход; 82 - полосовой фильтр; 83 - демодулятор; 84 - информационный выход.

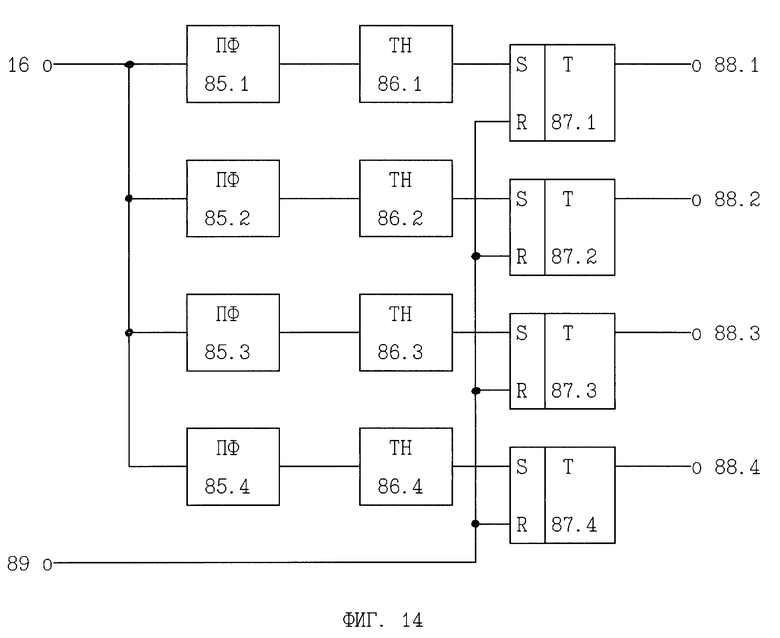

Функциональная схема дешифратора 18 частот (см. фиг. 14) содержит: 16 - канальный вход; 851-854 - группу полосовых фильтров; 851-864 - группу триггеров Шмитта (пороговых устройств); 871-874 -группу RS-тримггеров; 881-884 -группу управляющих выходов; 89 - управляющий вход.

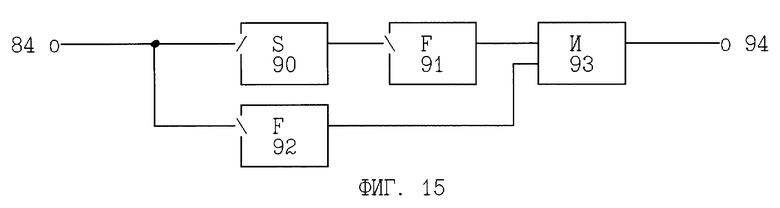

Функциональная схема селектора 19 синхросигнала (см. фиг. 15) содержит: 84 - информационный вход; 90 - генератор одиночного импульса (одновибратор), длительность которого равна длительности синхросигнала; 91, 92 - формирователя сигналов заднего фронта импульсов; 93 - элемент И; 94 - управляющий выход.

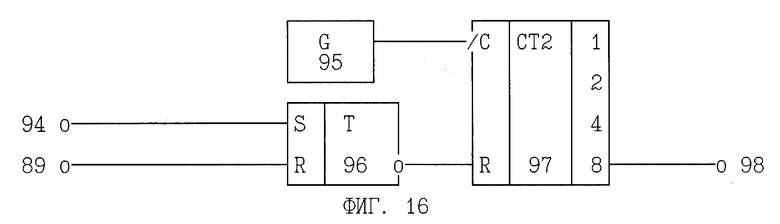

Функциональная схема блока 20 генератора тактовых импульсов (см. фиг. 16) содержит: 89, 94 - соответственно второй и первый управляющие входы; 95 - генератор импульсов высокой частоты; 96 - RS-триггер; 97 - двоичный счетчик, выполняющий функции делителя частоты; 98 - тактовый выход.

Функциональная схема перестраиваемого распределителя 21 приемного устройства (см. фиг. 17) содержит: 881-884-группу управляющих входов; 89 - управляющий выход; 94 - управляющий вход; 98 - тактовый вход; 991, 992 - RS-триггеры; 100 -формирователь сигнала переднего фронта импульса; 101 - регистр сдвига; 1021-1024, 1031-1034 - соответственно первую и вторую группу элементов И; 1041-1044, 1051-1054 - соответственно первую и вторую группы управляющих выходов; 106 - элемент ИЛИ.

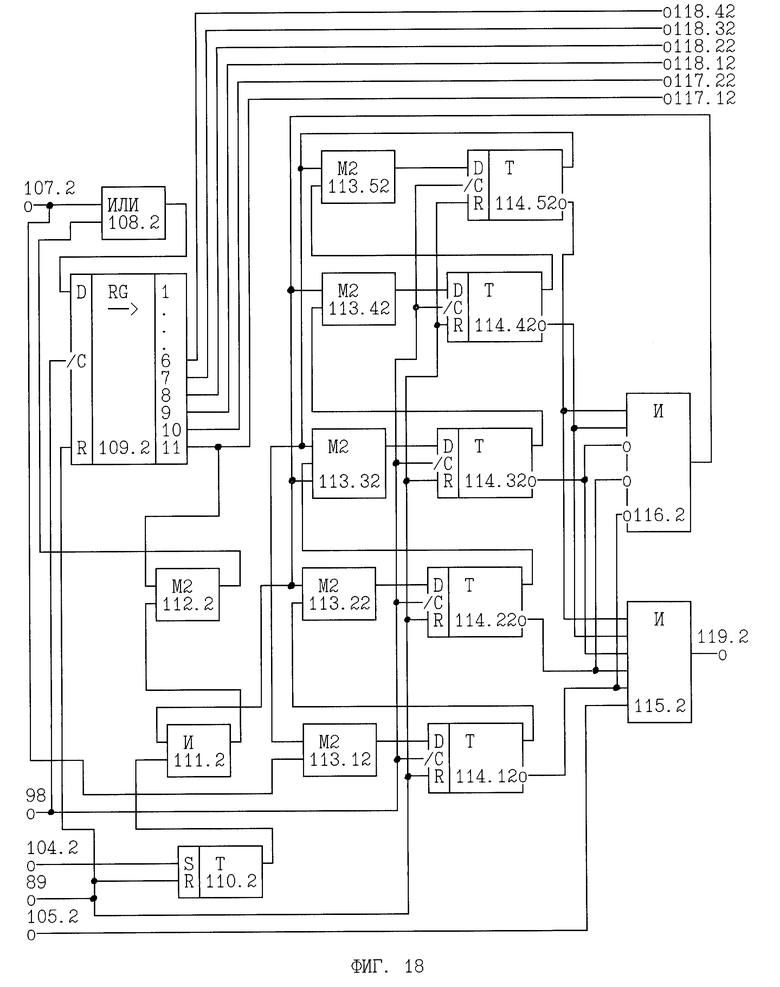

Функциональная схема декодирующего блока 232 (см. фиг. 18) содержит: 89 - третий управляющий вход; 98 - тактовый вход; 1042, 1052 - соответственно первый и второй управляющие входы; 1072 - информационный вход; 1082 - элемент ИЛИ; 1092 - регистр сдвига; 1102 - RS -триггер; 1112-элемент И; 1122 - сумматор по модулю два; 11312-11352 - группу сумматоров по модулю два; 11412-11452 - группу D-триггеров; 1152, 1162 - элементы И; 11712-11722, 11812-11842 - соответственно вторую и первую группы информационных выходов; 1192 - управляющий выход.

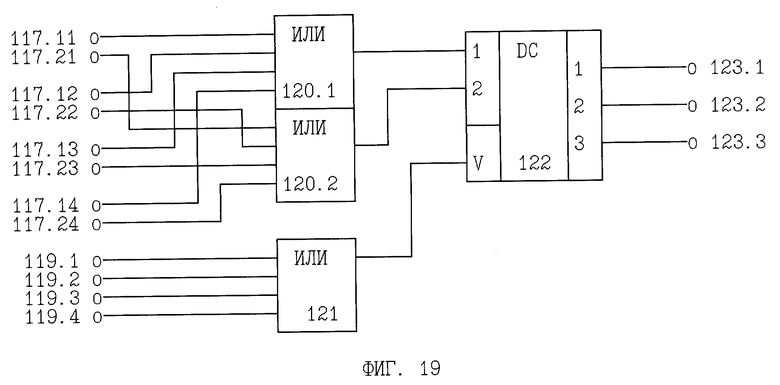

Функциональная схема дешифратора 24 адреса (см. фиг. 19) содержит: 1171J-1172J, J=1,4 - четыре группы информационных входов; 1191-1194 - группу управляющих входов; 1201, 1202 - два элемента ИЛИ; 122 - дешифратор двоичного кода; 121 - элемент ИЛИ, 1231-1233 - группу управляющих выходов.

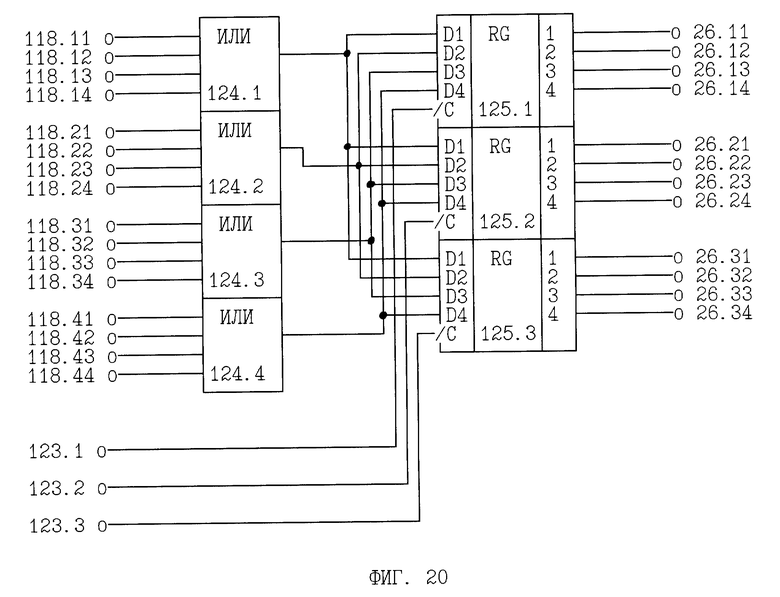

Функциональная схема блока 25 выдачи данных (см фиг. 20) содержит: 1181J-1184J, J= 1,4, - четыре группы информационных входов; 1231-1233 - группу управляющих входов; 1241-1244 -группу элементов ИЛИ; 1251-1253 - группу регистров памяти; 126I1-126I4, I=1,3, - три группы информационных выходов.

Функциональная схема пусконачинающего блока 4, коммутатора 5, формирователя 6 адреса, шифратора 8 полинома, блока 9 генератора частот, перестраиваемого распределителя 10 передающего устройства, блока 12 кодирования, блока 13 оценки состояний канала, дешифратора 18 частот, перестраиваемого распределителя 21 приемного устройства, декодирующего блока 232, дешифратора 24 адреса, блока 25 выдачи данных приведены для примера реализации системы передачи и приема информации кодами переменной длины в случае, когда число источников сообщений B=3; число разрядов кода адреса V=2; число разрядов сообщения W= 4; используются H=4 циклических кода с параметрами (10, 6), (11, 6), (14, 6), (15, 6), где первое число в скобках обозначает длину NJ, J=1,4, кода, а второе число - количество M=V+W информационных символов в кодовой комбинации; коэффициент удлинения синхроимпульса U=2.

Элементы системы передачи и приема информации кодами переменной длины взаимосвязаны следующим образом.

В передающем устройстве (см. фиг. 1) группа управляющих входов 11-1B пусконачинающего блока 4 является группой управляющих входов системы, группа информационных входов 21-2B коммутатора 5 является группой информационных входов системы, группа управляющих выходов 31-3B коммутатора 5 является группой управляющих выходов системы. Группа управляющих выходов пускноначинающего блока 4 соединена с группами управляющих входов коммутатора 5, первой группой управляющих входов формирователя 6 адреса и группой управляющих входов блока 13 оценки состояний канала. Информационный выход коммутатора 5 соединен с первым информационным входом блока 12 кодирования. Информационный выход формирователя 6 адреса соединен с вторым информационным входом блока 12 кодирования, выход генератора 7 тактовых импульсов соединен с тактовыми входами перестраиваемого распределителя 10 и блока 12 кодирования. Группа управляющих выходов шифратора 8 полинома соединена с группой управляющих входов блока 12 кодирования, выход блока 9 генератора частот соединен с управляющим входом блока 14 согласования. Группа управляющих выходов перестраиваемого распределителя 10 соединена с второй группой управляющих входов формирователя 6 адреса, первый управляющий выход перестраиваемого распределителя 10 соединен с управляющим входом пусконачинающего блока 4 и первым управляющим входом блока 12 кодирования. Второй управляющий выход перестраиваемого распределителя 10 соединен с вторыми управляющими входами коммутатора 5 и блока 12 кодирования. Третий управляющий выход перестраиваемого распределителя 10 соединен с первым управляющим входом коммутатора 5, четвертый и пятый управляющие выходы перестраиваемого распределителя 10 соединены соответственно с первым и вторым управляющими входами формирователя 11 синхросигнала, информационный выход которого соединен с вторым информационным входом блока 14 согласования, информационный выход блока 12 кодирования соединен с первым информационным входом блока 14 согласования, группа управляющих выходов блока 13 оценки состояний канала соединена с группами управляющих входов шифратора 8 полинома, блока 9 генераторов частот, перестраиваемого распределителя 10. Канальный выход 15 блока 14 согласования является канальным выходом системы.

В приемном устройстве (см. фиг. 2) канальный вход 16 системы соединен с канальными входами блока 17 согласования и дешифратора 18 частот. Информационный выход блока 17 согласования соединен с информационным входом селектора 19 синхросигнала и первыми входами элементов И 22J, J=1,H. Группа управляющих выходов дешифратора 18 частот соединена с группой управляющих входов перестраиваемого распределителя 21 и J-й, J= 1,H, выход группы соединен с вторым входом элемента И 22J, J=1,H. Управляющий выход селектора 19 синхросигнала соединен с первым управляющим входом блока 20 генератора тактовых импульсов и управляющим входом перестраиваемого распределителя 21. Выход блока 20 генератора тактовых импульсов соединен с тактовыми входами перестраиваемого распределителя 21 и декодирующих блоков 23J, J=1,H. Управляющий выход перестраиваемого распределителя 21 соединен с управляющим входом дешифратора 18 частот, вторым управляющим входом блока 20 генератора тактовых импульсов и третьими управляющими входами декодирующих блоков 23J, J=1,H, J-е, J= 1,H, выходы первой и второй групп управляющих выходов перестраиваемого распределителя 21 соединены соответственно с первым и вторым управляющими входами декодирующего блока 23J, J=1,H. Выход элемента И 22J, J=1,H, соединен с информационным входом декодирующего блока 23J, J=1,H. Первая группа информационных выходов декодирующего блока 23J, J=1,H, соединена с J-й, J=1, H, группой информационных входов блока 25 выдачи данных, вторая группа информационных выходов декодирующего блока 23J, J=1,H, соединена с J-й, J=1,H, группой информационных входов дешифратора 24 адреса, управляющий выход декодирующего блока 23J, J=1,H, соединен с J-м, J=1,H, входом группы управляющих входов дешифратора 24 адреса, группа управляющих выходов которого соединена с группой управляющих входов блока 25 выдачи данных, B групп информационных выходов 26I1-26IW, I=1,B, которого являются группами информационных выходов системы.

В пусконачинающем блоке 4 (см. фиг. 3) для примера реализации входы 11-13 группы управляющих входов соединены соответственно с входами установки в состояние "1" RS-триггеров 281-283. Управляющий вход 27 соединен с первыми входами элементов И 311-313. Прямые входы RS-триггеров 281-283 соединены соответственно с первыми входами элементов И 291-293, инверсный выход RS-триггера 281 соединен с вторыми входами элементов И 292, 293, инверсный выход RS-триггера 282 соединен с третьим входом элемента И 293. Выходы элементов И 291-293 соединены соответственно с входами установки в состояние "1" RS-триггеров 301-303, прямые выходы которых соединены соответственно с вторыми входами элементов И 311-313, входами элемента ИЛИ 32, выходами 341-343 группы управляющих выходов. Инверсный выход RS-триггера 302 соединен с третьим входом элемента И 291, инверсный выход RS-триггера 303 соединен со вторым входом элемента И 291 и третьим входом элемента И 292. Выходы элементов 311-313 соединены соответственно с входами сброса RS-триггеров 281-283, 301-303. Выход элемента ИЛИ 32 соединен с входом формирователя 33 сигналов переднего фронта импульсов, выход которого соединен с управляющим выходом 35.

В коммутаторе 5 (см. фиг. 4) для примера реализации входы 21-23 группы информационных входов соединены соответственно с первыми входами элементов И 391-393, входы 341-343 группы управляющих входов соединены соответственно со вторыми входами элементов И 391 - 39 3 и первыми входами элементов И 401 - 403. Первый 36 и второй 37 управляющие входы соединены соответственно с входами установки в состояние "12" и сброса RS-триггера 38, выход которого соединен со вторым входом И 42 и вторыми входами элементов И 401-403. Выходы элементов И 391-393 соединены с входами элемента ИЛИ 41. Выходы элементов И 401-403 соединены с выходами 31-33 группы управляющих выходов. Выход элемента ИЛИ 41 соединен с первым входом элемента И 42. Выход элемента И 42 соединен с управляющим выходом 43.

В формирователе 6 адреса (см. фиг. 5) для примера реализации входы 341-343 первой группы управляющих входов соединены с входами шифратора 45 двоичного кода. Входы 441-442 второй группы управляющих входов соединены соответственно с вторыми входами элементов И 461-462. Первый выход шифратора 45 двоичного кода соединен с первым входом элемента И 461, второй выход шифратора 45 соединен с первым входом элемента И 462. Выходы элементов И 461-462 соединены с входами элемента ИЛИ 47, выход которого соединен с информационным выходом 48.

В шифраторе 8 полинома (см. фиг. 6) для примера реализации вход 491 группы управляющих входов соединен с первыми входами элементов ИЛИ 503, 504, вход 492 группы управляющих входов соединен с первыми входами элементов ИЛИ 502, 505 и вторым входом элемента ИЛИ 504, вход 493 группы управляющих входов соединен с первым входом элемента ИЛИ 501, вторыми входами элементов ИЛИ 503, 505 и выходом 516 группы управляющих выходов, вход 494 группы управляющих входов соединен с вторыми входами элементов ИЛИ 501, 502, третьими входами элементов ИЛИ 503, 504 и выходом 511 группы управляющих выходов, выходы элементов ИЛИ 501-505 соединены соответственно с выходами 512-515, 517 группы управляющих выходов.

В блоке 9 генераторов частот (см. фиг. 7) для примера реализации входы 491-494 группы управляющих входов соединены соответственно с вторыми входами элементов Монтажное И 531-534, выходы генераторов 521-524 гармонических колебаний соединены с первыми входами элементов Монтажное И 531-534, выходы которых соединены с входами элемента Монтажное ИЛИ 54, выход которого соединен с управляющим выходом 55.

В перестраиваемом распределителе 10 (см. фиг. 8) для примера реализации управляющий вход 35 соединен с входом установки в состояние "1" RS-триггера 57. Входы 491-494 группы управляющих входов соединены соответственно с вторыми входами элементов И 611-614. Тактовый вход 56 соединен с входом синхронизации регистра 58 сдвига. Выход RS-триггера 57 соединен с информационным входом регистра 58 сдвига. Выход первой ячейки регистра 58 сдвига соединен с входом сброса RS-триггера 57 и четвертым управляющим выходом 59, выход третьей ячейки регистра 58 сдвига соединен с пятым управляющим выходом 60, выходы четвертой и пятой ячеек регистра 58 сдвига соединены соответственно с выходами 441, 442 группы управляющих выходов, выходы шестой и десятой ячеек регистра 58 сдвига соединены соответственно с третьим 36 и вторым 37 управляющими выходами, выходы 24-й, 26-й, 32-й и 34-й ячеек регистра 58 сдвига соединены соответственно с первыми входами элементов И 611-614. Выходы элементов И 611-614 соединены с входами элемента ИЛИ 62, выход которого соединен с первым управляющим выходом 27 и входом сброса регистра 58 сдвига.

В формирователе 11 синхросигнала (см. фиг. 9) первый 59 и второй 60 управляющие входы соединены соответственно с входами установки в состояние "1" и сброса RS-триггера 63, выход которого соединен с информационным выходом 64.

В блоке 12 кодирования (см. фиг. 10) для приема реализации первый управляющий вход 27 соединен с входами сброса D-триггеров 671-679 и RS-триггера 68, второй управляющий вход 37 соединен с входом установки в состояние "1" RS-триггера 68. Первый 43 и второй 48 информационные входы соединены соответственно с входами элемента ИЛИ 70. Входы 511-517 группы управляющих входов соединены соответственно с вторыми входами элементов И 651-657. Тактовый вход 56 соединен с входами синхронизации D-триггеров 671-679. Выход элемента И 651 соединен с информационным входом D-триггера 671. Выходы элементов И 652-657 соединены соответственно с первыми входами сумматоров 661-666 по модулю два. Выход сумматора 661 по модулю два соединен с информационным входом D-триггера 672. Выходы сумматоров 662-666 по модулю два соединены соответственно с информационными входами D-триггеров 675-679. Выход сумматора 667 по модулю два соединен с первыми входами элементов И 691, 692. Выход D-триггера 671 соединен с вторым входом сумматора 661 по модулю два. Выход D-триггера 672 соединен с информационным входом D-триггера 673, выход которого соединен с информационным входом D-триггера 674. Выходы D-триггеров 674-679 соединены соответственно с вторыми входами сумматоров 662-667 по модулю два. Прямой и инверсный выходы RS-триггера 68 соединены соответственно с вторыми входами элементов И 691-692, выход элемента И 691 соединен с первыми входами элементов И 651-657, выход элемента И 692 соединен с первым входом элемента ИЛИ 71. Выход элемента ИЛИ 70 соединен с первым входом сумматора 667 по модулю два и вторым входом элемента ИЛИ 71, выход которого соединен с информационным выходом 72.

В блоке 13 оценки состояний канала (см. фиг. 11) для примера реализации входы 341-343 группы управляющих входов соединены соответственно с инверсными входами элементов И 741-743 и первыми входами элементов И 771J-773J, J = 1,4, выходы генераторов 731-733 пуассоновской последовательности импульсов соединены соответственно с прямыми входами элементов И 741-743, выходы которых соединены соответственно с входами синхронизации регистров 751-753 сдвига, выходы ячеек регистра 75I, I=1,3, сдвига соединены с входами элементов ИЛИ 76I1-76I4, I=1,3, в соответствии с вероятностными характеристиками математической модели канала, выход последней ячейки регистра 75I, I=1,3, сдвига соединен с его информационным входом, т.е. регистр замкнут в кольцо, выходы элементов ИЛИ 76I1-76I4, I=1,3, соединены с вторыми входами элементов И 77I1-77I4, I= 1,3. Выходы элементов И 77I1-77I4, I=1,3 соединены соответственно с входами элементов ИЛИ 781-784, выходы которых соединены соответственно с выходами 491-494 группы управляющих выходов.

В блоке 14 согласования передающего устройства (см. фиг. 12) реализации управляющий вход 55 соединен с входом несущего сигнала модулятора 80. Второй 64 и первый 72 информационные входы соединены с входами элемента ИЛИ 79, выход которого соединен с входом модулирующего сигнала модулятора 80, выход которого соединен с входом полосового фильтра 81, выход которого соединен с канальным выходом 15.

В блоке 17 согласования приемного устройства (см. фиг. 13) канальный вход 16 соединен с входом полосового фильтра 82, выход которого соединен с входом демодулятора 83, выход которого соединен с информационным выходом 84.

В дешифраторе 18 частот (см. фиг. 14) для примера реализации канальный вход 16 соединен с входами полосовых фильтров 851-854, выходы которых соединены соответственно с входами триггеров 861-864 Шмитта (пороговых устройств), выходы которых соединены соответственно с входами установки в состояние "1" RS-триггреов 871-874, выходы которых соединены соответственно с выходами 881-884 группы управляющих выходов. Управляющий вход 89 соединен с входами сброса RS-триггеров 871-874.

В селекторе 19 синхросигнала (см. фиг. 15) информационный вход 84 соединен с входами одновибратора 90 и формирователя 92 сигналов заднего фронта импульсов, выход одновибратора 90 соединен с входом формирователя 91 сигналов заднего фронта импульсов, выход которого соединен с первым входом элемента И 93 Выход формирователя 92 сигналов соединен с вторым входом элемента И 93, выход которого соединен с управляющим выходом 94.

В блоке 20 генератора тактовых импульсов (см. фиг. 16) второй 89 и первый 94 управляющие входы соединены соответственно с входами сброса и установки в состояние "1" RS-триггера 96. Выход генератора 95 импульсов высокой частоты соединен с входом синхронизации двоичного счетчика 97. Инверсный выход RS-триггера 96 соединен с входом сброса двоичного счетчика 97, выход которого соединен с тактовым выходом 98.

В перестраиваемом распределителе 21 приемного устройства (см. фиг. 17) для примера реализации входы 881-884 группы управляющих входов соединены соответственно с вторыми входами элементов И 1021-1024, 1031-1034, управляющий вход 94 соединен с входом установки в состоянии "1" RS-триггера 991. Тактовый вход 98 соединен с входом синхронизации регистра 101 сдвига. Выход RS-триггера 991 с входом формирователя 100 сигналов переднего фронта импульсов, выход RS-триггера 992 соединен с информационным входом регистра 101 сдвига. Выход формирователя 100 сигналов переднего фронта импульсов соединен с входом установки в состояние "1" RS-триггера 992. Выход первой ячейки регистра 101 сдвига соединен с входом сброса RS-триггера 992, выходы 11-й, 12-й, 15-й, 16-й ячеек регистра 101 сдвига соединены соответственно с первыми входами элементов И 1021-1024, выходы 21-й, 23-й, 29-й и 31-й ячеек регистра 101 сдвига соединены соответственно с первыми входами элементов И 1031-1034. Выходы элементов И 1021-1024 соединены соответственно с выходами 1041-1044 первой группы управляющих выходов. Выходы элементов 1031-1034 соединены соответственно с выходами 1051-1054 второй группы управляющих выходов и входами элемента ИЛИ 106, выход которого соединен с входами сброса RS-триггера 991 и регистра 101 сдвига и управляющим выходом 89.

В декодирующем блоке 232 (см. фиг. 18) для примера реализации третий управляющий вход 89 соединен с входами сброса регистра 1092 сдвига, RS-триггера 1102 и D-триггеров 11412-11452, тактовый вход 98 соединен с входами синхронизации регистра 1092 сдвига и D-триггеров 11412-11452, первый управляющий вход 1042 соединен с входом установки в состояние "1" RS-триггера 1102. Второй управляющий вход 1052 соединен с шестым входом элемента И 1152. Информационный вход 1072 соединен с вторыми входами элемента ИЛИ 1082 и сумматора 11312 по модулю два. Выход элемента ИЛИ 1082 соединен с информационным входом регистра 1092 сдвига. Выходы 9-й, 8-й, 7-й и 6-й ячеек регистра 1092 сдвига соединены соответственно с выходами 11812-11842 первой группы информационных выходов, выход 10-й ячейки регистра 1092 сдвига соединен с выходом 11722 второй группы информационных выходов, выход 11-й ячейки регистра 1092 сдвига соединен с первым входом сумматора 1122 по модулю два и выходом 11712 второй группы информационных выходов. Выход RS-триггера 1102 соединен с первым входом элемента И 1112, выход которого соединен с вторым входом сумматора 1122 по модулю два, выход которого соединен с первым входом элемента ИЛИ 1082. Выходы сумматоров 11312-11352 по модулю два соединены соответственно с информационными входами D-триггеров 11412-11452, инверсные выходы которых соединены соответственно с первым-пятым входами элемента И 1152, а также первым и вторым прямыми и третьим-пятым инверсными входами элемента И 1162, прямые выход D-триггеров 11412-11442 соединены соответственно с первыми входами сумматоров 11322-11352 по модулю два, прямой выход D-триггера 11452 соединен с первым входом сумматора 11312 по модулю два и вторыми входами сумматоров 11332, 11352 по модулю два. Выход элемента И 1152 соединен с управляющим выходом 1192. Выход элемента И 1162 соединен с вторыми входами элемента И 1112, сумматоров 11322, 11342 по модулю два и третьим входом сумматора 11332 по модулю два.

В дешифраторе 24 адреса (см. фиг. 19) для примера реализации информационные входы 11711-11714 соединены с входами элемента ИЛИ 1201, информационные входы 11721-11724 соединены с входами элемента ИЛИ 1202. Входы 1191-1194 группы управляющих входов соединены с входами элемента ИЛИ 121. Выходы элементов ИЛИ 1201, 1202 соединены с входами дешифратора 122 двоичного кода. Выход элемента ИЛИ 121 соединен с входом разрешения приема информации (V-входом) дешифратора 122 двоичного кода, выходы которого соединены с выходами 1231 - 1233 группы управляющих выходов.

В блоке 25 выдачи данных (см. фиг. 20) для примера реализации информационные входы 118L1-118L4, L=1,4, соединены с входами элемента ИЛИ 124L, L= 1,4, входы 1231-1233 группы управляющих входов соединены соответственно с входами синхронизации регистров 1251-1253 памяти. Выход элемента ИЛИ 124L соединен с L-ми, L=1,4, информационными входами регистров 1251-1253 памяти, выходы регистра 125I, I=1,3, памяти соединены с выходами 26I1-26I4 I-й I= 1,3, группы информационных выходов.

Система передачи и приема информации кодами переменной длины работает следующим образом.

Вначале рассмотрим обобщенный алгоритм. В исходном состоянии на передающей стороне генератор 7 тактовых импульсов, а на приемной стороне - генератор 95 импульсов высокой частоты (см. фиг. 16) в блоке 20 генератора тактовых импульсов. При появлении у I-го, I=1,B, источника информации сообщения на соответствующем входе 1I группы управляющих входов пусконачинающего блока 4 появляется сигнал запроса передачи от I-го источника. Этот сигнал запоминается в пусконачинающем блоке 4, реализующем относительный приоритет обслуживания по возрастанию номеров. Согласно указанному типу приоритета, если при передаче некоторого сообщения возникли сообщения у других источников, они ожидают окончания передачи данного сообщения, а затем начинается передача сообщения источника с наименьшим номером. Пусть в момент возникновения сообщения у I-го источника система не занята передачей сообщения другого источника, тогда на I-м выходе группы управляющих выходов пусконачинающего блока 4 появляется сигнал разрешения обработки сообщения I-го источника.

Под действием указанного сигнала в формирователе 6 адреса формируется параллельный код адреса I-го источника, а в блоке 13 оценки состояний канала определяется номер J, J=1,H, корректирующего кода, используемого в данный момент времени для передачи сообщения I-го источника. Сигнал, несущий информацию о номере кода, поступает на J-й выход группы управляющих выходов блока 13 оценки состояний канала.

Под действием указанного сигнала в блоке 9 генераторов частот выбирается несущее колебание с соответствующей данному коду частотой, которое поступает на управляющий вход блока 14 согласования. Кроме того, шифратор 11 полинома в соответствии с поступающим управляющим сигналом выдает на группу управляющих входов блока 12 кодирования сигналы, которые несут информацию об образующем полиноме выбранного кода. Также сигнал с J-го выхода группы управляющих выходов блока 13 оценки состояния канала задает в перестраиваемом распределителе 10 число тактов работы для передачи и обработки (декодирования) сообщения с помощью J-го кода.

По переднему фронту сигнала разрешения обработки сообщения на управляющем выходе пусконачинающего блока 4 формируется сигнал запуска перестраиваемого распределителя 10, который начинает переключаться под действием тактовых импульсов, вырабатываемых генератором 7 тактовых импульсов. Сигналы с 4-го и 5-го управляющих выходов перестраиваемого распределителя 10, вырабатываемые на 1-м и (U+1)-м тактах, используются для формирования синхросигнала, который поступает на второй информационный вход блока 14 согласования и после преобразования (модуляция и фильтрация) через канальный выход 15 в канал связи.

Сигналы с группы управляющих выходов перестраиваемого распределителя 10, вырабатываемые на тактах с (U+2)-го по (U+1+V)-й, используются в формирователе 6 адреса для преобразования параллельного кода адреса в последовательный код, поступающий на второй информационный вход блока 12 кодирования.

На (U+2+V)-м такте перестраиваемый распределитель 10 выдает на 3-й управляющий выход сигнал разрешения приема информационных разрядов сообщения источника. Под действием указанного сигнала (совместно с сигналом разрешения обработки сообщения I-го источника, поступающего от пусконакачивающего блока 4) на выходе 3I группы управляющих выходов коммутатора 5 появляется сигнал разрешения передачи информации I-го источника. В результате в течение W тактов (с (U+2+V)-го по (U+1+M)-й) информационные разряды сообщения в последовательном коде поступают на вход 2I группы информационных входов коммутатора 5, а с информационного выхода коммутатора 5 - на первый информационный вход блока 12 кодирования.

Процедура кодирования реализуется в соответствии с соотношением

A(X)=C(X)•XK+R(X),

где

A(X) - кодовый полином циклического кода;

C(X) - полином информационных символов, к которым относятся символы кода адреса и сообщения источника;

K - степень образующего полинома G(X), равная числу контрольных символов кода;

R(X) - полином контрольных символов, равный остатку от деления полинома C(X)•XK на полином G(X).

В течение M тактов (с (U+2)-го по (U+1+M)-й) в блоке 12 кодирования происходит вычисление контрольных символов; одновременно информационные символы, поступающие в блок 12 кодирования с второго и первого информационных входов, выдаются через информационный выход блока 12 кодирования на первый информационный вход блока 14 преобразования и после преобразования (модуляция и фильтрация) поступает вслед за синхросигналом через канальный выход 15 в канал связи.

На (U+2+M)-м такте перестраиваемый распределитель 10 выдает на второй управляющий выход сигнал выдачи контрольных разрядов. Под действием указанного сигнала с выхода 3I группы управляющих выходов коммутатора 5 снимается сигнал разрешения передачи информации от I-го источника, а входы 21-2B группы информационных входов коммутатора 5 отключаются от его информационного входа. В течение KJ тактов (с (U+2+M)-го по (U+1+M)-й) контрольные символы вслед за информационными поступают на первый информационный вход блока 14 согласования и после преобразования (модуляция и фильтрация) через канальный выход 15 в канал связи.

На (U+2+2NJ)-м такте перестраиваемый распределитель 10 выдает на первый управляющий выход сигнал сброса. Под действием этого сигнала устанавливаются в состояние "0" элементы с памятью блока 12 кодирования и перестраиваемого распределителя 10, а также RS-триггеры 28I, 30I (см. фиг. 3) пусконачинающего блока 4. При этом с I-го выхода группы управляющих выходов пусконачинающего блока 4 снимается сигнал разрешения обработки сообщения от I-го источника и с J-го выхода группы управляющих выходов блока 13 оценки состояний канала - сигнал, определяющий номер используемого для передачи кода.

На приемной стороне системы сигнал с канального входа 16 поступает в блок 17 согласования, где осуществляется его фильтрация и демодуляция, и блок 18 дешифратора частот, где определяется номер J кода, используемого для передачи. В результате на J-м выходе группы управляющих выходов дешифратора 18 частот появляется сигнал, несущий информацию о номере кода. Указанный сигнал поступает на второй вход элемента И 22J, разрешая прием и декодирование кодовой комбинации, поступающей на первые входы элементов И 221-22H с информационного выхода блока 17 согласования, декодирующим блоком 23J.

По заднему фронту синхроимпульса селектор 19 синхросигнала вырабатывает сигнал запуска блока 20 генератора тактовых импульсов и перестраивоемого распределителя 21. Под действием тактовых импульсов начинает переключаться перестраиваемый распределитель 21 и работать декодирующий блок 23J. Таким образом, 1-й такт работы перестраиваемого распределителя 21 приемного устройства соответствует (U+2)-му такту работы перестраиваемого распределителя 10 передающего устройства.

В течение первых NJ тактов в декодирующем блоке 23J происходит запись принятой комбинации в буферный регистр и вычисление синдрома (остатка от деления принятого полинома на образующий полином). Начиная с (NJ+1)-го такта, по сигналу, выдаваемому с перестраиваемого распределителя 21 на первый управляющий вход декодирующего блока 23J, в последнем в течение NJ тактов происходит исправление ошибок.

На (2NJ+1)-м такте перестраиваемый распределитель 21 выдает сигнал завершения этапа исправления ошибок, поступающий на второй управляющий вход декодирующего блока 23J. Если в принятой комбинации отсутствуют ошибки или содержатся исправляемые или необнаруживаемые ошибки, то под действием указанного сигнала декодирующий блок 23J выдает на дешифратор 24 адреса сигнал разрешения декодирования кода адреса источника информации, поступающего на дешифратор 24 адреса со второй группы информационных выходов декодирующего блока 23J. В противном случае (в принятой комбинации содержатся обнаруживаемые, но неисправляемые ошибки) декодирующий блок 23J сигнала разрешения декодирования на дешифратор 24 адреса не дает.

при получении сигнала разрешения декодирования дешифратор 24 адреса в свою очередь выдает на 1-й вход группы управляющих входов блока 25 выдачи данных сигнал выдачи 1-му получателю информации разрядов сообщения, поступающих с первой группы информационных выходов декодирующего блока 23J.

На (2NJ+1)-м такте с небольшой задержкой во времени на управляющий выход перестраиваемого распределителя 21 выдается сигнал сброса, поступающий на управляющий вход дешифратора 18 частот, второй управляющий вход блока 20 генератора тактовых импульсов и третий управляющий вход декодирующего блока 23J, в которых (а также и в перестраиваемом распределителе 21) элементы с памятью устанавливаются в состояние "0". При этом прекращается выдача тактовых импульсов блоком 20 генератора тактовых импульсов, а также снимается сигнал с J-го выхода группы управляющих выходов дешифратора 18 частот, определяющий номер используемого для передачи кода.

В качестве примера подтверждения работоспособности устройства рассмотрим реализацию блоков 8, 12, 13, 232 и функционирование устройства в случае, когда число источников сообщений B=3 (откуда число разрядов кода адреса V=2); число разрядов сообщения W=4; используются H=4 циклически или укороченных циклических кода с образующими полиномами G1(X)=X4+X+1, G2(X)=X5+X4+X2+1, G3(X)= X8+X7+X6X4+1, G4(X)=X9+X6+X5X4+X+1; коэффициент удлинения синхроимпульса U=2.

Представим образующие полиномы GJ(X), J=1,4, в нормализованной форме, при этом старший член полинома имеет степень K=9, а K4-KJ=9-KJ младших членов равны нулю: G1(X)•X5 = X9+X6+X5, G2(X)•X4 = X9+X8+X6+X4, G3(X)•X = X9+X8+X7+X5+X, G4(X) = X9+X6+X5+X4+X+1,

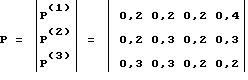

На основании значений коэффициентов полиномов в нормализованной форме составим матрицу для синтеза шифратора 8 полинома, в которой строки соответствуют входным сигналам XJ, J=1,4, а столбцы - выходным сигналам YL, L= 1,9, шифратора

Из матрицы следует, что выходные сигналы YL шифратора 8 полинома определяются через его входные сигналы XJ следующим образом:

Y1=X4; Y2=X3VX4; Y4=0; Y5=X2VX4; Y6=X1VX3VX4; Y7=X1VX2VX4; Y8= X3; Y9=X2VX3.

В шифраторе 8 полинома (см. фиг. 6) логика соединений входов 49 с входами элементов ИЛИ 50 и выходами 51 соответствует логическим функциям Y1, Y2 и Y5-Y9.

Сигналы, поступающие с шифратора 8 полинома на входы 51 блока 12 кодирования (фиг. 10) обеспечивают с помощью элементов И 65 реализацию схемы деления на образующий полином используемого для передачи кода (кода, номер которого соответствует номеру выхода 49 блока 13 оценки состояний канала, на котором появится сигнал).

В основу реализации блока 13 оценки состояний канала (фиг. 11) положена следующая математическая модель.

При исследовании реального канала для каждого однородного потока сообщений, характеризуемого заданными требованиями к верности передачи, выделяется H состояний, характеризуемых, например, различным уровнем помех в канале. Тогда для каждого 1-го, I=1,B, источника однородных сообщений математическая модель канала записывается в виде матрицы строки

P(I) = |P

где

P

Элементы стохастических матриц P(I) нормированы, поэтому выбор состояний канала будет отвечать схеме случайных событий.

В силу того, что автоматные модели для каждого 1-го источника гомоморфны, схема блока 13 оценки состояний канала состоит из B идентичных друг другу узлов, реализованных на генераторах 73 пуассоновского потока импульсов, элементах И 74, циклически замкнутых регистрах 75 сдвига, группах элементов ИЛИ 76 и группах элементов И 77.

На элементе И 74, регистре 75 и генераторе 73 реализуется равновероятностный (1-f)-полюсник, где f - число ячеек (разрядов) регистра 75. Выходы ячеек регистра 75I, I=1,B, сдвига соединены с входами группы элементов ИЛИ 76IJ, J=1,H, в соответствии с величинами вероятностей P

Для примера реализации на фиг. 11 принято, что матрица P имеет вид:

В этом случае для реализации вероятностного (1-f)-полюсника выбираем f= 10. Тогда к элементу ИЛИ 7611 следует подключить выходы первой и второй ячеек регистра 751, к элементу ИЛИ 7612 - выходы третьей и четвертой ячеек регистра 751, к элементу ИЛИ 7613 - выходы пятой и шестой ячеек регистра 751, к элементу ИЛИ 7614 - выходы седьмой, восьмой, девятой и десятой ячеек регистра 751 и т.д.

Частоты генераторов 73 пуассоновского потока импульсов на порядок и более превышают частоту опроса по входам 34. В один из разрядов (произвольно выбранный) регистров 75 предварительно записывается единица (для упрощения схемы цепи предварительной записи единицы в регистры 75 на фиг. 11 не показаны). Генератора 73 подают импульсы через элементы И 74 на тактовые входы регистров 75 и единица в каждом из регистров между моментами опроса многократно "обегает" ячейки памяти.

В момент опроса по входу 341 элемент И 741 закрывается и на одном их выходов регистра 751 квазиравновероятно фиксируется потенциал, который через соответствующие элементы ИЛИ 76, элемент И 77, элемент ИЛИ 78 поступает на один из выходов 49 блока. Таким образом на выходах 491-494 обеспечивается появление сигналов на время опроса по входу 341 с вероятностями P

Декодирующий блок 232 (фиг. 18) осуществляет декодирование по синдрому (последовательный режим) кода с параметрами:

N2 = 11, D2=4, G2(X) = X5+X4+X2+1.

При этом исправляются однократные ошибки и обнаруживаются двухкратные ошибки и часть ошибок более высокой кратности.

Схема вычислителя синдрома, представляющая собой схему деления на образующий полином, реализована на D-триггерах 114 и сумматорах 113 по модулю два. Ненулевые коэффициенты образующего полинома G2(X)=X5+X4+X2+1 определяют наличие сумматоров 11352, 11332, 11312 по модулю два, подключаемых к цепи обратной связи, заводимой с выхода D-триггера 11452.

При исправлении однократных ошибок множество селектируемых синдромов состоит из одного синдрома S*(X), определяемого как остаток от деления XN-1 на G(X). В данном случае S*(X)=X2+X+1. Селектор синдромов исправляемых ошибок реализован на элементе И 1162. В соответствии с коэффициентами S*(X) инверсные выходы D-триггеров 114 вычислителя синдрома соединяются с прямыми и инверсными входами элемента И 1162.

Полином T(X), задающий обратную связь для обнуления D-триггеров вычислителя синдрома после исправления ошибки, определяется как остаток от деления XN на G(X). В данном случае T(X)=X3+X2+X. Ненулевые коэффициенты T(X) определяют наличие сумматора 11342, 11332, 11322 по модулю два, подключаемых к цепи обратной связи, заводимой с выхода селектора синдромов.

Селектор нулевого синдрома, реализованной на элементе И 1152, опрашивается на (2N+1)-м такте (в данном случае на 23-м) работы приемного устройства. Если синдром нулевой, то на выход 1192 поступает сигнал разрешения декодирования кода адреса; если же синдром ненулевой, то сигнал разрешения декодирования кода адреса на выход 1192 не поступает.

Пусть в некоторый момент времени у 1-го источника возникло сообщение 1010. При этом на входе 11 пусконачинающего блока 4 (фиг. 3) появляется сигнал запроса передачи от 1-го источника, запоминаемый в триггере 281. Предположим, что система в данный момент времени не занята передачей сообщений от других источников. Тогда триггеры 282, 283, 302, 303 пусконачинающего блока 4 находятся в нулевом состоянии, вследствие чего срабатывают элемент И 291, триггер 301 и на выходе 341 пусконачинающего блока 4 появляется сигнал разрешения обработки сообщения 1-го источника.

Под действием указанного сигнала в формирователе 6 адреса (фиг. 5) с помощью шифратора 45 двоичного кода формируется параллельный код 01 адреса 1-го источника, а в блоке 13 оценки состояний канала (фиг. 11) закрывается элемент И 741 и на одном из выходов регистра 751 сдвига фиксируется сигнал "1". Пусть этот сигнал зафиксирован на 3-м выходе регистра 751. Это означает, что для передачи сообщения от 1-го источника в данный момент времени будет использоваться 2-й код - код с параметрами N2=11, D2=4 и образующим полиномом G2(X)= X5+X4+X2+1. Сигнал, определяющий номер кода, поступает с 3-го выхода регистра 751 сдвига через элементы ИЛИ 7612, И 7712, ИЛИ 782 на выход 492 блока 13 оценки состояний канала.

Под действием указанного сигнала в блоке 9 генераторов частот (фиг. 7) выбирается соответствующий 2-му коду генератор 522 несущей частоты и гармоническое колебание с соответствующей частотой поступает на вход 55 блока 14 согласования передающего устройства системы. Кроме того, на выходах 511-517 шифратора 8 полинома (фиг. 6) формируется набор сигналов 0010101, используемый для коммутации цепи обратной связи в схеме деления блока 12 кодирования. Также сигнал о номере кода подготавливает элемент И 612 перестраиваемого распределителя 10 (фиг. 8), определяя тем самым число тактов работы (25 тактов) передающего устройства.

По переднему фронту сигнала разрешения обработки сообщения 1-го источника на выходе 35 пусконачинающего блока 4 формируется сигнал, устанавливающий в единичное состояние триггер 57 перестраиваемого распределителя 10 (фиг. 8), и по переднему фронту очередного тактового импульса в первую ячейку регистра 58 сдвига записывается единица. Сигнал с выхода первой ячейки устанавливает триггер 57 в нулевое состояние, обеспечивая тем самым выполнение регистром сдвига функции распределителя (появление в любой момент времени сигнала "1" только на одном из выходов распределителя). Тактовые импульсы, обеспечивающие продвижение единицы по регистру, поступают на вход 56 перестраиваемого распределителя 10 от генератора 7 тактовых импульсов.

Сигналы с выходов 59 и 60 перестраиваемого распределителя 10, вырабатываемые соответственно на 1-м и 3-м тактах, используются в формирователе 11 синхросигнала (фиг. 9) для формирования с помощью триггера 63 импульса, длительность которого в два раза превышает длительность элементарного сигнала. Указанный синхросигнал поступает на вход 64 блока 14 согласования (фиг. 12) и после преобразований, выполняемых модулятором 80 и полосовым фильтром 81, через канальный выход 15 в канал связи.

Сигналы с выходов 441, 442 перестраиваемого распределителя 10, вырабатываемые соответственно на 4-м и 5-м тактах, используются в формирователе 6 адреса (фиг. 5) для преобразования с помощью элементов И 461, 462 и элемента ИЛИ 47 параллельного кода 01 адреса 1-го источника в последовательный код, поступающий на вход 48 блока 12 кодирования.

На 6-м такте перестраиваемый распределитель 10 выдает на выход 36 сигнал разрешения приема информационных разрядов сообщения источника, устанавливающий в единичное состояние триггер 38 коммутатора 5 (фиг. 4). Сигналом с прямого выхода триггера 38 совместно с сигналом разрешения обработки сообщения 1-го источника на входе 341 с помощью элемента И 401 на выходе 31 коммутатора 5 формируется сигнал разрешения передачи информации от 1-го источника. В результате в течение 4-х тактов (с 6-го по 9-й) информационные разряды 1010 сообщения в последовательном коде поступают на вход 21 коммутатора 5 и через элементы И 391, ИЛИ 41, И 42 на вход 43 блока 12 кодирования.

В течение 6 тактов (с 4-го по 9-й) происходит выдача информационных символов 011010, поступающих в блок 12 кодирования (фиг. 10) с входов 48 и 43, через элементы ИЛИ 70, 71 на выход 72; одновременно в блоке 12 кодирования происходит вычисление контрольных символов 10000 кодовой комбинации, при этом схема деления на образующий полином G2(X) = X5 + X4 + X2 + 1 реализована на триггерах 675-679 и сумматорах 662, 664 и 666 по модулю два.

На 10-м такте перестраиваемый распределитель 10 выдает на выход 37 сигнал выдачи контрольных разрядов. Указанный сигнал устанавливает в нулевое состояние триггер 38 коммутатора 5, вследствие чего с выхода 31 коммутатора снимается сигнал разрешения передачи информации от 1-го источника, после чего 1-й источник снимает сигнал запроса передачи с входа 11 пусконачинающего блока 4, а входы 21-23 коммутатора 5 отключаются от его выхода 43. Сигнал выдачи контрольных разрядов также переключает в блоке 12 кодирования (фиг. 10) ключ управления, собранный на триггере 68 и элементах И 691, 692, и в течение 5 тактов (с 10-го по 14-й) контрольные символы 10000 поступают из триггеров 675-679 через сумматор 667, элементы И 692, ИЛИ 71 вслед за информационными на выход 72 блока 12 кодирования.

Символы 01101010000 кодовой комбинации (информационные и контрольные) с выхода 72 блока 12 кодирования поступают в блок 14 согласования (фиг. 12) и после преобразований, выполняемых модулятором 80 и полосовым фильтром 81, через канальный выход 15 - в канал связи.

На 25-м такте (по переднему фронту) перестраиваемый распределитель 10 выдает через элементы И 612, ИЛИ 62 на выход 27 сигнал сброса. Под действием указанного сигнала устанавливаются в нулевое состояние триггеры 671-679, 68 блока 12 кодирования, регистр 58 сдвига перестраиваемого распределителя 10, а также триггеры 281 и 301 пусконачинающего блока 4 (фиг. 3). При этом с выхода 341 пусконачинающего блока снимается сигнал разрешения обработки сообщения от первого источника, после чего с выхода 492 блока 13 оценки состояний канала снимается сигнал, определяющий номер используемого для передачи кода. Передающее устройство системы готово к приему сообщения от I-го, I=1,B, источника, его кодированию и передаче по каналу связи.

В приемном устройстве системы сигнал с канального входа 16 поступает в блок 17 согласования (фиг. 13), где осуществляется его фильтрация и демодуляция, и в блок 18 дешифратора частот (фиг. 14), где с помощью полосового фильтра 852 и триггера Шмитта 862 определяется диапазон частот, в котором ведется передача. Номер диапазона определяет в свою очередь номер используемого для передачи кода. Сигнал, несущий информацию о номере кода, формируется с помощью RS-триггера 872 и поступает на выход 882 дешифратора частот. Указанный сигнал подготавливает элементы И 1022, 1032 перестраиваемого распределителя 21 (фиг. 17), определяя тем самым такт начала этапа исправления ошибок (12-й такт) и число тактов работы (22 такта) приемного устройства. Кроме того, сигнал о номере кода подготавливает элемент И 222, разрешая прием декодирующим блоком 232 кодовой комбинации, поступающей с выхода 84 согласующего блока 17.

Одновибратор 90 селектора 19 синхросигнала (фиг. 15) вырабатывает импульс, длительность которого равна длительности синхросигнала, поэтому по заднему фронту синхросигнала на выходе 94 селектора появляется сигнал запуска. Указанный сигнал устанавливает в единичное состояние RS-триггер 96 блока 20 генератора тактовых импульсов (фиг. 16), разрешая тем самым работу двоичного счетчика 97 вычитающего типа, выполняющего функцию делителя частоты. Разрядность счетчика определяет величину максимального рассогласования по фазе тактовых импульсов передающего и приемного устройств системы. Так, для приведенного на фиг. 16 четырехразрядного счетчика максимальное рассогласование составит 6%, при этом частота импульсов, вырабатываемых генератором 95, должна в 16 раз превышать частоту тактовых импульсов, т.е. fВЧ = 16fТИ. Кроме того, под действием сигнала запуска в перестраиваемом распределителе 21 (фиг. 17) с помощью цепочки элементов, состоящей из RS-триггера 991, формирователя 100 сигналов переднего фронта импульсов и RS-триггера 992, осуществляется запись единицы в регистр 101 сдвига тактовым импульсом, соответствующим 4-му тактовому импульсу в передающем устройстве. Таким образом, 1-й такт работы перестраиваемого распределителя 21 приемного устройства соответствует 4-му такту работы перестраиваемого распределителя 10 передающего устройства.

В течение первых 11 тактов работы перестраиваемого распределителя 21 происходит запись принятой комбинации в буферный регистр 1092 сдвига декодирующего блока 232 (фиг. 18) и вычисление синдрома в схеме деления на образующий полином G2(X) = X5 + X4 + X2 + 1, реализованный на D-триггерах 11412-11452 и сумматорах 11312-11352 по модулю два. Пусть при передаче по каналу связи произошли искажения, в результате которых кодовая комбинация на выходе блока 17 согласования имеет вид 01101110000, т.е. содержит одиночную ошибку. Тогда синдром принятой комбинации равен 10101.

На 12-м такте перестраиваемый распределитель 21 выдает на выход 1042 сигнал начала этапа исправления ошибок, устанавливающий в единичное состояние RS-триггер 1102 декодирующего блока 232. В результате выход селектора синдромов исправляемых ошибок, реализованного на элементе И 1162, подключается к второму входу сумматора 1122, в котором на 17-м такте работы перестраиваемого распределителя 21 происходит исправление ошибки. На 18-м такте триггеры 114 вычислителя синдрома устанавливаются в нулевое состояние сигналом обратной связи с выхода элемента И 1162.

На 23-м такте перестраиваемый распределитель 21 выдает на выход 1052 сигнал завершения этапа исправления ошибок, опрашивающий селектор нулевого синдрома, реализованный на элементе И 1152. В результате на выходе 1192 декодирующего блока 232 формируется сигнал, разрешающий работу дешифратора 122 двоичного кода, входящего в дешифратор 124 адреса (фиг. 19). На информационные входы 11712 и 11722 дешифратора 24 адреса поступает параллельный код 01 адреса первого источника с соответствующих выходов декодирующего блока 232.

В свою очередь на выходе 1231 дешифратора 24 адреса формируется сигнал записи в регистр 1251 блока 25 выдачи данных (фиг. 20) разрядов 1010 сообщения, поступающих в параллельном коде на входы 11812-11842 с соответствующих выходов декодирующего блока 232. В итоге сообщение с выходов 2611-2614 блока 25 выдачи данных поступает к 1-му получателю информации.

На 23-м такте с небольшой задержкой во времени перестраиваемый распределитель 21 выдает на выход 89 сигнал сброса. Указанный сигнал устанавливает в нулевое состояние триггер 96 в блоке 20 генератора тактовых импульсов (фиг. 16). Сигнал с инверсного выхода триггера 96 запрещает работу двоичного счетчика 97, в результате чего прекращается выдача тактовых импульсов в схему приемного устройства системы. Сигнал сброса также устанавливает в нулевое состояние триггер 872 в дешифраторе 18 частот, регистр 1092 сдвига, и триггер 1102 в декодирующем блоке 232, и триггер 991, и регистр 101 сдвига в перестраиваемом распределителе 21. Приемное устройство системы готово к приему сообщения из канала связи, его декодированию и выдаче 1-му получателю.

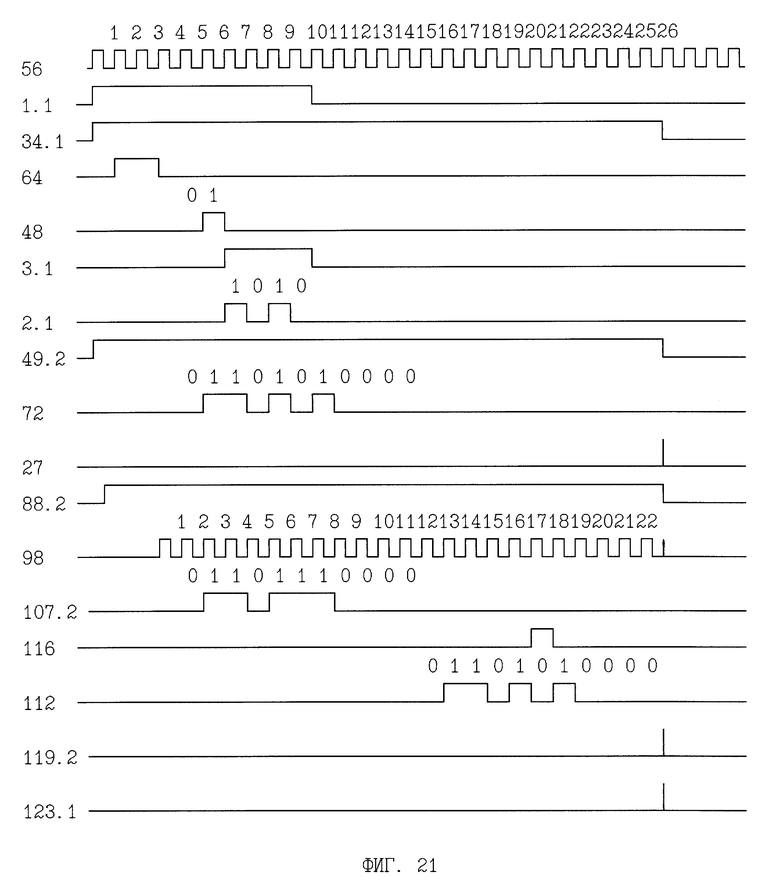

Временная диаграмма работы системы для рассматриваемого примера приведена на фиг. 21.

Технико-экономическую эффективность предлагаемой системы передачи и приема информации кодом переменной длины по отношению к известной системе (см. авт. свид. СССР N 1109927, М. кл. H 04 L 5/22, опубликованное в офиц. бюлл. БИ N 31 от 23.08.84) возможно оценить из уменьшения коэффициента использования канала связи.

Коэффициент R использования канала связи определяет долю времени, в течение которой канал занят передачей сообщений. Очевидно, что для известной системы R=1.

Для предлагаемой системы

где

AI - интенсивность потока сообщений I-го источника (сооб./ед. врем);

TI - время передачи сообщения I-го источника (ед. врем/сооб.).

Для многих систем передачи информации (например, систем телемеханики) выполняется

Экономическая эффективность Э за время T при известной стоимости C использования канала в единицу времени составит $

$

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО АДАПТИВНОГО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ | 2000 |

|

RU2169431C1 |

| Устройство декодирования циклических кодов | 1990 |

|

SU1735996A2 |

| УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА | 1999 |

|

RU2152072C1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Адаптивная система передачи информации | 1983 |

|

SU1109927A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 2000 |

|

RU2182359C2 |

| МНОГОКАНАЛЬНЫЙ ПАНОРАМНЫЙ ПРИЕМНИК | 1996 |

|

RU2115997C1 |

| УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА | 1993 |

|

RU2087939C1 |

| НЕЧЕТКИЙ ВЕРОЯТНОСТНЫЙ АВТОМАТ | 1995 |

|

RU2110090C1 |

| УСТРОЙСТВО ДЛЯ УЧЕТА ЭЛЕКТРОЭНЕРГИИ | 1997 |

|

RU2125269C1 |

Изобретение относится к области техники связи и может быть использовано в телемеханике, телеметрии, при передаче данных по каналам связи кодами различной корректирующей способности, что отвечает выполнению различных требований по уровням достоверности передачи сообщений от различных источников. Технический результат от применения изобретения заключается в уменьшении коэффициента использования канала связи за счет перехода от циклического к спорадическому режиму передачи информации. что позволяет увеличить количество источников и получателей сообщений, передающих информацию по выделенному каналу. Для достижения технического результата в систему для передачи и приема информации кодом переменной длины, содержащую на передающей стороне коммутатор 5, генератор тактовых импульсов 7, шифратор полинома 8, блок генераторов частот 9, перестраиваемый распределитель 10, блок кодирования 12, блок оценки состояния канала 13, блок согласования 14, а на приемной стороне -блок согласования 17, дешифратор частот 18, перестраиваемый распределитель 21, элементы И 221-22н, декодирующие блоки 231-23н, блок выдачи данных 25, дополнительно введены на передающей стороне пусконачинающий блок 4, формирователь адреса 6 и формирователь синхросигнала 11, а на приемной стороне - селектор синхросигнала 19, блок генератора тактовых импульсов 20 и дешифратор адреса 24. 21 ил.