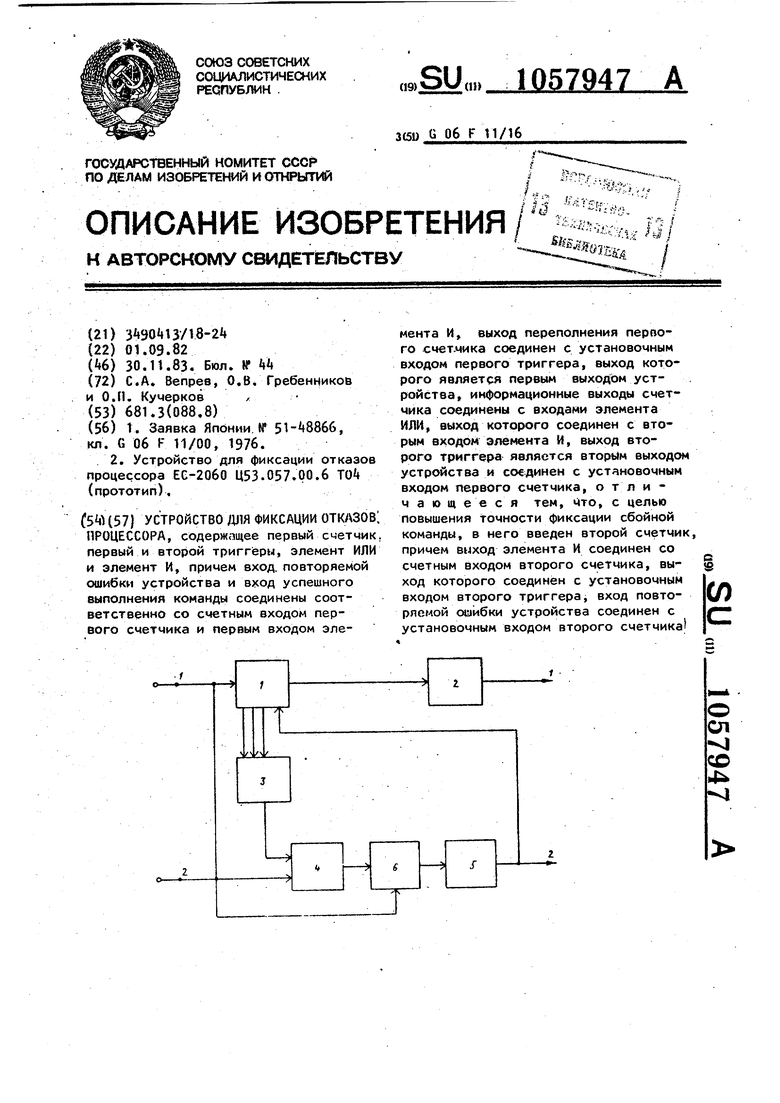

Изобретение относится к вычислительной технике и может быть использовано в электронных вычислительных машинах, в которых выполнение команды совмещено во времени с предварительной обр-лботкой нескольких последующих команд и имекнцих возможность аппаратного повторения в несовмещенном режиме выполняемой или выполненной команды при возникновении сбоев в процессоре. Известно устройство для фиксации отказов, входящее в состав системы для повторного выполнения команд, со д(;ржащее блок сравнения адресов повторенной и обрабатываемой команды, олок формирования сигнала отказа и блок управления 11 .. Недостатком устройства является ограниченная область применения толь ко для вычислительных машин, не совмещающих во времени обработку нескол ких команд„ Наиболее близким по технической сущности к предлагаемому является устройство для фиксации отказов процессора, содержащее триггер тяжелой ошибки, триггер прерывания по легкой ошибке, счетчик повторений, элемент элемент ИЛИ„ Счетный вход счетчика повторений является первым входом устройства, выходной сигнал переполнения счетчика повторений поступает на вход триггера тяжелой ошибки, выход которого является первым выходом устройства, информационные выходы с счетчика повторений соединены с входами элемента ИЛИ, выход которого со единен с первым входом элемента И, виход которого в свою очередь соединен с входом триггера прерываний по легкой ошибке, выход триггера прерываний по легкой ошибке является вторым выходом устройства, а второй вхо элемента И является вторым входом устройства. 1ри поступлении на первый вход устройства сигнала повторяемой ошибки от схем контроля процессора содер жимое счетчика повторений увеличивается на единицу При переполнении счетчика повторений устанавливается в единицу триггер тяжелой ошибки, выходной сигнал которого идентифицирует неотложное условие прерывания от схем контроля. При поступлении на второй вход устройства сигнала успеш ного выполнения команды в режиме повторения устанавливается в единицу триггер прерывания по легкой ошибкъ, выходной сигнал которого идентифицирует ожидающее условие прерывания от схем контроля и устанавливает в ноль счетчик повторений fz Недостатком устройства является невозможность фиксации отказов при возникновении ошибки, фиксируемой во время обработки одной из команд, что приводит к ошибочной установке три1- гера прерываний по легкой ошибке и зацикливанию процессора, тем самым время фиксации отказа становится неограниченно велико Команды в процессоре могут находиться на одном из уровней обработки или на уровне выполнения- Зацикливание происходит в силу того, что аппаратные средства повторения команд используют минимальное количество оборудования с целью запоминания : информации, необходимой для повторения одной из команд, а именно команды, которая последней находилась на уровне выполнения., Поэтому при возникновении ошибки, фиксируемой во время обработки одной из команд, повторно выполняется предыдущая команда, выполнение которой началось или завершилось., В этом случае в зависимости от состояния маски прерывания от схем контроля по легкой ошибке возможны следующие два варианта зацикливания процессора, совмещающего обработку k команд, при возникновении ошибки, фиксируемой на { -м уровне п-и команды„ Если маска прерывания по легкой ошибке закрыта, то зацикливание происходит по алгоритму: успешное повторение ti-k+i-й команды в несовмещенном режиме, сброс счетчика повторений, дальнейшая обработка команд программы, ошибка при обработке на i-м уровне и-и команды, успешное повторение П -k--i-й команды и ТоД„ Если маска прерывания по легкой сниибке открыта, то зацикливание происходит по алгоритму: успешное повторение И -k+i-й команды в несовмещенном режиме, сброс счетчика повторений, выполнение программы обработки прерывания от схем контроля, дальнейшая обработка текущей программы, начиная с команды + 1 , ошибка при обработке на -м уровне П-й команды, успешное повторение последней команды программы прерывания от схем контроля, сброс счетчика повторений, выполнение программы обработки прерывания от схем контроля и т.д.. Последний алгоритм зацикливания возможен при возникновении ошибок, фиксируемых при обработке команд, не используемых в программе обработки прерывания от схем контроля, Оба алгоритма зацикливания допускают обработку прерываний всех классов согласно приоритету с последующим входом обратно в цикло Цель изобретения - повышение точности фиксации сбойной команды. Поставленная цель достигается тем что в устройство, содержащее первый счетчик, первый и второй триггеры, элемент ИЛИ, элемент И, причем вход повторяемой ошибки устройства и вход успешного выполнения команды соединены соответственно со счетным входом первого счетчика и первым входом элемента И, выход переполнения первого счетчика соединен с установочным входом первого триггера, выход которого является первым выходом устройст ва, информационные выходы счетчика соединены с входами элемента ИЛИ, выход которого соединен с вторым входом элемента И, выход второго триггера является, вторым выходом устройства и соединен с установочным входом пер вого счетчика, введен второй счетчик причем выход элемента И соединен со счетным входом второго счетчика,выход которого соединен с установочным входом второго триггера, вход повторяемой ошибки устройства соединен с установочным входом второго счетчика Таким образом, второй счетчик блокирует установку в единицу второго триггера при поступлении первого си1- нала успешного выполнения команды на второй вход устройства, тем самым не допуская ложного формирования на втором выходе устройства сигнала, идентифицирующего ожидающее условие преры вания от схем контроля при наличии отказа в оборудовании процессора, В этом случае процессор не обрабатывает ложные запросы на прерывание, исключается зацикливание процессора и время фиксации отказа уменьшается. На чертеже приведена структурная схема устройства для фиксации отказо процессора Устройство содержит первый счетчик 1, первый триггер 2, элемент . ИЛИ 3, элемент И k, второй триггер 5 второй счетчик 6, Счетный вход первого счетчика 1 соединен с входом установки в ноль второго счетчика 6 и является первым входом устройства, выход переполнения первого счетчика 1 подключен к входу первого триггера 2, выход которого является первым выходом устройства, информационные выходы первого счетчи ка 1 соединены с входами элемен- . та ИЛИ 3, выход которого соединен с первым входом элемента И 4. Выход элемента И Л соединен со счетным уходом второго счетчика 6, выход переполнения которого подключен к входу второго триггера 5, выход которого является вторым выходом устройства и соединен с входом установки в ноль первого счетчика 1, второй вход элемента И k является вторым входом устройства. Цепи установки в ноль три|- геров и счетчиков при включении питания условно не показаны. Устройство работает следующим образом. При поступлении на первый вход устройства сигнала повторяемой ouJибки от схем контроля процессора содержимое первого счетчика 1 увеличивается на единицу. При переполнении первого счетчика 1 устанавливается в единицу первый триггер 2, выходной сигнал которого поступает в процессор, идентифицируя неотложное условие прерывания от схем контроля. В режиме повторения содержимое первого счетчика не равно нулю, при этом с выхода элемента ИЛИ 3 на вход элемента И А поступает сигнал логической единицы, При поступлении на второй вход устройства си| нала успешного выполнения команды в режиме повторения содержимое второго счетчика 6 увеличивается на единицуо При переполнении второго счетчика 6 устанавливается в единицу второй триггер 5, выходной сигнал которого поступает в процессор, идентифицируя ожидающее условие прерывания от схем контроля. Ожидающее условие прерывания от схем контроля возникает только в том случае, если после повторения одной из команд успешно выполнены команды, находившиеся на уровнях обработки в момент первичного возникновения сигнала ошибки. В этом случае процессор не обрабатывает ложные запросы на прерывание, что исключает его зацикливание. В ином случае по переполнению первого счетчика 1 эафикси- руется неотложное условие прерывания от схем контроля, т.е. отказ процессора.

Устройство позволяет фиксировать любые отказы в контролируемом оборудовании процессора.

Таким образом, изобретение путем точного указания сбойной команды

уменьшает время нахоедения ЭВМ в ре «име циклического повторения сбойной команды.

Экономический эффект от исполь зования предлагаемого изобретения состоит в сокращении времени беспо- . лезной работы ЭВМ в режиме цикличес|кого аппаратного повторения команд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для восстановления процессора после сбоя | 1979 |

|

SU857999A1 |

| Устройство для контроля хода программ | 1989 |

|

SU1645959A1 |

| Устройство для контроля времени выполнения программы | 1983 |

|

SU1140124A1 |

| Устройство для контроля времени выполнения программ | 1979 |

|

SU928360A1 |

| Устройство для контроля хода программ | 1983 |

|

SU1101831A1 |

| Дублированная вычислительная система | 1990 |

|

SU1783528A1 |

| Устройство для контроля выполнения программ на эвм | 1986 |

|

SU1383371A1 |

| Генератор тестовой псевдослучайной двоичной последовательности | 1987 |

|

SU1640699A1 |

| Устройство для контроля хода программы и перезапуска ЭВМ | 1985 |

|

SU1337901A1 |

| Устройство для контроля следования модулей программы | 1985 |

|

SU1249521A1 |

УСТРОЙСТВО /ДЛЯ ФИКСАЦИИ ОТКАЗОВ; ПРОЦЕССОРА, содержащее первый счетчик, первый и второй триггеры, элемент ИЛИ и элемент И, причем вход, повторяемой ошибки устройства и вход успешного выполнения команды соединены соответственно со счетным входом первого счетчика и первым входом элемента И, выход переполнения первого счет-чика соединен с установочным входом первого триггера, выход которого является первым выходом устройства, информационные выходы счетчика соединены с входами элемента ИЛИ, выход которого соединен с вторым входом элемента И, выход второго триггера является вторым выходом устройства и соединен с установочным входом первого счетчика, о т л и чающееся тем, , с целью повышения Точности фиксации сбойной команды, в него введен второй счетчик, причем выход элемента И соединен со I счетным входом второго счетчика, выход которого соединен с установочным (Л входом второго триггера, вход повторяемой оаибки устройства соединен с установочным входом второго счетчика ел со 4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Заявка Японии | |||

| № , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Прибор для промывания газов | 1922 |

|

SU20A1 |

Авторы

Даты

1983-11-30—Публикация

1982-09-01—Подача