t

Изобретение относится к вычисли- . тельной технике и предназначено для организации восстановления в случае сбоев в процессорах, использующих микропрограммный принцип управления.

Известно устройство восстановления процессора путем повторения команд при сбое, которое содержит специальные регистры хранения, в которых запоминается информация,необходимая для повторения команды.. Для запоминания факта изменения операндов во время выполнения команд устройство содержит триггер изменения исходных данных, который устанавливается при выполнении микрокоманд записи результатов и указывает, что операнды команды могут измениться. Значение триггера определяет действия, необходимые для повторения команды

Недостатком известного устройства является то, что оно требует дополнительных затрат оборудования для сохранения необходимой информации в случае невозможности повторения команды (выполнялась системная операция - прорывание, обновление таймера и т.д.).

Известно также устройство восстанонлени.ч процессора путем повторения

2

микрокоманд при сбое, содержащее специальные регистры повторенияig запоминающие адрес сбойной микрокоманды, операнды микрооперации и дополнительную информацию, необходимую для повторения. В случае фиксации сбоя в узле контроля осуществляется переход на микропрограмму повторения сбойной микрокоманды 2.

10

Недостатком этого устройства является малая эффективность восстановления сбоев, так как бработка сбоя начинается сразу же после фиксации его в узле контроля устройства, и .

15 также потеря управления в случае постоянного сбоя.

Наиболее близким техническим решением к предлагаемому изобретению является устройство для восстановления

20 процессора после сбоя, содержащее блок микропрограммного управления и синхронизации, блок обработки данных, узел контроля и узел микропрограммных прерываний, первый выход которого

25 соединен с первым входом блока микропрограммного управления и синхронизации , первый и второй выходы которого соединены с первым и вторым входами узла контроля, третий вход которого соединен с первым выходом блока

30

обработки, а первый выход узла контроля соединен с первым входом узла микропрограммных прерываний 3.

Недостатком устройства является низкая эффективность восстановления, так как условия, вызвавшие сбой (изменение питающих напряжений, контактные явления и т.д.), имеют время действия, большее чем рабочий цикл про дессора. Поэтому обработка сбоя сразу же может привести к неповторяемой ситуации. Кроме этого, устройст-во может привести к потере управления в случае зацикливания микропрограммы повторения из-за наличия постоянного сбоя в процессоре.

Целью изобретения является повышение надежности и расширение функциональных возможностей устройства за счет обеспечения процесса восстановления с различным напряжением питания.

Поставленная цель достигается тем что в устройство для восстановления процессора после сбоя, содержащее блок микропрограммного управления, синхронизатор, блок обработки данных блок контроля я блок формирования адреса микрокоманд, причем первый,второй и третий выходы блока микропрограммного управления соединены соответственно с первым и вторьйч входом блока контроля и с первым входом блока обработки данных, выход которого соединен с третьим входом блока контроля, первый аыход блока контроля соед4 нен с первым входом блока формирования адреса микрокоманд, первый выход которого соединен с первым входом блока микропрограммного управления, введены первый и второй счетчики, первый и второй дешифраторы, первый и второй триггеры, элемент И, регистр, индикатор отклонен .я напряжения питания, причем выход элемента И соединен с первым входом первого триггера, выход которого соединен с входом синхронизатора, четвертый и пятый выходы блока микропрограт-много управления соединены соответственно с первым входом второго триггера и с первым входом второго счетчика,второй выход блока контроля соединен с nepBbBvi входом элемента И и с вторым входом второго триггера, выход которого соединен с вторым входом элемента и, выход синхронизатора соединен с первым входом первого счетчика выход которого соединен с первым входом первого дешифратора, выход которого соединен с вторыми входами первого счетчика и первого триггера, первый вход устройства соединен с входом индикатора отклонения напряжения питания, выход которого соединен с вторым входом первого дешифратора , второй выход блока формирования адреса микрокоманд соединен с вторым входом второго счетчика, вы.ход которого соединен с входом вто рого дешифратора, выход второго дешифратора соединен с вторьм входом блока формирования адреса микрокоманд, второй выход блока обработки данных соединен с первым входом регистра, первый и второй выходы которого соединены соответственно с первьам выходом устройства и вторым входом блока обработки данных.

Кроме того, блок микропрограммного управления содержит блок памяти микрокоманд, .регистр микрокоманд и дешифратор микрокоманд, причем первый вход блока памяти микрокоманд соединен с входом блока, вь1ход блока памяти микрокоманд соединен с первым входом регистра микрокоманд, первый, ,второй и третий выходы которого соединены соответственно с первые выходом блока, с вторым входом блока памяти микрокоманд, с входом дешифратор микрокоманд, первый, второй, трбтий и четвертый выходы дешифратора микрокоманд являются соответственно вторым, третьим, четвертым и пятым выходами блока.

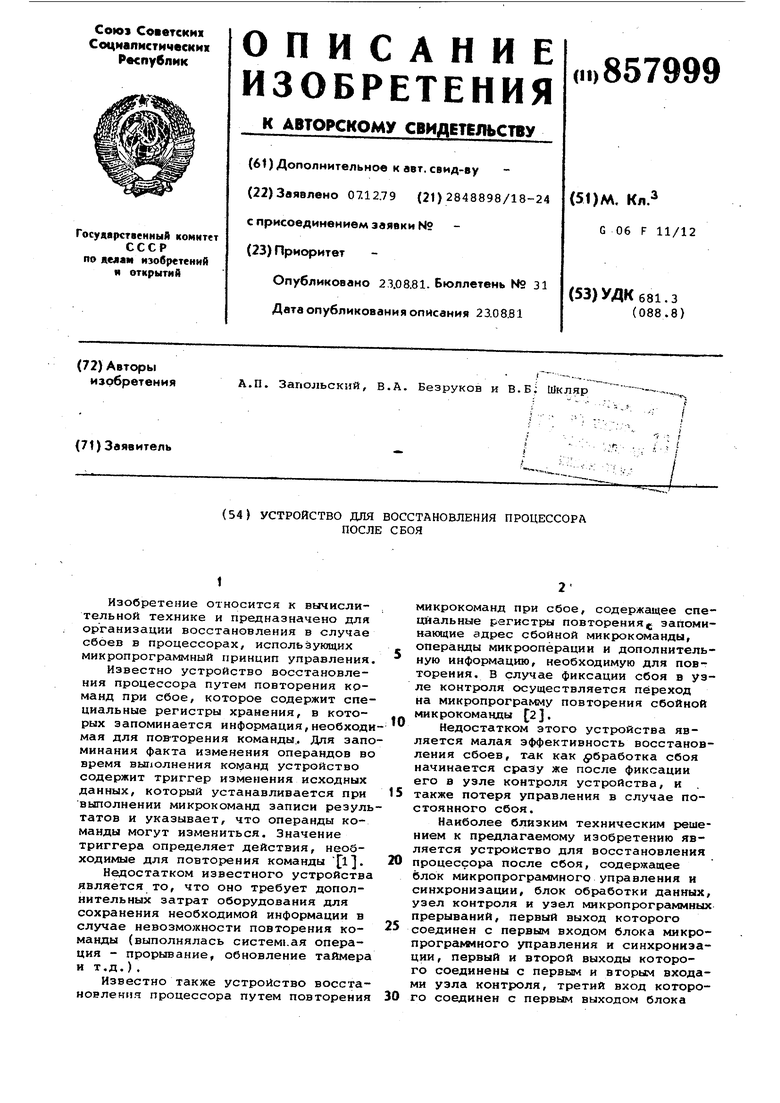

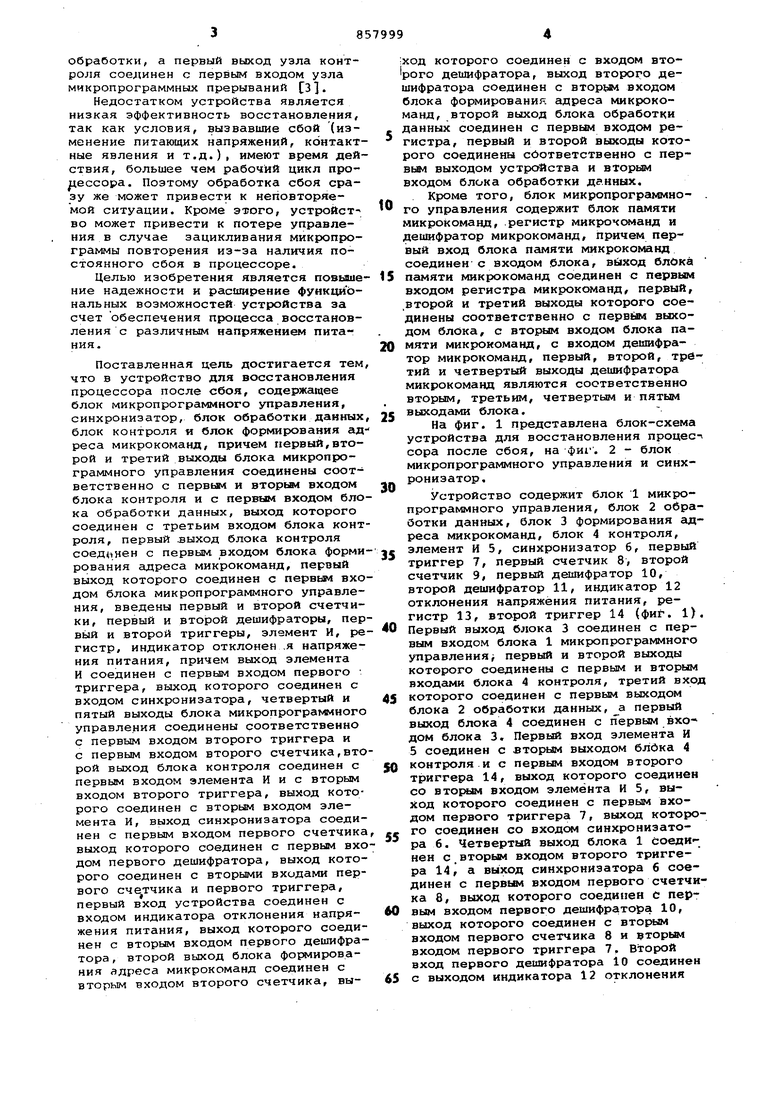

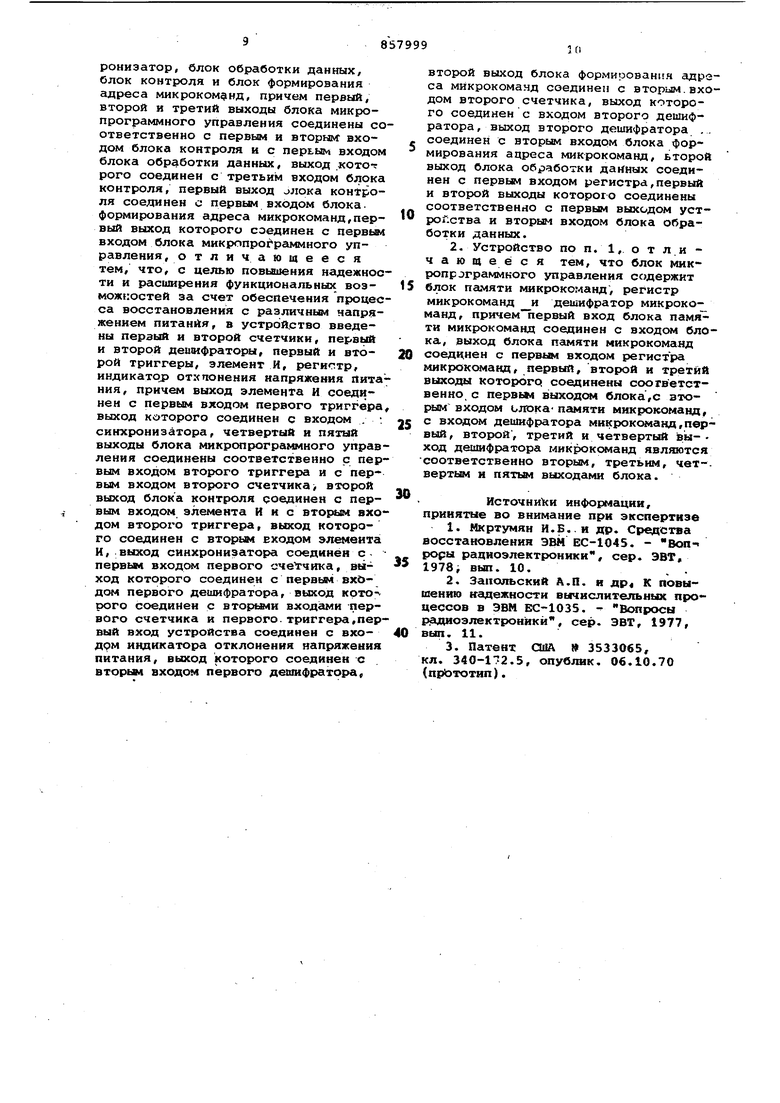

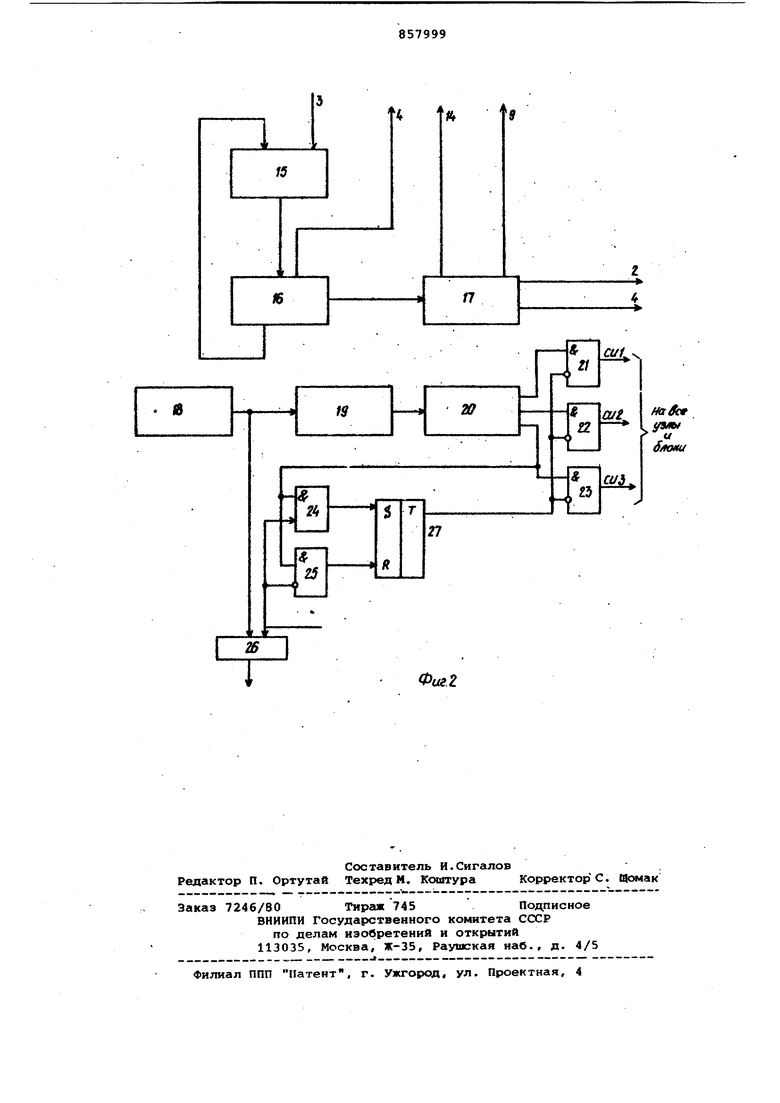

На фиг. 1 представлена блок-схема устройства для восстановления процес сора после сбоя, на . 2 - блок микропрограммного управления и синхронизатор.

Устройство содержит блок 1 микропрограммного управления, блок 2 обработки данных, блок 3 формирования адреса микрокоманд, блок 4 контроля, элемент И 5, синхронизатор 6, первый триггер 7, первый счетчик 8, второй счетчик 9, первый дешифратор 10, второй дешифратор 11, индикатор 12 отклонения напряжения питания, регистр 13, второй триггер 14 (фиг. 1) Первый выход блока 3 соединен с первым входом блока 1 микропрограммного управленияj первый и второй выходы которого соединены с первым и вторым входами блока 4 контроля, третий вхо которого соединен с первым выходом блока 2 обработки данных, а первый выход блока 4 соединен с гГервым входом блока 3. Первый вход элемента И 5 соединен с вторым выходом блдка 4 контроля.и с первым входом второго триггера 14, выход которого соединен со BTOixjM входом элемента И 5, выход которого соединен с первым входом первого триггера 7, выход которого соединен со входом синхронизатора 6. Четвертый выход блока 1 соеди нен с вторым входом второго триггера 14j а выход синхронизатора 6 соединен с первьм входом первого счетчика 8, выход которого соединен с первым входом первого дешифратора 10, выход которого соединен с вторым входом первого счетчика 8 и эторьм входом первого триггера 7. Второй вход первого дешифратора 10 соединен с выходом индикатора 12 отклонения напряжения питания, вход которого соединен с устройством питания процессора, которое соединено с первым выходом регистра 13, осуществляющего управление выходным напряжением пита ния процессора, второй выход и вход регистра 13 соединены соответственно с вторым входом и вторым выходом бло ка 2 обработки данных, первый вход которого соединен с ретьим выходом блока 1 микропрограммного управления пятый выход которого соединен с первым входом второго счетчика 9, второй вход-которого соединен с вторым выходом блока 3, второй вход которого соединен с выходом второго дешифратора 11, вход которого соединен с выходом второго счетчика 9. Блок 1 микропрограммного управления вырабатывает управляющие сигналы для всего устройства. Блок микропрограммного управления и синхронизатор (фиг. 2) содержит блок 15 памяти мик рокоманд, регистр 16 микрокоманд и дешифратор 17 микрокоманд, генератор 18, счетчик 19, дешифратор 20, элементу И 21-26 и триггер 27 запуска синхронизации. Выход генератора 18 соединен с входом элемента И 26 и счетчиком 19, выход которого соединен с дешифратором 20, первый выход которого соединен с первым входом элемента И 21, второй выход, соединен с первым входом элемента И 22, третий выходсоединен с первыми входами элементов И 23-25, вторые входы элементов И 21-23 соединены с выходом триггера 27 запуска синхронизаци первый вход которого соединен с выходом элемента И 24, второй вход которого соединен с выходом триггера 7 останова синхронизации и вторыми входами элементов И 25 и 26, выходы которых соединены соответственно с вторым входом триггера 27 запуска синхронизации .и выходом синхронизато ра, вход дешифратора 17 микрокоманд соединен с выходом регистра 16 микрокоманд , второй выход которого соединен с входом блока 15, выход Которого соединен с входом регистра 16, а второй вход соединен с блоком 3, первый, второй, третий и четвертый выходы дешифратора 17 соединены соот ветственно с блоком 4 контроля, блоком 2 обработки данных, вторым счетчиком 9 и вторым триггером 14 режима повторения, регистр 16 микрокоманд соединен с блоком 4 контроля. Выходы элементов И 21-23 соединены с всеми блоками и узлами устройства. Элементы И 21-23 вырабатывают синхросигналы СИ1, СИ2 . и СИЗ. Блок 3 формирования адреса микрокоманд предназначен для выработки начального адреса входа микропрограм много прерывания, который использует ся для считывания микрокоманды из па мятг микропрограмм 15 в регистр микрокоманд 16 (фиг. 2), и содержит регистр адреса, формироьатоль адреса и два элемента И. Блок 2 обработки данных предназначен для обработки информации под управлением блока 1. в состав блока 7 входит память, в которой хранится обрабатываемая информация и промежуточные результаты, узел арифметическо-логических операций, который осуществляет необходимые действия по обработке информации. Блок 4 контроля предназначен для контроля правильности функционирования блока 2 обработки данных ,с блока 1 и блока 6 и выработки суммарного сигнала ошибки. Блок 4 контроля состоит из элементов сложения по модулю два, элемента ИЛИ и регистра ошибок. Регистр 13 управления выходным напряжением питания предназначен для управления выходным напряжением вторичных источников питания процессоров. Выход регистра 13 соединён с устройством питания процессора, другой выход соединен с блоком 2 обработки данных, а вход соединен с блоком 2 обработки данных. Регистр 13 доступен микропрограмме и состоит из адресной части - адреса вторичного источника питания и управления режимом профконтроля, содержащего два бита: 00 напряжение вторичного источника питания номинально . , 01 напряжение вторичного источника питания, отличается на -5% от номинала, 10 - напряжение вторичного источника питания, отличается на +5% от номинала . Первый триггер 7 останова синхронизации предназначен для управления режимом работы процессора (при установке триггера процессор переходит в состояние Останов). Второй триггер 14 режима повторения предназначен для фиксации обработки ошибки (т.е. индицирует нахождение в микропрограмме повторения) и определяет реакцию устройства на ошибку. Индикатор 12 отклонения напряжения ; питания представляет собой триггер, который устанавливается в случае выхода напряжения питания процессора за определенные рамки (+5%) от номинала и сбрасывается в противном случае. Устройство работает следующим образом. Сбой, возникший в одном из блоков устройства, обнаруживается блоком 4 контроля и поступает на вход элемента И 5 и второго триггера 14 режима повторения, устанавливая его, одновременно происходит установка и первого триггера 7 останова синхронизации, выход которого поступает в блок 6 на входы элементов И 24,25, 26. В конце выполнения микрокоманды (по

последнему синхроимпульсу СИЗ) устанавливается триггер 27 запуска синхронизации, блокируя выдачу синхросигналов элементами И 21-23, тем самым процессор переводится в состояние Останов. Сигнал с выхода триггера 7 поступает на вход элемента И 26, разрешая прохождение сигнала генератора 18 через элемент И 26 на 1ервый счетчик 8. После достижения заданного значения первого счетчика, при отсутствии установленного индикатора 12, первый дешифратор 10 вырабатывает сигнал, сбрасывающий первый счетчик 8 в исходное состояние и первый триггер 7, тем самым разрешая сброс триггера 27 по сигналу из дешифратора 20. После сброса триггера 27 разреишется выдача синхроимпульсов элементами И 21-23, т.е. процессор переводится в состояние Работа

Если индикатор 12 установлен,первый децифратор 10 вырабатыва1ет сигнал сброса первого счетчика 8 и первого триггера 7 при максимальном значении счетчика. Индикатор 12 устанавливается в случае отклонения напряжения питания от номинала по сигналам из устройства питания процессора Поэтому максимальное значение первого счетчика 8 выбирается таким образом, чтобы время пересчета первого счетчика 8 до максимального значения было больше, чем время флуктуации, напряжения питания. Сигнал ошибки из блока 4 поступает на вход блока- Зр который вырабатывает запрос на микропрограммное прерывание, по которому в следующем цикле работы устройства блок 3 формирует адрес, передавае№лй в качестве следующего адреса микрокоманды в блок 15 памяти микрокоманд в блок 1.

В ходе выполнения микрот оограммы повторения второй триггер 14 установлен , поэтому по следующим сигналам ошибки процессор не переводится в состояние Останов. В конце микропрограммы повторения производится сброс второго триггера 14.

Регистр 13 задает изменение напряжения питания для вторичных источников питания процессора. Регистр 13 доступен микропрогрс1мме, поэтому, в случае безуспешного повторения сбоя, делается еще ряд повторений при различных значениях напряжений вторичл&к. источников питания.

В случае возникновения постоянного сбоя (отказа) возможна потеря управления из-за аклиниванил микропрограммы повторения. Поэтому устройство содержит второй счетчик 9, на вход которого из блока 3 с выхода элемента подается сигнал в случае запроса на микропрограммное прерывание на микропрограмму повторения. Счетчик 9 сбрасывается в исходное состояние сигналом из блока 1 и из

дешифратора 17 микрокоманд в конце выполнения каждой команды процессора Если за время выполнения одной команды второй счетчик 9 достигнет заданного значения (например 256) , второй дешифратор 11 вырабатывает сигнал,поступающий в блок 3, что вызывает, по следующему сигналу ошибки из блока 4, выработку на выходе блока 3 адреса микропрограммного прерывания,отличного от адреса микропрограммы повторения.

Любой случайный сбой является следствием изменения параметров вычислительной системы. Примерами таки параметров явлиютср температура,напряжение питания, время нарастания сигнала, время задержки на элементах контактные явления и т.д. Параметры .изменяются не мгновенно, а в течение некоторого промежутка времени, которое как правило, больше, чем рабочий цикл вычислительной системы. Следовательно, немедленная обработка сбоя, (как в известном устройстве) может привести к ряду ошибок, которые сделают восстановление вычислительного процесса невозможным. В предлагаемом устройстве по сигналу ошибки процессор переводится в состояние Останов, которое максимально устойчиво к причине сбоя, и лишь спустя промежуток времени, определяемых устройством, начинается обработка сбоя. Тем самым устройство обеспечивает эффективное восстановление вычислительного процесса. После первого неудачного повторения устройство делает ряд повторений: при различных значениях напряжения питания, что позволяет повторить сбои, связанные со старением микросхем. Предлагаемое устройство переводит процессор в состояние Останов по первой ошибке, и если в ходе обработки ошибки она появляется снова, процессор в состояние Останов не переводится, что не увеличивает время обработки данной ситуации процессором.

При возникновении постоянного сбоя (отказа) предлагаемое устройство обеспечивает сохранность управления, так.как происходит передача управления микропрограмме обработки данной ситуаций. В известном устройстве произойдет зацикливание на микропрограмму повторения,т.е.потеря управления вычислительным процессором. Таким образом, можно сделать заключение, что предлагаемое изобретениезначительно увеличивает надежность процессора.

Формула изобретения

Устройство для восстановления процессора после сбоя, содержащее блок микропрограммного управления, синхрониэатор, блок обработки данных, блок контроля и блок формирования адреса микрокомч1нд, причем первый, второй и третий выходы блока микропрограммного управления соединены соответственно с первым и вторым входом блока контроля и с перьым входом блока обработки данных, выход котот рого соединен с третьим входом блока контроля, первый выход олока контроля соединен с первьм входом блока, формирования адреса микрокоманд,первый выход которого сэединен с первьм входом блока микропрог раммного управления, отличающееся тем, что, с целью повышения надежности и расширения функциональных возможностей за счет обеспечения процесса восстановления с различньш напряжением питания, в устройство введены перзый и второй счетчики, первый и второй деашфраторы, первый и второй триггеры, элемент И, регистр, индикатор откпонения напряжения литания, причем выход элемента И соединен с первым входом первого триггера, выход которого соединен с входом . -. синхронизатора, четвертый и пятый выходы блока микропрограммного управления соединены соответственно с первым входом второго триггера и с первым входом второго счетчикаi второй выход блока контроля соединен с первым входом эпемета. И и с вторым входом второго триггера, выход которого соединен с вторым входом элемента И, выход синхронизатора соединен с. первьм входом первого счетчика, Eftiход которого соединен с первым входом первого дешифратора, выход крто рого соединен с вторыми входами первого счетчика и первого.триггера,первый вход устройства соединен с входрм индикатора отклонения напряжения питания, выход которого соединен с вторым входом первого дешифратора.

второй выход блока формирования адреса микрокоманд соединен с вторым.входом второго счетчика, выход которого соединен с входом второго дешифратора, выход второго дешифратора .. соединен с вторым входом блока формирования адреса микрокоманд, второй выход блока обработки данных соединен с первым входом регистра,первый и второй выходы которого соединены соответственно с первым выходом уст0роГ;ства и вторым входом блока обработки данных.

2. Устройство по П.1, о т л.и чающееся тем, что блок микропрограммного управления содержит

5 блок памяти микрокоманд , регистр микрокоманд и дешифратор микрокоманд, причем первый вход блока памяти микрокоманд соединен с входом блока, выход блока памяти микрокоманд

0 соедцнен с первым входом регистра дшкрокоманд, первый, второй и третий выходы KOTOpbrq соединены соответственно с первьм выходом блока ,с вторым входом олока-памяти микрокоманд, с входом дешифратора микрокстанд,пер5вый, второй , третий и четвертый вы- ход дешифратора микрокоманд являются соответственно вторым, третьнм, чет-вертым и пятым выходами блока.

0

Источники информации, принятые во внимание при экспертизе

1.Нкртумян И.Б..и др. Средства восстановления ЭВМ ЕС-1045. - Вопч роры радиоэлектроники, сер. ЭВТ,

5 1978; вып. 10.

2.Запольский А.П. и др К повышению н адежности вычислительных процессов в ЭВМ ЕС-1035. - Всшросы радиоэлектроники, сер. ЭВТ, 1977,

0 вып. 11.

3.Патент СЗйА 3533065, кл. 340-172.5, опублик. 06.10.70 (прЬтотип).

11

I

0

fS

-

4

Hagcf

уял/ и

$ЛО1Ш

a/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для восстановления работы процессора | 1984 |

|

SU1191910A1 |

| Устройство для управления каналами | 1984 |

|

SU1372329A2 |

| Процессор | 1984 |

|

SU1246108A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Микропрограммный процессор с контролем | 1981 |

|

SU985791A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Двухканальное устройство для контроля и восстановления процессорных систем | 1986 |

|

SU1397917A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Устройство для управления каналами | 1979 |

|

SU877519A1 |

Фиг2

Авторы

Даты

1981-08-23—Публикация

1979-12-07—Подача