Изобретение относится к автома.тике и вычислительной технике и может быть использовано при построении специализированных устройств для вычисления Фурье преобразования последовательности цифровых отсчетов сигнала в реальном масштабе времени.

Известно устройство для вычисления коэффициентов Фурье по методу быстрого преобразования Фурье (БПФК имеющее память операндой, -память весовых коэффициентов, память резулвтат-ов и арифметический блок : 3Недостатками известного устройства являются значительная сложность и недостаточно высокое быстродействие, обусловленные наличием множительных узлов в составе арифметического блока.

Наиболее близким к предлагаемому является устройство для вычисления -. коэффициентов Фурье содержащее шесть сумматоров, а также регистры действительных и мнимых частей весового коэффициента и операндов и четыре множительных блока t2 .

S Недостатком известного устройства является низкое быстродействие обусловленное наличием операций умножения, а также необходимостью дополнительных громоздких преобразований для перехода от действительных и мнимых частей в представлении результата к его модулю и аргументу.

Цель изобретения - повышение быстродействия устройства,

Поставленная цель достигается тем, что устройство для вычисления коэффициентов Фурье, содержащее шесть сумматоров, содержит три вычитателя, два сумматрра-вычитателя и восемь блоков постоянной памяти, причем вход весового коэффициента и вход :. аргумента первого операнда устройства соединены с соответствующими входами первого сумматора, вход модуля первого операнда соединен с первыми входами второго и третьего сумматоров, вход аргумента второго операнда соединен с первыми входами четвертого и пятого сумматоров, вход модуля второго операнда соединен с адрес ними входами первого и второго блоков постоянной памяти, вход первого сумматора -подключен к адресным входам третьего и четвертого блоков постоянной памяти, выходы первого, второго, третьего и четвертого блоков постоянной памяти подключены к вторым входам четвертого, пятого, второго и третьего сумматоров соответственно, выход второго сумматора подключен, к сумми- РУ10ЩИМ входам первого вычитателя и первого сумматора-вычитателя, выход третьего сумматора подключен к суммирукхдим входс1М второго вычитателя и второго сумматора-вычитателя, вы- ,

ходы четвертого и пятого сумматоров подключены к вычитающим входам первого и BTOjooro вычитателей соответственно, выходы первого и второго вычитателей подключены к адресным вхоЬам пятогр и шестого блоков постоянной памяти соответственно, выходы пятого и шестого, блоков постоянной памяти подключены к cyмlvIиpyющим входам первого и второго сумматоров-вычитателей соответственно, управляющие входы первого и второго -сумлаторов-вычитателей соединены с управляющим входом устройства, выход первого сумматора-вычитателя подключен к первому входу шестого сумглатора и к суммирующему входу третьего вычитателя, выход второго сумматора-вычитателя подключен к вычитающему входу третьего вычитателя, выход которого подключен к адресным входам седьмого и восьмого блоков постоянной памяти,. выход седьмого блока постоянной памяти подключен к втopo ry входу шестого сумматора, выходы которого и восьмого блоке постоянной памяти являются выходами модул-я и аргумента результата устройства соответственное

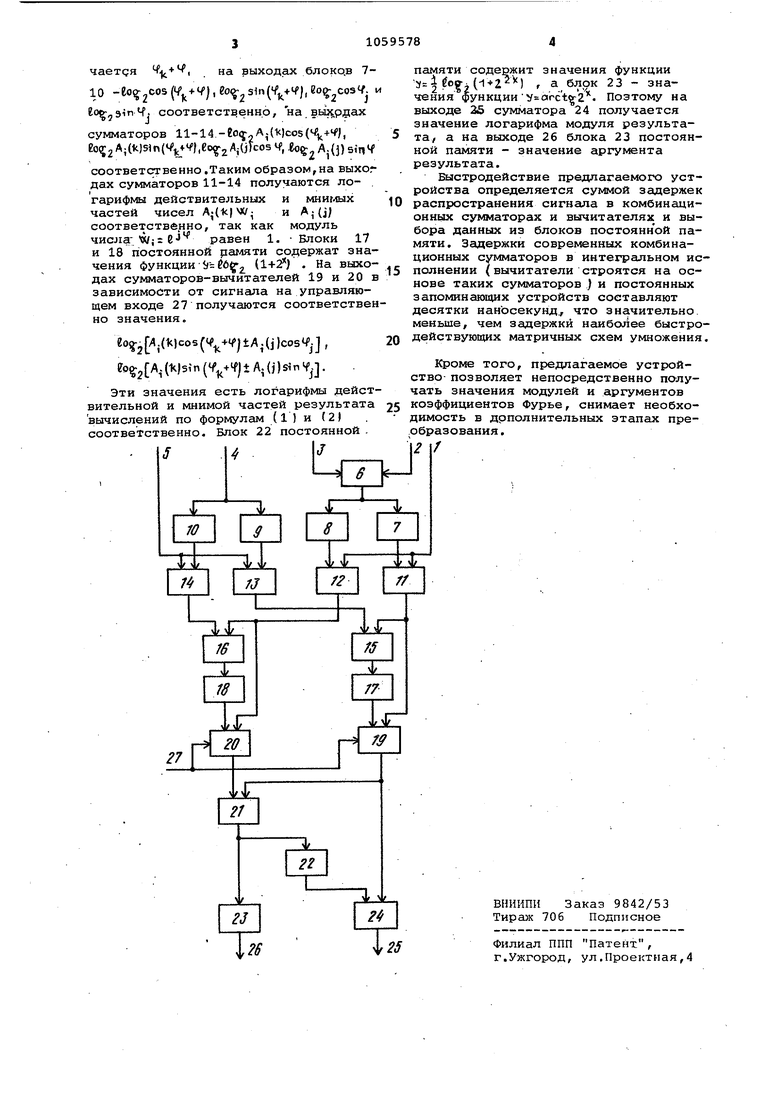

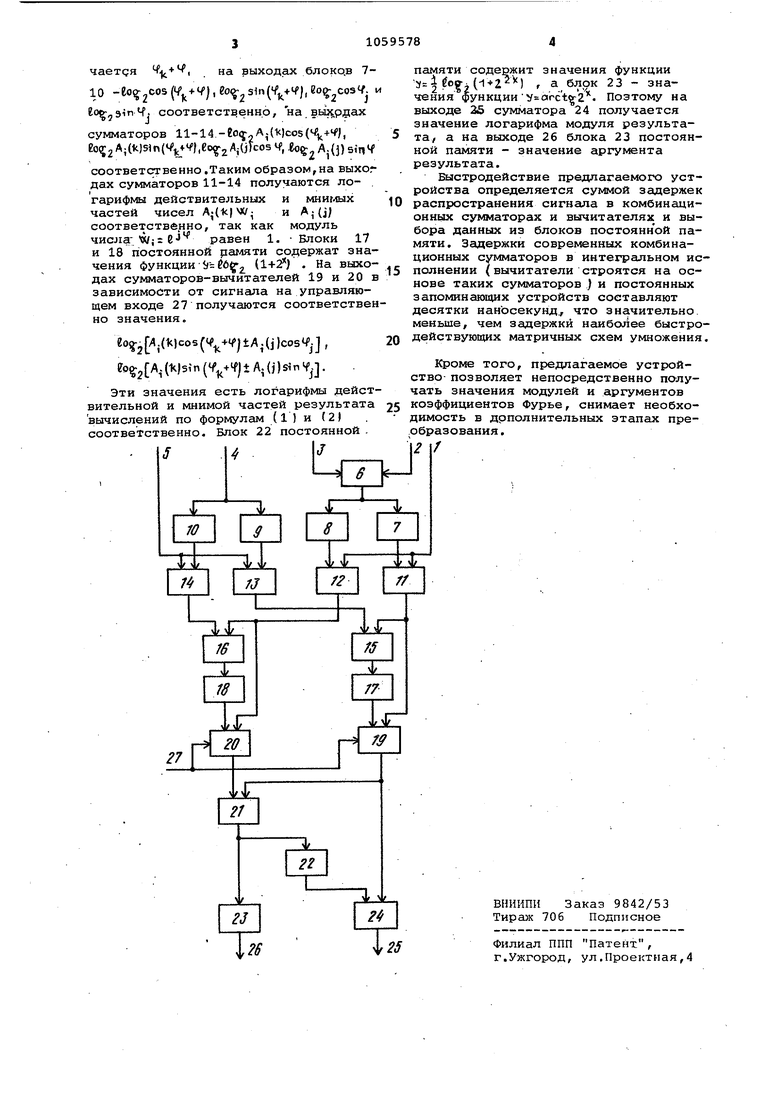

На чер7.еже представлена функциональная схема устройства дл.я: вычисления коэффициентов Фурье„

Устройство содержит информационные входы шины 1-5, cyivB-iaTop б, блоки 7-10 постоянной памяти, сумматоры 11-14,.вычитатели 15 и 16, блоки 17 и 18 постоянной памяти, сумматоры-вычитатёли 19 и 20, вычитатель 21, блоки 22 и 23 постоянной памяти, суь-магг тор 24 и ззыходы 2S и 26,

Устройство реализует алгоритмы вычисления в соответствии с выраженил )

ями

(( Н Д (k).(j)-A.(-klW, (2)

используя при выполнении операции умножения представление комплексных чисел в показательной форме, а при выполнении операции сложения - в алгебраической форме. Результат вычисления получается в показательной форме. Числа, подаваемые на вход устройства, также представлены в показательной форме, ,

По.шине 1 поступает модуль числа А.; (1)/в, логарифмической форме .. Eag2 п.о..1|шне 2 аргумент этого числа fV , по шине 3-, аргумент V весового коэффициента .j, по шине 4 - . модуль числа ,{1 в форме О) A,.(j, по шине 5- аргумент этого числа fj . Блоки 7 и 9 постоянной паг/шти содержат значения функции . б-х, а блоки 8 и 10 значения функции Ko4;Sin. На выходе cyNjMaTopa 6 получаетдя на выходах блоко.в 710 (), sl(Vb Ч, соответственно, на. сумматоров ll-14. A.(K|cos(.+Ч), eoqjj A;(k)s)i(,eo.Aj(jtcos Ч, .eo5.A.(j) 5,-пЧ соответственно .Таким образом,на выхогдах сумматоров 11-14 получаются ло- . гарифмы действительных и мниглых частей чисел А-{1с|ЧХ/ и A,(j; соответственно, так как модуль числа Wj: KJ равен 1. Блоки 17 и 18 постоянной рагляти содержат значения функции- 6 2. ( . На выходах сумматоров-вычитателей 19 и 20 в зависимости от сигнала на управляющем входе 27 получаются соответствен но значения. ,(fJiA.(, ,-(i)s(V) значения есть логарифмы действительной и мнимой частей результата вычислений по формулам (1 ) и (21 соответственно. Блок 22 постоянной . памяти содержит значения функции ojg-i (-1-12) , а блок 23 - значения функции y circt 2. Поэтому на выходе 25 сумматора 24 получается значение логарифма модуля результата, а на выходе 26 блока 23 постоянной памяти - значение аргумента результата. Быстродействие предлагаемого устройства определяется суммой задержек распространения сигнала в комбинационных сумматорах и вычитателях и выбора данных из блоков постоянной памяти. Задержки современных комбинационных сумматоров в интегральном исполнении (вычитатели строятся на основе таких сумматоров ) и постоянных запоминающих устройств составляют десятки наносекунд., что значительно меньше, чем задержки наиболее быстродействующих матричных схем умножения. Кроме того, предлагаемое устройство позволяет непосредственно получать значения модулей и аргументов коэффициентов Фурье, снимает необхоимость в дополнительных этапах преобразования .

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор быстрых дискретных преобразований | 1989 |

|

SU1725227A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для реализации безызбыточного алгоритма быстрого преобразования Фурье | 1981 |

|

SU1056206A1 |

| Устройство для быстрого действительного преобразования Фурье | 1986 |

|

SU1476488A1 |

| Устройство для быстрого преобразования Фурье | 1986 |

|

SU1392577A1 |

| Устройство для нахождения экстремума функции | 1985 |

|

SU1287182A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СКОЛЬЗЯЩЕГО СПЕКТРА | 1998 |

|

RU2125291C1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для вычисления функции арктангенса отношения | 1990 |

|

SU1751750A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОЭФФИЦИЕНТОВ ФУРЬЕ, содержащее шесть сумматоров, отличающееся тем, что, с целью повышения его быстродействия, оно содержит три вычитателя, два сумматора-вычитателя и восемь блоков постоянной памяти,причем вход весового коэффициента и вход аргумента первого операнда устройства соединены с соответствующими входами первого сумматора, вход модуля первого операнда соединен с первыми :входами, второго и третьего суммато- ров, вход аргумента второго операнда соединен с первыми входами четвертого и пятого сумматоров, вход модуля второго операнда соединен с адресными входами первого и второго блоков постоянной памяти, вход первого сумматора подключен к адресным входам третьего и четвертого блоков постоянной памяти, выходал первого, второго, третьего и четвертого блоков постоянной памяти пoдкJшчeн,ы к вторым входам четвертого, пятого, второго и третьего сумматоров соответственно, выход второго сумматора подключен к суммирующим входам первого вычитателя и первого сумматоравычитателя, выход третьего сумматора подключен к суммируквдим входам второго вычитателя и второго сумматоравычитателя, выходы четвертого и пятого сумматоров подключены к вычитающим входам первого и второго вычитателей соответственно, выходы перво- го и второго вычитателей подключены к адресным входам пятого и шестого блоков постоянной памяти соответственно, выходы пятого и шестого блоi ков постоянной памяти подключены к суммирующим входам первого и второго сумматоров-вычитателей соответственно, управляющие входы первого и второго сумматоров-вычитателей соединены с управляющим входом устройства, выход первого сумматора-вычитателя подключен к первому входу шестого сумматора и к суммирукхцему входу третьего вычитателя, выход второго сумматора-вычитателя подклюел чен к вычитающему входу третьего со ел вычитателя, выход которого подключен к адресным входам седвмого и восьмого блоков постоянной памяти, выход седьмого блока постоянной памяти подключен Тс второму входу шестого оо сумматора, выходы шестого сумматора и восьмого блока постоянной памяти являются выходами модуля и аргумента результата устройства соответственно

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для преобразованияфуРьЕ | 1978 |

|

SU794637A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| 1971 |

|

SU421994A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-12-07—Публикация

1982-07-09—Подача