со г

СП

1

Изобретение относится к вычислительной технике и предназначено д.тя построения систем цифровой обработки сигналов, основанных на выполнении алгоритма быстрого преобразования Фурье.

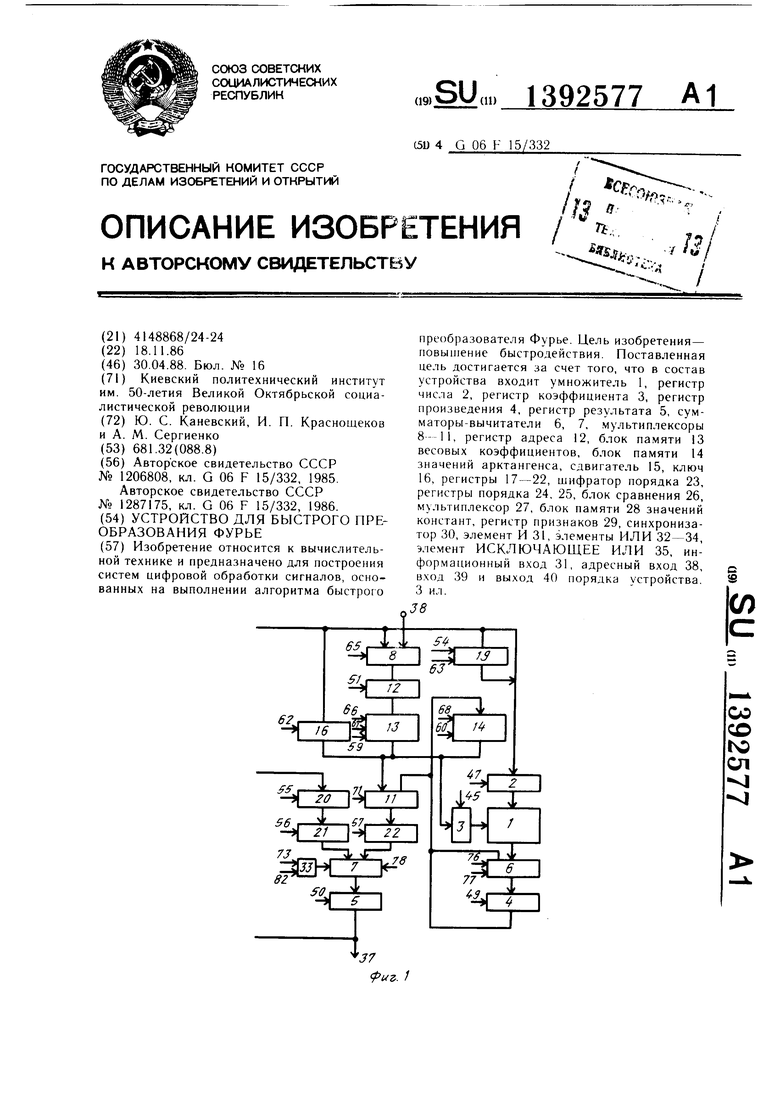

ila фиг. 1 и 2 ноказана структурная схема устройства для быстрого преобразования Фурье (БПФ); на фиг. 3 - структура синхронизатора.

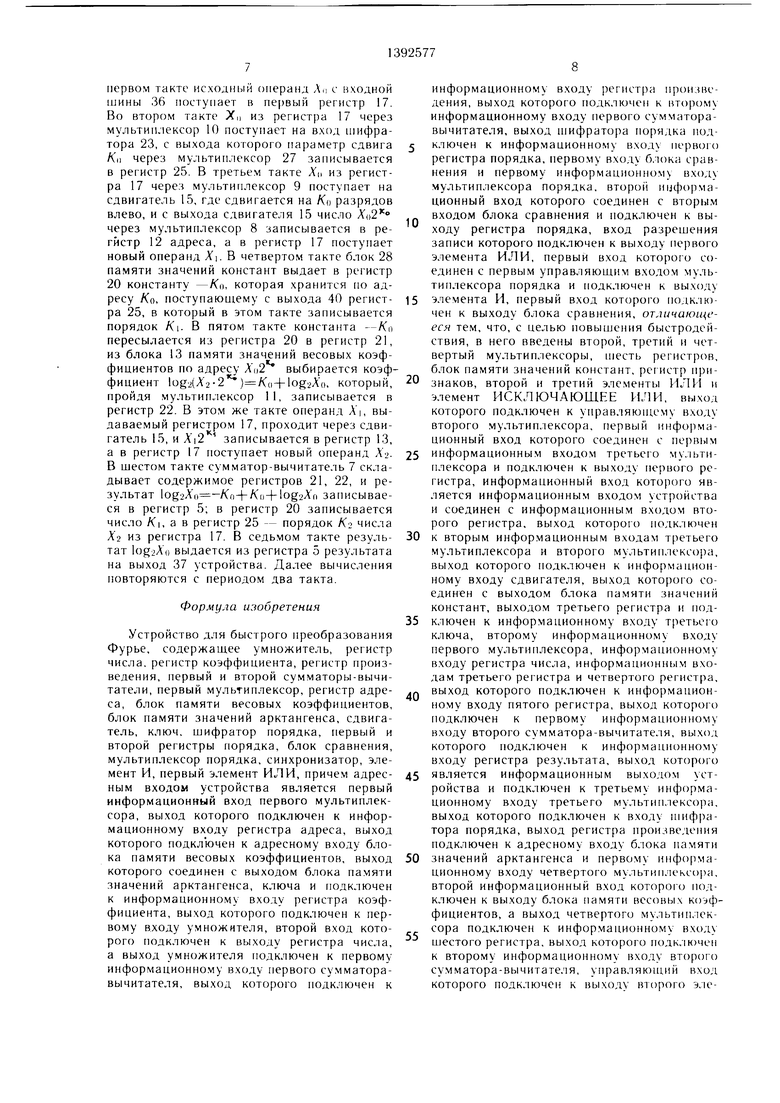

Устройство для быстрого преобразования Фурье содержит умножитель 1, регистр 2 числа, регистр 3 коэффициента, регистр 4 произведения, регистр 5 результата, первый 6 и второй 7 сумматоры-вычитатели, с первого по четвертый му.тьтинлексоры 8 - 11, регистр 12 адреса, блок 13 памяти весовых ко- ффицнентов, блок 14 памяти значений арктангенса, сдвигатель 15, ключ 16 (выполненный с тристабильным состоянием), с iiepuorcj по пестой регистры 17 22, 1пиф- ратор 23 порядка, первый 24 и второй 25 регистры порядка, блок 26 сра 5пения, муль- тип.лексор 27 порядка, блок 28 памяти зпа- чепий копстант, регистр 29 признаков, синхронизатор 30, элемент И 31, с lepBOio по третий .тементы ИЛИ 32 34, э.темепт ИСКЛЮЧАЮЩЕЕ ИЛИ 35, информационные вход 36 и выход 37 устройства, адресный вход 38, вход 39 и выход 40 порядка устройства. Синхронизатор 30 (фиг. 3) содержит счетчик 41 адреса микрокоманды, элемент ИЛИ 42, блок 43 памяти микрокоманд, второй вход 44 запуска, входы 45, 46 задания режима устройства, выходы синхронизатора 47 79. На структурных схемах (фиг. 1, 2) юказаны также шины 80-82 устройства.

Работа устройства начинается при подаче сигнала на вход 44, который устанавливает в нуль счетчик 41. По состоянию ninn 45 и 46 в блоке 43 памяти микрокоманд выбирается одна из трех зон памяти с соответствующей мик)оирограммой: при вычпслении БИФ состояние пжн 45, 46 - 00, при вычислении модуля и фазы - - 10, а при вычислении логари ф.ма - 01. С каждым тактом состояние счетчика 41 увеличивается на I и из блока 43 выбирается новая микрокоманда. При ноявлении сигнала на выходе управления следующим адресом б,лока 43 счетчик 41 обнуляется и начинается новый цикл работы устройства.

Рассмотрим работу устройства для быстрого преобразования Фурье при выполнении базовой операции БПФ. В первом такте в регистр 12 адреса записывается адрес весового коэффициента нулевой базовой операции с тины 38 адреса. В этом же такте с входной П1ИНЫ 39 порядка записывается число О, если на предыдущей итерации алгоритма БПФ зафиксировано возможное переполнение, или число Л , если во всех результатах предыдущей итерации имеется не менее К старших незначащих цифр. В пе1)вый регистр 17 с входной щины 36 записывается

5

операпд й нулевой базовой операции. Во втором такте с тины 36 операнд В- записывается в первый регистр 17, из которого операнд В пересылается через второй

му.тьтиплексор 9 и сдвигатель 15 в регистр 2 числа и в третий регистр 19, а в регистр 3 коэффициента из блока 13 памяти весовых коэффициентов записывается коэффициент Wiio . В третьем такте операнд Лт с щины 36 записывается в регистр 17, из которого операнд В, пересылается через мультиплексор 9 и сдвигатель 15 в регистр 2 числа, в регистр 3 коэффициента из блока 13 памяти весового коэффициента записывается коэффициент Wij, . Умножитель 1 выполняет проr изведение операндов из регистров 2 числа и 3 коэффициента, результат которого Bt X X It Ко пройдя первый сумматор-вычита- тель 6, записывается в регистр 4 произведения. В четвертом такте из произведения операндов из регистров 2 числа и 3 коэффи0 циента В W j вычитается на сумматоре- вычитател°е 6 промежуточный результат из pei HCTpa 4 произведения и результат Л 1. io ч. lu записывается в регистр 4 произведепия. В этом же такте исходный операнд А постугшет в первый регистр 17, Лй„ из которого пересылается через второй мультиплексор 9 и сдвигатель 15 в четвертый регистр 20; в регистр 3 коэффиниепта из блока 14 памяти весовых коэффициентов записывается коэффициент

Q WR, . В пятом такте полученное на умножителе 1 произведение В WR , пройдя первый сумматор-вычитатель 6, записывается в регистр 4 произведения, операпд Л , из которого,- пройдя четвертый мультиплексор 11, записывается в щестой регистр 22,

5 операнд А- пересылается из четвертого 20 в пятый 21 регистр, а операнд А пересылается через второй мультиплексор 9 и сдви- гате.ть 15 в четвертый регистр 20. В этом же такте повый операнд В поступает с входа 36 в первый регистр 17, операнд BR пере сылается из третьего регистра 19 в регистр 2 числа, а в регистр 3 коэффициента из блока 13 памяти записывается коэффициент W в регистр 12 адреса с адресного входа 38 через первый мультиплексор 8 записывается

5 адрес нового весового коэффициента. В шестом такте произведение Bi Wi , полученное на умножителе 1, складывается с содержимым регистра 4 произведения, результат

lo bfii. Ti, записывается в регистр 4 произведения, второй сумматор0 вычитатель вычитает из содержимого пятого регистра 21 содержимое щестого регистра 22, и первый результат . - « нулевой базовой операции записывается в регистр 5 результата. В этом же такте новый операнд SR, пересылается через второй мулыиплек5 сор 9 и сдвигатель 15 в третий регистр 19 и регистр 2 числа, а новый операнд Bj с входа 36 записывается в первый регистр 17; в pervicrp 3 коэффициента из блока 13 памяТИ IIUl | IIHt T IKlUhiii ИеСОКОЙ KObull-iHHIIC liT

W-K. . i седьмом liiKTc операнды и f пятого 2 и мкч гого 22 pei nc i ров ск,1адын;и01Ч Я на втором суммато|)С -иычи тателе 7 и вт()|К)й речу.|ьтат , . I AR ;iannci Bat i4 я li ре- 1 истр Г) рс :1у. 1Ы ата, .:1ыат С из которо- г.) поступает на 37 устройства, а также на трети вход третьего мультппдексора 1Г) и далее на вход (нифратора 23 порядка; операнд Л пе Н сылае гея и: регисгра 4 произведения черен четвертый iin/ieix- еор II в нн стой ре1истр 22; операнд /Ьо не рее1 1лается из четве)гого 2Г) в пягий 21 le- гистр. В этом же такте по.тученное на ч.мпо- жителе 1 произведение /j W j заиисывасч ся в регист) 4 нроизведения, операнд В через второй му.ты ии.к ксор 9 и сдкиг;. ie. ii 15 пересы.тается в регистр 2 чис.та, в регистр 3 ко :)ффипиента записьп ается ко:)ф- фициепт U j , а в первый )е1 исгр 17 с входа 36 запис1)1ваегся новый операнд /1. 15 восьмом такте BTopoii сумматор-вычпта гель

7производит сложение содержимьгх iiHroiD 21 и нестого 22 )егистров, и третий резу ль гат + A i записывается в )егнсгр Г) резу.тьтата. который выдает резу.1ьтаг /)„ иа выход 37, который также поступает через третий мультиплексор И) на вход н1И({)ра тора 23 порядка. В этом же такте из произ ведения В, U/ )ia нервом сумматоре-вь1- читателе 6 вычитается нроизведепие В X XW, и результат , Ц , запис1 1вается в регистр 4 произведения, в ре1ист) 3 коэффициента записывается чис.то Wf , с входа 36 новый операнд A-i занисы- вается в 1)егистр 17, oHeiuiiti А из Koropoio через второй му.чьтнплексор 9 и сдиига- тель 15 11ересь1.1ается в четвертый регисгр 20.

8девятом такте второй сумматорл ычига- тель 7 вычитает из соде1)жимого пятого ре- I Истра 21 (операнд из нестого регисг)а 22. и четвертый резу.11)Гат Oj Лi -Л записывается в регистр 5 результата, резу.тьта; Cj из которого выдается на выход 37 и через третий му.тьтип.чексор И) поступает па вход 11)И(()рат()ра 23 порядка. В этом же гакге

прои:шедение

и. -w;

ч.,

записывается в ре

гистр 4 произведения, операнд Л и f кпто- KJIO пересылается в нюстой регистр 22. операнд Ag пересылает 1-я из четвертого 20 в пятый 21 регистр, операид А иересы.чаегся из первого регистра 17 в четвертый ре:истр 20, коэффициент Wj. :1аписывается в le- гистр 3 коэффициента, в регистр 2 лается чис.то из регистра 19, а в нерв1)1Й регистр 17 поступает новый операнд В, в регистр 12 адреса записывается адрес иес(ь вог() коэ(|)фициепта д,тя второй базовой опе- )ании. В десятом такте нос.тедний резу.тьтаг f выдается в тину iJ7 и нодается на вход нифратора 23 порядка через третий мульти- H. ieKCOp 10; второй су мматор-вычи га гел

,, - Н зульпроизводит действие (,

тат которого запис1,1вается в регнс р о резу.т1)Тата; nepBijiii сумматор-вычитате.ть 6

-7

0

0

5

0

5

0

5

0

)и; .во.чпг де1 |С11и1с Aj , R, , I рез льгат Koropoio 1аппсывае Ч-я n регистр 4 произве.Н Пия; О11е)аид В iiepeci.i.iaeTCM в трети11 |1с1 П1 тр 19 и perncip 2 числа, а нозанис1)1иается в 3

оиерапд В

pei Hcrp 17; в

коэф||)ицпепт U . /1а,тее paOoia с1ройст ва

повторяется с периодом четыре тактл. Г.с.ти

при этом iia вход 3(i 1:г1 ичпо nocrynaioi

.е данные /L , li . Л„ . А. . а на

1

вход 3 ад))1. са весов1)1х к()эф|рициент()5, И) на 37 бчдх г появ.1Ягься |ic.i .тьгатлп

COOT ветч твенпп Г,, inie Ы1Ф в

at- . -j . Вычис.те- стр()йсгве производится с по- F

о.точпо 1|.1авак)|деи запятой. Не.) л ьтаты очередной птерсиши поступают па вход схемы. сост()ян1е11 из nnujip.aTopa 2.3 порядка, Hei)Bor(j 24 и второго 25 регистров порядка, о.тока 26 сравпепия, м,тьтип,1ексора 27 ио- рял.ка, э.тементов 11 .31 и H/lil ,32, KOTojiai; .т.тя он|)еделения возможности пе1НМ1о.1пения н)о|и ряет рез.тьтат па иа.тнчие незнача- HUix раз|)ядов iiepe.i старншм зиачаниш раз|)яд(м. При 1НА т II,тении С.к на вход Н1иф- KiTopa 23 пос.тедний выдает ко.т ко.тичества пе.()1ачан1их umlip (порядок, когор1)1Й запн- С1.1ваегся в ni-pBbiii ре -истр 24 11О)ядка при е,иип1чном сигна.те на Н1ине 72 как нача.тыюе значение для с)авнения. По мере ностуи.те- ния с.тедуюших . гов б.ток 26 сравне- 1И1я сравнивает минима.тьпый норядок, за- ())нкси)овапп1)111 в регистре 24, с по()ядком текущего ре.и,тьтата, ес,ти теку1ил1Й порядок меныне, го он занисывается в ре1ист) 24 при единичном н ну.тевом еигналах на типах 74, 72 соот ветствеиио. В конце вьию.т- пения нтерацпп ГзПФ в регисгре 24 ока- зывае|СЯ норядок А максима.Т1,пого чис.та в массиве резу,т1)татов, которь1Й но на тине 59 за11ИС1)1вается во второй (тегистр ио)ядка и да.тее вьнается в .Bijixo.uiyio тину 40 норядка. i пача. /е с.тедуюним итерации чис.то А записывается во второй регистр 25 но1 )ядка t- иины 39. 11оск(),тьк опе- ранд1 1 на тине 37 нередаются в ОЗУ для хранения промежу гочпьгх Н зу.тьт атов сдвинутыми на один ви)аво, то когда зафикси 1о1 ана во.-1можность переио.тнения, Л 0 и на noBoii inepaiuni исходные данные, проходя сдвигатель 15. будут сдвигаться на О разрядов в.тево, т. е. в конечном счеге оие 1анд1)1 на вход умножипмя 1 т подаваться уменьшенными вдвое и нс-рено.тне- ния не произойдет. При А; исходные данные буд г норма.тизовагься пугем на А разря.юв в.теио на 1 дви1ате.те 15. тем с.амым по.тччится высокая точность вь1чпс ле1

55

I at CMoTpiiM работу u TpoiicTiia при вычис ленип .модуля н фазы ко.мп.тексного числа. В нервом такте па BXO.I 36 CTpoiiciBa но- стл нас ; реа.тьпая частл, н,тево1О операн.ча .1|г , когорая занисывае-тся в не)ВЫ11 ре- 1Л1ст) 17. Во втором гакте с входа 36 во вгорои регистр 18 : аносится мнимая часгь H,:i. - вого операнда А , а операнд А чере TIK - тий му.чьтпплекеор И) нопупает на пшфр: т()|) порядка, кот()|)ый выдае H( Лц операнда А. который занп(. ывает1 я н первый pei HCTp 24 порядка при наличия единичного си1 нала на тине 72. В третьем такте А ил ESTuporo регистра 18 через i|)e- тий му.тьтиплексор К) нодаетея на вход тиф ратора 23 порядка, К(торый выдает код Л порядка чис,1а А , кого)ый с|)авнивается с кодом Л из регис г)а 24 порядка в б. юке 2ii С1)авнсния, сигнал с вьгчода которого, 11ро11дя через схему И 31, управляет мульгиплексо- ром 27 порядка, которы пропускает МИ1Ч1- малы1ЬП1 из порядков l i niiti{K К I, ко- 1О|1ый в конце 1акга :1апис1 1вается в рг гистр 25. При zJTOM па тине 74 едпнпчш сигпал, а в )егис1р 29 признаков в разряд1,1 III, 113, 114 cooTBeicTBenno заиисываюгси

состояпия 311ак()В1)Гх разрядов А-„ тинам 80, 81 п нрпзнак хода б.юка 2В сравнения.

.,„ ПУСТЬ /1.

4., МО

До

Ito

что соответствует (. - .-.

стоянию pel Истра 29 п|1изнаков 000.

в четвертом такте операпд y , из го ре1истра 18 ироходпг едвигагель 15, где сдвигается в,тево па К разрядов, и получ1Ч1- ный таким обра.зом операнд V d 2 запись:- вается в регист|) 2 чис.та, проходиг через ключ И) и записывается в регистр 3 коэффициента. В пятом гакте операнд Л(|,4 и iiepBOix) регистра 17 проходит второй муль тпгкчексор 9, сдвпга1е.т) 15, где сдви1 ае ся на Л о разрядов, и операпд АИ 2 записывается в регпсгр 2 числа, через ключ 16 запп- сывается в )егистр 3 ко (})фицпепга и через первый мультиплексор 8в регистр 12

адреса; умножитель 1 умножаег оиерапды из регистров 2, 3, и ироизведеиие У Г) , пройдя через первый сумматор (, заппсыпп- ется в регистр 4 произведения; повый операнд Л«., поступает в регистр 17. В с,, если Лв. , первый разряд регисг- ра 29 признаков паходится в состоянии 111 -- 1 ив четвертом такте второй мультиплек сор 9 пропускает операнд с регистра 17 , а в пятом такте мультиплексор 9 пропускает операнд ,г с вьгхода вт()(()- го регистра 18. Таким образом, па вход элемента ИСКЛЮЧ.ЛЮИШН ИЛИ 35 в четвертом такте подается О, а в нято.м такте 1. В шестом такте б,1ок 13 памяти .uianeiuiii весовы.х коэффициентов выдает Ko cjxjin- циент, равпый l/(A( ), кот())ый записыва ется в регистр 3; первый суммаго) 6 CK.I;;- дывает по.тученное на умпожиге,1е 1 uponзис- дение Ari2 ° с содержимым ()егпстра 4 произведения и результат Ari2- ° -(- г, за1П1- сывается li 1)егистр 4 п)оизведепия. В -лом же такте блок 28 памяти значени копстан выдает код yi-ла коррекции, K(jTopbiii iaiuu-ni от знаков .-IR.. Л,, (ИЗ, 114) и соопюшеьпя

их абсолютпьгх зпачений, и в слччае А Л, ) равеп Н () при 113 -Л)

I -

5

0

5

0

5

C

5

0

5

при 1 3 1, .0, И:- I |.рн , I. а . с лучае И 1 -1 paiien Н---(),Г) при 114 --ill , И ;.: 0,5 при 114;-I. 410 rooiTieicT- (-1. --il п -ь90 , п ко| орыГ| запи- сыи,11.. 1 ./ IS четвср1Ь1Й |)егпс|р 20 И I o .лке I .j.e.viM МО pci4icip 18 им; i у цщ т ио1и,1Й операп...-), , а . Ij,, ni pernciiia Ь поступает 4. pc:i iv. i-i иплексор 10 па и.чод пшфраю- ра 23, ;i Л записьшается в |)ei пст 24. 1 (ЧМ,М()М 1акте операпд из нмтк тра 4 по- . па ад|)есп1)1Й вход 6..ioK,i 14 памяти inasennii ajiKTain enca с вьгхо.и ко О| я)го 1,ыд:;| ;;я зпачение 2 v V ri-| -Vn, оторое ,апП . :1и;и тся в регистр . )-Jф(|liMLп irra по ;npi ..i Ли; пз б..:. 28 пч. мям .пачепии .) ;-:;ii i 1и,|бира1. Konc i а;| : а 2 , кото- |) ;:ипиывается в p(4Tic ip 2, мпо/кп кмь I

о.V

upon-;|-,11Д1Г1 умпо/К1МП1е 1/(. } на Уп2 , п |11 ; .:, га I } ,|/. о заппсьшаегси в pci пстр 4 npoii 1;| депия. ti этом же т акте / из )е- rMcipa 18 noc iynacT через му,:11.т..п1лскс ;|) 10 па iixo.i ninijtpa го|)а 23, noBbiii nojni.aoK Л | ; П1 :и.|нае 1Ч Я в piTncT i 25; в ркмпсгр 29 .аши мнакл ся п|)пзпаки 1П)в:)й napni даипых. а пр;ипак П1 iicpennt-ывается в разряд И2. В г;(м ьмом 1 акге операпд }(,/.(. ni periicTpa 4 постчпаег па адрес1п 1Й вход блока 14 памягп значении арктапгепса, с выхода кото)ого число а1Ч 1ц 1 У ,|/.,|1 чере; му:1Ь|-иплексор 11 -;апис1 1в;и -| ся в 1пестой регистр 22; умпожиi4 .;ii,1 умножает о11е }апд|)1 2 и 2 Х

X ri - .г., п прои (ведение iii(nl.-l,i-- УЧ- А заппсьП)ае 1 ся в IIITHC III 4; yio/i кор|)екции HI, i;e|iec-i,r:iae гея из рсчлн тра 20 в pei нстр 21. В -/iOM же такте noiibiit операпд ;-ппп: .-Inj ;l.4i, |i nocTynaei в регпггры 2, . i сдв1П I i)iM на Л pa (рядов влепо. В дс вягом ,)е ;у. ib i ;;т nioii. ln чере i v. ii.nin. lek Ci.ip 1 поступает is pel пстр 22. при roi |()Я1П1И pa.,ii.ia peinci pa 28 признаков 112-:..-О сум ма i i. p-ы,1чн 1 ате. iij 7 ск.тадывае1 содержимое i)u jii.Mi 21, 22, а п)п 112-1 libinni aer пз i:)ji4.i:.K ;M;:i i) pei ncT ;a 21 содер/ |1 мое pei HC i- 1)а 22. п )1 з ль 1аг i| ,i-r ai cltj; ) M/AIII ча- .-i.ii;ae i ся н perni. 1 p 5 pt .чьта га. 15 этом КГ -pii .H операпд А i -П11п(;/4в, , .-1, ,} но- 1Ч г;:11.ч I , рс гис 1 ры 2 3, 12, в periicip 4 за- ni cbinaiMCH опе1)апд } i2 , а в пе:)вь:й Н - |истр 17 юсгупает повы11 onepair;i Af . L5 ;iec ,rio .; laK i e резу.чыат В1 1дается из регистра t г; 1 1л1ходпук) Hinfiy 37 устройства, ма и: -иьппггате. 1Ь 7 nponycKaei )ой )е- ly.ibiai niod. lii из регист)а 22 в pi-1 истр 5; I pcinnp 4 заиис1;1вается сумма произве- ) у2 -f A f2 . : в peiiirip : записы- iiie c /: нисл) 1/;Л .2 ); С )егпсгра 17 па в.хо.т ;iini|:ii;a I ора 24 noci- nae-i операнд .4 , а в н- I i .c i р 18 нос гу nai i повый операп, г .-1 . В о,,1 i aKie В10)ой |)езу,. 1ьт; . i гпо(1,4. | 1 KMiDii )диых даппЬ Х выдается на и.ыход, .)7 VC I poiic iTia. Далее pa6o ia yci- j)oii .-гн.. поп Iорнсдч и с периодом ч1 ТЫ)е I ак I.

, u. Hne . 10 арп||)ма чпс, 1а в . iii прои(водП|СЯ с. К дуюпгпм o6j;a-ioM. В

первом такте исходный операнд An с входной 1иины 36 1юсту |ает в первый регистр 17. Во втором такте Хп из регистра 17 через мультиплексор 10 поступает на вход шифратора 23, с выхода которого параметр сдвига К, через мультиплексор 27 записывается в регистр 25. В третьем такте Х(, из регистра 17 через мультиплексор 9 поступает на сдвигатель 15, где сдвигается на Ко разрядов влево, и с выхода сдвигателя 15 число X( через мультиплексор 8 записывается в регистр 12 адреса, а в регистр 17 поступает новый операнд Х. В четвертом такте блок 28 памяти значений констант выдает в регистр 20 константу -Ка, которая хранится по адресу Kfi, поступаюи1ему с выхода 40 регистра 25, в который в этом такте записывается порядок /(|. В пятом такте константа -Кп пересылается из регистра 20 в регистр 21, из блока 13 памяти значений весовых коэффициентов по адресу А()2 выбирается коэффициент log2(A 2-2 )/(()-|-log2A (), который, пройдя мультиплексор 11, записывается в регистр 22. В этом же такте операнд A l, выдаваемый регистром 17, проходит через сдвигатель 15, и А |2 записывается в регистр 13, а в регистр 17 поступает новый операнд А а. В шестом такте сумматор-вычитатель 7 складывает содержимое регистров 21, 22, и результат log2A o -A o + )+log2A n записывае- ся в регистр 5; в регистр 20 записывается число К, а в регистр 25 - порядок К- числа А 2 из регистра 17. В седьмом такте результат log2A o выдается из регистра 5 результата на выход 37 устройства. Далее вычисления повторяются с периодом два такта.

Формула изобретения

Устройство для быстрого преобразования Фурье, содержащее умножитель, регистр числа, регистр коэффициента, регистр произведения, первый и второй сумматоры-вычи- татели, первый мультиплексор, регистр адреса, блок памяти весовых коэффициентов, блок памяти значений арктангенса, сдвигатель, ключ, шифратор порядка, первый и второй регистры порядка, блок сравнения, мультиплексор порядка, синхронизатор, элемент И, первый элемент ИЛИ, причем адресным входом устройства является первый информационный вход первого мультиплексора, выход которого подключен к информационному входу регистра адреса, выход которого подключен к адресному входу блока памяти весовых коэффициентов, выход которого соединен с выходом блока памяти значений арктангенса, ключа и подключен к информационному входу регистра коэффициента, выход которого подключен к первому входу умножителя, второй вход которого подключен к выходу регистра числа, а выход умножителя подключен к первому информационному входу первого сумматора- вычитателя, выход которого подключен к

информационному входу регистра произведения, выход которого подключен к второму информационному входу первого сумматора- вычитателя, выход шифратора порядка подключен к информационному входу первого регистра порядка, первому входу б. юка сравнения и первому информационному входу мультиплексора порядка, второй информационный вход которого соединен с вторым входом блока сравнения и подключен к выходу регистра порядка, вход разрешения записи которого подключен к выходу первого элемента ИЛИ, первый вход которого соединен с первым управляющим входом мультиплексора порядка и подключен к выходу

5 элемента И, первый вход которого подк.чю- чен к выходу блока сравнения, отличающееся тем, что, с целью повышения быстродействия, в него введены второй, третий и четвертый мультиплексоры, шесть регистров, блок памяти значений констант, регистр при0 знаков, второй и третий элементы ИЛИ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к управляющему входу второго мультиплексора, первый информационный вход которого соединен с первым

5 информационным входом третьего мультиплексора и подключен к выходу первого регистра, информационный вход которого является информационным входом устройства и соединен с информационным входом второго регистра, выход которог о подключен

0 к вторым информационным входам третьего мультиплексора и второго мультиплексора, выход которого подключен к информационному входу сдвигателя, выход которого соединен с выходом блока памяти значений констант, выходом третьего регистра и под5 ключен к информационному входу третьего ключа, второму информационному входу первого мультиплексора, информационному входу регистра числа, информационным входам третьего регистра и четвертого регистра,

д выход которого подключен к информационному входу пятого регистра, выход которого подключен к первому информационному входу второго сумматора-вычитателя, выход которого подключен к информационному входу регистра результата, выход которого

5 является информационным выходом устройства и подключен к третьему информационному входу третьего мультиплексора, выход которого подключен к входу шифратора порядка, выход регистра произведения подключен к адресному входу блока памяти

0 значений арктангенса и первому информационному входу четвертого мультиплексо))а, второй информационный вход которого подключен к выходу блока памяти весовых коэффициентов, а выход четвертого мультиплексора подключен к информационному входу шестого регистра, выход которого подключен к второму информационному входу второг о сумматора-вычитателя, управляющий вход которого подключен к выходу второго эле5

мента ИЛИ, первый вход которого чен к первому разряду выхода регистра признаков, первый разряд информационного входа которого подключен к выходу блока сравнения, второй разряд информационного входа регистра признаков соединен с первым входом третьего элемента ИЛИ и подключен к второму разряду выхода регистра признаков, выход третьего элемента ИЛИ подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третий информационный вход мультиплексора порядка является входом порядка устройства, выходы знаковых разрядов первого и второго регистров подключены к входам соответственного третьего и четвертого разрядов регистра признаков, остальные разряды выхода которого подключены к входам соответствующих разрядов первого адресного входа блока памя ти значений констант, выход второго регистра порядка подключен к второму адресному входу блока памяти значений констант и является выходом порядка устройства, первым входом задания режима работы которого являются соединенные между собой второй вход третьего элемента ИЛИ, вход управления записью блока памяти значений констант и вход задания режима работы синхронизатора, вход запуска которого является входом запуска устройства, второй вход задания режима работы которого подключен к входу управления считыванием блока памяти значений констант и установочному входу синхронизатора, выходы которого с первого по двенадцатый подключены к входам разрешения записи соответственно регистра числа, регистра коэффициента, регистра произведеГ

Уагг

Составитель А. Баранов Редактор А. МаковскаяТехред И. ВересКорректор Н. Король

Заказ 1809/54Тираж 704Подписное

ВНИИПИ Государственного комитета СССР по делам изабретений и открытий

113035, Москва, Ж - 35, Раушская иаб., д. 4/5 Производственно-полиграфическое предприятие, г Ужгород, ул. Проектная, 4

5

кия, регистра результата, регистра адреса, первого, второго, третьего, четвертого, пятого и шестого регистров, второго регистра порядка, выходы синхронизатора с тринадцатого по восемнадцатый подключены соответственно к входам управления записью блока памяти весовых коэффициентов и блока памяти значений арктангенса, тактовому входу сдвигателя, управляющему входу ключа, тактовому входу третьего регистра и входу управления считыванием блока памяти значений констант, управляющий вход первого мультиплексора подключен к девятнадцатому выходу синхронизатора, выходы которого с двенадцатого по двадцать второй подключены соответственно к первому и второму входам выборки зоны блока памяти весовых коэффициентов и входу выборки зоны блока памяти значений арктангенса, первый и второй управляющие входы третьего мультиплексора и управляющий вход четвертого мультиплексора подключены соответственно к выходам синхронизатора с двадцать третьего по двадцать пятый, выходы которого с двадцать шестого по двадцать девятый подключены к вторым входам

5 соответственно первого и второго элементов ИЛИ, элемента И и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, установочный и управляющий входы первого сумматора-вычитателя подключены соответственно к тридцатому и тридцать первому выходам синхронизатора,

0 тридцать второй и тридцать третий выходы которого подключены соответственно к установочному входу второго сумматора-вычитателя и второму управляющему входу мультиплексора порядка.

0

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для быстрого преобразования Фурье | 1989 |

|

SU1633425A1 |

| Устройство для быстрого действительного преобразования Фурье | 1986 |

|

SU1476488A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

Изобретение относится к вычислительной технике и предназначено для построения систем цифровой обработки сигналов, основанных на выполнении алгоритма быстрого преобразователя Фурье. Цель изобретения- повышение быстродействия. Поставленная цель достигается за счет того, что в состав устройства входит умножитель 1, регистр числа 2, регистр коэффициента 3, регистр произведения 4, регистр результата 5, сум- маторы-вычитатели 6, 7, мультиплексоры 8 - 11, регистр адреса 12, блок памяти 13 весовых коэффициентов, блок памяти 14 значений арктангенса, сдвигатель 15, ключ 16, регистры 17 - 22, шифратор порядка 23, регистры порядка 24, 25, блок сравнения 26, мультиплексор 27, блок памяти 28 значений констант, регистр признаков 29, синхронизатор 30, элемент И 31, элементы ПЛИ 32-34, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 35, информационный вход 31, адресный вход 38, вход 39 и выход 40 порядка устройства. 3 ил. .JS i (Л

| Устройство для выполнения операций присоединения списка | 1984 |

|

SU1206808A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-30—Публикация

1986-11-18—Подача