Изобретение относится к средствам вычислительной техники, предназначено для получения комплексного спектра Фурье по типу скользящей временной выборки с разверткой вектора в реальном масштабе времени и может быть использовано при решении задач цифровой обработки сигналов в специализированных системах, требующих высокого быстродействия цифровой аппаратуры.

Известно (а. с. 1363240, кл. G 06 F 15/332, 1987) устройство для вычисления скользящего спектра, которое содержит два блока памяти, предназначенные доя накопления исходных отсчетов и хранения синусной и косинусной компонент спектра, блок памяти коэффициентов, мультиплексор, три триггера, сумматор, вычитатель, арифметический блок и блок управления.

Недостатком устройства является необходимость хранения постоянных коэффициентов и низкое быстродействие.

Наиболее близким техническим решением к изобретению является анализатор спектра (а.с. 1013970, кл. G 06 F 15/332, 1983), содержащий аналого-цифровой преобразователь (АЦП), первый, второй и третий блоки памяти, блок постоянной памяти, первый, второй и третий сумматоры, выход АЦП подключен к входу первого блока памяти и к первому входу первого сумматора, второй вход которого подключен к выходу первого блока памяти, а вход АЦП является входом анализатора, который также содержит коммутатор и блок суммирования, выход которого соединен с входом коммутатора, первый выход которого подключен к первому входу второго сумматора, выход которого является первым выходом анализатора и соединен с входом второго блока памяти, выход которого подключен к второму входу второго сумматора, выход блока постоянной памяти соединен с управляющим входом коммутатора, второй выход которого подключен к первому входу третьего сумматора, выход которого является вторым выходом анализатора и подключен к входу третьего блока памяти, выход которого соединен с вторым входом третьего сумматора, причем вход блока суммирования соединен с выходом первого сумматора.

Недостатком данного устройства является сложность блока суммирования и коммутатора, пропорциональная длине блока данных для дискретного преобразования Фурье (ДПФ) и отсутствие возможности обработки комплексных входных данных. Данное устройство не обеспечивает создание быстродействующего анализатора спектра с ограниченной сверху сложностью для больших длин блоков данных ДПФ.

В этой связи важнейшей задачей является создание нового устройства для получения комплексного спектра Фурье по типу скользящей временной выборки с новым арифметическим блоком для обработки комплексных входных данных с разверткой вектора, тем самым создается возможность выполнения прямого и обратного ДПФ с использованием блока развертки вектора, работающего на базе блока взвешенного суммирования с ограниченной сверху сложностью, и нового блока управления процессом вычисления, который осуществляет распределение тактовых и управляющих сигналов между блоками устройства. Блок развертки вектора осуществляет последовательные повороты входного вектора на фиксированный малый угол, что позволяет вычислять один поворот за один такт при малых аппаратурных затратах с любой наперед заданной точностью. Полученные в результате развертки вектора комплексные числа используются для обновления соответствующих спектральных коэффициентов.

Техническим результатом заявленного устройства для вычисления скользящего спектра является повышение быстродействия получения спектра и увеличение функциональных возможностей обработки комплексных входных данных, что позволяет использовать данное устройство в системах цифровой обработки сигналов, в автоматизированных системах управления непрерывными процессами, в том числе в системах обработки речевых сигналов в реальном масштабе времени.

Указанный технический результат достигается тем, что устройство для вычисления скользящего спектра содержит первый, второй и третий блоки памяти, первый, второй и третий сумматоры, причем первый вход первого сумматора соединен с входом первого блока памяти, выход которого соединен с вторым входом первого сумматора, второй вход второго сумматора соединен с выходом второго блока памяти, вход которого соединен с выходом второго сумматора и является первым выходом устройства, второй вход третьего сумматора соединен с выходом третьего блока памяти, вход которого соединен с выходом третьего сумматора и является вторым выходом устройства, отличающееся тем, что оно содержит коммутатор и блок развертки вектора, второй вход которого подключен к выходу четвертого сумматора, к второму входу которого подключен выход четвертого блока памяти, вход которого соединен с первым входом четвертого сумматора и с выходом регистра ординаты, вход которого является вторым входом устройства, первый вход которого подключен к входу регистра абсциссы, выход которого соединен с первым входом первого сумматора, выход которого соединен с первым входом блока развертки вектора, первый и второй выходы которого соединены с входами пятого и шестого блоков памяти соответственно, выходы которых соединены с первым и вторым входами коммутатора соответственно, первый и второй выходы которого соединены с первыми входами второго и третьего сумматоров соответственно, входы режима работы и внешнего строба устройства соединены с первым и вторым входами блока управления соответственно, вход сброса памяти устройства соединен с входами обнуления первого, второго, третьего и четвертого блоков памяти и с третьим входом блока управления, первая выходная шина которого соединена с адресными входами первого и четвертого блоков памяти, вторая выходная шина блока управления соединена с адресными входами пятого и шестого блоков памяти, третья выходная шина блока управления соединена с адресными входами второго и третьего блоков памяти, четвертая выходная шина блока управления соединена с управляющими входами коммутатора, первый тактовый выход блока управления соединен с входами записи регистров абсциссы и ординаты, второй тактовый выход блока управления соединен с входами записи первого и четвертого блоков памяти, третий тактовый выход блока управления соединен с первым тактовым входом блока развертки вектора, четвертый тактовый выход блока управления соединен с вторым тактовым входом блока развертки вектора, пятый тактовый выход блока управления соединен с входами записи пятого и шестого блоков памяти, шестой тактовый выход блока управления соединен с входами записи второго и третьего блоков памяти, первый и второй управляющие выходы блока управления соединены с первым и вторым управляющими входами блока развертки вектора соответственно, выход строба выходных данных блока управления является одноименным выходом устройства, выход признака окончания счета блока управления является одноименным выходом устройства; при этом, блок развертки вектора содержит два коммутатора, четыре регистра, два арифметических блока и один элемент НЕ, причем первый вход блока развертки вектора соединен с первым входом первого коммутатора, выход которого соединен с входом первого регистра, выход которого соединен с входом первого аргумента первого арифметического блока и с входом второго аргумента второго арифметического блока, выход которого соединен с входом четвертого регистра, выход которого является вторым выходом блока развертки вектора и соединен с вторым входом второго коммутатора, первый вход которого является вторым входом блока развертки вектора, выход второго коммутатора соединен с входом второго регистра, выход которого соединен с входом первого аргумента второго арифметического блока и с входом второго аргумента первого арифметического блока, выход которого соединен с входом третьего регистра, выход которого соединен с вторым входом первого коммутатора и является первым выходом блока развертки вектора, первый управляющий вход блока развертки вектора соединен с управляющим входом первого арифметического блока и с входом элемента НЕ, выход которого соединен с управляющим входом второго арифметического блока, второй управляющий вход блока развертки вектора соединен с управляющими входами первого и второго коммутаторов, первый тактовый вход блока развертки вектора соединен с входами записи первого и второго регистров, второй тактовый вход блока развертки вектора соединен с входами записи третьего и четвертого регистров; арифметический блок содержит блок изменения знака, блок взвешенного суммирования и вычитатель, причем вход первого аргумента арифметического блока соединен с первым входом блока взвешенного суммирования и с первым входом вычитателя, вход второго аргумента арифметического блока соединен с входом блока изменения знака, выход которого соединен с вторым входом блока взвешенного суммирования, выход которого соединен с вторым входом вычитателя, выход которого является выходом арифметического блока, управляющий вход арифметического блока соединен с управляющим входом блока изменения знака; блок управления содержит генератор тактовых импульсов, узел синхронизации, два счетчика, сумматор, два мультиплексора, регистр, блок переадресации, причем первый вход блока управления соединен с управляющим входом первого мультиплексора и с вторым входом узла синхронизации, первый выход которого соединен с вторым входом первого мультиплексора, первый вход которого является вторым входом блока управления, третий вход блока управления соединен с входом установки в "0" первого счетчика, счетный вход которого соединен с выходом первого мультиплексора и с третьим входом узла синхронизации, информационные выходы первого счетчика соединены с первым входом сумматора и являются первой выходной шиной блока управления, выход сумматора соединен с входом регистра, выход которого соединен с вторым входом сумматора и с входом блока переадресации, первая выходная шина которого является четвертой выходной шиной блока управления, вторая выходная шина блока переадресации подключена к первому входу второго мультиплексора, выход которого является второй выходной шиной блока управления, информационные выходы второго счетчика соединены с вторым входом второго мультиплексора и являются третьей выходной шиной блока управления, второй выход узла синхронизации соединен с входами установки в "0" регистра и второго счетчика, третий выход узла синхронизации соединен с входом записи регистра и со счетным входом второго счетчика, тринадцатый выход узла синхронизации соединен с управляющим входом второго мультиплексора, четвертый и пятый выходы узла синхронизации являются первым и вторым управляющими выходами блока управления соответственно, выход тактового генератора соединен с первым входом узла синхронизации, выход первого мультиплексора является первым тактовым выходом блока управления, выходы с восьмого по двенадцатый узла синхронизации являются тактовыми выходами блока управления с второго по шестой соответственно, шестой выход узла синхронизации является выходом строба выходных данных блока управления, седьмой выход узла синхронизации является выходом признака окончания счета блока управления.

Отличительным признаком изобретения является то, что в устройство дополнительно введены блок развертки вектора для генерации гармонических сигналов и коммутатор, причем второй вход блока развертки вектора подключен к выходу четвертого сумматора, к второму входу которого подключен выход четвертого блока памяти, вход которого соединен с первым входом четвертого сумматора и с выходом регистра ординаты, вход которого является вторым входом (мнимая часть) устройства, тем самым обеспечивается возможность обработки комплексных входных данных и вычисления прямого и обратного ДПФ, первый вход (вещественная часть) устройства подключен к входу регистра абсциссы, выход которого соединен с первым входом первого сумматора, выход которого соединен с первым входом блока развертки вектора, первый и второй выходы которого соединены с входами пятого и шестого блоков памяти соответственно, выходы которых соединены с первым и вторым входами коммутатора соответственно, первый и второй выходы которого соединены с первыми входами второго и третьего сумматоров соответственно, входы режима работы и внешнего строба устройства соединены с первым и вторым входами блока управления соответственно, вход сброса памяти устройства соединен с входами обнуления первого, второго, третьего и четвертого блоков памяти и с третьим входом блока управления, первая выходная шина которого соединена с адресными входами первого и четвертого блоков памяти, вторая выходная шина блока управления соединена с адресными входами пятого и шестого блоков памяти, третья выходная шина блока управления соединена с адресными входами второго и третьего блоков памяти, четвертая выходная шина блока управления соединена с управляющими входами коммутатора, первый тактовый выход блока управления соединен с входами записи регистров абсциссы и ординаты, второй тактовый выход блока управления соединен с входами записи первого и четвертого блоков памяти, третий тактовый выход блока управления соединен с первым тактовым входом блока развертки вектора, четвертый тактовый выход блока управления соединен с вторым тактовым входом блока развертки вектора, пятый тактовый выход блока управления соединен с входами записи пятого и шестого блоков памяти, шестой тактовый выход блока управления соединен с входами записи второго и третьего блоков памяти, первый и второй управляющие выходы блока управления соединены с первым и вторым управляющими входами блока развертки вектора соответственно, выход строба выходных данных блока управления является одноименным выходом устройства, выход признака окончания счета блока управления является одноименным выходом устройства.

Блок развертки вектора содержит два коммутатора, четыре регистра, два арифметических блока и один элемент НЕ, причем первый вход блока развертки вектора соединен с первым входом первого коммутатора, выход которого соединен с входом первого регистра, выход которого соединен с входом первого аргумента первого арифметического блока и с входом второго аргумента второго арифметического блока, выход которого соединен с входом четвертого регистра, выход которого является вторым выходом блока развертки вектора и соединен с вторым входом второго коммутатора, первый вход которого является вторым входом блока развертки вектора, выход второго коммутатора соединен с входом второго регистра, выход которого соединен с входом первого аргумента второго арифметического блока и с входом второго аргумента первого арифметического блока, выход которого соединен с входом третьего регистра, выход которого соединен с вторым входом первого коммутатора и является первым выходом блока развертки вектора, первый управляющий вход блока развертки вектора соединен с управляющим входом первого арифметического блока и с входом элемента НЕ, выход которого соединен с управляющим входом второго арифметического блока, второй управляющий вход блока развертки вектора соединен с управляющими входами первого и второго коммутаторов, первый тактовый вход блока развертки вектора соединен с входами записи первого и второго регистров, второй тактовый вход блока развертки вектора соединен с входами записи третьего и четвертого регистров. Арифметический блок содержит блок изменения знака, блок взвешенного суммирования, в котором весовыми коэффициентами являются тригонометрические функции от фиксированного угла, что позволяет повысить скорость вычисления поворота вектора, и вычитатель, причем вход первого аргумента арифметического блока соединен с первым входом блока взвешенного суммирования и с первым входом вычитателя, вход второго аргумента арифметического блока соединен с входом блока изменения знака, выход которого соединен с вторым входом блока взвешенного суммирования, выход которого соединен с вторым входом вычитателя, выход которого является выходом арифметического блока, управляющий вход арифметического блока соединен с управляющим входом блока изменения знака.

Новый блок управления содержит генератор тактовых импульсов, узел синхронизации для распределения тактовых импульсов, два счетчика -счетчик времени и счетчик индекса, сумматор, два мультиплексора, регистр, блок переадресации, необходимый в том случае, если часть значений повернутых векторов получается из вычисленных в блоке развертки вектора путем перестановки их компонент и изменений их знаков, причем первый вход блока управления, задающий режим работы устройства и обеспечивающий внешний/внутренний строб входных данных, соединен с управляющим входом первого мультиплексора и с вторым входом узла синхронизации, первый выход - внутренний строб - которого соединен с вторым входом первого мультиплексора, первый вход которого является вторым входом - внешний строб - блока управления, третий вход блока управления соединен с входом установки в "0" первого счетчика для установки нулевого значения времени, счетный вход которого соединен с выходом первого мультиплексора, таким образом, строб входных значений увеличивает значение счетчика времени на "1", и с третьим входом узла синхронизации, информационные выходы первого счетчика соединены с первым входом сумматора и являются первой выходной шиной блока управления, выход сумматора соединен с входом регистра, выход которого соединен с вторым входом сумматора и с входом блока переадресации, первая выходная шина которого является четвертой выходной шиной блока управления, вторая выходная шина блока переадресации подключена к первому входу второго мультиплексора, выход которого является второй выходной шиной блока управления, информационные выходы второго счетчика соединены с вторым входом второго мультиплексора и являются третьей выходной шиной блока управления, второй выход узла синхронизации соединен с входами установки в "0" регистра и второго счетчика, третий выход узла синхронизации соединен с входом записи регистра и со счетным входом второго счетчика, тринадцатый выход узла синхронизации соединен с управляющим входом второго мультиплексора, четвертый и пятый выходы узла синхронизации являются первым и вторым управляющими выходами блока управления соответственно, выход тактового генератора соединен с первым входом узла синхронизации, выход первого мультиплексора является первым тактовым выходом блока управления, выходы с восьмого по двенадцатый узла синхронизации являются тактовыми выходами блока управления с второго по шестой соответственно, шестой выход узла синхронизации является выходом строба выходных данных блока управления, седьмой выход узла синхронизации является выходом признака окончания счета блока управления.

Приведенный заявителем анализ уровня техники, включающий поиск по патентам и научно-техническим источникам информации и выявление источников, содержащих сведения об аналогах заявленного решения, позволил установить, что заявителем не обнаружен аналог, характеризующийся признаками, идентичными всем существенным признакам заявленного изобретения. Определение из перечня выявленных аналогов прототипа, как наиболее близкого решения по совокупности признаков, позволило выявить совокупность существенных по отношению к усматриваемому заявителем техническому результату отличительных признаков в заявленном объекте, изложенных в формуле изобретения.

Следовательно, заявленное изобретение соответствует требованию "новизна" по действующему законодательству. Для проверки соответствия заявленного изобретения требованию "изобретательского уровня" заявитель провел дополнительный поиск известных решений с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного изобретения, результаты которого показывают, что заявленное изобретение для специалиста не следует явным образом из известного уровня техники.

Следовательно, заявленное изобретение соответствует требованию "изобретательский уровень".

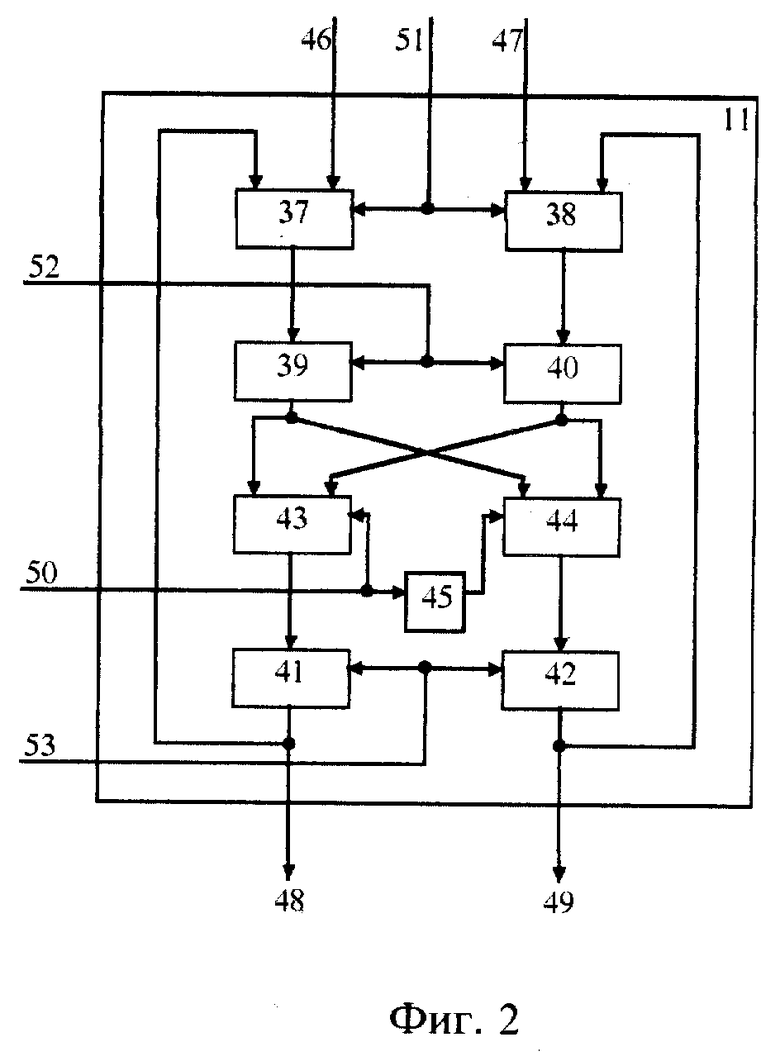

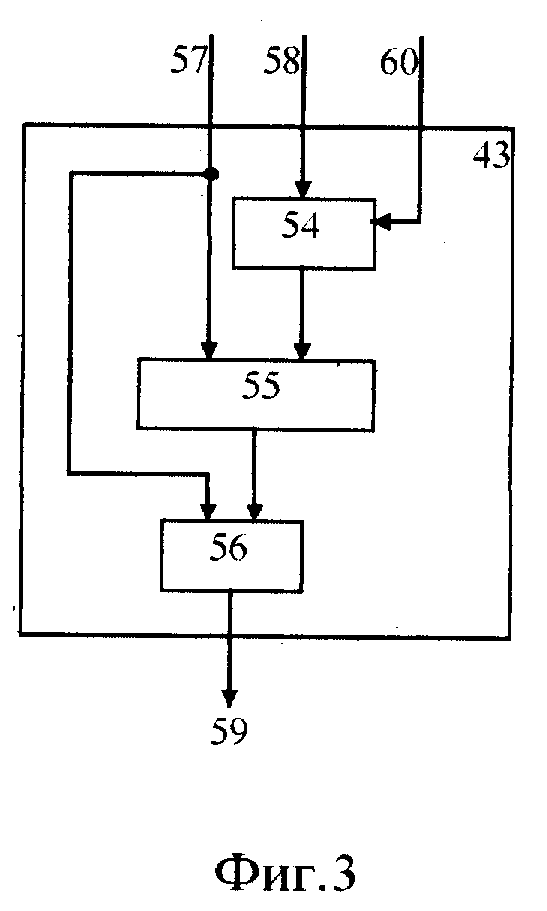

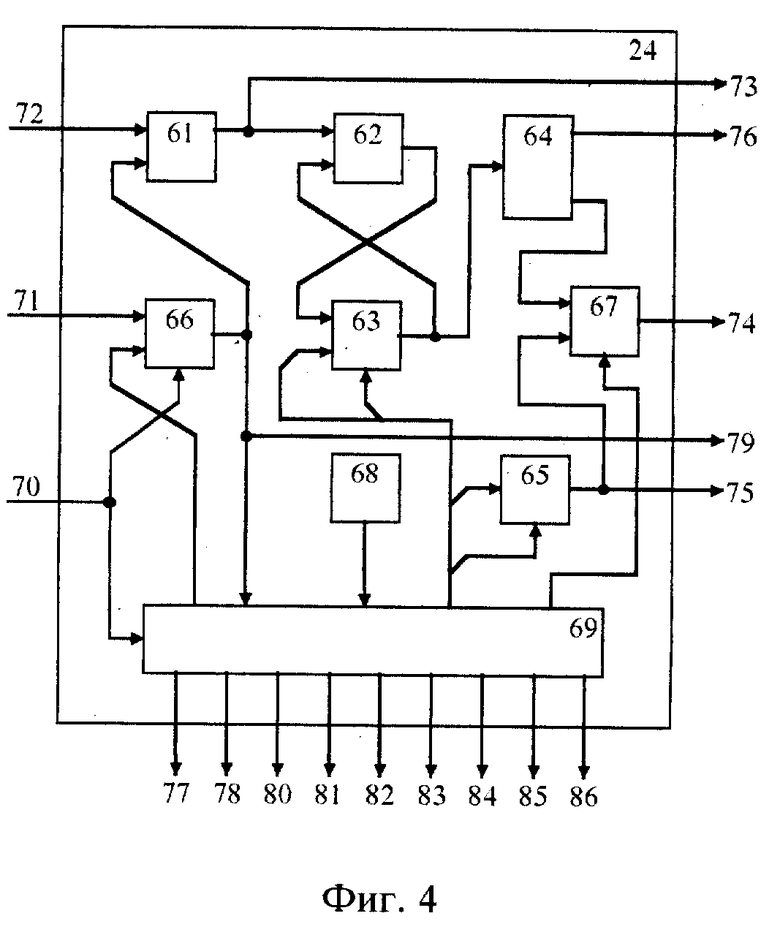

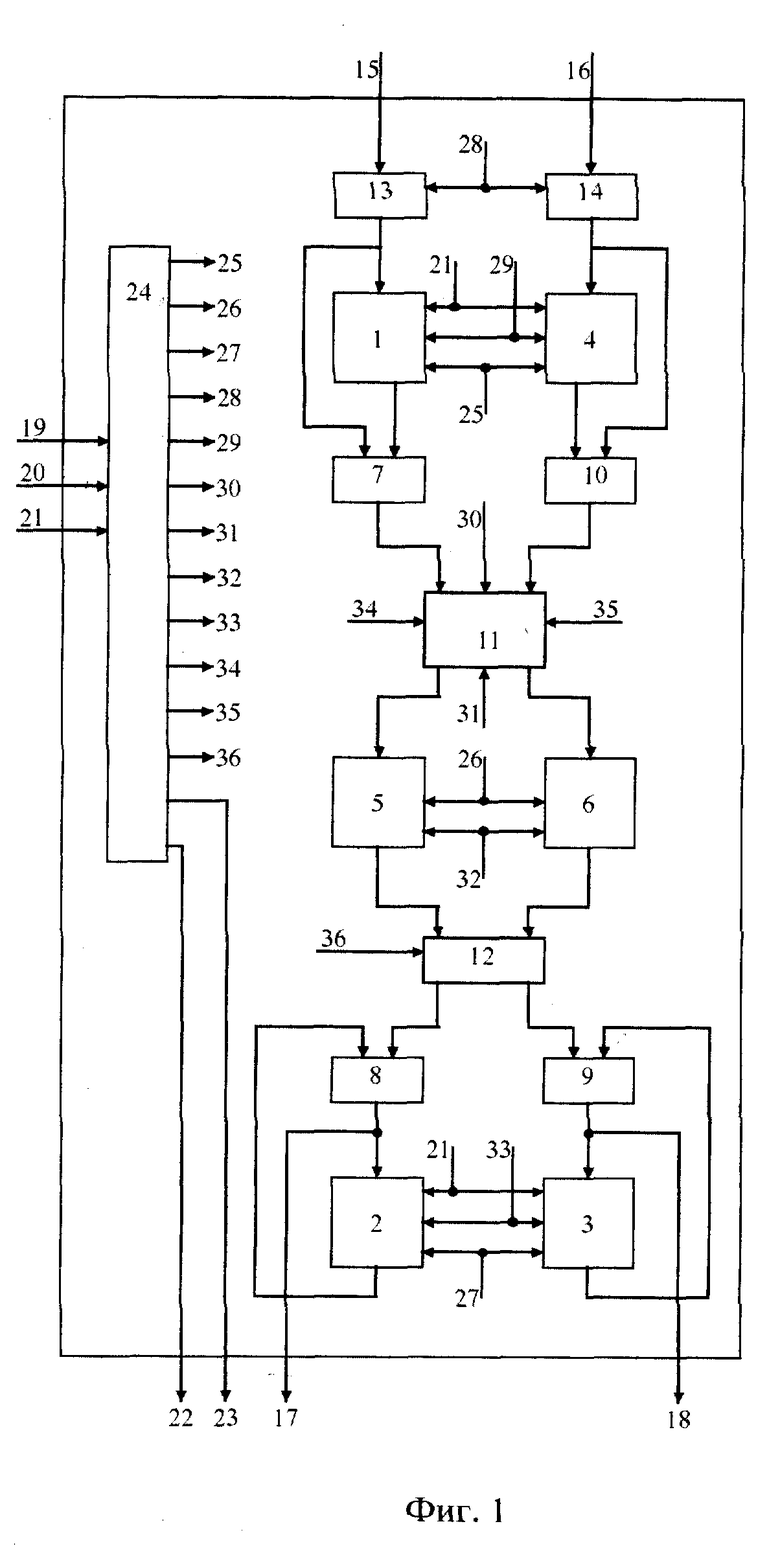

На фиг.1 представлена функциональная схема устройства; на фиг. 2 - схема блока развертки вектора; на фиг.3 - схема арифметического блока; на фиг. 4 - схема блока управления.

Устройство для вычисления скользящего спектра содержит (фиг. 1) первый 1, второй 2, третий 3, четвертый 4, пятый 5 и шестой 6 блоки памяти (оперативной), первый 7, второй 8, третий 9 и четвертый 10 сумматоры, блок развертки вектора 1 1, коммутатор 12, регистры абсциссы 13 и ординаты 14, первый 15 и второй 16 входы для вещественной и мнимой частей входных данных, первый 17 и второй 18 выходы для комплексных выходных данных устройства, вход режима работы устройства 19, вход внешнего строба 20 для входных данных, вход сброса памяти 21, выход строба выходных данных 22, выход признака окончания счета 23 и блок управления 24, причем первый 15 и второй 16 входы устройства соединены с регистрами абсциссы 13 и ординаты 14 соответственно, выходы которых соединены с первыми входами первого 7 и четвертого 10 сумматоров соответственно и с входами первого 1 и четвертого 4 блоков памяти соответственно, выходы которых соединены с вторыми входами первого 7 и четвертого 10 сумматоров соответственно, выходы которых соединены c первым и вторым входами блока развертки вектора 11 соответственно, первый и второй выходы которого соединены с входами пятого 5 и шестого 6 блоков памяти соответственно для сохранения результатов развертки входного вектора, причем выходы пятого 5 и шестого 6 блоков памяти соединены с первым и вторым входами коммутатора 12 соответственно, первый и второй выходы которого соединены с первыми входами второго 8 и третьего 9 сумматоров соответственно, к вторым входам которых подключены выходы второго 2 и третьего 3 блоков памяти соответственно, входы которых соединены с выходами второго 8 и третьего 9 сумматоров и являются первым 17 и вторым 18 выходами устройства соответственно. Для управления процессом вычисления посредством блока управления 24 входы режима работы 19 и внешнего строба 20 устройства соединены с первым и вторым входами блока управления 24 соответственно, вход сброса памяти 21 устройства соединен с входами обнуления первого 1, второго 2, третьего 3 и четвертого 4 блоков памяти и с третьим входом 21 блока управления 24, первая выходная шина 25 которого соединена с адресными входами первого 1 и четвертого 4 блоков памяти, вторая выходная шина 26 блока управления 24 соединена с адресными входами пятого 5 и шестого 6 блоков памяти, третья выходная шина 27 блока управления 24 соединена с адресными входами второго 2 и третьего 3 блоков памяти, первый тактовый выход 28 соединен с входами записи регистров абсциссы 13 и ординаты 14, второй тактовый выход 29 соединен с входами записи первого 1 и четвертого 4 блоков памяти, третий тактовый выход 30 соединен с первым тактовым входом блока развертки вектора 11, четвертый тактовый выход 31 соединен с вторым тактовым входом блока развертки вектора 11, пятый тактовый выход 32 соединен с входами записи пятого 5 и шестого 6 блоков памяти, шестой тактовый выход 33 соединен с входами записи второго 2 и третьего 3 блоков памяти, первый 34 и второй 35 управляющие выходы блока управления 24 соединены с первым и вторым управляющими входами блока развертки вектора 11 соответственно, четвертая выходная шина блока управления 24 соединена с управляющими входами коммутатора 12, выход строба выходных данных 22 блока управления 24 является одноименным выходом устройства, выход признака окончания счета 23 блока управления 24 является одноименным выходом устройства.

Блок развертки вектора 11 содержит (фиг.2) первый 37 и второй 38 коммутаторы, первый 39, второй 40, третий 41 и четвертый 42 регистры, первый 43 и второй 44 арифметические блоки, элемент НЕ 45, первый 46 и второй 47 входы, первый 48 и второй 49 выходы, причем первый вход 46 блока развертки вектора соединен с первым входом первого коммутатора 37, выход которого соединен с входом первого регистра 39, выход которого соединен с входом первого аргумента первого арифметического блока 43 и с входом второго аргумента второго арифметического блока 44, выход которого соединен с входом четвертого регистра 42, выход которого является вторым выходом 49 блока развертки вектора и соединен с вторым входом второго коммутатора 38, первый вход которого является вторым входом 47 блока развертки вектора, причем выход второго коммутатора 38 соединен с входом второго регистра 40, выход которого соединен с входом первого аргумента второго арифметического блока 44 и с входом второго аргумента первого арифметического блока 43, выход которого соединен с входом третьего регистра 41, выход которого соединен с вторым входом первого коммутатора 37 и является первым выходом 48 блока развертки вектора; первый управляющий вход 50 блока развертки вектора задает направление вращения входного вектора и с этой целью соединен с управляющим входом первого арифметического блока 43 и с входом элемента НЕ 45, выход которого соединен с управляющим входом второго арифметического блока 44, второй управляющий вход 51 блока развертки вектора соединен с управляющими входами первого 37 и второго 38 коммутаторов, первый тактовый вход 52 блока развертки вектора соединен с входами записи первого 47 и второго 48 регистров, второй тактовый вход 53 блока развертки вектора соединен с входами записи третьего 41 и четвертого 42 регистров.

Арифметический блок 43 содержит (фиг.3) блок изменения знака 54, блок взвешенного суммирования 55 и вычитатель 56, причем вход первого аргумента 57 соединен с первым входом блока взвешенного суммирования 55 и с первым входом вычитателя 56, вход второго аргумента 58 соединен с входом блока изменения знака 54, выход которого соединен с вторым входом блока взвешенного суммирования 55, выход которого соединен с вторым входом вычитателя 55, выход которого является выходом арифметического блока 59, управляющий вход арифметического блока 60 соединен с управляющим входом блока изменения знака 54, причем изменение знака входного числа происходит при " 1 " на управляющем входе.

Арифметический блок 44 идентичен арифметическому блоку 43.

Блок управления 24 обеспечивает распределение тактовых и управляющих сигналов, содержит (фиг. 4) первый счетчик 61 времени по модулю N (N -длина блока данных для ДПФ), сумматор 62 по модулю N, регистр 63, блок переадресации 64, второй счетчик 65, первый 66 и второй 67 мультиплексоры, генератор тактовых импульсов 68, узел синхронизации 69, первый 70, второй 71 и третий 72 входы блока управления, первую 73, вторую 74, третью 75 и четвертую 76 выходные шины, первый 77 и второй 78 управляющие выходы, первый 79, второй 80, третий 81, четвертый 82, пятый 83 и шестой 84 тактовые выходы, выход строба выходных данных 85 и выход признака окончания счета 86, причем первый вход 70 блока управления соединен с управляющим входом первого мультиплексора 66 и с вторым входом узла синхронизации 69, первый выход которого соединен с вторым входом первого мультиплексора 66, первый вход которого является вторым входом 71 блока управления, третий вход 72 блока управления соединен с входом установки в "0" первого счетчика 61, счетный вход которого соединен с выходом первого мультиплексора 66 и с третьим входом узла синхронизации 69, информационные выходы первого счетчика 61 соединены с первым входом сумматора 62 и являются первой выходной шиной 73 блока управления, выход сумматора 62 соединен с входом регистра 63, выход которого соединен с вторым входом сумматора 62 и с входом блока переадресации 64, первая выходная шина которого является четвертой выходной шиной 76 блока управления, вторая выходная шина блока переадресации 64 подключена к первому входу второго мультиплексора 67, выход которого является второй выходной шиной 74 блока управления, информационные выходы второго счетчика 65 соединены с вторым входом второго мультиплексора 67 и являются третьей выходной шиной 75 блока управления, второй выход узла синхронизации 69 соединен с входами установки в "0" регистра 63 и второго счетчика 65, третий выход узла синхронизации 69 соединен с входом записи регистра 63 и со счетным входом второго счетчика 65, тринадцатый выход узла синхронизации 69 соединен с управляющим входом второго мультиплексора 67, четвертый и пятый выходы узла синхронизации 69 являются первым 77 и вторым 78 управляющими выходами блока управления соответственно, выход тактового генератора 68 соединен с первым входом узла синхронизации 69, выход первого мультиплексора 66 является первым тактовым выходом 79 блока управления, выходы с восьмого по двенадцатый узла синхронизации являются тактовыми выходами блока управления с второго по шестой (80,81,82,83,84) соответственно, шестой выход узла синхронизации 69 является выходом строба выходных данных 85 блока управления, седьмой выход узла синхронизации 69 является выходом признака окончания счета блока управления 86.

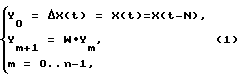

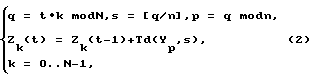

Устройство функционирует следующим образом. Работа устройства выражается формульными зависимостями

и

где

N - длина блока данных ДПФ;

W = exp(-jα), α = 2π/N;

X(t) - комплексное входное значение в момент времени t;

Zk - k-й спектральный коэффициент, n=[N/d], где d зависит от N и от вида входных данных, Td(Yp, s)- преобразование комплексного числа Yp путем перестановки его частей и изменения их знаков в зависимости от параметров d и s. Например, при четных N и комплексных входных данных d=2 (при развертке вектора вычисляются только первые [N/2] векторов, остальные получаются из вычисленных отражением их относительно точки начала координат)

Максимальное значение d равно 8 при N кратных 4 и действительных входных данных (при этом достаточно получение первых [N/8] векторов, остальные получаются из вычисленных соответствующей функцией Td(Yp,s), где s=0..7).

В общем случае для любого N и комплексных входных данных d=1, и n-N, s-[q/n]=0, Td(Yp,s)=Td(Yp0)=Yp.

Вычисление скользящего спектра начинается с инициализации устройства подачей сигнала сброса памяти. Устройство имеет два режима работы: внешний/внутренний строб входных данных. При этом новый цикл обновления спектра начинается в первом случае с приходом сигнала внешнего строба, во втором - после окончания предыдущего цикла. Сигнал строба с выхода первого мультиплексора 66 блока управления 24 увеличивает на "1" (по модулю N) счетчик времени 61, поступает на входы записи регистров абсциссы 13 и ординаты 14 и запускает узел синхронизации 68. Далее комплексная разность входных значений в моменты времени (t) и (t-N) записывается в первый 39 и второй 40 регистры блока развертки вектора 11. Затем по формульной зависимости (1) выполняется n поворотов входного вектора на угол (2π/N) с запоминанием полученных векторов в пятом 5 и шестом 6 блоках памяти. Полученные вектора прибавляются к соответствующим спектральным коэффициентам по формульной зависимости (2). Для этого в начале обнуляются регистр 63 и второй счетчик 65 блока управления 24, на вторую выходную шину 74 блока управления 24 подаются информационные выходы блока переадресации 64 через второй мультиплексор 67. Каждый такт увеличивает содержимое второго счетчика на "1" (индекс k) и содержимое регистра 63 на t по модулю N (индекс q), где t хранится в первом счетчике 61. На первую выходную шину блока переадресации 64 подается значение s (s= [q/n]), а на вторую выходную шину - индекс р (р = q mod n). Обновленный k-ый коэффициент сохраняется во втором 2 и третьем 3 блоках памяти и поступает на первый 17 (вещественная часть) и второй 18 (мнимая часть) выходы устройства в сопровождении сигнала строба выходных данных 22. При достижении k значения N цикл обновления спектра заканчивается и активизируется сигнал окончания счета 23 устройства. Новый цикл запускается следующим сигналом строба входных данных.

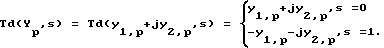

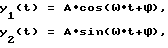

Блок развертки вектора функционирует следующим образом. В первый такт абсцисса (первый вход 46) и ордината (второй вход 46) входного вектора через первый 37 и второй 38 коммутаторы (при сигнале "0" на втором управляющем входе 51) поступают на входы первого 39 и второго 40 регистров, где и фиксируются по сигналу записи от первого тактового входа 52. Первый управляющий вход 50 задает направление вращения вектора на угол α первым 43 и вторым 44 арифметическими блоками. Абсцисса и ордината повернутого вектора поступают на входы третьего 41 и четвертого 42 регистров, где фиксируются сигналом записи от второго тактового входа 53 и передаются на третий 48 и четвертый 49 выходы соответственно, а также на вторые входы первого 37 и второго 38 коммутаторов и (при сигнале "1" на втором управляющем входе 51) на входы первого 39 и второго 40 регистров соответственно, и так далее. Таким образом, на первом 48 и на втором 49 выходах блока развертки вектора 11 формируются соответствующие сигналы

где  ω = ξ1•2π/N, ϕ = arctg(x2/x1),

ω = ξ1•2π/N, ϕ = arctg(x2/x1),

x1 и x2 - абсцисса и ордината входного вектора, ξ1 определяет направление вращения (первый управляющий вход 50) и равно 1 или (-1).

Арифметический блок 43 функционирует следующим образом. Значение x1 с входа первого аргумента 57 поступает на первый вход блока взвешенного суммирования 55, значение x2 с входа второго аргумента 58 поступает на вход блока изменения знака 54, с выхода которого значение ξ2x2 (где ξ2 равно 1 или (-1) в зависимости от состояния управляющего входа 60) поступает на второй вход блока взвешенного суммирования 55, на выход которого подается сумма

S = (1-cos(α))•x1+sin(α)•ξ2x2,

где

α = 2π/N = const.

На выход 59 арифметического блока 43 поступает разность

F = x1-S = x1•cos(α)-ξ2x2•sin(α).

Арифметический блок 44 полностью идентичен арифметическому блоку 43, но первый и второй входы арифметического блока 44 соединены соответственно с вторым и первым входами арифметического блока 43, а на управляющий вход арифметического блока 44 подается сигнал, противоположный сигналу на управляющем входе арифметического блока 43 (через элемент НЕ 45).

Таким образом, вышеизложенное свидетельствует о выполнении при использовании заявленного изобретения следующей совокупности условий:

- устройство для вычисления скользящего спектра, воплощающее заявленное изобретение при его осуществлении, предназначено для применения в системах цифровой обработки сигналов для вычисления прямого и обратного ДПФ с разверткой вектора с возможностью обработки комплексных входных данных, тем самым расширяется область применения кодеков в компактном аппаратурном исполнении с использованием в системах обработки речевой информации для автоматизированных систем управления непрерывными процессами;

- для заявленного изобретения в том виде, как оно охарактеризовано в формуле изобретения, подтверждена возможность его осуществления в соответствии с описанием и прилагаемым чертежом;

- устройство для вычисления скользящего спектра, воплощающее заявленное изобретение при его осуществлении, способно обеспечить достижение усматриваемого заявителем технического результата.

Следовательно, заявленное изобретение соответствует требованию "промышленная применимость".

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СОБСТВЕННЫХ ЗНАЧЕНИЙ МАТРИЦ | 2000 |

|

RU2168760C1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТНЫЙ ДИСКРИМИНАТОР | 1996 |

|

RU2143182C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ОШИБОК В КАНАЛЕ | 2001 |

|

RU2192038C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК СИНХРОНИЗАЦИИ В ПОТОКЕ ДАННЫХ | 2002 |

|

RU2224282C1 |

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТНЫЙ ДИСКРИМИНАТОР | 1996 |

|

RU2139640C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МОДУЛЯ ТРЕХМЕРНОГО ВЕКТОРА | 1993 |

|

RU2040039C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КООРДИНАТ | 1991 |

|

RU2007749C1 |

Изобретение относится к вычислительной технике и может быть использовано для вычисления скользящего спектра Фурье. Техническим результатом является повышение быстродействия и расширение функциональных возможностей за счет обработки сигналов в реальном масштабе времени. Устройство содержит блоки памяти, сумматоры, блок развертки вектора, коммутатор, регистры абсциссы и ординаты и блок управления. 3. з.п. ф-лы, 4 ил.

| Анализатор спектра | 1981 |

|

SU1013970A1 |

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

Авторы

Даты

1999-01-20—Публикация

1998-02-24—Подача