1

Изобретение относится к измерению электрических величин, в частности к измерению сдвига фаз между двумя периодическими сигналами и может быть использовано для измерения фазовых сдвигов в пределах, значительно больших ЗбО .

Известен цифровой фазометр, содержащий преобразователь фаза-временной интервал, выход которого , соединен с одним входом совпадения, другой вход - с выходом генератора счетных импульсов, а выход - со счетным входом счетчика, f 1 J.

Данное устройство обладает низкой точностью при измерении углов, превышающих збо.

Известно устройство для счета циклов в дискретной электронной фазометрии, содержащее счетчик долей фазового цикла, реверсивный счетчик целых циклов, блок управления, вентили записи, электронный блок определения перехода границы фазового цикла и его знака, выполненный на двух элементах совпадения и триггера, памяти, входы которого через вентили, записи соединены с потенциальными выходами старшего разряда счетчика долей фазового цикла, при этом входы одного из элементов совпадения соединены с нулевыми выходами двух старших разрядов счетчика и единичным выходом триггера памяти, входы

10 другого элемента совпадения соединены с единичными выходами двух старших разрядов счетчика долей фазового цикла и нулевым выходом триггера памяти, а выходы схем совпадеISния - с входами реверсивного счетчика целыхциклов f2J.

Известное устройство имеет высокую точность при изменении фазового сдвига в пределах, превышающих 360

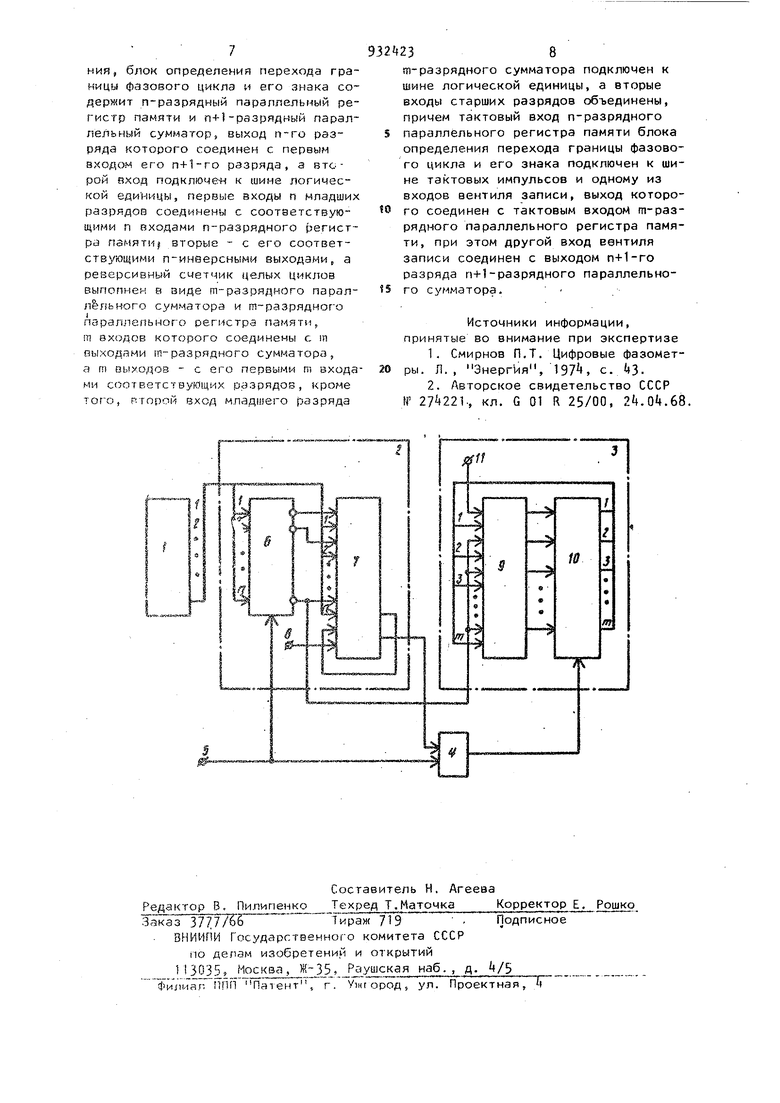

20 Однако, если разность двух последовательных значений сдвига фаз превышает 30°, то возникает аномальная ошибка измерения, заключающаяся в неправильном подсчете числа целых циклов сдвига фаз, в результате чего резко снижается точность измерения. Цель изобретения - повышение -точности измерений. Поставленная цель достигается тем, что в цифровом фазометое, содер жащем счетчик долей фазовогЪ цикла, выходами соединенный с блоком определения перехода границы фазового цикла и его знака, выходы которого соединены с реверсивным счетчиком целых циклов, и вентиль записи, блок определения перехода границы фазового цикла и его знака содержит п-разрядный параллельный регистр памяти, п+1-разрядный параллельный сумматор выход п-го разряда которого соединен с первым входом его п+1-разряда, а второй вход подключен к шине логи ческой единицы, первые входы п младших разрядов соединены с соответствующими п входами п-разрядного регистра памяти, вторые - с его соответствующими п инверсными выходами, а реверсивный счетчик целых циклов выполнен в виде т-разрядного параллельного сумматора и т-разрядного параллельного регистра памяти, m входов которого соединены с выходами т-разрядного сумматора, а m выходов с его первыми ш входами соответствующ 1х разрядов, кроме того второй вход младшего разрг да т-разрядного сумматора подключен к шине логической единицы, а вторые входы старших разрядов объединены, причем тактовы вход п-разрядного .параллельного регистра памяти блока определения перехода границы фазового цикла и его знака подключен к шине тактовых импульсов и к одному из входов вентиля записи, выход которого соединен тактовым входом т-разрядного параллельного регистра памяти, при этом другой вход вентиля записи соединен с выходом п+1-го разряда п+1-разрядного параллельного сумматора. На чертеже представлена функциональная схема предлагаемого устройства. , Цифровой фазометр состоит из сче чика 1 долей фазово.го цикла, блока 2 определения перехода границы фазового цикла иего знака, с реверси ного счетчика 3 целых циклов, вентиля Ц записи, шины 5 тактрвых импульсов. Блок 2 определения перехо да границы фазового цикла и его знака содержит п-разрядный параллельный регистр 6 памяти, п+1-разрядный параллельный сумматор 7 выход п-го разряда которого соединен с первым входом его п+1-го разряда, а второй вход подключен к шине 8 логической единицы, первые входы п младших разрядов соединены с cooтвeтctвyюu ими п входами п-разрядного регистра 6 памяти, вторые с его соответствующими п инверсными выходами. Реверсивный счетчик 3 целых циклов выполнен в виде т-разрядного параллельного сумматора 9 и т-разрядного параллельного регистра 10 памяти, m входов которого соединены с m выходами т-разрядного сумматора 9i а m выходов - с его первыми m входами соответствующих разрядов. Второй вход младшего разряда т-разрядного сумматора 9 подключен к шине 11 логической единицы, а вторые входы старших разрядов объединены, п входов п-разрядного параллельного регистра 6 памяти блока 2 определения перехода границы фазового цикла и его знака соединены с соответствующими п выходами счетчика 1 долей фазового цикла, инверсный выход старшего разряда с объединенными входами старших разрядов т-разрядного параллельного сумматора Э а тактовый вход подключен к шине 5 тактовых импульсов к одному из входов вентиля k записи, выход которого соедини с тактовУм входом т-разрядного параллельного регистра 10 памяти, при этом другой вход вентиля k записи соединен с выходом п+1-го разряда п+1-го разрядного параллельного сумматора 7Устройство работает следующим образом. Счетчик 1 долей фазового цикла измеряет и преобразует дробную часть величины сдвига фаз (цикл равный ЗбО принят за единицу) в параллельный двоичный арифметический п-разрядный код. Масштаб преобразования выбран так, чтобы при изменении сдвига фаз от О до ЗбО значение входного кода изменялось от О до 2 . Результат измерения дробной части последнего фазового сдвига с выходов счетчика 1 долей фазового цикла поступа.ет на один из п входов младших разрядов п+1-го разрядного сумматора 7, на другие п входов этих разрр дов с п инверсных выходов п-разрядного регистра 6 памяти поступает инверсный код дробной части предыдущего значения фазового сдвига. 3 n+1-M разряде п+1-го разрядного сумматора 7 производится сложение по модулю два значений п-го разряда, переноса f)-ro разряда п+1 разрядного сумматора .7 и единицы. В результате сложения на выходе п+1 разряда п+1-разрядного сумматора 7 либо возникает уровень логической единицы и открывается вентиль k записи, либо уровень логического нуля и вентиль k записи закрывается. Первый случай соответствует разности дробных частей двух послед-. них значений фазовых сдвигов большей 180, при этом фиксируется переход в соседний цикл фазового сдвига. Тактовый импульс с шины 5 проходит через вентиль k записи, поступает на тактовый вход т-разрядного регистра 10 памяти и записывает в виде параллельного двоичного арифметического кода число целых циклов последнего значения сдвига фаз. Если предыдущее значение дробной части сдвига фаз, записанное в п-раз рядном регистре 6 памяти меньше 180 , знак перехода фазового цикла отрицательный, значение числа целых циклов уменьшается на единицу. При этом с инверсного выхода, старшего разряда п-разрядного регистра 6 памяти на объединенные входы т-разрядного сумматора 9 поступает уровень логической единицы, т-разрядный сумматор 9 производит сложение двоичного кода числа целых циклов г редыду щего сдвига фаз, записанного в т-разрядном регистре 10 памяти с кодом, состоящим из одних единиц. Например, пусть число целых циклов предыдущего сдвига фаз равно 12, тогда число целых циклов последнего значения сдвига фэз определяется: Л 1111 Если дробная часть предыдущего значения сдвига фаз больше 180, знак перехода - положительный, число целых циклов увеличивается на единицу. На объединенные входы т-разрядного сумматора 9 поступает уровень логического нуля, а на вход младшего разряда - уровень логической единицы с шины 11 логической единицы. При 36 этом т-разрядный сумматор 9 производит сложение двоичного кода числа целых циклов предыдущего сдвига фаз с кодом, имеющим единицу в младшем разряде и нули в остальных. Например, операция определяется; 1100 0001 Второй случай соответствует разности дробных частей двух последних значений фазовых сдвигов меньшей 180 , при этом фиксируется отсутствие перехода в соседний цикл, вентиль k записи закрывается и в пп-разрядном регистре 10 памяти остается записанным двоичный код значения числа целых циклов предыдущего фазового сдвига. Причем как в случае записи в т-разрядный регистр 10 ;памяти, так и при отсутствии ее с ши;Ны 5 тактовых импульсов на тактовый :вход п-разрядного регистра 6 памяти поступает тактовый импульс и запи|сывает значение дробной части последнего сдвига фаз, которое поступает . на его п входов с п выходов счетчика 1 долей фазового цикла. При таком выполнении блока определения перехода границы фазового цикла и его знака и реверсивного счетчика целых циклов производится сравнение всех разрядов двоичных кодов значений дробных частей двух последних фазовых сдвигов. Следовательно, даже если их разность близка к 180, производится правильное определение числа целых циклов сдвига фаз.. Указанное значение разности фазовых сдаигов практически не возникает даже при минимальном отношении сигнал/шум в усилительных каналах цифрового фазометра. Таким образом, снижается вероятность возникновения аномальной ошибки, что приводит к повышению точности измерения сдвига фаз. Формула изобретения Цифровой фазометр, содержа14ий счетчик долей фазового цикла, выходами соединенный с блоком определения перехода границы фазового цикла и его знака, выходы которого соединены с реверсивным счетчиком целых циклов, и вентиль записи, отличающийся тем, что, c целью повышения точности измере7

НИИ, блок определений перехода границы фазового цикла и его знака содержит п-разрядный параллельный регистр памяти и п+1-разрядный парал лельный сумматор, выход разряда которого соединен с. первым входом его П+1-ГО разряда, а второй вход подключбН к шине логической единицы, первые входы п младших разрядов соединены с соотаетствующими п входами п--разрядного регистра памяти вторые - с его соответствующими п инверсными выходами, а реверсивный счетчик целых циклов выпопнен а виде т-разрядного паралл&яьного сумматора и т разрядного параллельного регистра памяти, ш входов которого соединены с in выходами in-разрядного сумматора, а m вь Уодов - с его первыми m входами соответствующих разрядов, кроме того, второй вход млад1)его разряда

.32if238

m-разрядного сумматора подключен к шине логической единицы, а вторые входы старших разрядов объединены, причем тактовый вход п-разрядного S параллельного регистра памяти блока определения перехода границы фазового цикла и его знака подключен к шине тактовых импульсов и одному из входов вентиля записи, выход которого го соединен с тактовым входом т-разрядного параллельного регистра памяти, при этом другой вход вентиля записи соединен с выходом п+1-го разряда п+1-разрядного параллельноtS го сумматора.

Источники информации, принятые во внимание при экспертизе

1.Смирнов П,Т. Цифровые фазометры. Л., Энерг1 я, 197, с. «43.

2.Авторское свидетельство СССР

W ., кл. G 01 R 25/00, 2+.0.68.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Цифровой фазометр | 1983 |

|

SU1188669A2 |

| Цифровой генератор частоты | 1984 |

|

SU1228095A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Цифровой фазометр | 1986 |

|

SU1348744A1 |

| Измерительный двухфазный генератор | 1986 |

|

SU1359751A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для умножения | 1984 |

|

SU1249507A1 |

| Корреляционный измеритель фазовых соотношений узкополосных случайных процессов | 1990 |

|

SU1714616A1 |

| Цифровой фазометр | 1988 |

|

SU1626186A2 |

Авторы

Даты

1982-05-30—Публикация

1980-01-02—Подача