1

элементах И, причем первьй выход распределителя импульсов подключен к первому входу первого триггера, а каждый . I -и выход распределителя им- пульсов, начиная с второго и по (и -1)-й включительно, подключен к первому входу i-го триггера непосредственно и через последовательно соединенные ( i-1)-e двухвходовые элементы И и ИЛИ к второму входу ( I -1)-го триггера, h-й выход распределителя импульсов подключен к второму входу (и -1)-го триггера и к объединенным вторым входам всех двухвходовых элементов ИЛИ, выход первого разряда h-разрядного сдвигающего регистра подключен через сумматор к объединенным вторым входам соответствующих h -2 двухвходовых элементов И, при этом первьй вход (h -1)-го двухвходового элемента И является первым входом блока уйравления фазовращателем, а выход подключен к информационному входу h -разрядного сдвигающего регистра и Р -входу h -го триггера, выход которого соединен с вторым входом полусумматора, вторым входом блока управления фазовращателем является второй вход (и -1)-f o двухвходового элемента И, объединенный с входами установки нуля распределителя импульсов и И -разрядного сдвигающего регистра и первым входом и-го двухвходового элемента И, второй вход которого является третьим входом блока управления фазов ращателем, а выход - со сченым входом распределителя импульсов, причем выход С И +1)-го двухвходового элемента И соединен с входом синхронизации h -го триггера, первый вход с h -м выходом распределителя импульсов, а второй вход объединен с входом сдвига И-разрядного сдвигающего регистра и является четвертым входом блока управления.фазовращателем, первой группой выходов которого я II л я ют ся выходы h-разрядного регисра, а выходами второй группы выходов ссю тветственно выходы соответствующи (1 -1 триггеров.

3. Элемент по п. 1, отличающийся тем, что управляемый фазовращатель выполнен на h -1 соединенных между собой последовательно фазовращателях .и и ключах, щшчем каждьй из И 1 ключей под90

ключен параллельно каждому из h -1 фазовращателей, входы управления h -1 ключей являются первыми входами управляемого фазовращателя, вход первого фазовращателя и выход (h-l)-ro фазовращателя являются соответственно третьим входом и выходом управляемого фазовраща- теля, между которыми включен ключ, вход управления которого яв- лязтся BTopbLM входом управляемого фазовращателя.,

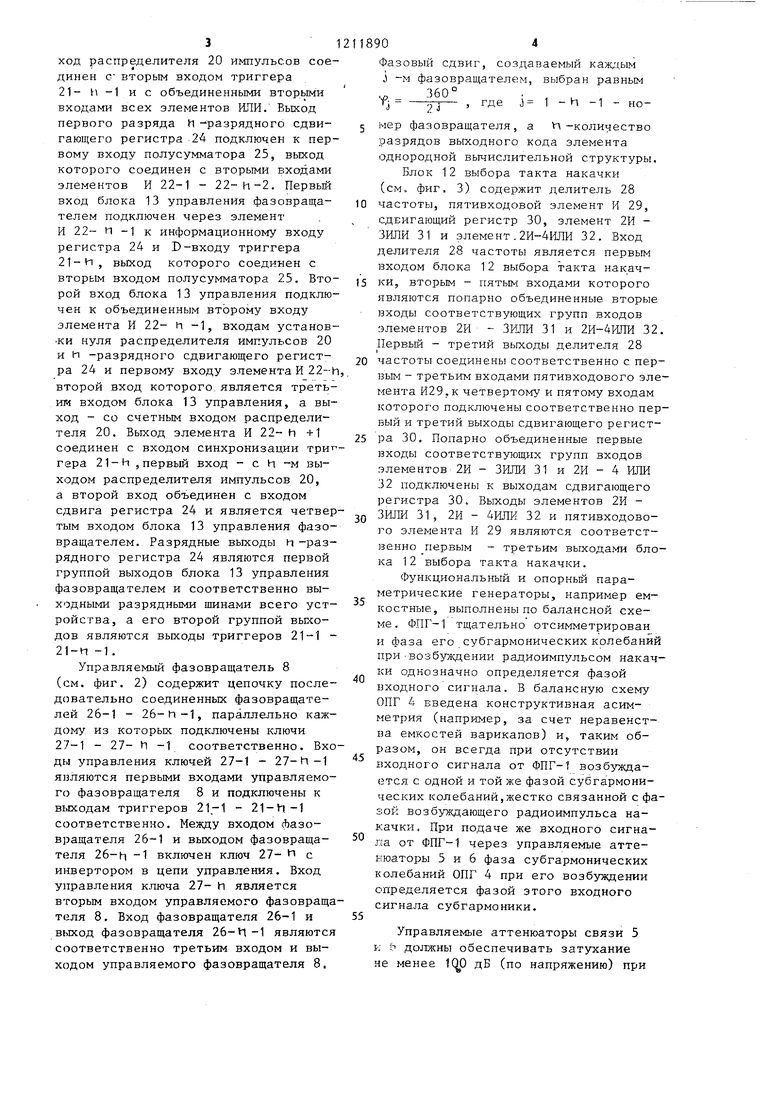

4. Элемент по п. 1, отличающийся тем, что блок выбора такта накачки выполнен на делителе частоты, сдвигающем регистре, пятивходовом элементе И, элементе 2И - ЗИЛИ и элементе 2И - 4ИЛИ, причем первый вход блока выбора такта накачки подключен к входу делителя частоты, первый и второй выходы которого подключены соответственно к первому и второму входам пятивходового элемента И, а третий выход подключен к объединенным третьему входу пятивходового элемента И и входу сдвигающего регистра, первый выход которого подключен к объединенным четвертому входу пятивходового элемента И и первым входам первых групп входов элементов 2И - ЗИЛИ и 2И - 4ИЛИ, второй выход - к объединенным первым входам вторых групп входов элементов 2И - ЗИЛИ и 2И - 4ИЛИ, а третий выход - к объединенным первым входам третьих групп входов элементов 2И - ЗИЛИ и 2И - 4ИЛИ и пятому входу пятивходового элемента И, объединенные попарно вторые входы первой группы входов элемента 2И - ЗИЛИ и второй группы входов элемента 2И - 4ИЛИ, вторые входы второй группы входов элемента 2И - ЗИЛИ и третьей группы входов элемента 2И - 4ИЛИ, вторые входы третьей группы входов элемента 2И - ЗИЛИ и первой группы входов элемента 2И - 4ИЛИ5 а также объединенные первый и второй входы четвертой группы входов элемента 2И - 4ИЛИ являются Соответственно вторым, третьим, четвертым и пятым входами блока выбора такта накачки, первым, вторым и третьим выходами которого являются соответственно выходы элементов 2И - ЗИЛИ, 2И - 4 ИЛИ и пятивходового элемента И.

Изобретение относится к области вычислительной техники и радиотехники, может быть использовано преимущественно при построении радиоим- пульсных однородных вычислительных структур, предназначенных для обрабоки радиосигналов, носителем информации в которых является фаза высокочастотных колебаний.

Цель изобретения - расширение функциональных возможностей путем обеспечения выполнения функции аналого-цифрового преобразования фазы радиосигнала.

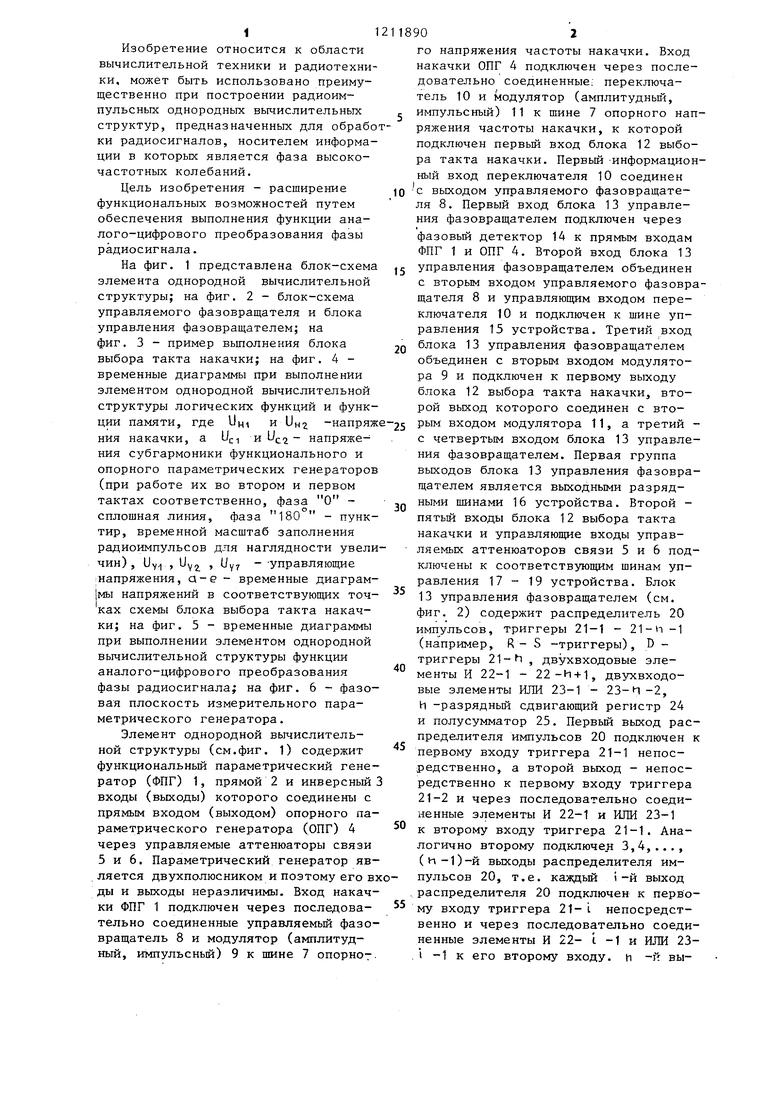

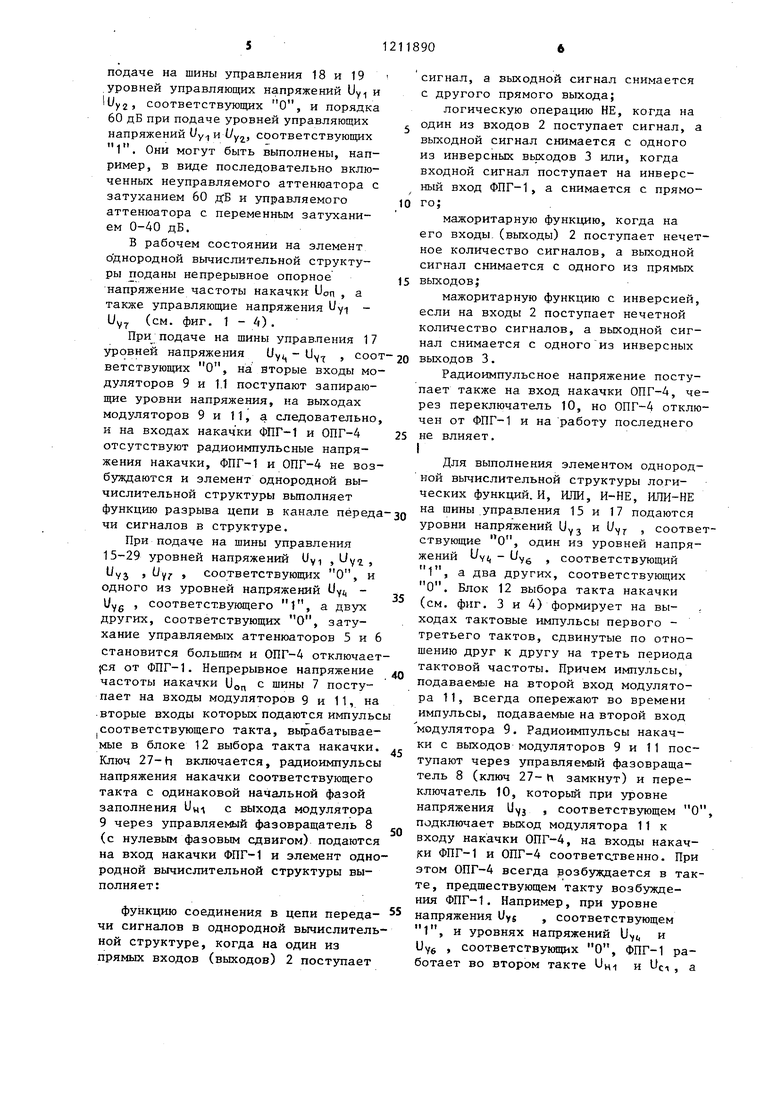

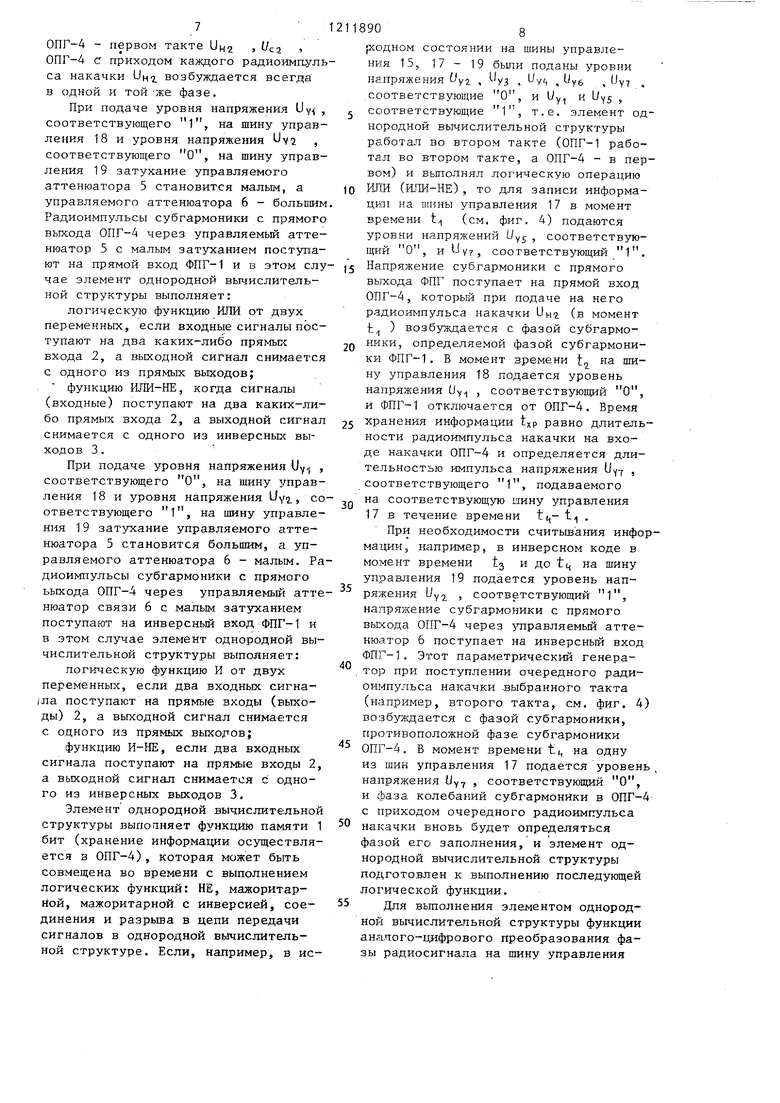

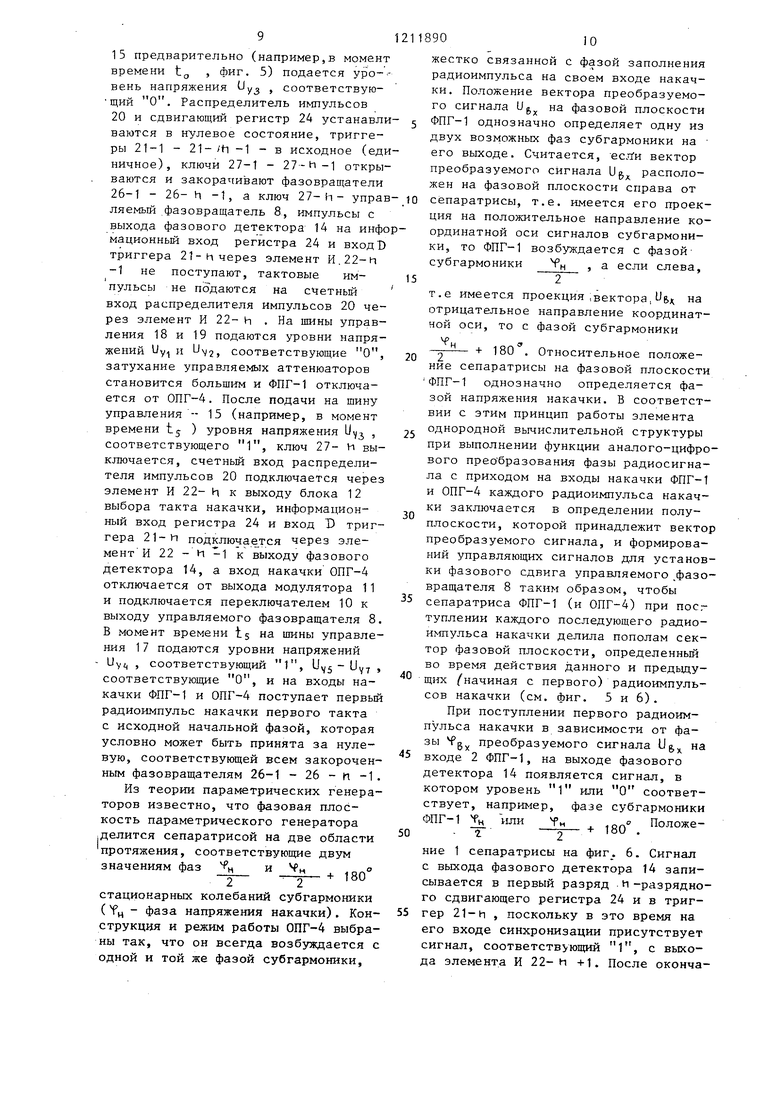

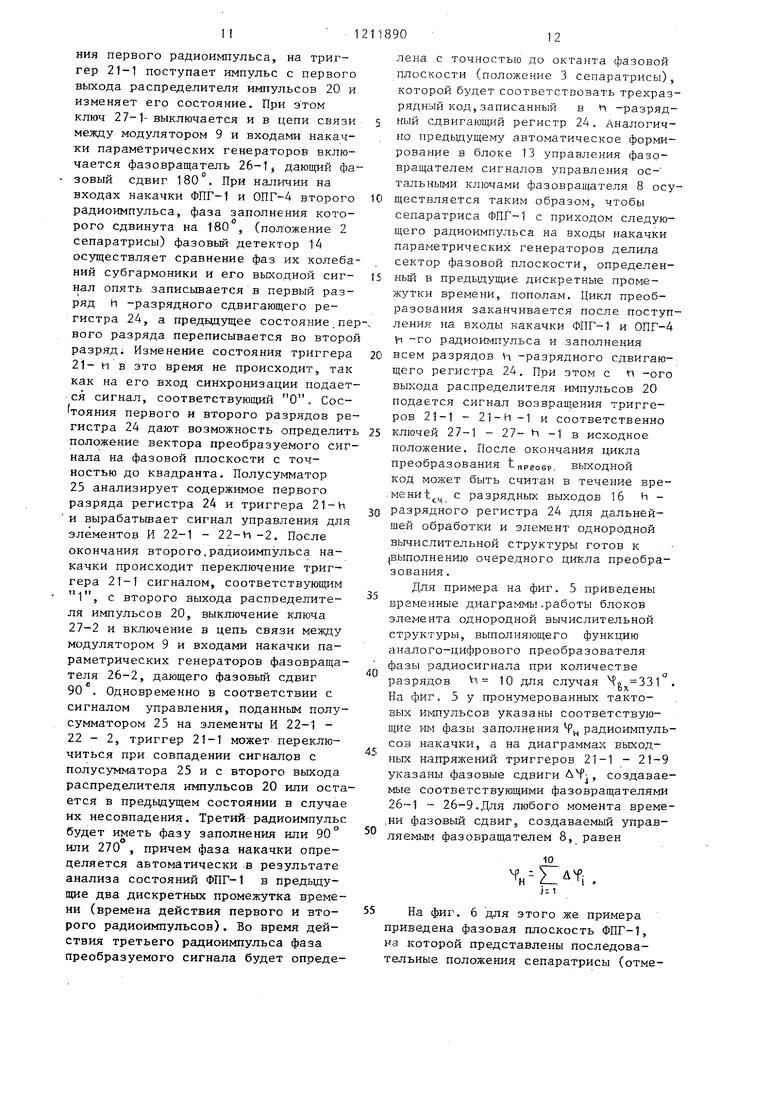

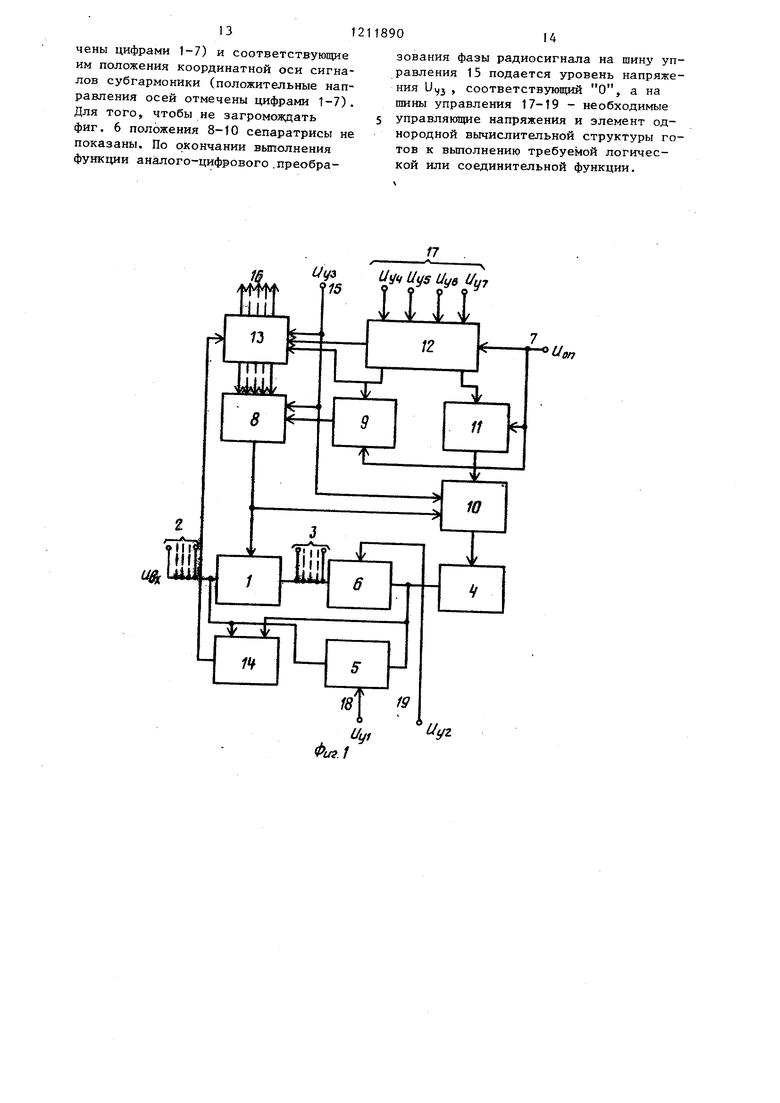

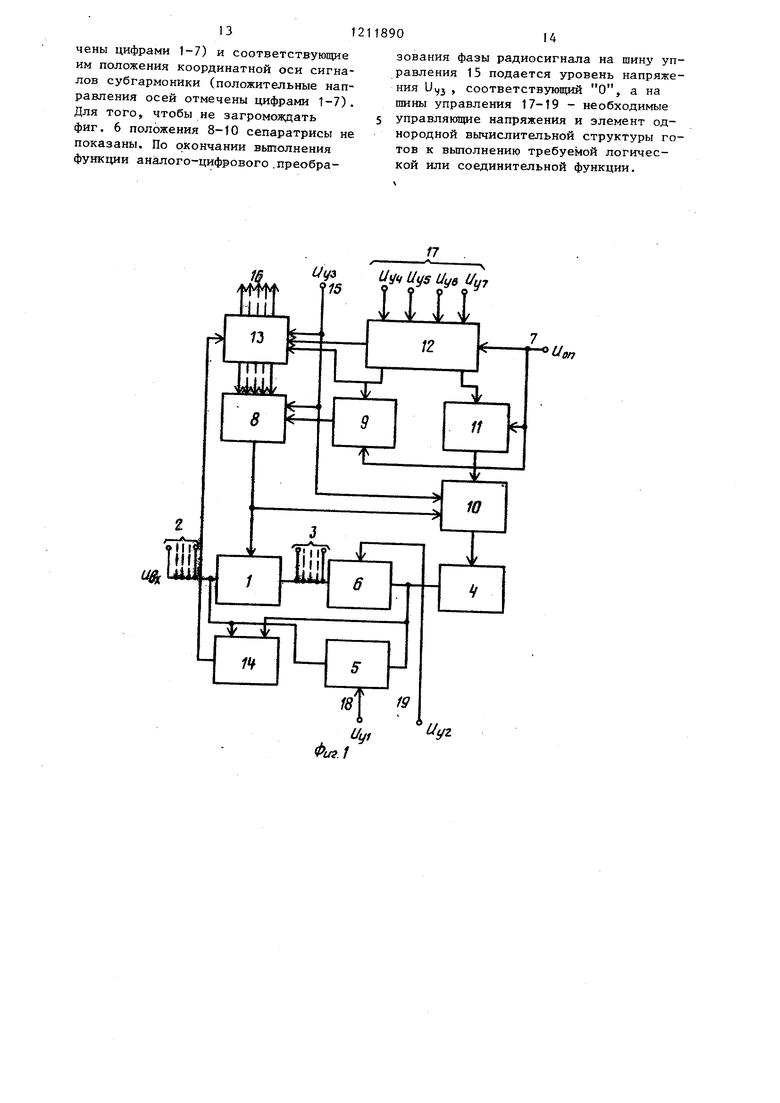

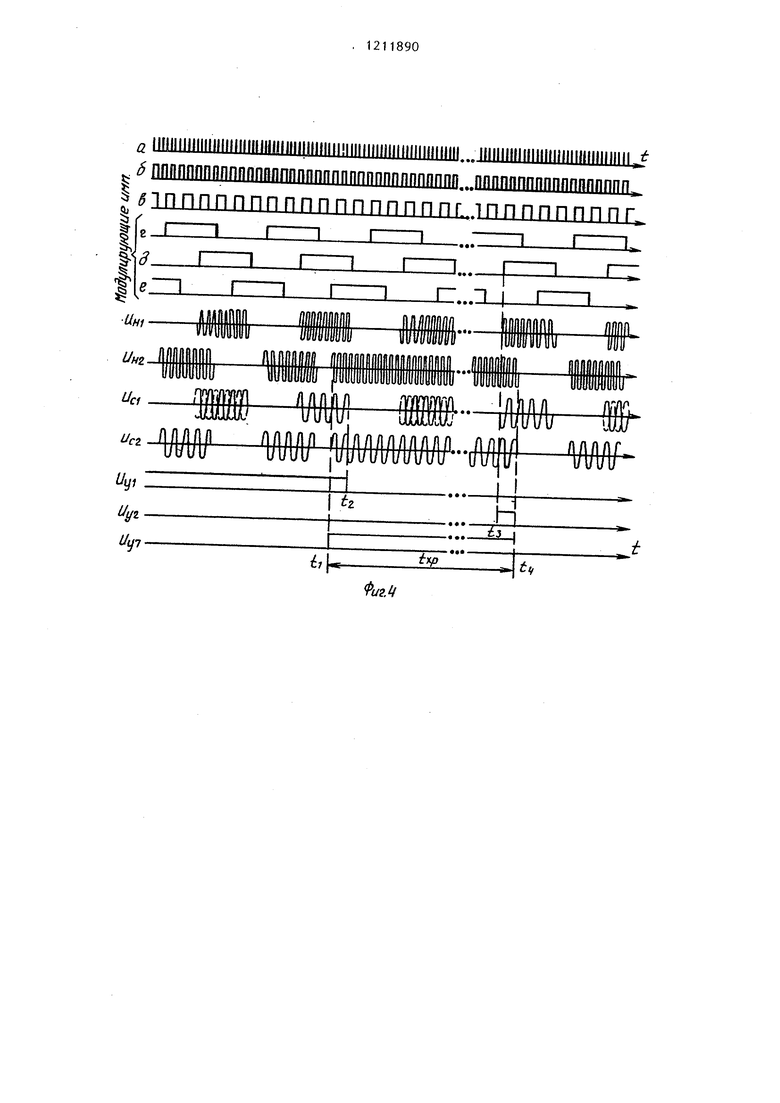

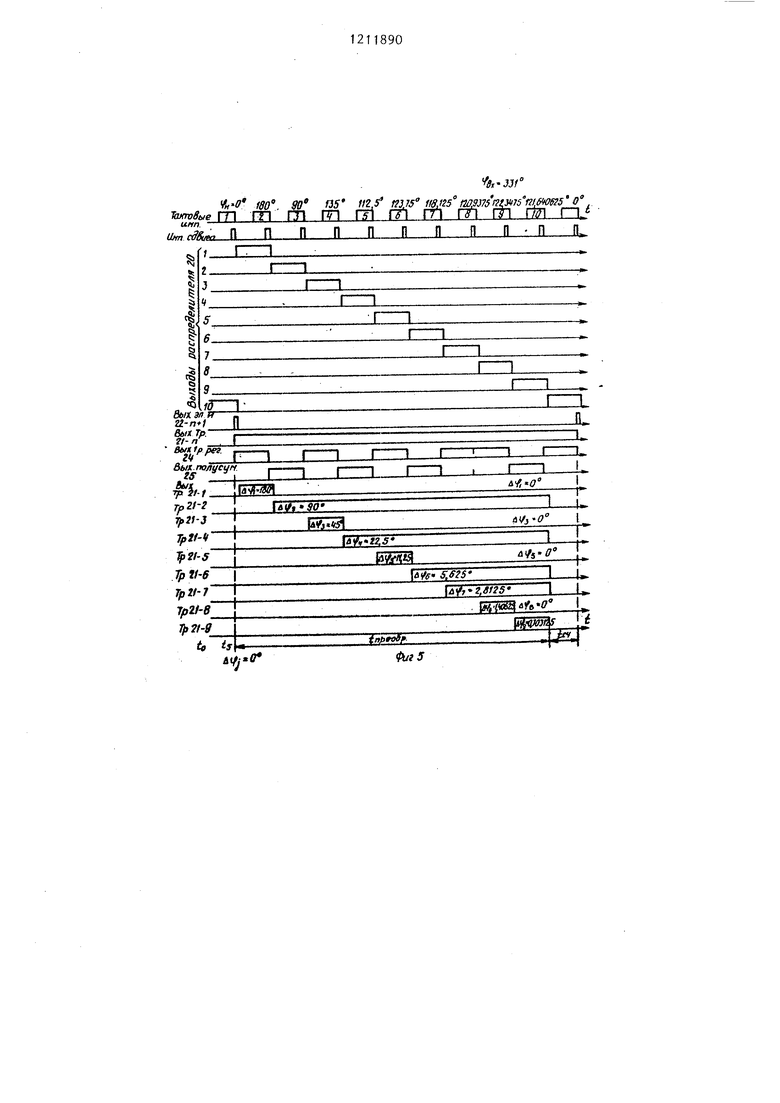

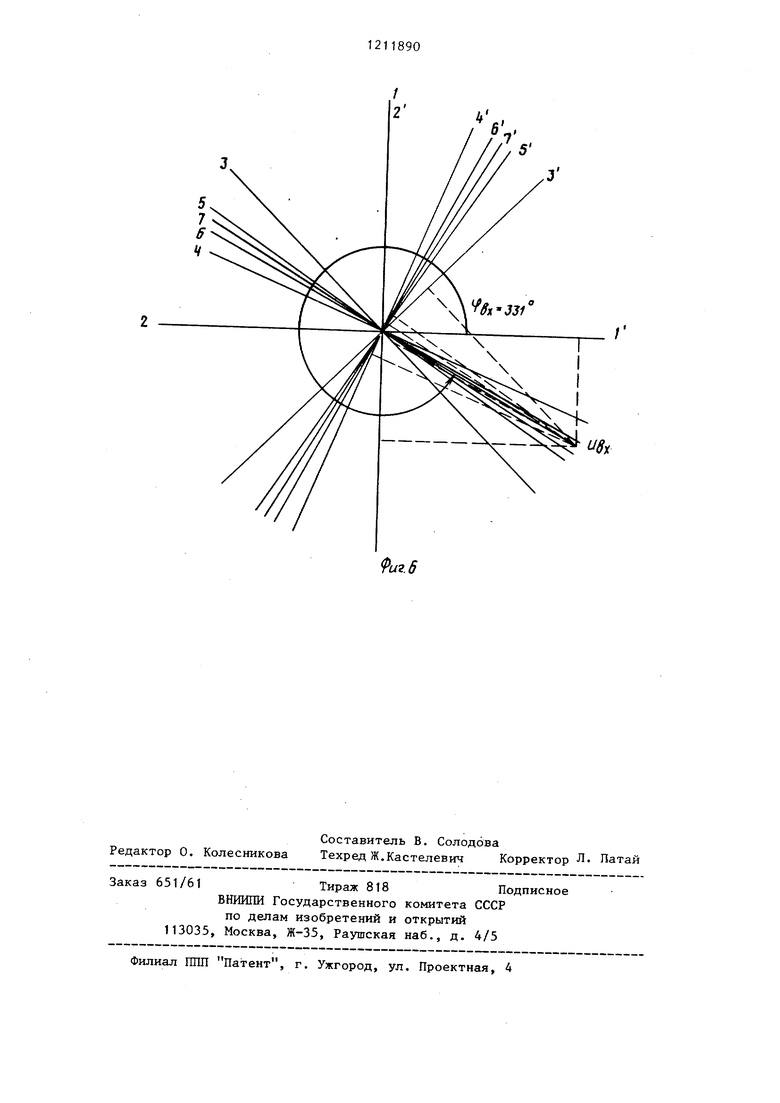

На фиг. 1 представлена блок-схема элемента однородной вычислительной структуры; на фиг. 2 - блок-схема управляемого фазовращателя и блока управления фазовращателем; на фиг. 3 - пример выполнения блока выбора такта накачки; на фиг. 4 - временные диаграммы при выполнении элементом однородной вычислительной структуры логических функций и функции памяти, где Ущ и UH -напряж ния накачки, а и Uc2 напряжения субгармоники функционального и опорного параметрических генераторов (при работе их во втором и первом тактах соответственно, фаза О - сплошная линия, фаза 180 - пунктир, временной масштаб заполнения радиоимпульсов для наглядности увеличим), UY , Uy2 , Uy7 - -управляющие напряжения, а-е - временные диаграм- |мы напряжений в соответствующих точ- ках схемы блока выбора такта накачки; на фиг. 5 - временные диаграммы при выполнении элементом однородной вычислительной структуры функции аналого-цифрового преобразования фазы радиосигнала; на фиг. 6 - фазовая плоскость измерительного параметрического генератора.

Элемент однородной вычислительной структуры (см.фиг. 1) содержит функциональный параметрический генератор (ФПГ) 1, прямой 2 и инверсный входы (выходы) которого соединены с прямым входом (выходом) опорного параметрического генератора (ОПГ) 4 через управляемые аттенюаторы связи 5 и 6. Параметрический генератор является двухполюсником и поэтому его вды и выходы неразличимы. Вход накачки ФПГ 1 подключен через последовательно соединенные управляемый фазовращатель 8 и модулятор (амплитудный, импульсньй) 9 к шине 7 опорно7

0

5

го напряжения частоты накачки. Вход накачки ОПГ 4 подключен через последовательно соединенные; переключатель 10 и модулятор (амплитудньш, импульсный) 11 к шине 7 опорного напряжения частоты накачки, к которой подключен первый вход блока 12 выбора такта накачки. Первьй -информационный вход переключателя 10 соединен с выходом управляемого фазовращателя 8. Первый вход блока 13 управления фазовращателем подключен через

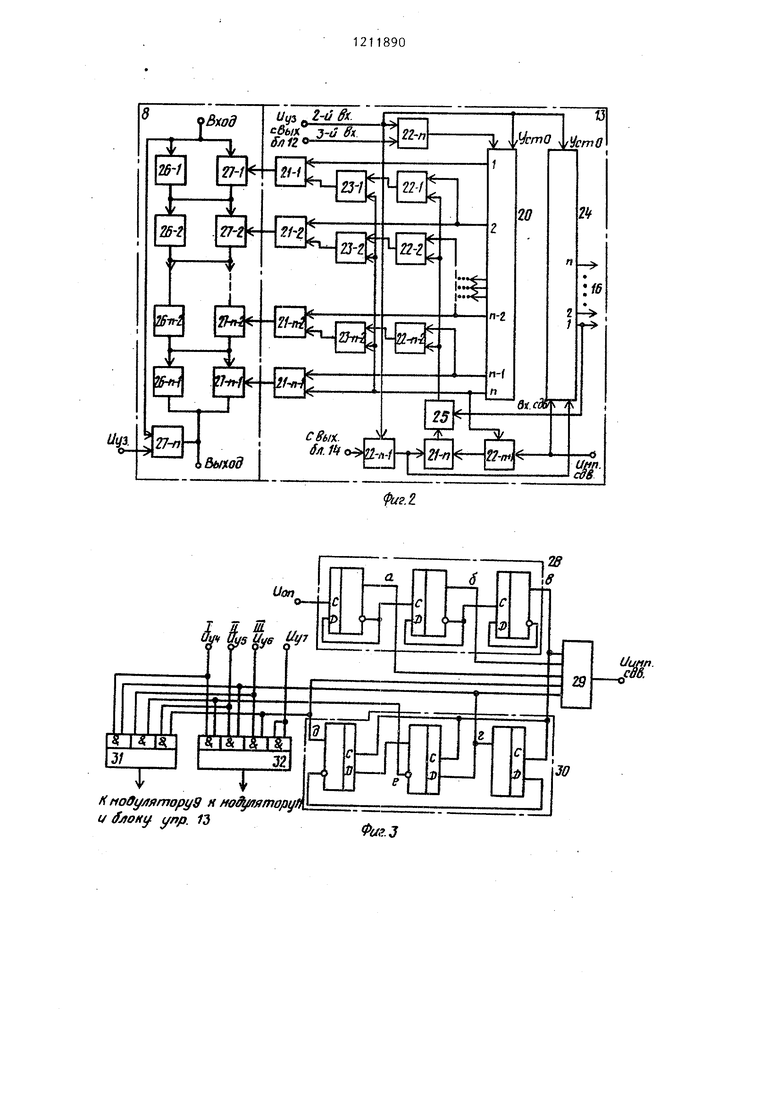

фазовый детектор 14 к прямым входам ФПГ 1 и ОПГ 4. Второй вход блока 13 5 управления фазовращателем обьединен с вторым входом управляемого фазовращателя 8 и управляющим входом переключателя 10 и подключен к шине управления 15 устройства. Третий вход блока 13 управления фазовращателем объединен с вторым входом модулятора 9 и подключен к первому выходу блока 12 выбора такта накачки, второй выход которого соединен с вторым входом модулятора 11, а третий - с четвертым входом блока 13 управления фазовращателем. Первая группа выходов блока 13 управления фазовращателем является выходными разрядными шинами 16 устройства. Второй - пятый входы блока 12 выбора такта накачки и управляющие входы управляемых аттенюаторов связи 5 и 6 подключены к соответствующим шинам управления 17 - 19 устройства. Блок 13 управления фазовращателем (см. фиг. 2) содержит распределитель 20 импульсов, триггеры 21-1 - 21-и-1 (например, R- S -триггеры), D - триггеры 21-h , двухвходовые элементы И 22-1 - 22-h + 1,, двухвходовые элементы ИШ 23-1 - 23-h-2, h -разрядньй сдвигающий регистр 24 и полусумматор 25. Первьй выход распределителя импульсов 20 подключен к первому входу триггера 21-1 непосредственно, а второй выход - непосредственно к первому входу триггера 21-2 и через последовательно соединенные элементы И 22-1 и ИЛИ 23-1 к второму входу триггера 21-1. Аналогично второму подключен 3,4,..., (и-1)-й выходы распределителя импульсов 20, т.е. каяодьй i-и выход распределителя 20 подключен к первому входу триггера 21-1 непосредственно и через последовательно соединенные элементы И 22- l -1 и ИЛИ 23- i -1 к его второму входу, h -и вы0

5

0

5

0

5

3

ход распределителя 20 импульсов соединен С вторым входом триггера 21- И -1 и с объединенными вторыми входами всех элементов ИЛИ. Выход первого разряда И -разрядного сдвигающего регистра 24 подключен к первому входу полусумматора 25, выход которого соединен с вторыми входами элементов И 22-1 - 22-Н-2, Первьш вход блока 13 управления фазовращателем подключен через элемент И 22- И -1 к информационному входу регистра 24 и D-входу триггера 21-h , выход которого соединен с вторым входом полусумматора 25. Второй вход блока 13 управления подключен к объединенным второму входу элемента И 22- И -1, входам установ ки нуля распределителя импульсов 20 и h -разрядного сдвигающего регистра 24 и первому входу элемента И 22второй вход которого является третьим входом блока 13 управления, а выход - со счетным входом распределителя 20. Выход элемента И 22- h +1 соединен с входом синхронизации три гера 21-h , первый вход - с h -м )зы- ходом распределителя импульсов 20, а второй вход объединен с входом сдвига регистра 24 и является четветым входом блока 13 управления фазовращателем. Разрядные выходы и -разрядного регистра 24 являются первой группой выходов блока 13 управления фазовращателем и соответственно выходными разрядными шинами всего уст ройства, а его второй группой выходов являются вькоды триггеров 21-1 21-и -1.

Управляемый фазовращатель 8 (см. фиг. 2) содержит цепочку последовательно соединенных фазовращателей 26-1 - 26-h-1, параллельно каждому из которых подключены ключи 27-1 - 27- h -1 соответственно. Вх ды управления ключей 27-1 - 27-h-1 являются первыми входами управляемого фазовращателя 8 и подключены к вьгходам триггеров 21-1 - 21 -h-1 соответственно. Между входом фазовращателя 26-1 и выходом фазовращателя 26-h -1 включен ключ 27- с инвертором в цепи управления. Вход управления ключа 27- h является вторым входом управляемого фазовращтеля 8. Вход фазовращателя и выход фазовращателя 26-И -1 являютс соответственно третьим входом и выходом управляемого фазовращателя 8,

Фазовый сдвиг, создаваемый каждым j -м фазовращателем, выбран равным

360° U .

, где J 1 - И -1 - но о

мер фазовращателя, а v -количество разрядов выходного кода элемента однородной вычислительной структуры.

Блок 12 выбора такта накачки (см. фиг, 3) содержит делитель 28

частоты, пятивходовой элемент И 29, сдвигающий регистр 30, элемент 2И - ЗИЛИ 31 и элемент.2И-4ИЛИ 32. Вход делителя 28 частоты является первым входом блока 12 выбора такта накачки, вторым - пятым входами которого являются попарно объединенные вторые входы соответствующих групп входов элементов 2И - ЗИЛИ 31 и 2И-4ИЛИ 32. Первый - третий выходы делителя 28

частоты соединены соответственно с первым - третьим входами пятивходового элемента И29.К четвертому и пятому входам которого подключены соответственно первый и третий выходы сдвигающего регистра 30, Попарно объединенные первые зходы соответствующих групп входов элементов 2И - ЗР1ЛИ 31 и 2И - 4 ИЛИ 32 подключены к выходам сдвигающего регистра 30. Выходы элементов 2И ЗШШ 31, 2И - 4ИЛК 32 и пятивходового элемента И 29 являются соответст- )зенно первым - третьим выходами бло- 1са 12 выбора такта накачки.

Функционалыгвш и опорньй параметрические генераторы, например емкостные, выполнены по балансной схеме. ФПГ-1 тщательно отсимметрирован и фаза его субгармонических колебаний при-возбуждении радиоимпульсом накачки однозначно определяется фазой входного сигнала. В балансную схему ОПГ 4 введена конструктивная асимметрия (например, за счет неравенства емкостей варикапов) и, таким образом, он всегда при отсутствии входного сигнала от ФПГ-1 возб ткда- ется с одной и той же фазой субгармонических колебаний,жестко связанной с фазой воз блуждающего радиоимпульса накачки.. При подаче же входного сигнала от ФПГ-1 через управляемые аттенюаторы 5 и 6 фаза субгармонических колебаний ОПГ 4 при его возбуждении определяется фазой этого входного сигнала субгармоники.

Управляемые аттенюаторы связи 5 к п дол:1кны обеспечивать затухание не менее IQO дБ (по напряжению) при

подаче на шины управления 18 и 19 уровней управляющих напряжений Uy;, и IUy2, соответствующих О, и порядка 60 дБ при подаче уровней управляющих напряжений Uy и (Уу соответствующих 1. Они могут быть выполнены, например, в виде последовательно включенных неуправляемого аттенюатора с затуханием 60 д Б и управляемого аттенюатора с переменным затуханием 0-40 дБ.

В рабочем состоянии на элемент однородной вычислительной структуры поданы непрерывное опорное напряжение частоты накачки Uon , а также управляющие напряжения Uy-| и

V7

(СМ. фиг. 1 - 4).

При подаче на шины управления 17 уровней напряжения Ууц - Uy , соо ветствующих О, на вторые входы модуляторов 9 и 1.1 поступают запирающие уровни напряжения, на выходах модуляторов 9 и 11, а следовательно и на входах накач ки ФПГ-1 и ОПГ-4 отсутствуют радиоимпульсные напряжения накачки, Ф11Г-1 и ОПГ-4 не возбуждаются и элемент однородной вычислительной структуры вьшолняет функцию разрыва цепи в канале перед чи сигналов в структуре.

При подаче на шины управления 15-29 уровней напряжений Uy , Uyj , Uyj , Uy , соответствующих О, и одного из уровней напряжений Uy, , , соответствующего 1, а двух

других, соответствующих О, затухание управляемых аттенюаторов 5 и 6

становится большим и ОПГ-4 отключает- (ся от ФПГ-1. Непрерывное напряжение частоты накачки UQ шины 7 поступает на входы модуляторов 9 и 11, на вторые входы которых подаются импульсы соответствующего такта, вьфабатывае- мые в блоке 12 выбора такта накачки. Ключ 27-h включается, радиоимпульсы напряжения накачки соответствующего такта с одинаковой начальной фазой заполнения UHI с выхода модулятора 9 через управляемый фазовращатель 8 (с нулевым фазовым сдвигом) подаются на вход накачки ФПГ-1 и элемент однородной вычислительной структуры выполняет:

функцию соединения в цепи переда- чи сигналов в однородной вычислительной структуре, когда на один из прямых входов (выходов) 2 поступает

Q

о 5 о

„

5

сигнал, а выходной сигнал снимается с другого прямого выхода;

логическую операцию НЕ, когда на один из входов 2 поступает сигнал, а выходной сигнал снимается с одного из инверсных вьрсодов 3 или, когда входной сигнал поступает на инверсный вход ФПГ-1, а снимается с прямого;

мажоритарную функцию, когда на его входы,(выходы) 2 поступает нечетное количество сигналов, а выходной сигнал снимается с одного из прямых выходов;

мажоритарную функцию с инверсией, если на входы 2 поступает нечетной количество сигналов, а выходной сигнал снимается с одного из инверсных выходов 3.

Радиоимпульсное напряжение поступает также на вход накачки ОПГ-4, через переключатель 10, но ОПГ-4 отключен от ФПГ-1 и на работу последнего не влияет. I

Для выполнения элементом однородной вычислительной структуры логических функций. И, ИЛИ, И-НЕ, ИЛИ-НЕ на шины управления 15 и 17 подаются уровни напряжений Uyj и Uy. , соответствующие о, один из уровней напряжений Uyi, - Uyg , соответствующий 1, а два других, соответствующих О. Блок 12 выбора такта накачки (см. фиг. 3 и 4) формирует на выходах тактовые импульсы первого - третьего тактов, сдвинутые по отношению друг к другу на треть периода тактовой частоты. Причем импульсы, подаваемые на второй вход модулятора 11, всегда опережают во времени импульсы, подаваемые на второй вход модулятора 9. Радиоимпульсы накачки с выходов модуляторов 9 и 11 поступают через управляемый фазовращатель 8 (ключ 27- |л замкнут) и переключатель 10, который при уровне напряжения Uyj , соответствующем О, подключает выход модулятора 11 к входу накачки ОПГ-4, на входы накач- {си ФПГ-1 и ОПГ-4 соответственно. При этом ОПГ-4 всегда розбуждается в такте, предшествующем такту возбуждения ФПГ-1. Например, при уровне напряжения Uyj , соответствующем 1, и уровнях напряжений U-yi, и Uyg , соответствующих О, ФПГ-1 работает во втором такте ц и Uc, , а

7 1211890

ОПГ-4 - первом такте UH э Jc2 ОПГ-4 с приходом каждого радио:импуль- са накачки UHT. возбуждается всегда в одной и той -же фазе.

При подаче уровня напряжения Uy{ , соответствующего 1, на шину управления 18 и уровня напряжения Jvi ,

соответствующего О, на шину управления 19 затухание управляемого аттенюатора 5 становится малым, а управляемого аттенюатора 6 - больпим. Радиоимпульсы субгармоники с прямого выхода ОПГ-4 через управляемьй аттенюатор 5 с малым затуханием поступают на прямой вход ФПГ-1 и в этом случае элемент однородной вычислительной структуры выполняет:

логическую функцию ИЛИ от двух переменных, если входные сигналы поступают на два каких-либо прямьк входа 2, а выходной сигнал снимается с одного из прямых выходов; . функцию ИЛИ-НЕ, когда сигналы (входные) поступают на два каких-либо прямых входа 2, а выходной сигнал снимается с одного из инверсньпс выходов 3.

При подаче уровня напряжения Uy , соответствующего О, на пшну управления 18 и уровня напряжения iJvi, соответствующего 1, на шину управления 19 затухание управляемого аттенюатора 5 становится большим, а управляемого аттенюатора 6 - малым. Радиоимпульсы субгармоники с прямого ьыхода ОПГ-4 через управляемьш аттенюатор связи 6 с малым затуханием поступают на инверсный вход ФПГ-1 и в этом случае элемент однородной вычислительной структуры выполняет:

логическую функцию И от двух переменных, если два входных сигна- (ла поступают на прямые входы (выходы) 2, а выходной сигнал снимается с одного из прямых выходов;

функцию И-НЕ, если два входных сигнала поступают на прямые входы 2, а выходной сигнал снимается с одного из инверсных выходов 3.

Элемент однородной вычислительной структуры выполняет функцию памяти 1 бит (хранение информации осуществляется в ОПГ-4), которая может быть совмещена во времени с выполнением логических функций: НЕ, мажоритарной, мажоритарной с инверсией, соединения и разрьша в цепи передачи сигналов в однородной вычислительной структуре. Если, например, в исрсодном состоянии на шины управления 15, 17-19 бьши поданы уровни

и

напряжения (уг , , v , Uye

и.

Uv

Uv

и

V7 ,

соответствующие О, и Uy и , соответствующие 1, т.е. элемент однородной вычислительной структуры работал во втором такте (ОПГ-1 работал во втором такте, а ОПГ-4 - в первом) и выполнял логическую операцию

)0 И.ЯИ (ИЛИ-НЕ) , то для записи информации на тины управления 17 в момент времени t (см, фиг. 4) подаются уровни напряжений Uy, соответствующий О, и Uy: соответствующий 1.

(5 Напряжение субгармоники с прямого выхода ФПГ поступает на прямой вход ОПГ-4, которьй при подаче на него радиоимпульса накачки UHI (в момент t ) возбуждается с фазой субгармо2Q НИКИ, определяемой фазой субгармоники ФПГ-1. В момент времени t на шину управления 18 подается уровень напряжения (Jy , соответствующий О, и ФПГ-1 отключается от ОПГ-4. Время

25 хранения информации txp равно длительности радиоимпульса накачки на входе накачки ОПГ-4 и определяется длительностью импульса напряжения Uy-f , соответствующего 1, подаваемого

,.. на соответствующую шину управления 17 в течение времени 1ц- t .

При необходимости считьш ания информации, например, в инверсном коде в момент времени tj и до 1ц на шину управления 19 подается уровень напряжения Uy2 , соответствующий 1, напряжение субгармоники с прямого выхода 011Г-4 через шравляемьш аттенюатор 6 поступает на инверсный вход ФПГ-1. Этот параметрический генера , тор при поступлении очередного радиоимпульса накачки выбранного такта (например, второго такта, см. фиг, 4) возбуждается с фазой субгармоники, противоположной фазе субгармоники

ОПГ-4. В момент времени ti, на одну

из шин управления 17 подается уровень, напряжения U , соответствующий О, и фаза колеба11ий субгармоники в ОПГ-4 с приходом очередного радиоимпульса

50 накачки вновь будет определяться его заполнения, и элемент однородной вычислительной структуры подготовлен к выполнению последующей логической функции.

55 Для вьшолнения элементом однородной вычислительной структуры функции аналого-цифрового преобразования фазы радиосигнала на шину управления

рсодном состоянии на шины управления 15, 17-19 бьши поданы уровни

и

напряжения (уг , , v , Uye

и.

Uv

Uv

и

V7

соответствующие О, и Uy и , соответствующие 1, т.е. элемент одjyi, , соответствующий i , U - Uy7 , соответствующие 0, и на входы накачки ФПГ-1 и ОПГ-4 поступает первый радиоимпульс накачки первого такта с исходной начальной фазой, которая условно может быть принята за нулевую, соответствующей всем закороченным фазовращателям 26-1 - 26 - п -1. Из теории параметрических генераторов известно, что фазовая плоскость параметрического генератора делится сепаратрисой на две области протяжения, соответствующие двум

значениям фаз н

+ 180

2 2 стационарных колебаний субгармоники ( ц - фаза напряжения накачки). Конструкция и режим работы ОПГ-4 выбраны так, что он всегда возбуждается с одной и той же фазой субгармоники.

15

91211890

15 предварительно (например,в момент времени t , фиг. 5) подается уро-- вень напряжения , соответствуюий О. Распределитель импульсов 20 и сдвигающий регистр 24 устанавли- вамтся в нулевое состояние, триггеры 21-1 - 21- Ж -1 - в исходное (единичное), ключи 27-1 - открываются и закорачивают фазовращатели 26-1 - 26- h -1, а ключ 27-h- управ- tO ляемый .фазовращатель 8, импульсы с выхода фазового детектора 14 на информационный вход регистра 24 и вход В триггера 21-h через элемент И.22-п -1 не поступают, тактовые импульсы не подаются на счетньй ход распределителя импульсов 20 чеез элемент И 22- h . На шины управения 18 и 19 подаются уровни напряений Uy и , соответствующие О, атухание управляемых аттенюаторов тановится большим и ФПГ-1 отключается от ОПГ-4. После подачи на шину управления -- 15 (например, в момент времени t5 ) уровня напряжения Uy- , соответствующего 1, ключ 27- н вылючается, счетньй вход распределителя импульсов 20 подключается через элемент И 22- И к выходу блока 12 выбора такта накачки, информационный вход регистра 24 и вход В триггера 21-и подключается через элемент И 22 - И -1 к выходу фазового етектора 14, а вход накачки ОПГ-4 отключается от выхода модулятора 11 и подключается переключателем 10 к выходу управляемого фазовращателя 8. В момент времени tj на шины управления 17 подаются уровни напряжений

Uvi. . соответствующий 1

20

25

30

35

40

же рад ки го ФП дв ег пр же се ци орд ки су

т. от но

-7::

ни ФП зо ви од пр во ла и ки пл пр ни ки вр се ту им то во щи со

пу зы

5 вх де ко ст ФП

50

ни с сы го

55 ге ег си да

90

10

жестко связанной с фазой заполнения радиоимпульса на своем входе накачки. Положение вектора преобразуемого сигнала U, на фазовой плоскости ФПГ-1 однозначно определяет одну из двух возможных фаз субгармоники на его выходе. Считается, есл и вектор преобразуемого сигнала Ug расположен на фазовой плоскости справа от сепаратрисы, т.е. имеется его проекция на положительное направление координатной оси сигналов субгармоники, то ФПГ-1 возбуждается с фазой- субгармоники YH , а если слева,

2

т.е имеется проекция .вектора, U на отрицательное направление координатной оси, то с фазой субгармоники

Vэ

-7::- - + 180 . Относительное положение сепаратрисы на фазовой плоскости ФПГ-1 однозначно определяется фазой напряжения накачки. В соответствии с этим принцип работы элемента однородной вычислительной структуры при выполнении функции аналого-цифрового преобразования фазы радиосигнала с приходом на входы накачки ФПГ-1 и ОПГ-4 каждого радиоимпульса накачки заключается в определении полуплоскости, которой принадлежит вектор преобразуемого сигнала, и формирований управляющих сигналов для установки фазового сдвига управляемого ,фазовращателя 8 таким образом, чтобы сепаратриса ФПГ-1 (и ОПГ-4) при пос.- туплении каждого последующего радиоимпульса накачки делила пополам сектор фазовой плоскости, определенный во время действия данного и предыдущих /начиная с первого) радиоимпульсов накачки (см. фиг. 5 и 6).

При поступлении первого радиоимпульса накачки в зависимости от фазы M g преобразуемого сигнала U на

входе 2 ФПГ-1, на выходе фазового детектора 14 появляется сигнал, в котором уровень 1 или О соответствует, например, фазе субгармоники ФПГ-1 YH или Тн pfx Положе-г 2

ние 1 сепаратрисы на фиг. 6. Сигнал с выхода фазового детектора 14 записывается в первый разряд h-разрядного сдвигающего регистра 24 и в триггер 21-h , поскольку в это время на его входе синхронизации присутствует сигнал, соответствующий 1, с выхода элемента И 22- h +1. После окончания первого радиоимпульса, на триггер 21-1 поступает импульс с первого выхода распределителя импульсов 20 и изменяет его состояние. При этом ключ 27-1- выключается и в цепи связи между модулятором 9 и входами накачки параметрических генераторов включается фазовращатель 26-1 дающий фазовый сдвиг 180 , При налкгчии на входах накачки ФПГ-1 и ОПГ-4 второго радиоимпульса, фаза заполнения которого сдвинута на 180°, (положение 2 сепаратрисы) фазовьш детектор 14 осуществляет сравнение фаз их колебаний субгармоники и его выходной сигнал опять записывается в первый разряд h -разрядного сдвигающего регистра 24, а предьщущее состояние,певого разряда переписывается во второ разряд; Изменение состояния триггера 21- h в зто время не происходит, так как на его вход синхронизации подается сигнал, соответствующий Сос- тояния первого и второго разрядов регистра 24 дают возможность определит положение вектора преобразуемого сигнала на фазовой плоскости с точностью до квадранта, 11олусу1 1матор 25 анализирует содержимое первого разряда регистра 24 и триггера 21-h и вырабатьшает сигнал управления для элементов И 22-1 - 22-И-2. После окончания второго,радиоимпульса, накачки происходит переключение триггера 21-1 сигналом, соответствующим 1, с второго выхода распределителя импульсов 20, выключение ключа 27-2 и включение в цепь связи между модулятором 9 и входами накачки параметрических генераторов фазовращателя 26-2, дающего фазовый сдвиг 90°, Одновременно в соответствии с сигналом управления, поданным полусумматором 25 на элементы И 22-1 - 22 - 2, триггер 21-1 может переключиться при совпадении сигнахгов с полусумматора 25 и с второго выхода распределителя ш«1ульсов 20 или остается в предыдущем состоянии в случае их несовпадения. Третий радиоимпульс будет иметь фазу заполнения или 90

0

или 270 , причем фаза накачки определяется автоматически в результате анализа состояний ФПГ-1 в предыдущие два дискретных промежутка времени (времена действия первого и второго радиоимпульсов). Во время действия третьего радиоимпульса фаза преобразуемого сигнала будет определена с точностью до октанта фазовой плоскости (положение 3 сепаратрисы), которой будет соответствовать трехраз- рядный код, записанный в И -разрядный сдвигарощий регистр 24. Аналогично предьщущему автоматическое формирование в блоке 13 управления фазовращателем сигналов управления ос- тальными ключами фазовращателя 8 осуществляется таким образом, чтобы

сепаратриса ФПГ-1 с приходом следующего радиоимпульса на входы накачки параметрических генераторов делила сектор фазовой плоскости, определен5 ный в предыдущие дискретные промежутки времени, пополам. Цикл преобразования заканчивается после поступления на входы какачки ФПГ-1 и ОПГ-4 h го радиоимпульса и заполнения

0 всем разрядов h -разрядного сдвигающего регистра 24. При этом с vi -ого выхода распределителя импульсов 20 подается сигнал возвращения триггеров 21-1 - 21-Н -1 и соответственно

5 ключей 27-1 - 27- h -1 в исходное положение. После окончания цикла преобразования npsosv. выходной код может быть считан в течение вре- -мени1 ц с разрядных выходов 16 h 0 разрядного регистра 24 для дальнейшей обработки и элемент однородной вычислительной структуры готов к (Выполнению очередного цикла преобразования .

Для примера на фиг. 5 приведены

временные диаграммы .работы блоков элемента однородной вычислительной структуры, выполняющего функцию аналого-цифрового преобразователя фазы радиосигнала при количестве

разрядов 10 для случая . На фиг. 5 у пронумерованных тактовых И1у1пульсов указань соответствующие фазы заполнения V радиоимпульсов накачки, а на диаграммах выход- ных напряжений триггеров 21-1 - 21-9 указаны фазовые сдвиги uM j, создаваемые соответствующими фазовращателями 26-1 - 26-9.Для любого момента време- ;НИ фазовый сдвиг5 создаваемый управ- ляемьм фазовращателем 8, равен

10

L..

J-1

55 На фиг, 6 для этого же примера приведена фазовая плоскость ФПГ-1, на которой представлены последовательные положения сепаратрисы (отмечены цифрами 1-7) и соответствуюпще им положения координатной оси сигналов субгармоники (положительные направления осей отмечены цифрами 1-7). Для того, чтобы не загромождать фиг. 6 положения 8-10 сепаратрисы не показаны. По окончании выполнения функции аналого-цифрового.преобразования фазы радиосигнала на шину управления 15 подается уровень напряжения Uv,3 , соответствующий О, а на шины управления 17-19 - необходимые управляющие напряжения и элемент однородной вычислительной структуры готов к выполнению требуемой логической или соединительной функции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Элементы однородной вычислительной структуры | 1980 |

|

SU930677A1 |

| Устройство для измерения фазы радиосигнала | 1979 |

|

SU976505A1 |

| Преобразователь фаза-код | 1979 |

|

SU864542A1 |

| Элемент однородной вычислительнойСТРуКТуРы | 1979 |

|

SU813786A1 |

| Цифровой измеритель RLC-параметров | 1986 |

|

SU1337820A1 |

| ИМПУЛЬСНО-ФАЗОВАЯ РАДИОВЫСОТОМЕРНАЯ СИСТЕМА | 2013 |

|

RU2551448C1 |

| Устройство для динамической балансировки роторов лучом лазера | 1987 |

|

SU1434301A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

| Формирователь последовательностей радиоимпульсов | 1981 |

|

SU1030961A1 |

иуз иуч Uys Uye Uyj ф ф ф ф

1

Вмд

и из о 2-tj ffx.

свыи 3-й ffx SfilZ

г

4

Ф 4

тО

13 cmQ

L

2/

|...

/б

TB-n-i

I-1 1 . n

n-ft

Вылод

CfftlK.

дл. т ./

г

t-

ru

п-г

n-t

п

f5

flif.fafr/v

ж

г/-/;

3i

№

// ffjfOHi упр. 13

Фи..3

а

llfllllHillinillltlllltlHIIIIHIfinillll llllllllinilllllll{}|llill..JtllllltNllllllllinillllH

: ТПППППППППППППППППГЛППППППППГ

Sj

J.

1

1

1

L

JL

c:...x.jс

т so 35 m m m m

Urn гЗК. П П П П П

ri

§ /g I

л- rj I I

flft/X ЭЯ ЙГ

JjB.-

/- /7

.

L

йья nonyctjii.

fs, 33f° tJ3JS 118,П5° nO 375nt.W5 ntfftOS2S 0

Ш

хд

t

jn П

JL

J

| ЭЛЕМЕНТ ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙСТРУКТУРЫ | 1972 |

|

SU432679A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Элементы однородной вычислительной структуры | 1980 |

|

SU930677A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| . | |||

Авторы

Даты

1986-02-15—Публикация

1984-07-11—Подача