Изобретение относится к автомати ке и вычислительной технике и может быть использовано в цифровых системах связи для построения устройств цифровой фильтрации, сжатия изображений и выделения контуров, основан ных на алгоритме быстрого преобразо вания Хаара (ВПХ) . Известно устройство, вычисляющее коэффициенты преобразования Хаара l Недостатками известного устройст ва являются сложность и громоздкост Наиболее близким к изобретению является устройство для ортогональн го преобразования цифровых сигналов по Хаару, содержащее соединенные последовательно модули единичного преобразования по основанию два, каждый из которых содержит по два регистра сдвига, реализующих функции задержки, -и арифметический блок Для упорядочения вычисленных коэффи циентов и преобразования их в последовательный поток устройство содержит группу регистров, каждый из которых соединен с одним из модулей Работу всего устройства синхронизирует блок управления, состоящий из счетчика и матрицы постоянного запоминаюш.его устройства ПЗУ 2 . По структуре указанное устройство относится к поточным многопроцес сорным схемам выполнения быстрого ортогонального преобразования. Эта структура пригодна для построения систем с высоким быстродействием. За п 2 тактов входного дискрехного сигнала устройство, с характер ной задержкой для всех поточных схем, выдает п коэффициентов преобразования. Однако в данном устройстве каждый последующий арифметический блок за время преобразования няет вдвое меньше операций сложения вычитания, чем предыдущий. Так, пер вый арифметический блок вычисляет половину всех коэффициентов преобразования, при этом первый арифмети ческий блок работает только половину всего времени преобразования. , Каждый последующий арифметический блок занят вычислениями в два раза меньшее время, чем предыдущий, т.е. первый арифметический блок за то же самое время выполняет столько же вычислений, сколько и все остальные вместе. Кроме того, устройство содержит много арифметических блоков, которые также используются не в пол . ной мере. Недостатком известного устройства является его сложность. Цель изобретения - упрощение уст ройства. Поставленная цель достигается тем, что устройство для ортогонального преобразования цифровых сигналов по Хаару, содержащее арифметический блок, три группы блоков задержки, две группы блоков сдвига, состоящих из последовательно соединенных регистров сдвига, и блок синхронизации, первый выход которого подключен к синхронизирующим входам регистров сдвига в каждом блоке сдвига, содержит пять переключателей, первая, вторая и третья группы блоков задержки .состоят соответственно из п (2 - объем входной выборки) , П - 1 и- одного блока задержки, первая и вторая группы блоков сдвига состоят из h - 1 блоков сдвига каждая, причем 1-е ( 1, . . ., ц -1) блоки сдвига первой и второй групп состоят соответственно из и 211-1 + п - 1 последовательно соединенных регистров сдвига, первый информационный вход первого переключателя является информационным входом устройства, информационные входы первого переключателя с первого по и -и через соответствующие блоки задержки первой группы подключены к одноименным информационным входам второго переключателя, выходы первого и второго переключателей подключены ко входам арифметического блока, выходы суммы и разности которот го подключены к информационным вхо- дам третьего и четвертого переключателей соответственно, i -и выход третьего переключателя через соответствующий блок задержки второй группы подключен к (i + 1)-му информационному входу первого переключателя, и -и выход третьего переключателя подключен к первому йн- , формационному входу пятого переключателя, j -и выход (j 1, ..., и), четвертого переключателя подключен ко входу первого регистра сдвига в )-м блоке сдвига первой группы, регистров сдвига в i -м блоке сдвига первой группы подключены ко входам одноименных регистров сдвига в 1 -м блоке сдЁига второй группы, выход ( + n-i)-ro регистра в i-M блоке сдвига второй группы, кроме vi - 1) -го блока сдвига второй группы, подключен ко входу первого регистра сдвига в (l + 1)-м блоке сдвига второй группы, выход третьего регистра сдвига в (п -1) -м блоке сдвига второй группы подключен к информационному вноду блока третьей группы, выход которого подключен ко второму информационному входу пятого переключателя, выход пятого переключателя является выходом устройства, второй выход блока синхронизации подключен к синхронизирующим входам первого, второго, третьего и четвертого переключателей, третий выход блока синхронизации подключен к синхронизирующему входу пятого переключателя, выходы блока синхронизации с четвертого по- ( 3) -и подключены к управляющим входам занесения в региртры сдвига соответствующих блоков сдвига второй группы.

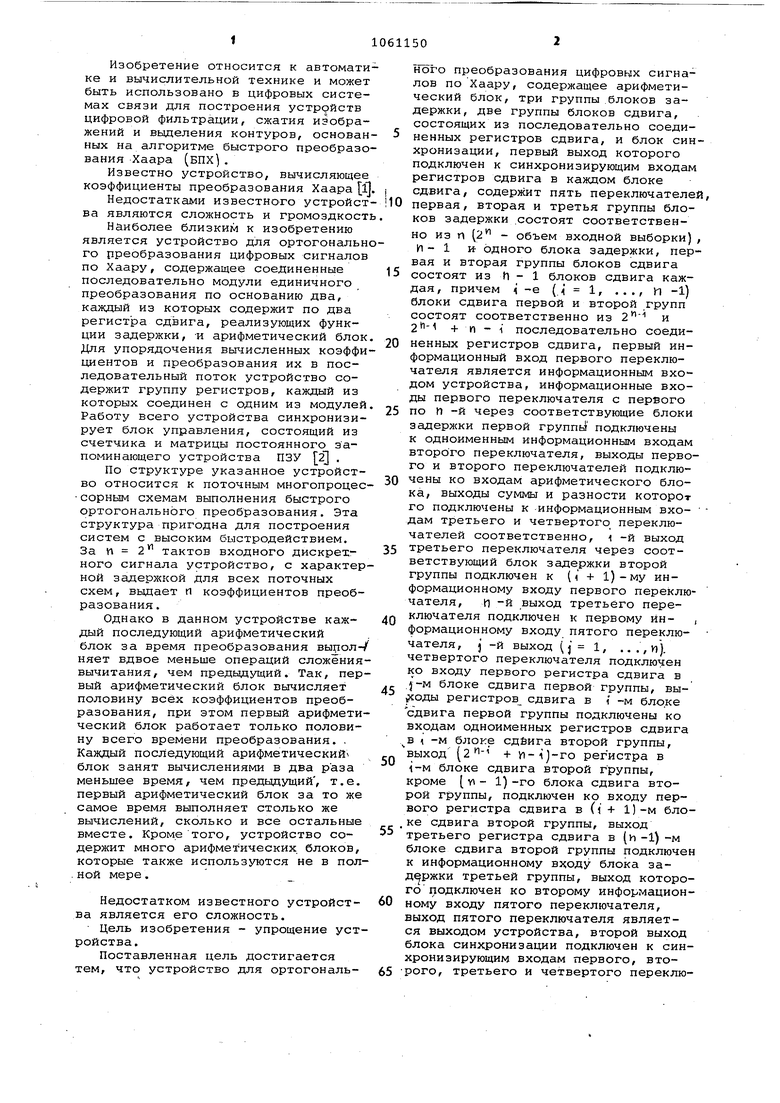

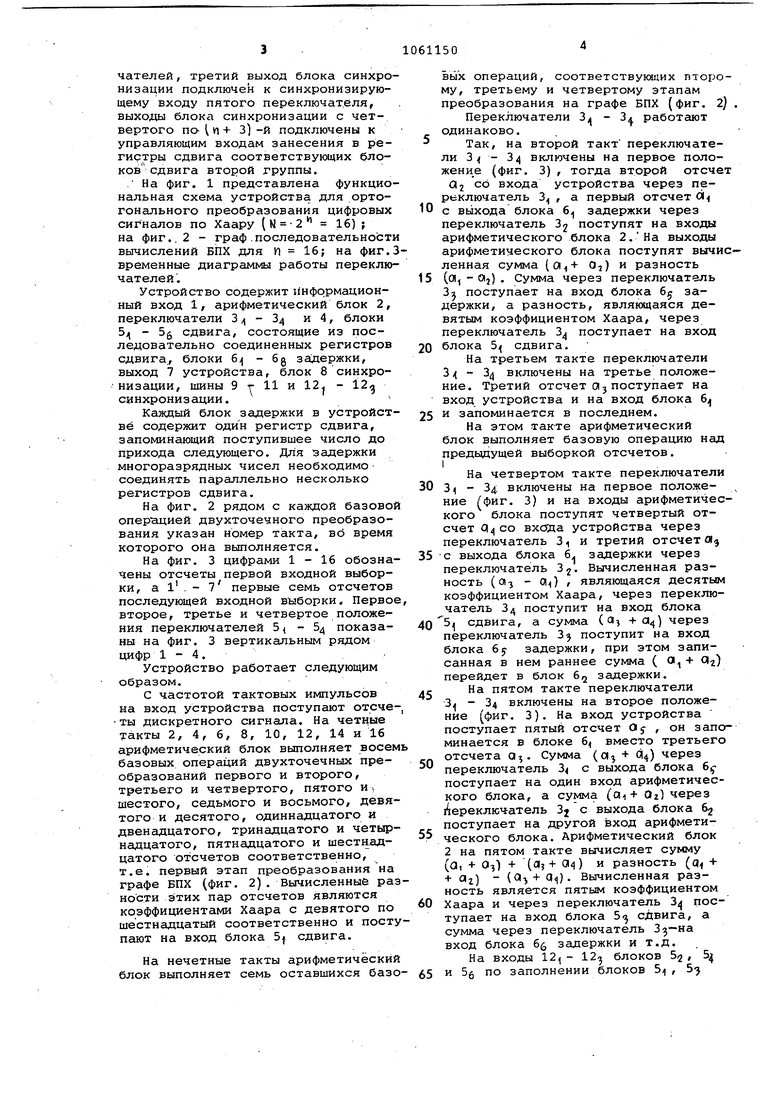

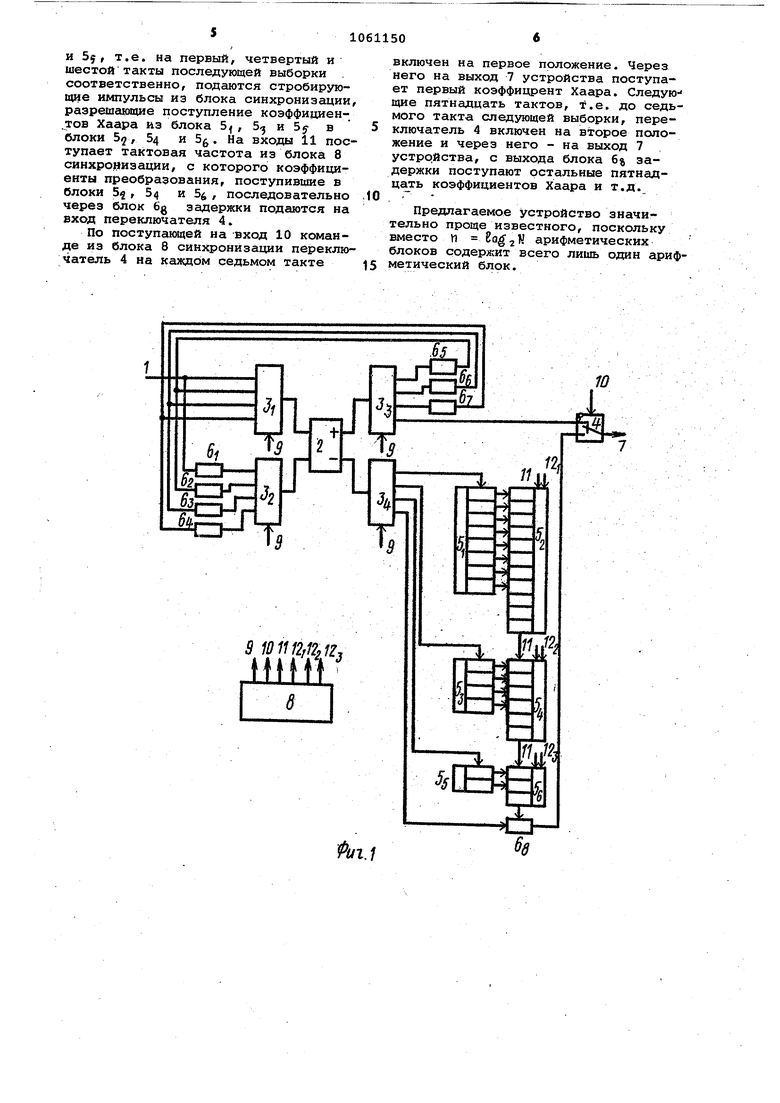

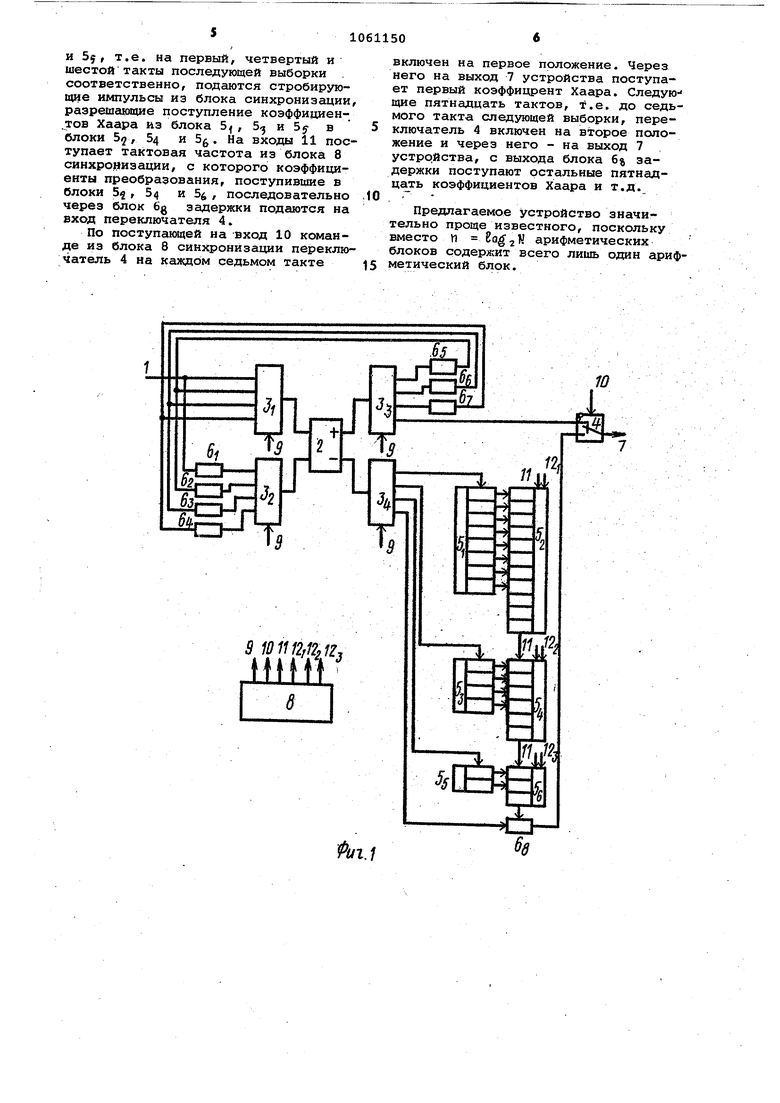

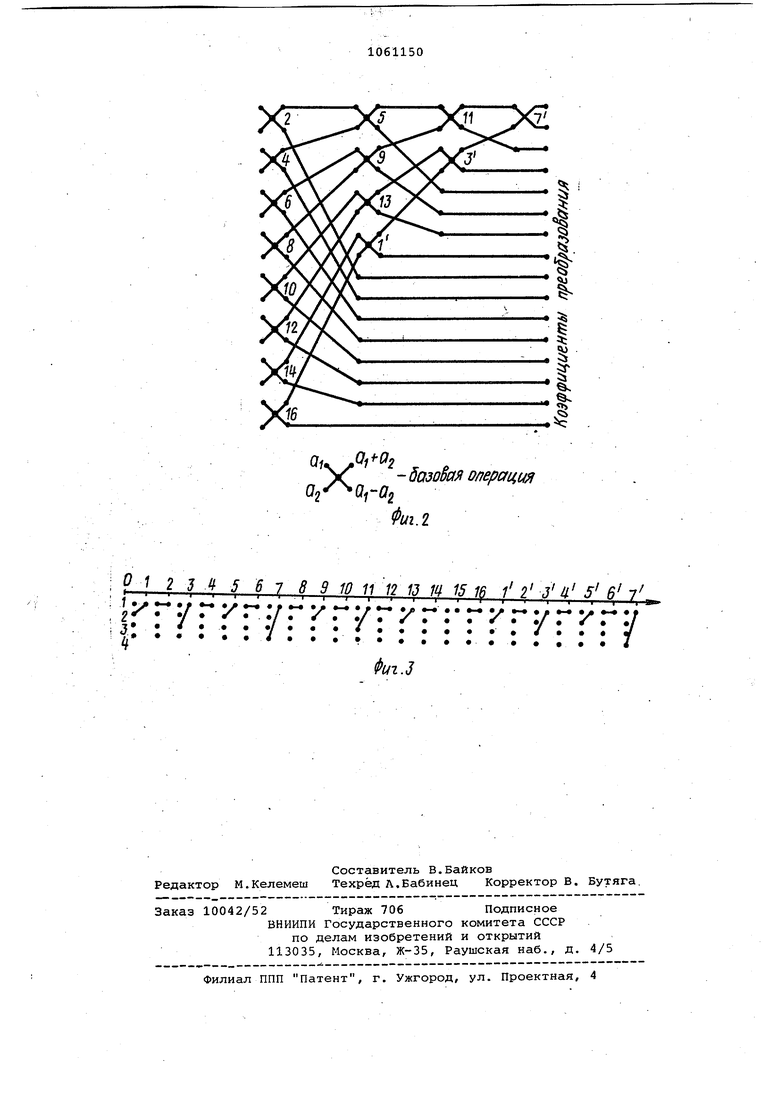

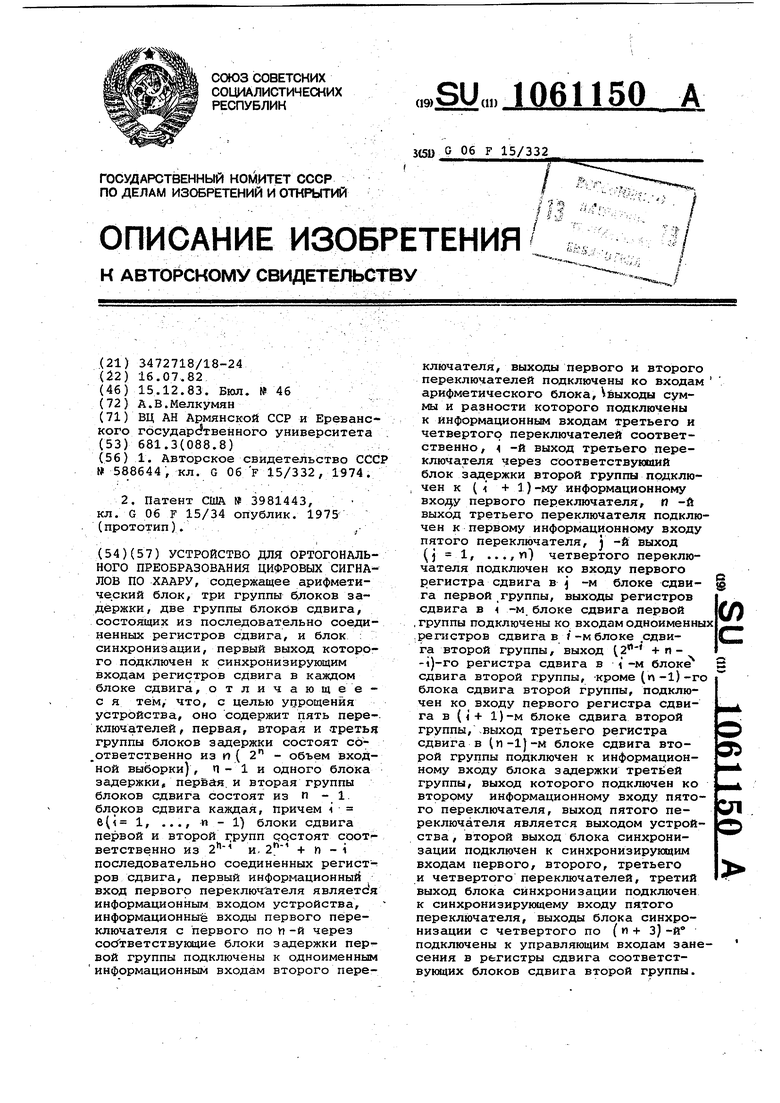

. На фиг. 1 представлена функциональная схема устройства для ортогонального преобразования цифровых сигналов по Хаару (N 16) ; на фиг.. 2 - граф.последовательности вычислений БПХ для п 16; на фиг.Звременные диаграммы работы переключателей.

Устройство содержит информационный вход 1, арифметический блок 2, переключатели Э - 3 и 4, блоки 5ц - Sg сдвига, состоящие из последовательно соединенных регистров сдвига, блоки 6/ - 6g задержки, выход 7 устройства, блок 8 синхро низации, шины 9 t- 11 и 12| - l2a синхронизации.

Каждый блок задержки в устройстве содержит один регистр сдвига, запоминающий поступившее число до прихода следующего. Для задержки многоразрядных чисел необходимо соединять параллельно несколько регистров сдвига.

На фиг. 2 рядом с каждой базовой операцией двухточечного преобразования указан номер такта, во время которого она выполняется.

На фиг. 3 цифрами 1-16 обозначены отсчеты первой входной выборки, а 1 . - первые семь отсчетов последующей входной выборки. Первое второе, третье и четвертое положения переключателей 5 - 5 показаны на фиг. 3 вертикальным рядом цифр 1 - 4.

Устройство работает следующим образом.

С частотой тактовых импульсов на вход устройства поступают отсчеты дискретного сигнала. На четные такты 2, 4, 6, 8, 10, 12, 14 и 16 арифметический блок выполняет восем базовых операций двухточечных преобразований первого и второго, третьего и четвертого, пятого и, шестого, седьмого и восьмого, девятого и десятого, одиннадцатого и двенадцатого, тринадцатого и четырнадцатого, пятнадцатого и шестнадцатого отсчетов соответственно, т.е. первый этап преобразования на графе БПХ (фиг. 2). Вычисленные разности этих пар отсчетов являются коэффициентами Хаара с девятого по шестнадцатый соответственно и поступают на вход блока 5| сдвига.

На нечетные такты арифметический блок выполняет семь оставшихся базовых операций, соответствукяцих второму, третьему и четвертому этапам преобразования на графе БПХ (фиг. 2} .

Переключатели 3j - 2л работают одинаково.

Так, На второй такт переключатели 3 - 3 включены на первое положени е (фиг. 3) , тогда второй отсчет

а2 со входа устройства через переключатель 3 , а первый отсчет 01

10 с выхода блока 6 задержки через переключатель 32 поступят на входы арифметического блока 2.На выходы арифметического блока поступят вычисленная сумма ( 0) и разность

5 (01, - Qj) . Сумма через переключатель 3 поступает на вход блока 6 задержки, а разность, являющаяся девятым коэффициентом Хаара, через переключатель 3 поступает на вход

0 блока 5 сдвига.

На третьем такте переключатели 3 /( - 3j включены на третье положение. Третий отсчет О} поступает на вход устройства и на вход блока 6

5 и запоминается в последнем.

На этом такте арифметический блок выполняет базовую операцию над

предьщущей выборкой отсчетов. I

На четвертом такте переключатели

0 3i - 3 включены на первое положе- . ние (фиг. 3) и на входы арифметического блока поступят четвертый отсчет Оц со входа устройства через переключатель 3 . и третий отсчет я

5 -с выхода блока 6. задержки через переключатель Вычисленная разность (Оз i являющаяся десятым коэффициентом Хаара, через переключатель 3 поступит на вход блока

0 сдвига, а сумма (0 + 3 через переключатель Зз поступит на вход блока 6у задержки, при этом записанная в нем раннее сумма ( О, + Q) перейдет в блок б, задержки.

На пятом такте переключатели

5 3 - 34 включены на второе положение (фиг. 3). На вход устройства поступает пятый отсчет Oj , он запоминается в блоке 6 вместо третьего отсчета а. Сумма (а + 014) через

переключатель 3 с выхода блока 6,,поступает на один вход арифметического блока, а сумма (ai+ Ог) через переключатель 3j с выхода блока 6 поступает на другой вход арифмети5 ческого блока. Арифметический блок 2 на пятом такте вычисляет сумму (а, + О) + ( 04) и разность (q + + Яг) - ( а). Вычисленная разность является пятым коэффициентом

0 Хаара и через переключатель 3 поступает на вход блока 5 сЛвига, а сумма через переключатель вход блока 6(3 задержки и т.д.

На входы 12, - 12 блоков Sj , 5

5 и 5 по заполнении блоков 5;| , S-j

И ЗУ, Т.е. на первый, четвертый и шестой такты последующей выборки . соответственно, подаются стробирующие импульсы из блока синхронизации разрешакадие поступление коэффициен.тов Хаара из блока 5, 5 и 5у в блоки 5, 54 и 5. На входы 11 поступает тактовая частота из блока 8 синхронизации, с которого коэффициенты преобразования, поступившие в блоки 5ч, 5 и 5б/ последовательно через блок 6g задержки подаются на вход переключателя 4.

По поступающей на вход 10 команде из блока 8 синхронизации переключатель 4 на каждом седьмом такте

включен на первое положение. Через него на выход 7 устройства поступает первый коэффицрент Хаара. Следую- щие пятнадцать тактов, т.е. до седьмого такта следующей выборки, переключатель 4 включен на второе положение и через него - на выход 7 устройства, с выхода блока б% задержки поступают остальные пятнадцать коэффициентов Хаара и т.д.

Предлагаемое устройство значительно проще известного, поскольку вместо и . арифметических блоков содержит всего лишь один арифметический блок.

ач (2

X - базовая операция i QrC

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ортогонального преобразования цифровых сигналов по функциям Хаара | 1983 |

|

SU1116435A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Хаару | 1988 |

|

SU1594561A1 |

| Устройство для выполнения обратного преобразования Хаара | 1983 |

|

SU1104528A1 |

| Процессор для преобразования цифровых сигналов по Хааро-подобным базисам | 1987 |

|

SU1418745A1 |

| Поточно-параллельный процессор Хаара | 1989 |

|

SU1756901A1 |

| Процессор для преобразования цифровых сигналов по Хааро-подобным базисам | 1984 |

|

SU1168966A1 |

| Параллельный процессор Хаара | 1989 |

|

SU1667103A1 |

| Устройство для реализации быстрого преобразования Хаара | 1983 |

|

SU1187176A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1987 |

|

SU1509930A1 |

УСТРОЙСТВО ДЛЯ ОРТОГОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ ПО ХААРУ, содержащее арифметический блок, три группы блоков задержки, две группы блоков сдвига, состоящих из последовательно соединенных регистров сдвига, и блок : синхронизации, первый выход которого подключен к синхронизирующим входам регистров сдвига в каждом блоке сдвига, отличающеес я тем, что, с целью упрощения устройства, оно содержит пять пере-, ключателей, первая, вторая и третья группы блоков задержки состоят со.ответственно из и{ 2 - объем входной выборки), П- 1 и одного блока задержки, первагя. и вторая группы блоков сдвига состоят из п - 1. блоков сдвига каждая, причем i e(i 1, ..., и - 1) блоки сдвига первой и второй групп достоят соот ветственно из и, + п - i последовательно соединенных регистров сдвига, первый информационный вход первого переключателя являетс я информационным входом устройства, информационные входы первого переключателя с первого по И-и через сойтветствукядие блоки задержки первой группы подключены к одноименным информационным входам второго переключателя, выходы первого и второго переключателей подключены ко входам арифметического блока,выходы суммы и разности которого подключены к информационным входам третьего и четвертого переключателей соответственно, -и выход третьего переключателя через соответствующий блок задержки второй группы прдклю, чен к ( + 1)-му информационному первого переключателя, п -ft выход третьего переключателя подключен к первому информационному входу пятого переключателя, j -и выход (J 1, ..., п) четвертого переключателя подключен ко входу первого регистра сдвига в j -м блоке сдви га первой группы, выходы регистров сдвига в 1 -м блоке сдвига первой , группы подключены ко входам одноименных .регистров сдвига в J -м блоке .сдвига второй группы, выход ( +п-i)-ro регистра сдвига в i -м блоке сдвига второй группы, кроме (п-1)-го блока сдвига второй группы, подключен ко входу первого регистра сдвига в (+ 1)-м блоке сдвига второй группы, -ВЫХОД третьего регистра сдвига в (n-lJ-M блоке сдвига второй группы подключен к информационному входу блока задержки третьей группы, выход которого подключен ко второму информационному входу пятосл го переключателя, выход пятого переключателя является выходом устройства , второй выход блока синхронизации подключен к синхронизируквдим входам первого, второго, третьего и четвертого переключателей, третий выход блока синхронизации подключен к синхронизирующему входу пятого переключателя, выходы блока синхронизации с четвертого по ( и + З) -и подключены к управляющим входам занесения в регистры сдвига соответствующих блоков сдвига второй группы.

2 3 Л 5 6 7 8 .J 10 iii2 i.l ia 1516 l 9 лli . fi -г

inTfrrfrrrrrrnfrrrrrri

Фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для приема информации, передаваемой путем инверсной модуляции псевдослучайной последовательности | 1976 |

|

SU588644A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3981443, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

Авторы

Даты

1983-12-15—Публикация

1982-07-16—Подача