Фиг.1

Из 1бретение относится к вычислительной технике и радиштехнике и мояскт быть использовано в системах цифровой обработки сигналов, основаных на алгоритме быстрого преобразо вания Хаара (БПХ).

Цель изобретения -упрощение уст- (ойст}за,

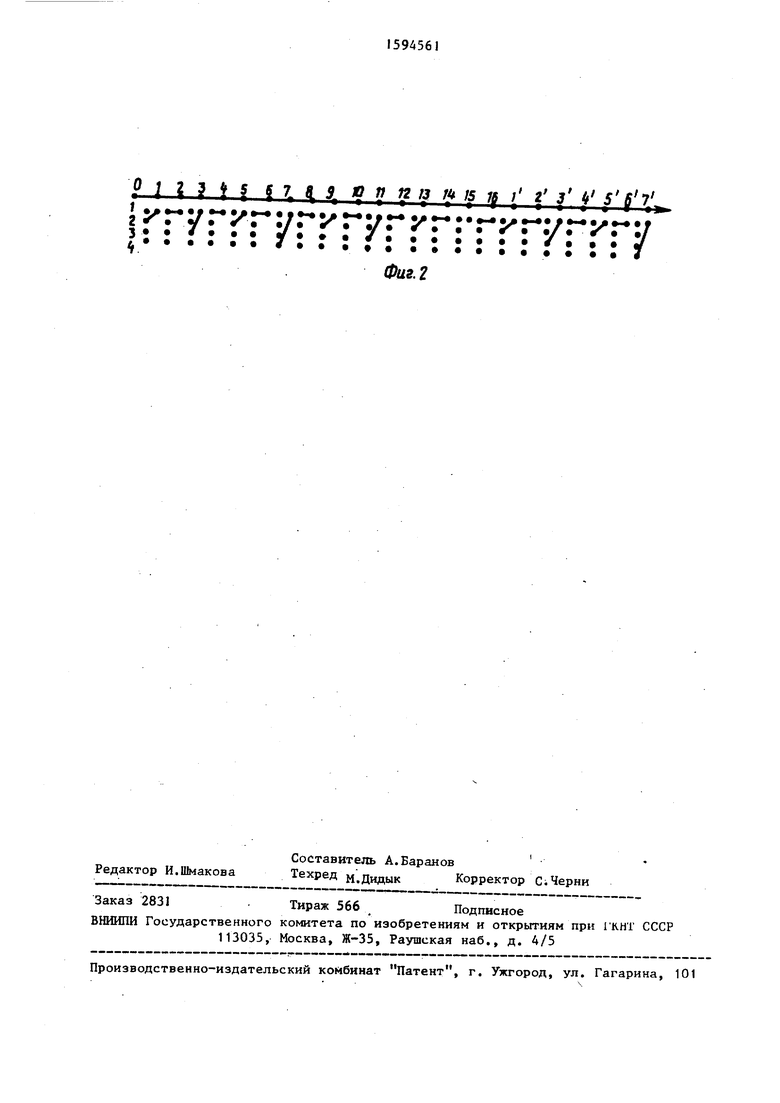

: На фиг.1 представлена функционал $тя схема устройства для ортогональ його преобразования цифровых сигналов по Хаару (N )| на фиг.2 - временные диаграммы работы коммутаторов ,

; Устройство содержит информацнонн йход 1, коммутаторы 2.1-2.5, суммат ычитатель 3, блоки 4.1--4.П задерж Первой группы, блоки 5..п-1 за- дершси второй группы, первый б и втрой 7 блоки сдвига, состоящие из последовательно соединенных регистров сдвига, информационный выход 8 устройства, блок 9 синхронизации, ыходы 10-12 синхронизации. Устройство работает следующим образом.

С частотой тактовых импульсов на ход 1 устройства поступают отсчеты входного сигнала. На четные такты ti, , , арифметический блок 3 выполняет 2 базовых операций Двухточечных преобразований (21-1)- и 2i-ro отсчетов соответственно (пе $ая ступень преобразования на граф- «Ьхеме БПХ). Вычисленные разности фтих отсчетов являются коэффициента с порядковыми номерами соответственно и поступают а вход первого блока 6 сдвига.

На нечетные такты сумматор-вычи- Татель 3 выполняет () базовых операций, соответствуюпщх ступеням преобразования на граф-схеме БПХ с Второго по п-й.

Коммутаторы 2.1-2.3 работают одинаково. Также одинаково работают коммутаторы 2, и 2,5,

Т2

2 Хаара +i)

На четные такты 2i, i 1,2 , коммутаторы 2.1-2,3 включены на первое положение, тогда 21-й отсчет че-; рез коммутатор 2.1, а (21-1 )-й отсчет через блок 4.1 задержки,, через коммутатор 2.2 поступают на входы сумматора-вычитателя 3, на вькоде которого имеются вычисленные сумма S,(i) X(2i-l) + X(2i) и разность R,(i) X(2i-l) - X(2i).

5

0

g

5

0

Сумма Sj(i) через коммутатор 2.3 поступает на вход блока 5.1 задержки, а разность R,(i), являющаяся ( +i)-M коэффициентом Хаара, через коммутатор 2.4 поступает на вход первого блока 6 сдвига. На нечетные такты ( -1 + , ,п-1, i 1,) коммутаторы 2.1-2.3 включены в (п+1-К)-е положение, при этом на входы сумматора-вычитателя 3 с блоков 5.П-К и 4.П+1-К задержки поступают соответственно, величины (21), 8„:к(21-1), где S.(j) S (2j) .S.,(2j-l). Ha выходе сумматора-вычитателя 3 имеется сумма ) и коэффициент Хаара с порядковым номером 2 . Величина .) через коммутатор 2.3 поступает в блок 5.П-К-И задержки, а коэффициент Хаара через коммутатор 2.4 - на вход первого бло- .ка 6, сдвига.

L

Во время (2 - -l)-fo (,n-l) такта сумматоргвычитатель 3 выполняет базовую операцию над промежуточны- ми результатами (п-К)-го этапа преобразования предьщущей выборки сигнала, т.е. на суммирующем выходе сумматора-вычитателя 3

с /оК-1

ij н

П-К4-1

()

h-K

(2) + s;,.k(2 -l).

5

0

а на вычитающем выходе - 2 -и коэффициент преобразования предыдущей вы- .борки сигнала. Во время ( )-го (,п-1) такта коэффициенты преобразования с вычитающего выхода сумматора-вычитателя 3 поступают в первый блок 6 сдвига, а сумма S J,,() через коммутатор 2.3, включенный на

(п4-1-к)-е положение, поступает в блок 5.П+1-К задержки. На ()-м такте вычисляются первый и второй коэффи- . циенты Хаара предьщущей выборки сиг5 t ° поступающему сигналу синх- ронизации (выход 12) коммутаторы 2.4 и 2.5 включены во второе положение. Через коммутатор 2.5 на выход 8 устройства поступает первый коэффиР циент Хаара, а второй коэффициент

Хаара через коммутатор 2.4 поступа- ет на вход N-ro регистра сдвига вто-, ; рого блока 7 сдвига. Следующие (N-1) тактов коммутаторы 2.4, 2.5 включены

в первое положение и через коммутатор 2.5 на выход 8 устройства поступают остальные (N-1) коэффициентов Хаара с выхода второго блока 7 сдвига и т.д.

На этом (2-1)-м такте на вход занесения в регистры второго блока 7 сдвига подается стробирующин сигнал с выхода 12 блока 9 синхронизации и тактовым импульсом информация на входах параллельного занесения регистров сдвига записывается в иих.

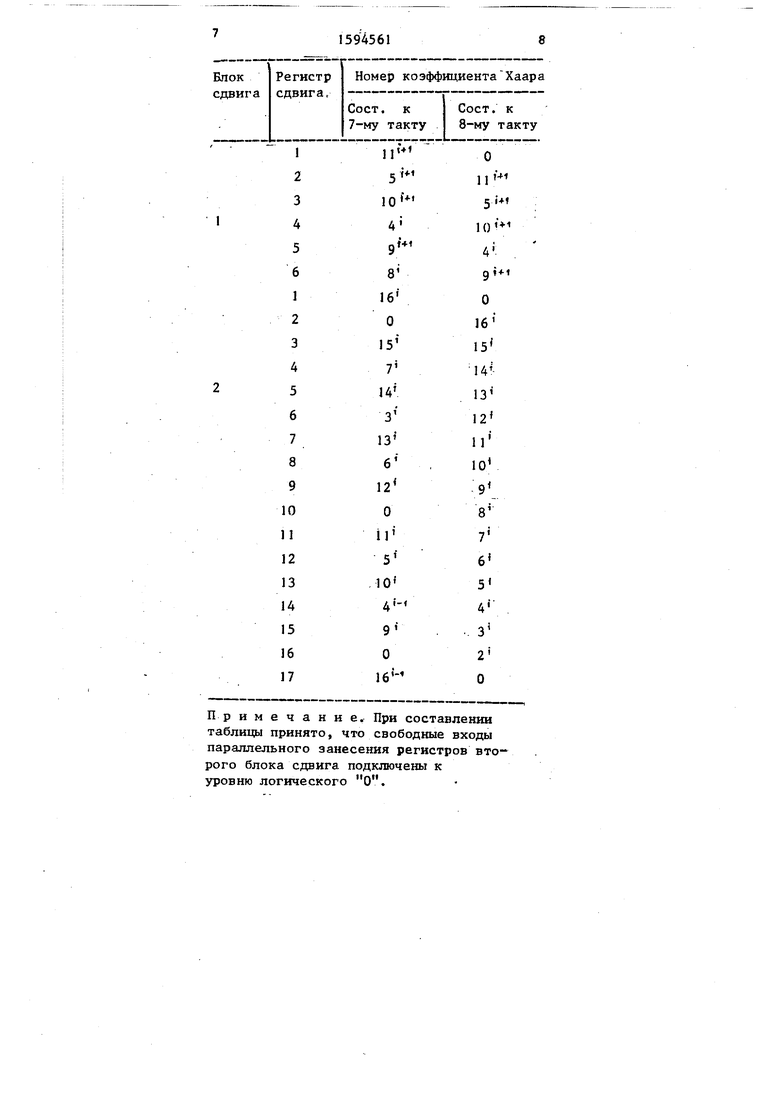

Поясним работу устройства анализом расположения коэффициентов Хаара в регистрах сдвига первого и второго блоков при . Содержимое регистров сдвига к началу 7-го и 8-го тактов некоторого i-ro цикла преобраз о- вания приведено в таблице.

В 7-м такте на входы занесения в регистры второго блока 7 сдвига подается разрешающей импульс и тактовый импульс записьшает информацию с - входов параллельного занесения в регистры.

Таким образом, соответствующее подключение выходов регистров сдвига к их входам параллельного занесения

10

тора, управляющий вход, которого соединен с управляющими входами первого и третьего коммутаторов и подключен к первому выходу блока синхронизации, второй выход которо го подключен к тактовым входам пер вого и второго блоков регистров сд га, i-й выход (,п-1; ра мер преобразования) третьего комму татора подключен к i-му входу втор го блока задерлски. i-й выход котор го подключен к (1+1)-му информацио ному входу первого коммутатора и

,с (i+1 ) -му входу второго блока задер ки, (1+1)-й выход которого подключен к (i+1)-му информационному вхо ду второго коммутатора, п-й выход третьего коммутатора подключен к

20 первому информационному входу пято го коммутатора, отличающе с я тем, что, с целью упрощения устройства, первый и второй выходы четвертого коммутатора подключены

достигается их расположением в естест- 25 соответственно к информационному

входу первого регистра сдвига блок регистров сдвига и информационному входу N-ro регистра сдвига блока регистров сдвига, выход ()-го 30 регистра сдвига первого блока реги ров сдвига подключен, к информацио ному входу первого регистра сдвига второго блока регистров сдвига, вы ход (2 +1)-го регистра сдвига кот

венном порядке, которое необходимо при последовательном вьшоде коэффициентов Хаара.

Формула изобретения

Устройство для ортогонального преобразования цифровых сигналов по Хаару, содержащее пять коммутаторов, два блока задержки, сумматор-вычита- тель, два блока регистров сдвига и блок синхронизации, причем вькодЫ - первого и второго коммутаторов подключены соответственно к первому и второму входам сумматора-вычитателя, выходы суммы и разности которого под- ключены к информационным входам соответственно третьего и четвертого коммутаторов, первый информационный вход первого коммутатора соединен

входу первого регистра сдвига блока регистров сдвига и информационному входу N-ro регистра сдвига блока регистров сдвига, выход ()-го 30 регистра сдвига первого блока регистров сдвига подключен, к информационному входу первого регистра сдвига второго блока регистров сдвига, выход (2 +1)-го регистра сдвига кото35

рого подключен к второму информационному входу пятого коммутатора, выход ( - )-го (,пг1) регистра . . сдвига первого блока регистров сдви- , га подключен к информациионому входу л0 ()-го регистра сдвига второго

блока регистров сдвига, выход

(N+2-2 -J- )-го (,n; , -(, где ..- символ Кронекера) регистра сдвига которого подключен

вход nepBUl U лиг-ич 1-. . /«.о 01-1 1

с первым входом первого блока задерж- 45 информационному входу (N+2-2J -1)-. -Ti fn в / 1 Л «ч

ки и является информационным входом устройства, информационным выходом которого является выход пятого коммутатора, первый выход первого блока задержки подключен к первому инфор-. мационному входу второго коммутаго регистра сдвига второго блока регистров сдвига, вход разрешения записи которого соединен с управляющими входам четвертого и пятого 5Q коммутаторов и подключен к третьему выходу блока синхронизации.

тора, управляющий вход, которого соединен с управляющими входами первого и третьего коммутаторов и подключен к первому выходу блока синхронизации, второй выход которого подключен к тактовым входам пер- / вого и второго блоков регистров сдвига, i-й выход (,п-1; размер преобразования) третьего коммутатора подключен к i-му входу второго блока задерлски. i-й выход которого подключен к (1+1)-му информационному входу первого коммутатора и

(i+1 ) -му входу второго блока задержки, (1+1)-й выход которого подключен к (i+1)-му информационному входу второго коммутатора, п-й выход третьего коммутатора подключен к

первому информационному входу пято- ч го коммутатора, отличающее- с я тем, что, с целью упрощения устройства, первый и второй выходы четвертого коммутатора подключены .

25 соответственно к информационному

входу первого регистра сдвига блока регистров сдвига и информационному входу N-ro регистра сдвига блока регистров сдвига, выход ()-го 30 регистра сдвига первого блока регистров сдвига подключен, к информационному входу первого регистра сдвига второго блока регистров сдвига, выход (2 +1)-го регистра сдвига кото35

рого подключен к второму информационному входу пятого коммутатора, выход ( - )-го (,пг1) регистра . . сдвига первого блока регистров сдви- , га подключен к информациионому входу л0 ()-го регистра сдвига второго

блока регистров сдвига, выход

(N+2-2 -J- )-го (,n; , -(, где ..- символ Кронекера) регистра сдвига которого подключен

/«.о 01-1 1

45 информационному входу (N+2-2J -1)Ti fn в / 1 Л «ч

го регистра сдвига второго блока регистров сдвига, вход разрешения записи которого соединен с управляющими входам четвертого и пятого 5Q коммутаторов и подключен к третьему выходу блока синхронизации.

Примечание. При составлении таблицы принято, что свободные входы параллельного занесения регистров второго блока сдвига подключены к урозню логического О.

У J g S 7, g я у у /j ;, /5 y ;/ 2 з «/

I

2 : : : : : : f : : : у

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования по функциям Хаара | 1986 |

|

SU1327119A1 |

| Устройство для выполнения обратного преобразования Хаара | 1983 |

|

SU1104528A1 |

| Устройство для преобразования по функциям Хаара | 1986 |

|

SU1322310A1 |

| Процессор для преобразования цифровых сигналов по Хааро-подобным базисам | 1987 |

|

SU1418745A1 |

| Параллельный процессор Хаара | 1989 |

|

SU1667103A1 |

| ПРОЦЕССОР БЫСТРОГО ПРЕОБРАЗОВАНИЯ СИГНАЛОВ ПО УОЛШУ С УПОРЯДОЧЕНИЕМ ПО АДАМАРУ | 1991 |

|

RU2025772C1 |

| Устройство для ортогонального преобразования цифровых сигналов по функциям Хаара | 1983 |

|

SU1116435A1 |

| Устройство для разложения цифровых сигналов по Уолшо-подобным базисам | 1983 |

|

SU1108461A1 |

| Устройство для преобразования булевых функций | 1988 |

|

SU1532946A1 |

| Устройство для ортогонального преобразования по Уолшу-Адамару | 1988 |

|

SU1571610A1 |

Изобретение относится к вычислительной технике и радиотехнике и может быть использовано в системах цифровой обработки сигналов, основанных на алгоритме быстрого преобразования Хаара. Цель изобретения - упрощение устройства. Поставленная цель достигается за счет того, что в состав устройства входят коммутаторы 2.1-2.5, сумматор-вычитатель 3, блоки задержки 4.1-4.п, 5.1-5.п-1, блоки сдвига 6, 7, блок синхронизации 9. 2 ил.

Фиг. 2

| Патент США № 3981443, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Хаару | 1982 |

|

SU1061150A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-09-23—Публикация

1988-05-18—Подача