(21)4185975/2А-24 .

(22) 22.01.87

(46) 23.08.88. Бкш. № 31

(71)Хозрасчетный научно-исследовательский институт Алгоритм при Узбекском научно-производственном объединении Кибернетика АН УзССР

(72)И.И.Исмагилов

(53) 681.32(088.8) .

(56)Рабинер Л., Гоулд В. Теория и применение цифровой обработки сигналов.- М.: Мир, 1978.

Авторское свидетельство СССР № 1168966, кл. G 06 F 15/332, 1985. :(34) ПРОЦЕССОР ДЛЯ ПРЕОБРАЗОВАНИЯ (ЦИФРОВЫХ СИГНАЛОВ ПО ХААРО-ПОДОБНЫМ . БАЗИСАМ .

(57)Изобретение относится к радиоэлектронике и может быть использовано в системах цифровой обработки сигналов, основанных на ортогональном преобразовании по Хааро-подобным базисам, когда объем входной выборки N .-.К, где Kj - натуральные - числа. Цель изобретения - упрощение устройства. Процессор содержит информационный вход I., вычислительные, блоки 2,-2,

переключатель , блоки

регистров сдвига , ,

синхронизации 6

блок Вычислительный бл ок

2 содержит элементы задержки 7-7, коммутатор 8, К умножителей ,, К узлов памяти ,, и -сумматор 11, i-й (i 2,п) вычислительный блок 2 содержит элемент задержки 12, умножитель 13, узел памяти 14, сумматор 15, регистры сдвига , и ключ. Процессор также имеет элемент задержки 18 и информационный выход 19. 2 .ил.

С5 :й

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор для преобразования цифровых сигналов по Хааро-подобным базисам | 1984 |

|

SU1168966A1 |

| Цифровой анализатор спектра в ортогональном базисе | 1983 |

|

SU1124326A1 |

| Устройство для ортогонального преобразования цифровых сигналов по функциям Хаара | 1983 |

|

SU1116435A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Хаару | 1988 |

|

SU1594561A1 |

| Устройство для выполнения обратного преобразования Хаара | 1983 |

|

SU1104528A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1981 |

|

SU1042028A1 |

| Устройство для преобразования по функциям Хаара | 1986 |

|

SU1327119A1 |

| Поточно-параллельный процессор Хаара | 1989 |

|

SU1756901A1 |

| Параллельный процессор Хаара | 1989 |

|

SU1667103A1 |

| Систолический процессор для двумерного дискретного преобразования Фурье | 1988 |

|

SU1608688A1 |

Иаай,

(, Т-25г 2, У25з fSn-r Y , ,

..

ф1/&/

гз I /

. 23/н

Изобретение относится к радиотехнике и может быть использовано в системах цифровой обработки сигналов, основанных на ортогональном преобра- | зовании по Хааро-подобным базисам, когда объем входной в;з1борки N К,,

К.

К

К ( любые натураль 2. 9 « 5

ные числа, i .

Цель изобретения - упрощение процессора путем снижения аппаратурных затрат, на его реализацию в случае, когда объем входной выборки N К ,

К

1

К, (К„ К

1

К,-.,

7, к.).

9 в 9

1 2,п.

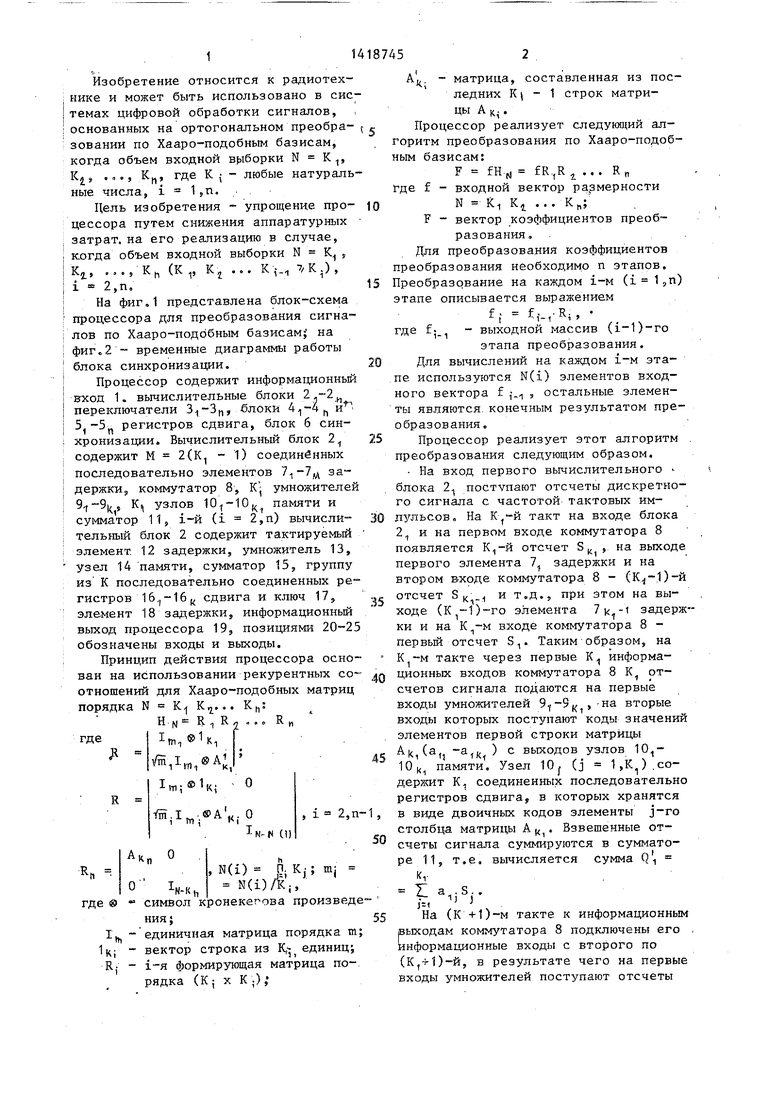

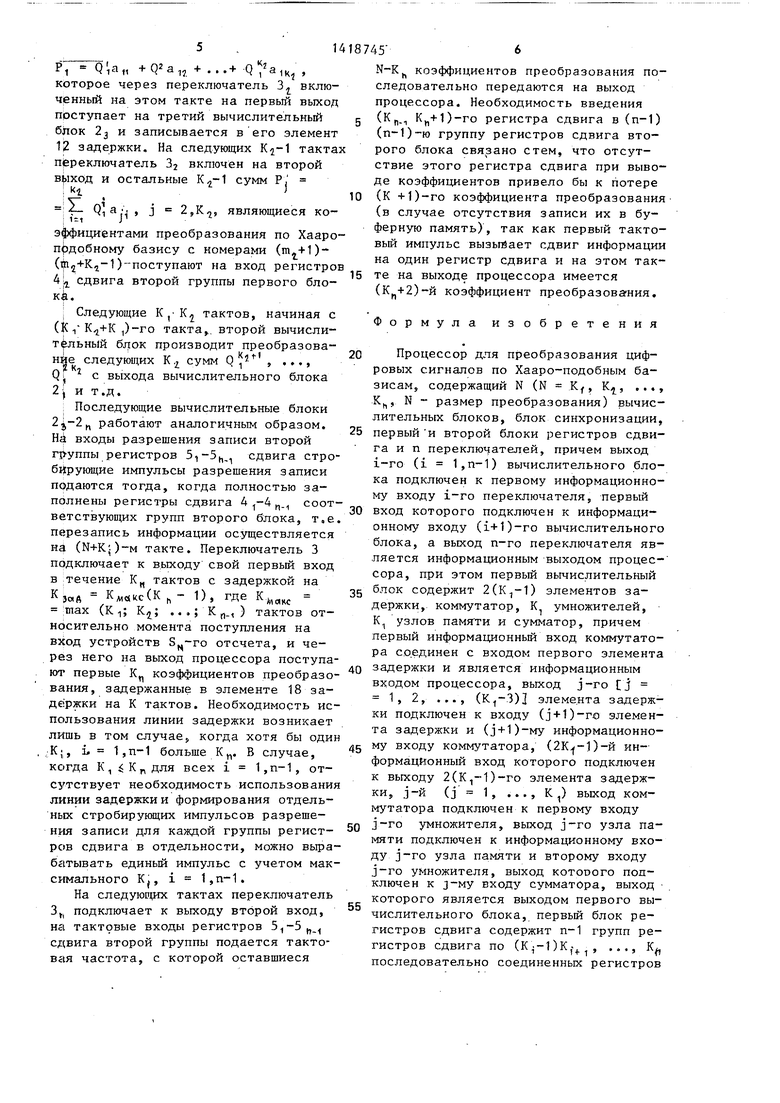

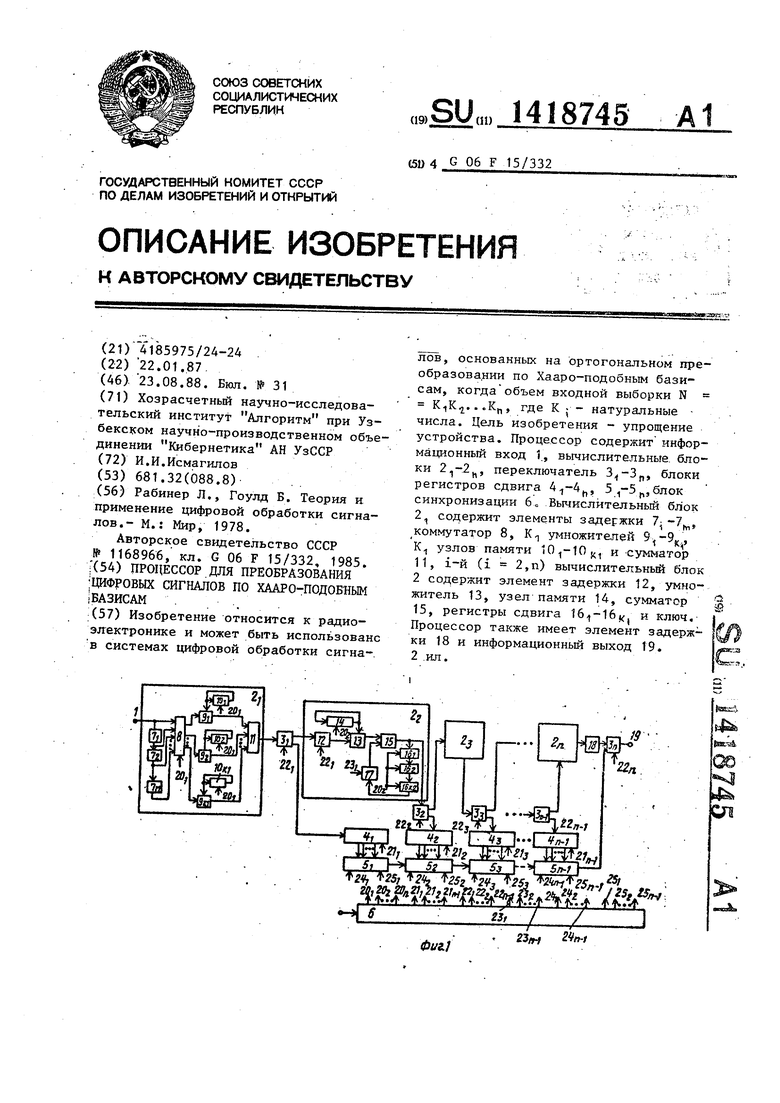

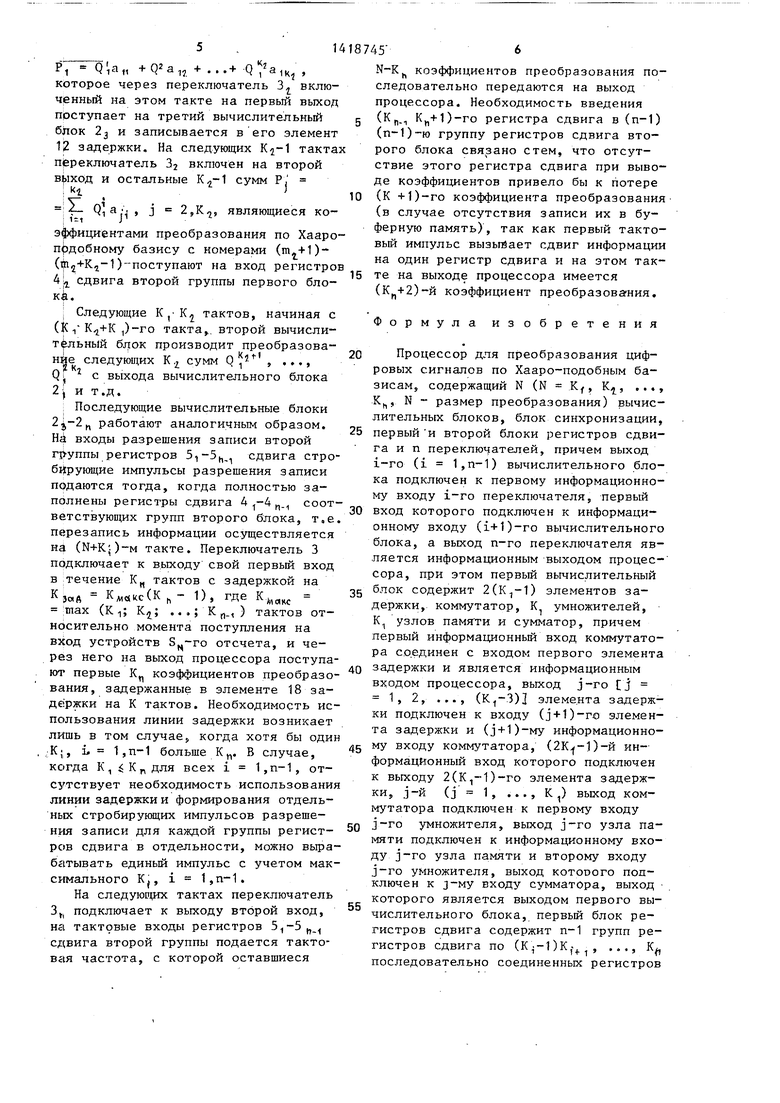

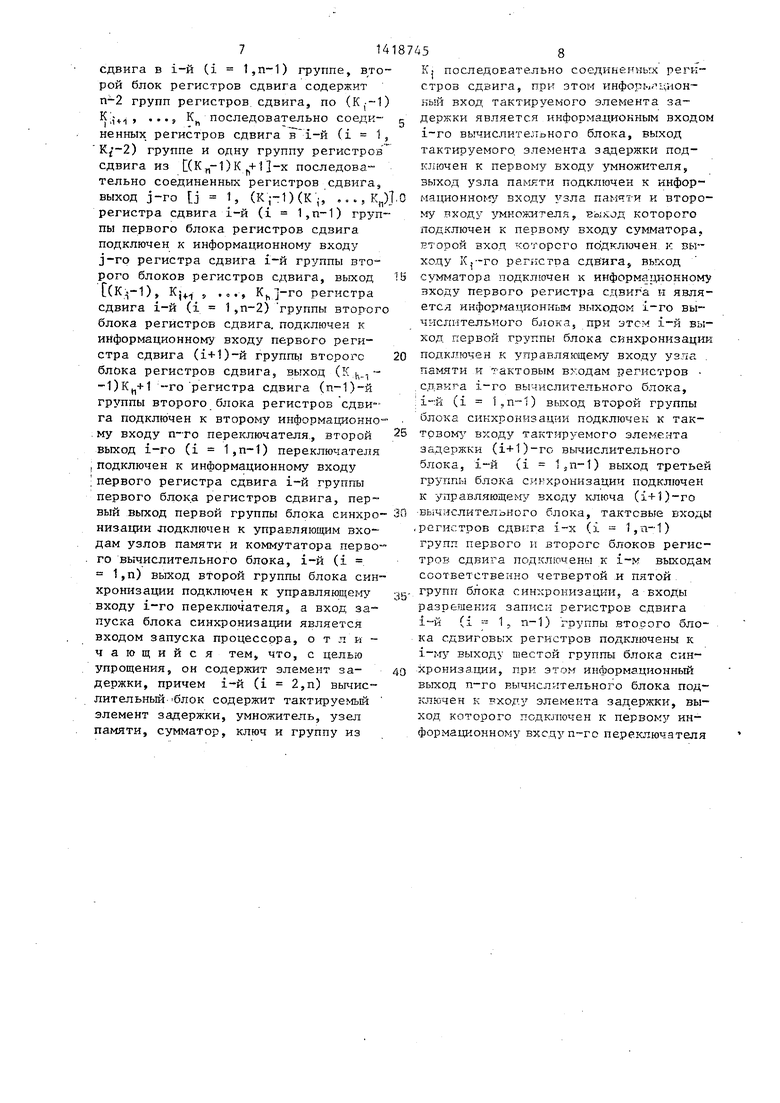

На фиг,1 представлена блок-схема процессора для преобразования сигналов по Хааро-подобным базисам на фиг.2 - временные диаграммы работы блока синхронизации.

Процессор содержит информационньй вход 1. вычислительные блоки 2,-2| переключатели , блоки 4;,-4f, регистров сдвига, блок б синхронизации. Вычислительный блок 2 содержит М 2(К - 1) соединенных последовательно элементов за- держкИд коммутатор 8, К умножителей узлов , памяти и сумматор 11, i-й (i 2,п) вычислительный блок 2 содержит тактируемый элемент, 12 задержки, умножитель 13, узел 14 памяти, сумматор 15, группу из К последовательно соединенных регистров 16,| -16 сдвига и ключ 17, элемент 18 задержки, информационный выход процессора 19, позициями 20-25 обозначены входы и выходы.

Принцип действия процессора основан на использовании рекурентных соотношений для Хааро-подобных матриц

10

15

20

25

35

40

порядка N К К

К,

- матрица, составленная из последних К) - 1 строк матри |

0

5

0

цы А

Кг

Процессор реализует следующий алгоритм преобразования по Хааро-подобным базисам:

F fH. fR-,R, ... К„ Где f - входной вектор размерности

N ...K|,} F - вектор коэффициентов преобразования.

Для преобразования коэффициентов преобразования необходимо п этапов. Преобразрвание на каждом i-м (i 1 ,,п) этапе описывается выражением

f,--,-K.

f,-

где f- - выходной массив (i-l)-ro

этапа преобразования. Для вычислений на каждом L-M эта- .пе используются N(i) элементов входного вектора f {. ,

остальньш элемен5

5

0

ты являются, конечным результатом преобразования.

Процессор реализует этот алгоритм , преобразования следующим образом.

На вход первого вычислительного блока 2 поступают отсчеты дискретного сигнала с частотой тактовых им- дульсов, На такт на входе блока 2 и на первом входе коммутатора 8 появляется К,-и отсчет S., , на выходе

-;

первого элемента / задержки и на втором входе коммутатора 8 - (К.,-,1)-й отсчет и т.д., при этом на выходе ()-го элемента 7 к -i задержки и на К -м входе коммутатора 8 - первый отсчет S,. Таким-образом, на такте через первые К информационных входов ком татора 8 К отсчетов сигнала подаются на первые входы умножителей 9.,-9 ,-на вторые входы которых поступают коды значений элементов первой строки матрицы

А

-а О

Tfci

) с выходов узлов

к памяти. Узел 10/ (j 1,К,).содержит К, соединенных последовательн регистров сдвига, в которых хранятся в виде двоичных кодов элементы j-ro столбца матрицы А«. Взвешенные отсчеты сигнала суммируются в сумматоре 11, т.е. вычисляется сумма Q,

Кг

-l-.

jn На (К +1)-м такте к информационны

выходам коммутатора 8 подключены его информационные входы с второго по (К,-1)-й, в результате чего на первы входы умножителей поступают отсчеты

S,-S . На вторые входы умножителей 9,-9 к подаются элементы второй строки матрицы АХ с выходов узлов 10ц, памяти. В результате на суммак,

торе вычисляется сумма

X S;,

Таким образом, последовательно вы1

числяются суммы Q, 2 а „-S-, при

р)

этом на ()-м такте первый вычислительный блок 2 заканчивает преобразование по основанию К первых К отсчетов сигнала. .

Первая из К, вычисленных сумм Qj через первый выход переключателя 3, на К-м такте переписывается в элемент 12 задержки второго вычислительного блока 2. На остальных тактах переключатель 3 включен на второй вход и остальные () вычисляемых сумм Qjo i - 2, К, являющиеся коэффициентами преобразования по Хааро- подобному базису с номерами (т+1)- (), поступают на вход регистров 4j первого блока, на которые подаются тактовые импульсы в течение К.-1 тактов.

Следующие К тактов, начиная с , первый вычислительный блок производит преобразование следующих К входных отсчетов (S +1)-S, и т.д.

После N-ro такта на вход первого вычислительного блока начинают поступать отсчеты следующей выборки, составленной из N отсчетов, а сумматор 11 за тактов вычисляет последние К -1 коэффициентов преобразования предьщущей выборки с порядковыми но- мерами с ()-ro по N-й, которые через переключатель 3 поступают на вход группы регистров 4 сдвига.

На следующем такте первый вычислительный блок 2 вычисляет первую сумму Q от первых К отсчетов второй выборки. На этом такте из блока син-, хронизации подается стробирующий им- пульс на вход разрешения записи пер- вой группы регистров сдвига второго блока, разрешающий поступление коэффициентов преобразования из группы регистров 4 сдвига в соответствующую группу регистров 5, сдвига.

Второй вычислительньй блок 2л работает следующим образом. Записанная с выхода блока 2, через переключатель

30

35 е

45 50 55

3 на К-м такте в элемент 12 задержки сумма О подается на первый вход умножителя 13, на второй вход которого поступает первый элемент первой строки матрицы А. с узла 14 памяти, Узел 14 памяти, содержит К последо- i вательно соединенных регистров сдвига, в которых последовательно записаны в виде двоичных кодов столбцы мат- ри1да АKj. На следующих тактах на второй вход умножителя 13 последовательно подаются элементы пер вого столбца матрицы Ai,j-aj, , а 3, .. з. Взвешенные значения Q, с выхода умножителя подаются на первьш вход сумматора 15, выход которого под1слючен к входу регистра 16 сдвига. На второй вход сумматора через ключ 17 под- ключен выход регистра 16«. Ключ 17 в течение этих К, тактов закрыт, поэтому на второй вход сумматора 15 в течение первых К тактов поступает уровень логического О. При этом на регистрах 16,-16ц сдвига записаны соответственно значения произведений

Q,a (к,-,)1. ° на вьгходе сумматора - значение .

На 2К -м такте в элемент 12 задержки записьгоается значение Q второй группы отсчетов сигнала S (; +, , кото рое в умножителе 13 перемножается с вторым элементом а , первой строки матрицы А, и сумматор 15 производит суммирование текущего результата умножения, со значением произведения Q,a предьщущего цикла обработки, которое поступает на второй вход сумматора 15 через открытьй ключ 17с выхода К,-го регистра сдвига. На этом . такте тактовые импульсы подаются в регистры 16,-16, сдвига и информация в них сдвигается, при этом в первом регистре 16 сдвига записывается произведение j предьщущего цикла обработки. На следующем (2К.ч-1)г-м такте в умножителе 13 Q умножается на элемент а,, и суммируется со значением Qlja, предьодущего цикла с выхода Kj-ro регистра сдвига, т.е. формируется частичная сумма РЧ - Q, . Таким образом осуществляется последовательных формирований частичных сумм Pj, ...,« в течение следующих тактов. Далее процесс формирования частичных сумм продолжается со значениями Q ..., Q . На ()-м такте на выходе сумматора 15 значение

+ Q a „+...+ , которое через переключатель 3. включенный на этом такте на первый выход поступает на третий вычислительньй блок 2з и записывается в его элемент 12 задержки. На следующих Kj-1 тактах п|ереключатель 32 включен на второй

вцход и остальные сумм Р, : KI .

; -

; .f- , j 2,К, являющиеся коэффициентами преобразования по Хааро- п0добному базису с номерами ()- (щ2+К,-1)поступают на вход регистров Aij, сдвига второй группы первого блоки.

: Следующие К, К, тактов, начиная с (К ,)-го такта, второй вычисли- тфльный блок производит преобразование следующих К . сумм Q , . Q с выхода вычислительного блока 21 и т.д.

; Последующие вычислительные блоки работают аналогичным образом. На входы разрешения записи второй регистров 5,-5, сдвига стро- бйрунщие импульсы разрешения записи подаются тогда, когда полностью заполнены регистры сдвига А -4 . соответствующих групп второго блока, т.е. перезапись информации осуществляется на (N+K;)-M такте. Переключатель 3 подключает к выходу свой первый вход в течение К„ тактов с задержкой на КЗОА Кд,о1кс( 1), где К.д ;шах ( .. .; К ,., ) тактов относительно момента поступления на вход устройств отсчета, и через него на выход процессора поступают первые К коэффициентов преобразования, задержанные в элементе 18 задержки на К тактов. Необходимость использования линии задержки возникает лишь в том случаер когда хотя бы один К;, 1. 1,п-1 больше К у,. В случае, когда К, Кр для всех i 1,п-1, отсутствует необходимость использования линии задержки и формирования отдельных стробирующих импульсов разреше- записи для каждой группы регистров сдвига в отдельности, можно вьфа- батывать единый импульс с учетом максимального Kj, i 1,n-1.

На следуюищх тактах переключатель 3 подключает к выходу второй вход, на тактовые входы регистров ,, сдвига второй группы подается тактовая частота, с которой оставшиеся

45 6

N-K коэффициентов преобразования последовательно передаются на выход процессора. Необходимость введения )-го регистра сдвига в (п-1) (п-1)-ю группу регистров сдвига второго блока связано с тем, что отсутствие этого регистра сдвига при выводе коэффициентов привело бы к потере

(К +1)-го коэффициента преобразования (в случае отсутствия записи их в буферную память), так как первый тактовый импульс вызывает сдвиг информации на один регистр сдвига и на этом такте на выходе процессора имеется

()-й коэффициент преобразования.

Формула изобретения

Процессор для преобразования цифровых сигналов по Хааро-подобным ба- зисам, содержащий N (N К, К, К, N - размер преобразования) вычис- лительньк блоков, блок синхронизации,

первый и второй блоки регистров сдвига и п переключателей, причем вЬ1ход i-ro (i 1,п-1) вычислительного блока подключен к первому информационному входу i-ro переключателя, первый

вход которого подключен к информационному входу (i+1)-ro вычислительного блока, а выход п-го переключателя является информационным выходом процес- сора, при этом первый вычислительный

блок содержит 2() элементов задержки, коммутатор, К умножителей, К узлов памя ти и сумматор, причем первый информационный вход коммутатора соединен с входом первого элемента

задержки и является информационным входом процессора, выход j-ro j 1, 2, ..., () элемента задержки подключен к входу (j+1)-ro элемента задержки и (j+1)-My информационноМУ входу коммутатора, ()-й информационный вход которого подключен к выходу 2(К,-1)-го элемента задержки, j-й (j 1, ..., К ) выход коммутатора подключен к первому входу

умножителя, выход j-ro узла памяти подключен к информационному входу j-ro узла памяти и второму входу j-ro умножителя, выход КОТОРОГО подключен к j-му входу сумматора, выход которого является выходом первого вычислительного блока, первый блок регистров сдвига содержит п-1 групп регистров сдвига по (K;J-I)K,., .,., К последовательно соединенных регистров

71418765

двига в i-и (i 1,n-1) группе, вто- К

ст кь де та кл вы м му по ВТ х су в е ч х п п сд : 1 т з г к

рой блок регистров сдвига содержит п-2 групп регистров сдвига, по ()

:К последовательно соеди1S

ot-i ненных регистров сдвига в а-й (,

К/-2) группе и одну группу регистров сдвига из С(К„-1)К +11-х последовательно соединенных регистров сдвига, выход j-ro j 1, (К,-1)(К ;, ,..,К).0 регистра сдвига i-й (i 1,п-1) группы первого блока регистров сдвига подключен к информационному входу j-ro регистра сдвига i-й группы втоого блоков регистров сдвига, выход t(K;.-1), Kj. 5 .0., регистра сдвига i-й (i 1 ,п-2) группы втор-ого блока регистров сдвига, подключен к информационному входу первого регистра сдвига (i+1)-й группы второго блока регистров сдвига, выход (К (. - -1)Kj,+ 1 -го регистра сдвига (п-1)-й группы второго блока регистров сдвига подключен к второму информационно™

у входу п-го переключателя., второй выход i-ro (i 1,n-1) переключателя

подключен к информационному входу

ервого регистра сдвига i-й группы первого блока регистров сдвига, пер20

25

вый выход первой группы блока синхро- 30 вычислительного слока, тактовые входы

.регистров сдвига i-x (1 1, а-1) групп первого и второго блоков регистров сдвига подключены к 1-м выходам

низации лодключен к управляющим входам узлов памяти и коммутатора первого вычислительного блока, i-й (i 1,п) выход второй группы блока синхронизации подключен к управляюпдему входу i-ro переклю ателя, а вход запуска блока синхронизации является входом запуска процессора, о т ли - чающийся тем, что, с целью упрощения, он содержит элемент задержки, причем (i 2,п) вычис- лительньй- блок содержит тактируемьй элемент задержки, умножитель, узел памяти, сумматор, ключ и группу из

соответственно четвертой -И пятой .

.щ, групп блока синхронизации, а вхоДы разрешения записи регистров сдвига (1 --- I, п-1) группы второго блока сдвиговых регистров подключены к i-1-ту выходу шестой группы блока син40 хронизации, при этом информационный выход п-го вычислительного блока подключен к входз элемента зад ержки, выход которого подключен к первом информационному входу переключателя

К

S

0

5

К. последовательно соединенных регистров сдвига, при этом инфорьяцион- вход тактируемого элемента задержки является информадиокным входом вычислительного блока, выход тактируемого, элемента за,цержки подключен к первому входу умножителя, выход узла памяти подключен к инфор- мационно . входу узла памяч-и и второму входу гмножителя, выхюд которого подключен к первому входу сумматора, ВТОРОЙ вход которого подключен к выходу регистра сдв ига, сумматора подключен к информагдаонному входу первого регистра сдвиг а и является информационным выходом 1-го вычислительного блока, при этом 1-й выход первой группы блока синхронизации подключен к управляющему входу узла . памяти и тактовым входам регистров - сдвига i-ro вычислительного блока, : (i 1,п-1) выход второй группы блока синхронизации подключен к тактовом входу тактируемого элемента задержки (i+1)-ro вычислительного блока, 1-й (1 IjR-l) выход третьей группь блока синхронизации подключен к управляющем:/ входу ключа (1+1)-го

соответственно четвертой -И пятой .

групп блока синхронизации, а вхоДы разрешения записи регистров сдвига (1 --- I, п-1) группы второго блока сдвиговых регистров подключены к i-1-ту выходу шестой группы блока синхронизации, при этом информационный выход п-го вычислительного блока подключен к входз элемента зад ержки, выход которого подключен к первом информационному входу переключателя

А

(11ЩЙйРШ1ДМДШ1МЖйОШШ Ш ПП ППП ППЖ1ЕЦ

п п р п п п t

LS--t-gJ

illjL Jl

L

«5 . .1 Дг

gf.,..11Пд..тдЛпя,аяя„.лдд..,лпп nnn.

- -CZLt

%r

Us-aJ

irzi

nt

Авторы

Даты

1988-08-23—Публикация

1987-01-22—Подача