подключен к первому входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ,прямой выход седьмого дополнительного триггера соединен с вторыми входами пятого основного и третьего дополнительного элементов И и входом второго элемента задержки, а инверсный его выход соединен с«первым входом второго основного триггера, выход главных синхронизирующих импульсов распределителя соединен с вторыми входами пятого и шестого дополнительных триггеров, выходы разрядных сигналов распределителя подключены к вторым входам группы И элментов И, при этом выходы ц-го и нулевого (знакового) разрядов распределителя соединены с первым и втрым входами восьмого дополнительного триггера, выход сигнала пере полнёния счетчика подключен к вторым входам четвертого основного триггера первого дополнительного элемента И и второго дополнительного элемента ИЛИ, выход второго основного элемента И соединен через элемент задержки с первым входом четвертого основного элемента И, а выход третьего основного элемента И соединен с вторым входом первого дополнительного триггера, выход четвертого основного элемента И подключен через вторую интегрирующую цепь к вторым входам третьего основного элемента ИЛИ и первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы группы ц элементов И подключены к п входам третьего дополнител ного элемента ИЛИ, выход третьего дополнительного элемента И

подключен к третьему входу второго основного элемента ИЛИ, выход четвертого дополнительного элемента И соединен с третьим входом второго дополнительного элемента ИЛИ, выход второго дополнительного элемента И соединен с информационным входом регистра сдвига, выход которого подклю 1ен к первому входу пятого дополнительного элемента И, выход которого является кодовым выходом преобразователя, выход первого до- полнительното элемента И подключен к второму входу третьего основного триггера, выход третьего основного элемента ИЛИ связан с в1;орым входом второго основного триггера, выход второго дополнительного элемента ИЛИ соединен с вторым входом третьего дополнительного триггера, выход третьего дополнительного элемента ИЛИ подключен к третьему входу второго дополнительного элемента И и второму входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого дополнительного элемента ИЛИ подключен к второму входу пятого дополнительного элемента И, выход второго элемента задержки подключен к второму входу седьмого дополнительного триггера, выход первого Элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входом четвертого до-полнительного триггера, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ .через третью,инвертирующую цепь соединен с третьим входом четвертого дополнительного элемента И, П кодовых выходов счетчика подключены соответственно кг входам-че.твертого основного элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ТЕЛЕСИГНАЛИЗАЦИИ | 1991 |

|

RU2029378C1 |

| КОДОИМПУЛЬСНОЕ ПЕРЕДАЮЩЕЕ УСТРОЙСТВО С СОКРАЩЕНИЕМ ИЗБЫТОЧНОСТИ ИНФОРМАЦИИ | 2001 |

|

RU2234738C2 |

| Устройство для приема и обработки команд телеуправления | 1989 |

|

SU1667137A1 |

| Измеритель временных интервалов | 1982 |

|

SU1034012A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ И ПЕРЕДАЧИ СИГНАЛОВ | 2004 |

|

RU2282246C2 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ПЕРЕДАЧИ ПОСЛЕДОВАТЕЛЬНОСТИ СИГНАЛОВ | 2005 |

|

RU2299474C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ МОТОРНЫМИ ПРИВОДАМИ РАЗЪЕДИНИТЕЛЕЙ КОНТАКТНОЙ СЕТИ | 2004 |

|

RU2274904C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННОГО ЗАМКА | 2006 |

|

RU2345203C2 |

| УСТРОЙСТВО ПРИЕМА КОМАНД УПРАВЛЕНИЯ | 2002 |

|

RU2237287C2 |

| ФОРМИРОВАТЕЛЬ КОМАНД УПРАВЛЕНИЯ | 2003 |

|

RU2244960C2 |

ПРЕОБРАЗОВАТЕЛЬ ВРЕМЯ-КОД, содержащий генератор импульсов, выход которого соединен с входом распределителя импульсов, синхронизирующим входом регистра сдвига и первыми входами первого и второго элементов И, первый триггер, прямой выход которого подключен к второму; входу первого элемента И, второй, триггер, выход которого соединен с вторым входом второго элемента И,, третий триггер, инверсный выход которого соединен с первым входом четвертого триггера, прямой выход которого является Выходом сигнала контроля, а инверсный выход соединён.с первым входом третьего элемента И, второй вход которогоявляется вхо-. дом преобразователя, а выход сое- ; динен через первый элемент задержки с входом первого триггера, счетчик, кодовые выходы которого подключены к первым входам группы Ц элементов И, четвертый элемент И, пятый элемент И, выход которого подключен через первый элемент ИЛИ к входу обнуления счетчика/второй элемент ИЛИ, выход которого соединен со счетным входом счетчика , а два первых входа соеда нены соответственно с, выходами первого и второго элементов И, третий элемент ИЛИ, а также второй и третий элементы задержки, отличающийся тем, что, с целью повышения достоверности преобразования, в него дополнительно введены восемь триггеров, пять элементов И, три элемента ИЛИ, два элемента ЙСКЛОЧАКЩЕЕ ИЛИ, три интегрирующих цепи, причем эыход первого основнОго триггера соединен с входом . первого дополнительного триггера, а инверсный его выход подключен- к первым входам вт.орого дополнительного триггера и первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, ВЫХОД второго основного триггера соединен с вторым входом второго дополнительного и первым входом третьего дополнительного триггеров, прямой выход третьего основного триггера подключен к первым.входам первого :дополнительного элемента И и первого дополнительного элемента ИЛИ, прямой выход «g четвертого основного триггера сое(Л динен с вторым входом первого дополнительного элемента ИЛИ, выход первого дополнительного триггера подключен к второму входу первого основного и к первым входам третьего 5 основного и второго дополнительного элементов ИЛИ, прямой выход второго дополнительного триггера соединен с первыми входами пятого основного к второго дополнительного элементов И, а инверсный его выход соединен с первыми входами третьего и Четвертого дополнительных элементов И, выход четвертого допол.нительнрго триггера через пятый дополнительный триггер и первую интегрирующую цепь соединен с первыми входами четвертого и шестого дополнительных триггеров, прямой выход последнего подключен к вторым входам второго и четвертого дополнительных элементов И, а инверсный его выход соединен с первым входом Седьмого дополнительного триггера выход третьего дополнительного триггера соединен с первым входом третьего основного триггера, выход восьмого дополнительного триггера

1

Изобретение относится к измерительной технике и может быть использовано в автоматизированных и автоматических измерительных системах.

Известен преобразователь времякод, содержащий соединенные последовательно генератор, триггер, счет,чик и схему И ij .

Недостатком такого преобразователя является отсутствие контроля работы счетчика и исправности кодовых выходов счетчика преобразовате-. ля.

Известен также преобразователь время-код, содержащий генератор пульсов, соединенный с входами двух элементов И,-триггер, вход которого подключен к второму входу первого элемента И, второй триггер, соединенный с вторым входом второго элемента И, третий триггер, инверсный выход которого связан с входом четвертого триггера, прямой выход которого является выходом сигнала

контроля, а инверсный выход соединен с входом третьего элемента И, второй вход которого является входом преобразователя, а выход связан через элемент задержки с. входом пер-

0 врго триггера, счетчик, выходы разрядов которого подключены к первым входам группы П элементов И, четвертый элемент И и пятый элемент И, подключенный через третий элемент

5 ИЛИ к входу обнуления счетчика, первый элемент ИЛИ, связанный выходом ео счетным входом счетчика, а двумя первыми входами соединенный с выходами первого и второго элементов И, второй элемент ИЛИ, второй и третий элементы задержки, регистр сдвига, пятый вход которого подключен к вы ходу генератора импульсов и к входу распределителя 23 . Данный преобразователь содержит схему контроля, обеспечивёиощу повы шение достоверности его работы. Однако его схемой контроля не охвачены кодовые выходы накопительного сч чика и элементы И съема с него инфо мации, что приводит к снижению; достоверности выходной информации об измеренном временном-интервале. Цель изобретения - повыше достоверности преобразования путем в дения контроля состояния кодовых вы ходов счетчика и элементов И съема информации со счетчика. Поставленная цель достигается тем, что в преобр эователь время-ко содержащий генератор импульсов, -выход которого соединен с входом распределителя импульсов, синхронизирующим входам регистра сдвига и пер выми входами первого и второго элем тов И, первый триггер, прямой выход которого подключен к второму входу первого элемента И, втйрой триггер, выход которого соединен с вторым входом второго элемента И, третий триггер, -инверсный выход которого сое динен с первым входом четвертого триггера, прямой выход которого является выходом сигнала контроля, а инверсный выход соединен -с первым, входом третьего элемента И, второй вход которого является входом преобразователя, а выход соединен чере первый элемент задержки с входом первого триггера, счетчик, кодовые выходы которого подключены к первым входам группы п элементов И, четвер тый элемент И, пятый элемент И, которого подключен через первый элемент ИЛИ к входу обнуления счетчика, второй элемент ИЛИ, выход которого соединен со счетным входрм счетчика,, а два первых в-хода соединены соответственно с выходами первого и второго элементов И третий элемент ИЛИ, а также второй и трети элементы задержки, дополнительно вв дены восемь триггеров, пять элементов И, -три элемента ИЛИ, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, три интегрирующих цепи, причем выход первого основного триггера соединен с входом первого дополнительного триггера, а инверсный его выход подключен к первым входам второго дбполнительного три1-гера и первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ,ВЫХОД второго основного триггера соединен с вторым входом второго дополнительного и первым входом третьего дополнительного триггеров, прямой выход третьего основного триггера подключен к первым входам первого дополнительного элемента И и первого дополнительного элемента ИЛИ, прямой четвертого основного триггера соединен с вторым входом первого дополнительного элемента ИЛИ, выход первого дополнительного триггера подключен к второму входу первого основного и к первым входам третьего основного и второго дополнительного элементов ИЛИ, прямой выход второго дополнительного триггера соединен с первыми входами пятого основного и второго дополнительного элементов И, а инверсный его выход соединен с первыми входами третьего и четвертого дополнительных элементов И, выход четвертого дополнительного триггера через пяты дополнительный триггер и первую интегрирующую цепь соединен с первыми входами четвертого и шестого дополнительных триггеров, прямой выход последнего пЪдключен к вторым входам второгр и четвертого дополнительных элементов И, а инверсный его выход соединен сПервым входом седьмого дополнительного триггера, выход третьего дополнительного триггера соединен с первым входом третьего основного триггера, выход восьмого дополнительного триггера подключен к первому входу второго элемента. ИСКЛЮЧАЮЩЕЕ ИЛИ, прямой выход седьмого дополнительного триггера соединен с вторыми входами пятого основного и третьего дополнительного элементов И и входом второго элемента Зсщержки,. а инверсный его йыход соединен с первым входом второго основного триггера, выход главных синхронизирующих импульсов 1распределителя соединен с вторыми входами пятого и шестого дополнительных триггеров, выходы разрядных сигналов распределителя подключены к вторым входам группы п элементов И, при этом выходы п-го и нулевого (знакового) разрядов распределителя соединены с первым и вторым входами восьмого дополнительного триггера, выход сигнала переполнения счетчика подклю-, чен к вторым входам четвертого основного триггера первого дополнительного элемента И и второго дополнительного элемента ИЛИ, выход второго основного элемента И соединен с.через третий элемент задержки с первым входом четвертого основного элемента И, а выход третьего основного элемента И соединен с вторым входом первого дополнительного триггера, выход четвертого основного элемента И подключен через вторую интегрирующую цепь к вторым входам третьего основного элемента ИЛИ и первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ,

выходы группы п элементов И подключеиы к и входам третьего дополнительного элемента ИЛИ, выход третьего дополнительногоэлемента И подключен к третьему входу в-ророго основного элемента. ИЛИ, В1ыхрд четвертого дополнительного элем(энта И соединен с третьим входом второго дополнительного элемента ИЛИ, выход йторого дополнительного элемента И соединен с информационным входом регистра сдвига, выход:которого Подключен кпе рвому вхрду пятого дополнительного элементе и;/выхОд которого является кодовым йыагодом преобразователя, выход первого до-. полнительного элемента, И подключен

К второму входу третьего основного триггера, выхоя третьего основного элемента ИЛИ связан с вторым входом jBToporo основногб ,триггера, выход в.торого дополнительного элёменд-а ИЛИ соединен с вторым входом третьего,

Дополнительного триггера, выход . третьегодополнительног® )га ИЛИ подключен к третьему входу второго дополнительного элемента Ии второму входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход дол рлнительного элемента ИЛИ йедключен к второму входу пятого дополнительного элемента И,-выход втрро о эле-, мента задержки подключ-ен к второму входу седьмого дополнительного триггера, . выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входом четвертогр дополнительного триггера, выход -второго ИСКЛЮЧАЮЩЕЕИЛИ через третью интег.рирующую. цепь соеди-нен с третьим входом четвертрго дополнительного элемента.И, ц кодовых выходов счетчика подключены соответственно к П входам четвертого осноЬного элемента И.

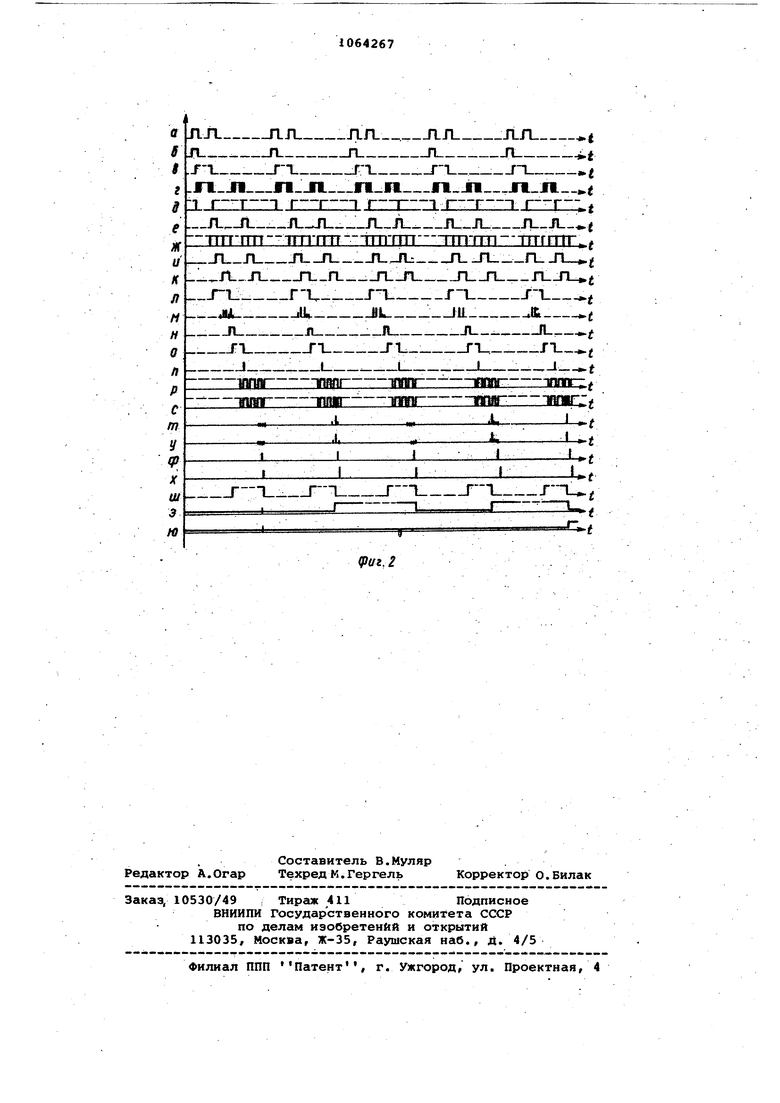

На фиг.1 представлена блок-схема преобразователя время-код на фи.г.2 - временные диаграммы его работы.. .

Преобразователь время-код (фиг.1) содержит генератор 1 импульсов этаонной частоты, распределитель 2 импульсов, элементы И 3 и 4, элеент ИЛИ 5, элемент 6 задержки, триггеры 7 и 8, элемент 9 задержки, лемент ИЛИ 10, элемент И 11, триггеры 12 и 13, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14, интегрирующую цепь 15, группу , элементов И, элемент ИЛИ 17, элемент И 18, интегрирующую цепь 19, накопительный счетчик 20, элемент ИЛИ 21, элемент ИСКЛЮЧАЮЩЕЕ шШ 22, триггер 23, элементы И 24, и 25, элемент ИЛИ 26, триггеры-27 и 28, интегрирующую цепь 29, триггер 30, элементы И 3.1 и 32, регистр 33 сдвига, элемент

И 34, триггеры 35 и 36, элемент И 37, триггеры 38 и 39, элемент 40 задержки, элемент ИЛИ 4i, входную шину 42 врёме.нного интервала, выходную шину 43 кода временного интервсша и выходную шину 44 сигнала контроля, . .

Выход генератора 1 связан с входамйг .элементов И 3 и 4 и распредег лителя 2 импульсов и такт.ирующим входом регкстра 33 сдвига, выход синхронидирующёгОу главного импулы са распределителя 2 подключён к синхронизирующим входс1м триггеров 28 и ЗО, выходы сигналов разрядов l-n. pacпpeдeлитeJlя 2 соединены с первыми входами группы , .элементов И, выход сигнала п-го разряда -распределителя 2 подключен к входу установки- в единицу триггера 13, а выход ну левого (/эндкового) разряда рачзпределителя 2 св.язан с входом установки внуль триггера 13, выход элемента И 3 подключен к входу элемента ИЛИ 5, выход кртораго связан со. счетным входом счетчика 120, выход элемента И 4 подключен к входам .элемента ИЛИ 5 и элемента 6 задержки, выход KOTopqro связан с входом элемента И 18, )прямрй выход .триггера 7 подключен к.входам элемента ИЗ и триггера 8v а инверсный выход связан с входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ,

22и триггера 23, выход триггера -8 подключен к входам элементов ИЛИ 10, 21 И 6, выход элемента- 9 задержки., связан с входом триггера 7, выход элем.ента ИЛИ 10 подключен к входу триггера 12,-выхрд которо.го связан

с входами триггеров. 23 и 35 jj элемента И 4, выход триггера 13 соединен с входом элемента ИСКЛЮЧАКМЦЕЕ ИЛИ 14, выход которогр черезинтёгрирующую цепь is подключен к входу э.лемента И 31,- выходы группы эле.мент-ов И чер.ез э.лемент ИЛИ 17 .связаны с входами элемента .ИСКЛЮЧАЮЩЕЕ ИЛИ 14 и элемента и.32, выход элемента И 18 через интегрирующую цепь 19 подключен к входам элемента ИЛИ 1 и элемента И.СКЛЮЧАЮ(ЧЕЕ ИЛИ 22, кодовые выходы счетчика 20 связаны, с вторыми входами группь;, ,6, элементов И и элемента И 18, а его выход переноса подключен к входам триг.гера 38, элемента -Н 37 и элемента ИЛИ 21, выход i OTOporo соединен с входом триггера.35, выход .элемента ИСК.ЛЮЧАЮЩЕЕ ИЛИ 22 подключен к входу триггера 27, прямой выход триггера

23связан с входами элементов И 24

и 32, а инверсный его выход, срединен с входами элементов И 25 и ЗГ, выходэлемента И 24 подключен черкез элемент ИЛИ 26 к входу обнуления счетчика 20, выход элемента И 25 связан с входом элемента ИЛИ 5, выход триггера 27 подключен к входу триггера 28, ВЫХОД которого черкез интегрирую щую цепь 29 связан с входами триггеров 27 и 30, прямой выходiтриггер 30 подключён -к,входам элементов И 3 .и 3.2, а инверсный его выход -овязан с входом триггера 39, выход элемента И 31,соединен;с входом элетлен та ИЛИ 21, вЕ«од элемента И .ключен к входу регистргГ 33, вы1||:од - которого свя зан с входом элемеита И 34-, выход которого соедайён с .цщной 4;3 кода временного интёрв-апа, ВЫХОД: триггера 35 подключен ,к в-хЬду триггера 36, пр-янюй выход связан с входом триггера 38, .а ияверсный ёговыхЪд соединен с Bxdv да1Ми элемента И 37 -и элемента ИЛИ 41, выход элемента И 37 подключен к входу триггера. 36, прямо выход триггера 38 связан с входом элемейта ИШ 41 и шиной 44 сигнала контроля, а инверсный его выход г с элементом И 11, прлмой В1ЛХо триггера, 39 подключен к входам элементов И 24 и 25 и элемента 40 ssir держки, а инверсный его выход свяэан с входом триггера 12, выход эле мента 40 задержки соединен с входом триггера 39 .выход элемента ИЛИ 41 подкли5ч н к входу элёмента И 34, входная шина 42 временного интервала связана Ь входом элемента. И 11/ выход которого .связан с входами триггера 8 и элемента 9 -вадержки. Преобразователь время-код работа ет следующим образом. . При включении преобразователя в работу осуществляе.тся начальное обнуление врех. элементов памяти преобразователя (цепь начального обнуления на фигИ не показана) . . На входную 42 преобразоватё ля ,поступает пара импульсов (фиг.2а которая через -элемент И 11 поступает на синх|)онизирук щий вход тригге- ра 8 и через элемент 9 задержки на синхронизирующий вход TpHrret a 7. . При этом на выходе триггера 8 по це реднему. фронту. первого импульса пЭяры формируется сигнал (фиг.2б), который устанавливает в состояние О счетчик 20 через элемент ,. ИЛИ 26ч, триггер 12 через элемент ИЛИ 10 и триггер 35 Через элемент ИЛИ 21. Сигнал,, сформированный на выходе триггера 7 (фиг. 2в.) ,. вбзбужпая вход элемента ИЗ, подключает . через, элемент ИЛИ 5 вы.ход генера7 тора 1 к счетному входу сче.тчика 20 (фиг.2)г) и устанавливает в состояние О триггер 8. По окончаНИИ временного интервала счетчик 20 отключается от выхода генератора 1, при этом по положительному фронту инверсного сигнала (фиг.д) на выход триггера. 7 триггер 27 устанавливается в состояние (фиг.2е)-, Боэбуждая вхдд 1 триггера 28, синхронизирующий вход которого возбуждав ется синхронизирующими импульсами генератора 1,поступающими с распределителя: 2 импульсов (фиг.2ж). При -наличии возбуждения -на входе Х триггер 28 в моьфнт: поступления импульса генератора. 1 :переклюЧ ается в состояние , возбуждая через интегрирующую цепь триггера. 3,0 (синхронизирующий вход кото-, pqro также возбуждается импульсами генератора ) и переключая в состояние О триггер 27. По спеду1&- дему импульсу генератора 1 -триггер 30 переключается в состояние Д, .а триггер 28 - в состояние . По третьему -импульсу генератора 1 триггер 30 возвращается в состояние 0 (фиг.2е,и,к),. формируя на . своем выходе сигнал съема кода, который возбуждает один из входов элементов И 31 и Д2., Съем информации со счетчика -20 в послед овательчом коде осуществляется в преобразователе с-помощью группы 16 -16f| элементов И, один из входов которых /возбуждается, кодовыми выходами счетчика 20, а вторые входа группу 16 -l-6j элементов, И возбуждаются сигналами разрядов, снимаемых с распределителя, 2 импульсов. Информация со счетчика 20, собранная на злементе ИЛИ 17 (иг.2с) , возбуждает, один из входов элемента И 32 и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ J14.Третьи вч;оды элементов И 32,.31 возбужлаются. выходами триггера 23, причем вход элемента И 32 возбужда.ется пр.ямь1м выходом--триггера, а .вход элемента И ЗЛ - -его инверсным выходом. Триггер 23 переключается в состояние ,М , по окончании сие-. нала врем н ого-интервала (фиг.2в, и,л) , обеспв ивая- в момент присутствия на: выходе триггера 30 сигнала съема кода запись, информации со счетчИка 20 регистр 33 сдвига .ерез элемент И 32 (фиг.2м). По заднему фронту сигнала съема с инверсного выхода триггера 30 триггер 39 переключается в состояние Ч на время, определяемое элементом 40 задержки, формируя при этом на-своем прямом выходе сигнал (фиг. 2н)., который проходит через элемент И 24, и элемент ИЛИ 26 наобнуление .счетчика 20. По зад не- -. му фронту сигнала с инверсного выходца .триггера 39 триггер 12 переключ чается в состояние 1 Лфиг.2о), обнуляя при этом триггер 23 и подключая через элемент И 4 и элемен КЛИ 5 выход генератора 1 к счетному входу счетчика 20 (фиг.2г) . Заполнение Счетчика 20 импульсами с генератора 1 осуществляется до тех пор, пока все разряды счетчика не окажутся в состоянии Ч (при исправном состоянии счетчика 20). В этот момент все п входов элемента И 18 оказываются возбужденными и е дующий импульс Q генератора 1, появившийся на (n+D-M входе элемента И 18, сформирует на его выходе сигнал, который через интегрирующую цепь 19 (фиг,2п) и элемент ИЛИ переключит триггер 12 в состояние О , отключая тем выход генератора 1 от .счетного входа сче чика 20, и триггер 27 - в состояние , обеспечиваяс помощью триггеров 28 и 30 и интегрирующей цепи 29 формирование на выходе три гера 30 сигнала съема кода. На выходе элемента ИЛИ 17 в этот момент формируется сигнал кода 11... 11 (фиг.2с), кбторый возбуждает один из входов элемента ИСКЛЮЧАЮЩЕЕ ИЛИ втброй вход которого возбуждается выходом триггера 13, на котором си нал эквивалентен сигналу кода 11... 11, так как триггер 13 включа ется сигна.лоМ-Ц-го разряда, снимаемым с распределителя 2 импульсов, а выключается сигналом нулевого (з кового) разряда, также снимаемым с распределителя 2 (фиг.2р). При исправном состоянии всех: ц элементов группы 16,-16f, элементов И сигнал на.выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ будет равен нулю (фиг.2т, первое измерение). По окончании сигнала съема кода, снимаемого с выхода триггера -30, триггер 39 вновь форми рует сигнал (фиг.2к,н), который проходит через элемент И 25 (фиг.2ф и через элемент ИЛИ 5 (фиг.2у) на счетный вход счетчика 20, вызывая при этом его переполнение (фиг.2х) Формируемый на выходе переноса счет чика 20 сигнал переноса поступает на обнуление триггера 35 через элемент ИЛИ 21, триггера 36 через элемент И 37 и триггера 38. Триг гер 35 при переключении триггера 1 в состояние i переключается этим триггером также в состояние (фиг.2о,ш). При появлении на выходе счетчика 20 сигнала переполн ния триггер 35 переключается в состояние О, возбуждая при этом си хронизирующий вход триггера 36. Однако переключение этого триггера в как он удерживается сигналом переноса со счетчика 20 (этот сигнал поступает на вход обнуления -триггера 36 через элемент И 37) в состоянииНа следующем измерении временного интервала (фиг.2а) процесс преобразования протекает аналогично описанному до момента сравнения сигналов на элементе ИСКЛОЧАЮЩЕЕ ИЛИ 14, поступающих с выходов элемента ИЛИ 17 (фиг.2с) и выхода триггера 17 (фиг.2р). При пропадании сигнала на выходе одного из элементов И группы (j на выходе элемента ИСКЛЮЧММЦЕЕ ИЛИ 14 сформируется сигнал, эквивалентный по времени пропавшему сигналу (фиг.2у), который, пройдя через элемент И 31, переключит триггер 35 в состояние О. В свою очередь, триггер 35 переключит в состоя.ние 1 триггер 36 (.фиг. 2э) . Если пропадание сигнала на выходе одного из элементов И группы lb -16f| носит случайный характер типа сбоя, то на следующем измерении временного интервала переключение триггера 35 из состояния 1 в состояние О в момент появления сигнала переноса на счеТчике 20 вызовет переключение триггера 36 из состояния в состояние О. Триггер 38, синхронизирующий вход которого возбуждается выходом триггера 36, при переключении последнего будет оставаться в состоянии О, в котором его удерживает сигнал переноса. Если пропадание сигнала на выходе одного из элементов И группы , носит постоянный .характер, т.е. вызвано неисправностью типа рбрыв в этом элементе, сигнал на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 на двух Смежных измерениях не будет равен нулю (фиг.2т, четвертое и пятое измерение). На четвертом измерении сигнал с выхода элемента ИСКЛЮЧАКЯЦЕЕ ИЛИ 14, пройдя через элемент И 31, переключит в состояние О Триггер 35, который в свою очередь, переключится в сосНа пятом измерении тояние временного интервала сигнал с выхода элемента ИСКЛЮЧАЮ ЕЕ ИЛИ 14 .переключит в состояние О триггер 35, который установит в состояние О также триггер 36. Переключение триггера 36 вызовет установку в состояние триггера 38, который возбудит шину 44 (фиг.2ю) сигнала контроля и снимет возбуждение с входов элементов И 11 и 34, прекращая поступление на преобразователь си1- налов временного интервала с шины 42 и выдачу кодовой информации на ши-. ну 43. Достоверность выдаваемой преобразователем время-код информации об измеряемом временном интервале существенно зависит от исправного состояния кодовых выходов счетчика преобразователя и элементов И, с помощью которых осуществляется съем кодовой информации со счетчика. Неисправность любого из кодовых выходов счетчика или элемента И младших разрядов приводит к искаже нию информации, резко снижающей точность измерительной системы, в которую встроен преобразователь. Неисправность любого из кодовых выходов, счетчика или элемента И средних и старших разрядов приводит к искажению информации, вызывающей выход из строя измерительной системы. Обнаружение подобных неисправностей требует больших материальных и програ мных затрат в вычислительном устройстве автоматизированной измерительной системы, которая яв-; ляется приемником информации о Bjpeменном интервале, и высокой квалификации оператора системы. В автоматической измерительной системе выявление таких неисправностей практически не выполнимо и может быть обйаружено лишь по конечному результату работы системы, что может привести к большим материальным и временным :потерям. Известные преоб разователи не в состоянии обнаружить появление описанных неисправностей.

Использование предлагаемого.преобразователя обеспечивает по сравнению с известными высокую достоверность работы, что -позволяет существенно повысить эффективность измерительных систем. Применение преоб- разователя позволяет также снизить квалификационные требования к обслуживающему персоналу.

ллп. ..

л-.-- ппп Г1

.-TT-- fL Г-Т Г-Тп

.ni fiп лjri jn

ттпгт--ттл-тт--ттл-гт---тт-гтт|--1тгг1т

- -Л-лЛ- Л Л-Л::- П -П.- -П-Л--гг..

.-r-L - r-U-/ L- -Г-Ь-J-L

.-jJL™ rfJ.,jil.:Ju Jtt - f

--П.л-: n ..

.:-TT...

.J..,(.L.

II,,:I,J1

wun-Tfimi--infgff----1НГЯГ---втпг В1ЙПГ таив ТУИ пнгиг

л

.

ти1п;

J.

t

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь временных интервалов в код | 1978 |

|

SU691804A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь "время-код | 1980 |

|

SU917173A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-12-30—Публикация

1982-09-03—Подача