Изобретение относится к информационно-управляющим комплексам и может быть использовано для кодирования и спорадической передачи информации о текущем состоянии датчиков дискретных сигналов, отображающих состояние (положение) двухпозиционных исполнительных механизмов (датчиков), цепей охранной и пожарной сигнализации, а также для передачи информации о последовательности изменений указанных сигналов. Данные о временной последовательности изменения сигналов от датчиков позволяют использовать предложенное устройство для анализа нештатной (аварийной) ситуации. Информационное сообщение представляется последовательным кодом, благодаря чему для передачи данных внешнему устройству могут использоваться телемеханические каналы связи.

Наиболее близким к предлагаемому является устройство для спорадической передачи телесигнализации по авторскому свидетельству №1260996 (М.Л.Портнов и др., бюллетень №36, 1986 г.), которое содержит источник питания, блок датчиков сигналов, состоящий из индивидуальных узлов для каждого из «n» датчиков, первый, второй и третий коммутаторы, преобразователь параллельного кода в последовательный, состоящий из мультиплексора и первого счетчика, генератор тактовых импульсов, первый распределитель, регистр - ОЗУ, компаратор последовательных кодов, первый, второй и третий триггеры, первый и второй формирователи импульсов, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы ИЛИ, первый и второй элементы И, элемент задержки.

Устройство-прототип обеспечивает динамический контроль работоспособности общих узлов путем проведения двух тестовых режимов, при которых обеспечивается получение, соответственно, сигналов «1» и «0» на всех индивидуальных выходах блока датчиков. В режиме ввода и обработки реальных и тестовых сигналов используются одни и те же элементы устройства, благодаря чему достигается диагностика работоспособности общих для всех сигналов узлов. Для этого ненулевой («U») выход источника питания подключен к первым входам первого и второго коммутаторов, а нулевой («0») выход - ко второму входу второго коммутатора, объединенные вторые выходы узлов блока датчиков сигналов соединены с выходом первого и вторым выходом второго коммутаторов, а первые индивидуальные выходы узлов блока датчиков сигналов подключены к информационным входам мультиплексора, у которого адресные входы соединены с соответствующими основными выходами первого счетчика и регистра - ОЗУ, а выход - с первым выходом второго коммутатора и входом третьего коммутатора, у которого выход соединен с первым входом компаратора последовательных кодов, подключенного вторым входом к первому выходу первого триггера, который является выходом «данные» устройства, пятый выход первого распределителя соединен со входом элемента задержки.

В устройстве-прототипе повышение достоверности данных обеспечивается проведением динамического контроля работоспособности общих узлов.

Недостатком устройства-прототипа является отсутствие диагностики исправности индивидуальных цепей кодирования и связи с датчиками и фиксации кратковременных сигналов от датчиков и временной последовательности их изменений, что не позволяет использовать устройство-прототип для регистрации нештатной (аварийной) ситуации.

Сущность и цель изобретения - расширение функциональных возможностей устройства за счет диагностики работоспособности индивидуальных цепей связи с датчиками, а также реакции на кратковременные изменения сигналов от датчиков и фиксация их временной последовательности.

Для реализации контроля работоспособности индивидуальных улов совмещаются процедуры ввода и кодирования, для чего в индивидуальные узлы блока датчиков сигналов вводится дополнительный первый диод, включенный последовательно с выходным элементом (контактом) датчика, причем параллельно указанной цепи из датчика и первого дополнительного диода включена вторая последовательная цепь из второго диода и опорного элемента - стабилитрона. Направление включения диодов в первой и второй цепи противоположно. Опрос состояния датчиков, совмещенный с процедурами кодирования, проводится в два этапа. На первом этапе опроса и кодирования поочередно для каждого датчика формируется сигнал, который проходит через цепь, включающую первый диод и выходной элемент (контакт) датчика. Кодовый сигнал, отображающий зафиксированное текущее (мгновенное) состояние датчика, заносится в регистр - оперативное запоминающее устройство (ОЗУ). Если контакт датчика замкнут, на первом этапе формируется сигнал «1», в противном случае - сигнал «0». После завершения первого этапа опроса и кодирования текущих состояний всех датчиков проводится второй этап. На втором этапе поочередно для каждого датчика формируется сигнал, который проходит по цепи из второго диода и стабилитрона узла датчика сигнала, причем уровень сигнала опроса для каждого датчика зависит от сигнала, зафиксированного на первом этапе опроса состояния этого датчика. Если на первом этапе был зафиксирован сигнал «1», соответствующий замкнутому состоянию контакта (выходного элемента) датчика, на втором этапе формируется сигнал относительно низкого уровня с тем, чтобы определить отсутствие короткого замыкания цепи связи датчика с соответствующим входом кодера. Если цепь связи замкнута, т.е. оказывается зашунтированным пороговый элемент - первый стабилитрон, сигнал относительно низкого уровня оказывается выше порога чувствительности кодера. В результате, узел ввода и кодирования сигнала и на проводимом втором этапе зафиксирует поступление от узла датчика сигнала «1». Полученная на двух этапах опроса и кодирования состояния соответствующего датчика комбинация сигналов «11» будет расшифрована как неисправность - короткое замыкание цепи связи кодера с опрашиваемым датчиком. При отсутствии указанной неисправности на двух этапах опроса и кодирования будет сформирована комбинация сигналов «10», которая будет расшифрована приемником как замкнутое состояние датчика и отсутствие неисправности цепи связи с ним.

Если на первом этапе опроса и кодирования от датчика получен сигнал «0», на втором этапе проводится контроль обрыва цепи связи этого датчика с кодером. Для этого уровень сигнала опроса, который поступает на второй диод и первый стабилитрон, повышается на величину, большую значения порога срабатывания стабилитрона. Если цепь связи опрашиваемого датчика с кодером не разорвана, уровень сигнала опроса оказывается больше порогового сигнала, а кодером будет зафиксирован сигнал «1». В результате на двух этапах опроса и кодирования соответствующего датчика будет сформирована пара сигналов «01», которая расшифровывается приемником как разомкнутое состояние датчика и отсутствие обрыва цепи связи с ним. Если же цепь связи кодера с опрашиваемым датчиком разорвана, на двух этапах кодирования формируется пара сигналов «00», которая интерпретируется приемником как неисправность - обрыв цепи связи с датчиком.

Сформированные на двух этапах опроса и кодирования состояния каждого датчика пары сигналов: «10» или «01» - при отсутствии неисправности, «11» или «00» - при обнаружении неисправности общей или индивидуальной цепи, заносятся в соответствующие ячейки регистра - ОЗУ. Информация из регистра - ОЗУ после выдачи устройством сигнала «запрос» и получения сигнала «передача» подается на выход «данные» устройства в сопровождении сигналов «такты» и «вывод данных».

При реализации двух этапов опроса и кодирования используются одни и те же узлы устройства, причем для всех общих и индивидуальных цепей создаются условия, при которых должны быть сформированы сигналы разного уровня («1» и «0»), что максимально повышает глубину диагностики работоспособности элементов устройства.

Для реакции на кратковременные входные сигналы в предложенном устройстве формируется два типа данных: «данные 1» - информация о текущих значениях сигналов от датчиков, «данные 2» - информация, включающая данные об изменении состояния датчиков и о временной последовательности указанных изменений. «Данные 2» сопровождаются метками времени, позволяющими идентифицировать во внешнем устройстве - приемнике информации, реальное время «событий» - моменты изменения состояния датчиков. Для идентификации типа сформированных данных устройство передает во внешнее устройство два сигнала запроса - «запрос 1» или «запрос 2». Данные поступают на выход устройства в соответствии с полученным от внешнего устройства сигналом разрешения передачи - «передача 1» или «передача 2».

Для обеспечения диагностики индивидуальных узлов в состав устройства, в отличие от прототипа, вводится второй распределитель, восьмой и девятый элементы ИЛИ, первый и второй элементы И-НЕ, элемент ИЛИ-НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ.

Для реализации цели изобретения в части реакции на кратковременные сигналы в состав устройства вводится блок формирования данных об изменениях сигналов от датчиков, сопровождаемых метками времени. Блок формирования данных включает второй, третий, четвертый, пятый и шестой счетчики, четвертый и пятый коммутаторы, компаратор параллельных кодов, третий распределитель, четвертый и пятый триггеры, первый, второй, третий, четвертый, пятый и шестой элементы НЕ, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И, первый и второй дешифраторы, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый и шестнадцатый элементы ИЛИ, второй регистр - ОЗУ, регистр - преобразователь параллельного кода в последовательный.

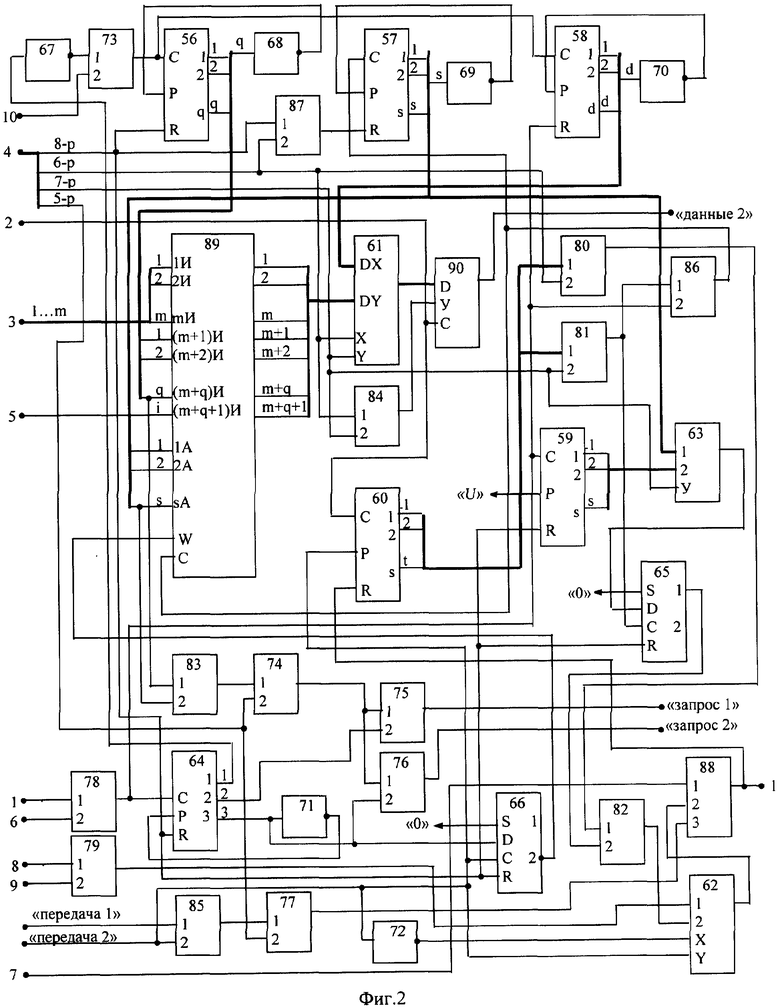

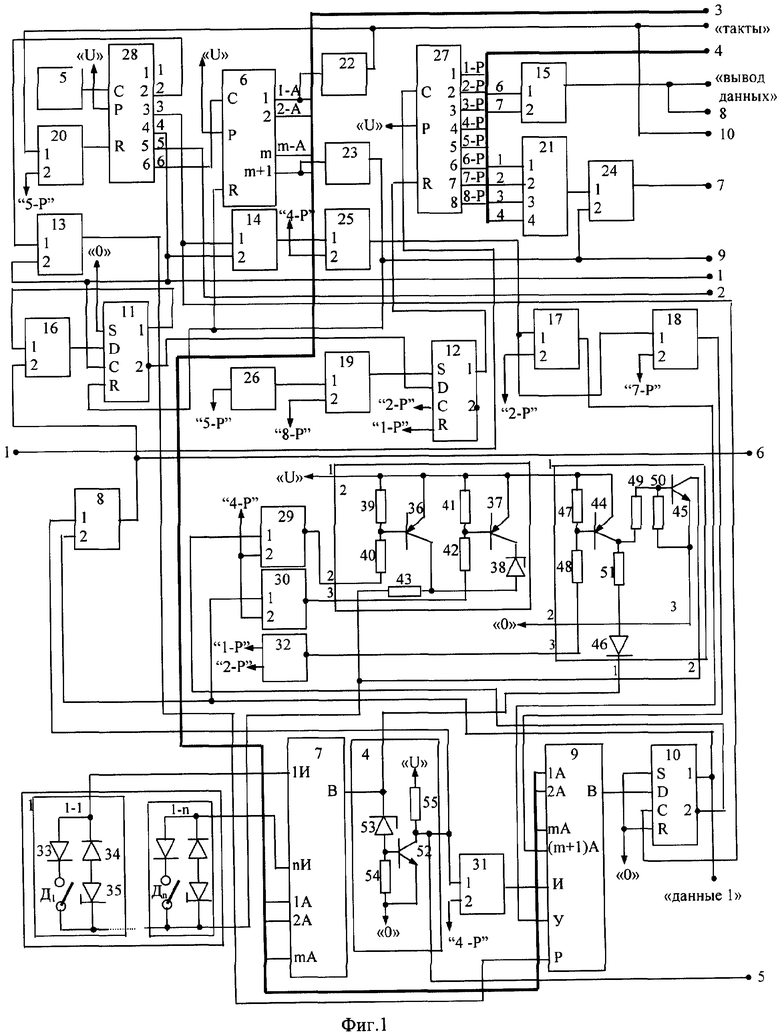

На фиг.1 приведена схема блока ввода, кодирования сигналов от датчиков дискретных сигналов, используемого для формирования и передачи данных о текущих значениях сигналов. На фиг.2 приведена схема блока, обеспечивающего фиксацию кратковременных сигналов от датчиков и передачу зафиксированной информации об изменениях сигналов от датчиков, сопровождаемых метками времени, отображающих временную последовательность изменений сигналов. На фиг.3 приведены соединения между блоками устройства, показанными на фиг.1 и 2, а также сигналы, передаваемые и получаемые от внешнего устройства - приемника информации.

В предложенное устройство, как и в прототип, входит (фиг.1) блок ввода и кодирования сигналов от датчиков, в состав которого включены блок 1 датчиков, который по числу «n» датчиков включает индивидуальные узлы 1-1...1-n, первый 2, второй 3 и третий 4 коммутаторы, генератор 5, преобразователь параллельного кода в последовательный, состоящий из первого счетчика 6 и мультиплексора 7, у которого адресные входы 1А...mA соединены с соответствующими основными выходами первого счетчика, а индивидуальные информационные входы 1И...nИ - с соответствующими индивидуальными выходами 1-1...1-n узлов блока 1, причем объединенные вторые выходы всех узлов соединены с выходом первого и вторым выходом второго коммутаторов. В устройство-прототип и предлагаемое устройство включены также компаратор последовательных кодов 8, регистр - ОЗУ 9, у которого основные адресные входы соединены с соответствующими входами мультиплексора, первый 10, второй 11 и третий 12 триггеры, первый 13, второй 14, третий 15, четвертый 16, пятый 17, шестой 18, седьмой 19 элементы ИЛИ, а также дополнительно введенные восьмой 20 и девятый 21 элементы ИЛИ, первый 22 и второй 23 формирователи импульсов, первый 24 и второй 25 элементы И, элемент 26 задержки, первый 27 и (дополнительно включенный) второй 28 распределители, дополнительно введенные первый 29 и второй 30 элементы И-НЕ, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 31, ИЛИ-НЕ 32.

Первый (прямой) выход триггера 10 является выходом «данные 1» устройства, выход ИЛИ 15 - выходом «вывод данных» устройства, а выход формирователя 22 - выходом «такты» устройства.

В состав блока 1 датчиков входят индивидуальные для датчиков Д1...Дn узлы 1-1...1-n. Каждый узел включает первый 33 и второй 34 диоды, пороговый элемент - первый стабилитрон 35, причем объединенные анод первого и катод второго диодов образуют первые индивидуальные выходы узлов 1-1...1-n, катод первого диода присоединен к одному выводу датчика, соединенные вместе катоды первых стабилитронов и вторые выходы датчиков всех узлов 1-1...1-n образуют второй выход блока 1, который присоединен к выходу первого и второму выходу второго коммутаторов.

Первый 2 коммутатор включает первый 36 и второй 37 транзисторы, второй стабилитрон 38, катод которого соединен с коллектором 37, а анод объединен с коллектором транзистора 36. Первый 39, второй 40, третий 41 и четвертый 42 резисторы задают рабочий режим и входной ток транзисторов 36 и 37, а пятый резистор 43 - уровень рабочего сигнала на выходе коммутатора 2. Один вывод резисторов 39, 41 соединен с эмиттерами транзисторов 36 и 37 и образует первый вход коммутатора, который подключен к ненулевому («U») выводу источника питания. Один вывод резисторов 40 и 42 подключен, соответственно, к базам транзисторов 36 и 37, а вторые выводы 40 и 42 образуют, соответственно, второй и третий входы коммутатора и подключены к выходам элементов И-НЕ 29 и 30, соответственно.

Второй 3 коммутатор включает третий 44 и четвертый 45 транзисторы, третий диод 46, шестой 47, седьмой 48, восьмой 49, девятый 50 резисторы, которые задают рабочий режим и входной ток транзисторов 44 и 45 и подключены аналогично соответствующим резисторам первого коммутатора, а десятый 51 резистор вместе с диодом 46 определяет уровень сигнала на первом выходе коммутатора 3. Эмиттер транзистора 44 образует первый вход коммутатора и подключен к выходу «U» источника питания, эмиттер транзистора 45 образует второй вход коммутатора и подключен к выходу «0» источника питания, а коллектор транзистора 45 образует второй выход второго коммутатора, объединенный с выходом первого коммутатора.

Третий 4 коммутатор включает пятый 52 транзистор, третий 53 стабилитрон, одиннадцатый 54 и двенадцатый 55 резисторы. Резистор 54 задает рабочий режим транзистора 52 и подключен одним выводом к базе 52, а вторым - к нулевому («0») выводу источника питания. Один вывод 55 соединен с коллектором 52 и образует выход третьего коммутатора, а второй вывод 55 подключен к ненулевому выводу («U») источника питания. Катод стабилитрона 53 образует вход третьего коммутатора, который соединен с выходом мультиплексора 7 и первым выходом коммутатора 2.

В состав устройства, в отличие от прототипа, включен показанный на фиг.2 блок фиксации кратковременных дискретных сигналов и передачи временной последовательности их изменений. В состав блока включены второй 56, третий 57, четвертый 58, пятый 59 и шестой 60 счетчики, четвертый 61 и пятый 62 коммутаторы, компаратор параллельных кодов 63, третий распределитель 64, четвертый 65 и пятый 66 триггеры, первый 67, второй 68, третий 69, четвертый 70, пятый 71 и шестой 72 элементы НЕ, третий 73, четвертый 74, пятый 75, шестой 76, седьмой 77, восьмой 78 и девятый 79 элементы И, первый 80 и второй 81 дешифраторы, десятый 82, одиннадцатый 83, двенадцатый 84, тринадцатый 85, четырнадцатый 86, пятнадцатый 87 и шестнадцатый 88 элементы ИЛИ, второй регистр - ОЗУ 89, регистр - преобразователь параллельного кода в последовательный 90.

Выходы «4» и «5» распределителя 28 соединены, соответственно, с первым входом И 78 и третьим входом регистра 90, выходы 1...m счетчика 6 - со входами регистра - ОЗУ 89; выходы 5-Р, 6-Р, 7-Р и 8-Р распределителя 27 соединены, соответственно, со входами элемента И 74, дешифраторов 80 и 81, счетчика 56; выход коммутатора 4 - с информационным входом (i) регистра - ОЗУ 89, выход компаратора 8 - со вторым входом элемента И 78; выход И 24 - с первым входом ИЛИ 88; выход ИЛИ 15 - с первым входом И 79, а выход формирователя 23 - со вторым входом И 79; выход формирователя 22 - со вторым входом И 73; выход ИЛИ 88 - с первым входом (С) распределителя 27. Входы элемента ИЛИ 85 соединены с выходами внешнего устройства "передача 1" и "передача 2"; выходы триггера 10 и регистра 90 - со входами внешнего устройства "данные 1" и "данные 2", соответственно; выходы элементов И 75, И 76 - с выходами устройства "запрос 1" и "запрос 2", соответственно; формирователь 22 образует выходные сигналы "такты" устройства; выход элемента ИЛИ 15 - сигналы "вывод данных" устройства.

Мультиплексор 7 преобразователя параллельного кода (состояний датчиков) в последовательный может быть, например, реализован на восьмиканальных микросхемах серии 561КП2. В этом случае число микросхем (M) определяется общим числом датчиков «n» по формуле

где Σ - знак округления до ближайшего большего целого числа. Выходы «В» всех микросхем объединяются. На адресные входы микросхем подаются сигналы от счетчика 6, причем число «m» основных разрядов счетчика определяется по формуле m=Σlog n. Если число датчиков больше восьми, они разделяются на группы по восемь датчиков в каждой группе. Сигналы от трех младших разрядов счетчика соединяются с соответствующими адресными входами мультиплексоров, остальные разряды счетчика преобразуются в позиционные сигналы и подаются на вход разрешения перехода в рабочее состояние мультиплексора соответствующей группы датчиков. На фигуре условно показан один мультиплексор, вход сигнала разрешения не показан.

Счетчики 6, 56, 57, 58, 59, 60 могут быть, например, реализованы на микросхемах 561 ИЕ10. На первый тактовый (С) вход микросхемы подаются импульсные сигналы. Счетчик переключается в смежную кодовую позицию при переходе входного сигнала из «0» в «1», а возвращается в начальное положение (нулевую кодовую позицию) при подаче сигнала «1» на третий (R) вход. Второй вход разрешения работы (Р) счетчика используется для блокировки чувствительности к входным тактовым сигналам. Если на указанный вход подается сигнал нулевого уровня («0»), счетчик не изменяет состояние при поступлении очередных сигналов на первый вход.

Регистр - ОЗУ 9 реализует последовательный ввод и последовательный вывод сигналов и может быть, например, выполнен на одной микросхеме оперативного запоминающего устройства 561 РУ2, если число датчиков «n» не превышает 256. На основные адресные входы ОЗУ 1А...mA подаются сигналы с основных выходов счетчика 6, а на дополнительный адресный вход (m+1)A - сигнал с выхода ИЛИ 18. В ячейки памяти с номерами от 0 до (2m-1) заносится последовательный код, полученный на первом этапе опроса и кодирования сигналов от датчиков, а в ячейки памяти с номерами от 2m до (2m+1-1) - последовательный код, полученный на втором этапе опроса и кодирования сигналов от датчиков. Код подается на информационный (И) вход регистра - ОЗУ, сигнал задания режима записи-считывания информации - на управляющий (У) вход с выхода ИЛИ 17 (режим записи реализуется при подаче на вход У сигнала «1»), а сигнал перевода регистра - ОЗУ в активное состояние - при подаче сигнала на вход разрешения (Р). В качестве управляющего используется вход W/R микросхемы 561 РУ2, а в качестве разрешающего - вход СЕ указанной микросхемы.

Регистр - ОЗУ 89 может быть, например, реализован на микросхемах КР 537 РУ17, причем число микросхем определяется требуемым числом адресных и информационных входов. Для предлагаемого устройства число информационных входов регистра - ОЗУ на единицу больше суммы числа «m» основных разрядов счетчика 6 и числа «q» разрядов счетчика 56, т.е. равно (m+q+1). Число «s» адресных сигналов ОЗУ равно числу разрядов счетчика 57. Регистр - ОЗУ 89 работает в режиме записи и считывания параллельного кода. Данные записываются по сигналу «1» на входе «W» при подаче рабочего сигнала на синхронизирующий (С) вход.

Распределители 27, 28 и 64 могут быть реализованы, например, на микросхеме 561 ИЕ9, сочетающей двоичный счетчик на восемь кодовых позиций и дешифратор. При подаче сигнала «0» на второй вход разрешения (Р) распределитель теряет чувствительность к тактовым сигналам.

Триггеры 10, 11, 12, 65, 66 могут быть реализованы, например, на микросхемах 561 ТМ2. Триггеры могут управляться асинхронно - сигналами, подаваемыми на первый вход установки состояния «1» (S) или четвертый вход установки состояния «0» (R), а также синхронно - при подаче на второй вход информационного сигнала (D), причем триггер переходит в состояние, соответствующее сигналу на входе D, по положительному перепаду сигнала на третьем тактовом входе (С).

Формирователи импульсов 22, 23 могут быть реализованы, например, на основе триггера, прямой выход которого через интегрирующую RC цепочку подключается к R входу. Формирователь переводится в рабочее состояние по перепаду уровня сигнала на С входе триггера, если в данный момент времени на D вход подан сигнал «1». Длительность формируемого импульса определяется постоянной времени интегрирующей RC цепочки.

Компаратор последовательных кодов 8 может быть реализован, например, на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ, на входы которого подаются сравниваемые сигналы последовательных кодов. На выходе компаратора образуется сигнал «1» при несовпадении входных сигналов.

Элемент задержки 24 может быть реализован, например, на интегрирующей RC цепочке.

Коммутаторы 61, 62 могут быть реализованы, например, на микросхемах 561 ЛС2. При подаче сигнала «1» на управляющий вход «X» или «У» на выход проходят сигналы, соответственно, с информационных входов «X» (1 - для коммутатора 62) или «У» (2 - для коммутатора 62). Число микросхем для реализации коммутатора 61 определяется по большему из двух чисел - (m+q+1) и «s».

Компаратор параллельных кодов 63 может быть реализован, например, на микросхемах 561 ЛП2. Число микросхем определяется числом сравниваемых разрядов от счетчиков 57 и 59. При равенстве кодов и подаче сигнала «1» на вход управления (У) на выходе компаратора образуется сигнал «1».

Дешифраторы 81 и 82 могут быть, например, реализованы на сочетании логических схем И, НЕ. При подаче на входы элемента И определенного сочетания прямых и инверсных (сформированных элементами НЕ) сигналов от счетчика 60 на все входы элемента И оказываются поданными сигналы «1», что приводит к появлению на его выходе сигнала «1». Для синхронизации работы дешифратора используется сигнал, подаваемый на его второй вход, при этом выходной сигнал «1» образуется синхронно с подачей сигнала на указанный вход дешифратора. Указанная структура дешифраторов позволяет выделить моменты времени, когда на вход счетчика 60 подано требуемое число тактовых импульсов.

Остальные элементы устройства реализуются, например, на стандартных логических микросхемах серии 561, работа которых не требует пояснений.

На фиг.1 и 2 приведен пример реализации предложенного устройства на отдельных интегральных схемах. Функции показанных на фигуре элементов могут частично выполняться программно с помощью элементов, входящих в однокристальную микроЭВМ, например, типа АТ89С52.

Рассмотрим работу предложенного устройства.

Процедуры ввода, кодирования, обработки и передачи информации, отражающей текущие значения сигналов от датчиков (фиг.1), разделяются на несколько этапов. Каждому этапу ставится в соответствие сигнал «1» на одном из выходов 1-Р...8-Р распределителя 27. Распределитель 27 переводится в очередную позицию (а устройство - на очередной этап работы) сигналом, поступающим на его первый (С) вход. Этапы разделяются на такты, которые задаются генератором 5 и счетчиком 6. Счетчик 6 переключается из одной кодовой позиции в смежную по фронту сигнала на первом (С) входе - при появлении сигнала «1» на выходе «6» второго распределителя 28. Сигнал «1» появляется на выходе «6» второго распределителя при поступлении шести тактовых сигналов на первый (С) вход 28 от генератора 5. Одновременно с поступлением сигнала на первый вход счетчика 6 изменяется сигнал на его первом выходе. При каждом изменении сигнала на первом выходе 6 на выходе первого формирователя 22 образуется импульсный сигнал, который через ИЛИ 20 подается на R вход 28 и переводит второй распределитель в начальное состояние. Таким образом, с помощью распределителя 28 одна кодовая позиция счетчика 6 - один такт, преобразуется в шесть разделенных во времени микротактов. Число тактов, составляющих один этап работы устройства при вводе и кодировании сигналов от датчиков, определяется числом датчиков «n». После завершения опроса или другого вида обработки информации от всех датчиков сигнал «1» формируется на дополнительном (m+1) выходе счетчика 6. Второй формирователь импульсов 23 фиксирует появление сигнала «1» на выходе (m+1) счетчика и формирует при этом импульсный сигнал, который подается на R вход счетчика 6. Счетчик 6 указанным импульсным сигналом переводится в начальное состояние, а распределитель 27 на этапах 1-Р...4-Р ввода и кодирования сигналов от датчиков переключается в смежную позицию. Сигнал переключения 27 формируется ИЛИ 21, И 24, ИЛИ 88. Описанная работа генератора 5, первого 27 и второго 28 распределителей и счетчика 6 проводится циклически.

При установке сигнала «1» на выходе 1-Р, т.е. на каждом первом этапе работы устройства, контролируется изменение состояния любого датчика. Так как в указанное время сигнал «1» подается на вход ИЛИ-НЕ 32, на его выходе образуется сигнал «0». В результате образуется цепь: выход «U» источника питания - параллельная ветвь из перехода эмиттер-база транзистора 44 и резистора 47 - резистор 48 - выход 32 - выход «0» источника питания. Резистор 47 фиксирует рабочую точку транзистора 44 (препятствует самопроизвольному переходу транзистора в рабочее состояние при изменении в широких пределах температуры окружающего воздуха), а резистор 48 определяет величину рабочего тока во входной цепи 44. Ток во входной цепи 44 вызывает появление тока в выходной цепи 44, который проходит по двум параллельным ветвям. Одна из ветвей включает резистор 51 и разделительный диод 46, а вторая - последовательную цепочку из резистора 49, перехода база-эмиттер транзистора 45 и замыкается на вывод «0» источника питания. Резистор 50, аналогичный резистору 47, фиксирует рабочую точку 45. В результате на второй выход коммутатора 3 и второй (общий) выход блока 1 подается сигнал с уровнем «0». Цепь протекания тока первой ветви транзистора 44 определяется состоянием опрашиваемого в рассматриваемый отрезок времени датчика. Номер опрашиваемого датчика определяется комбинацией кодовых сигналов на адресных входах 1А...mA мультиплексора 7, т.е. текущей кодовой позицией счетчика 6. Так, например, при m=log n и при установке счетчика 6 в начальное состояние выход «В» мультиплексора 7 подключается к первому (1И) информационному входу, а при установке сигналов «1» на всех адресных входах мультиплексора 7 выход «В» присоединяется ко входу nИ, т.е. к первому выходу узла 1-n блока датчиков 1.

Предположим, что контакт (выходной элемент) опрашиваемого в рассматриваемый момент времени датчика Д1 замкнут. Тогда создается цепь: выход 44-51 - 46 - выход «В» 7 - вход 1И мультиплексора 7 - первый выход узла 1-1 - 33 - Д1 - второй выход блока 1 - переход коллектор-эмиттер 45 - выход «0» источника питания. Так как сумма падений напряжения на мультиплексоре 7, диоде 33 и замкнутом контакте датчика Д1 ниже порогового напряжения стабилитрона 53 коммутатора 4, по входной цепи третьего коммутатора 4 ток не проходит. В результате транзистор 52 остается в нерабочем состоянии, а уровень сигнала на его коллекторе оказывается равным «U», т.е. логическому сигналу «1». Таким образом, в рассматриваемом режиме работы устройства при замкнутом контакте датчика сигнал на выходе коммутатора 4 равен «1». Если же контакт датчика разомкнут, описанная выше цепь тока не создается. Ток транзистора 44 замыкается через резистор 51, диод 46, стабилитрон 53, переход база-эмиттер транзистора 52 на выход «0» источника питания (отметим, что резистором 54 фиксируется рабочая точка транзистора 52). В результате транзистор 52 переводится в рабочее состояние, по его выходной цепи проходит ток, а уровень выходного сигнала коммутатора 4 становится равным «0» (падением напряжения на транзисторе 52 пренебрегаем). Аналогично описанному определяются сигналы от всех датчиков. Выходной сигнал коммутатора 4 подается на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 31, на второй вход которого в рассматриваемом случае подан сигнал «0» с выхода 4-Р распределителя 27. Элемент 31 на этапе 1-Р выполняет функцию повторителя сигнала, поступившего на его первый вход. Выходной сигнал 31 подается на информационный (И) вход регистра - ОЗУ 9. На этапе 1-Р на вход управления (У) 9 сигнал «1» не подан, поэтому регистр - ОЗУ переведен в режим считывания ранее записанной информации. Так как сигналы, подаваемые на адресные входы мультиплексора 7 и регистра - ОЗУ 9, идентичны, на выходы коммутатора 4 и регистра - ОЗУ 9 подаются сигналы, соответствующие одному и тому же датчику. Сигнал на выходе 4 отражает текущее значение сигнала от датчика, а на выходе 9 - значение сигнала, записанного в него ранее. Выходной сигнал регистра - ОЗУ 9 фиксируется триггером 10, причем в триггер 10 сигнал от регистра - ОЗУ 9 переписывается на третьем микротакте (при формировании сигнала «1» на третьем выходе распределителя 28), т.е. со сдвигом на один микротакт относительно момента перевода регистра - ОЗУ 9 в рабочее состояние сигналом на выходе ИЛИ 13. Важно, что момент перевода регистра - ОЗУ 9 в рабочее состояние также сдвинут на один микротакт относительно изменения кодовой позиции счетчика 6, т.е. относительно момента подключения ко входу мультиплексора сигнала от вновь выбранного (опрашиваемого) датчика. Видно, что использование разделенных во времени микротактов позволяет исключить влияние переходных процессов на работу устройства.

Если текущее состояние опрашиваемого датчика изменилось относительно зафиксированного ранее и занесенного в регистр - ОЗУ 9, на входы компаратора 8 поступают разные по уровню сигналы, а сигнал на выходе 8 становится равным «1», в противном случае выходной сигнал компаратора оказывается равным «0». Факт изменения сигнала от датчика условно назовем «событием» - основанием для последующей передачи информации. Сигнал компаратора, отображающий результат сравнения «старого» и «нового» значений сигналов от датчика, фиксируется триггером 11 по сигналу «1» на его третьем (С) входе при появлении сигнала «1» на четвертом выходе распределителя 28, т.е. со сдвигом на один микротакт относительно момента фиксации сигнала от регистра 9 триггером 10 и подачи сигнала на второй (D) вход триггера 11. После перевода триггера 11 в состояние «1» сигнал с его первого (прямого) выхода через ИЛИ 16 подается на второй (D) вход, блокируя возврат триггера 11 в состояние «0» независимо от соотношения текущих и ранее занесенных в регистр сигналов, отображающих состояние других датчиков. Таким образом, триггер 11 после однократного перевода в состояние «1», т.е. после фиксации хотя бы одного «события», сохраняет установленное состояние до окончания этапа сравнения сигналов от всех датчиков. Этап завершается при образовании импульсного сигнала формирователем 23, который через И 24, ИЛИ 88 подается на первый (С) вход распределителя 27 и на R вход счетчика 6. Распределитель 27 переходит в очередное состояние - сигнал «1» образуется на его выходе 2-Р. Если к этому моменту не зафиксировано ни одно «событие», триггер 11 остается в состоянии «0», а на его втором (инверсном) выходе образуется сигнал «1». Сигнал от 11 подается на второй (D) вход триггера 12. По фронту сигнала 2-Р, который подается на третий (С) вход, триггер 12 переводится в состояние «1», в результате чего распределитель 27 сигналом по третьему (R) входу возвращается в начальное состояние. Устройство возвращается на этап сравнения текущих и ранее занесенных в регистр - ОЗУ 9 сигналов от датчиков. При переходе на каждый новый этап работы по сигналу от формирователя 23, поступающему на четвертый (R) вход, триггер 11 возвращается в начальное состояние. После возврата распределителя 27 в начальное состояние сигналом «1» с выхода 1-Р триггер 12 возвращается (по входу R) в начальное состояние.

Если к моменту формирования сигнала «1» на выходе 2-Р триггер 11 переведен в состояние «1», на его втором выходе образован сигнал «0», триггер 12 не переводится в состояние «1», а распределитель 27 не возвращается в начальное состояние, устройство переходит на этап 2-Р.

На этапе 2-Р проводится запись текущих сигналов от датчиков в регистр - ОЗУ 9. На вход ИЛИ-НЕ 32 подается сигнал «1», поэтому сигналы, формируемые на выходах коммутатора 3, идентичны формировавшимся на этапе 1-Р. Сигнал «1» подается на вход ИЛИ 17, поэтому на вход управления (У) регистра - ОЗУ 9 подан сигнал «1» с выхода ИЛИ 17. Этим сигналом регистр - ОЗУ 9 переводится в режим записи информации от всех датчиков, начиная с первого, так как счетчик 6 к началу этапа 2-Р установлен в начальное состояние. На втором микротакте каждого такта по сигналу «1» с выхода ИЛИ 13, поданному на вход разрешения (Р) регистра - ОЗУ 9, сигнал от коммутатора 4, повторенный на выходе ИСКЛЮЧАЮЩЕГО ИЛИ 31 и поданный на информационный (И) вход 9, записывается в выбранную ячейку регистра - ОЗУ 9. Номер ячейки определяется адресными сигналами на входах 1А...mA мультиплексора 7 и регистра - ОЗУ 9. К моменту окончания этапа 2-Р в регистр - ОЗУ 9 оказываются записанными сигналы, соответствующие текущим состояниям всех «n» датчиков.

На очередном этапе 3-Р устанавливается тайм-аут, который отделяет моменты начальной и повторной записи данных в регистр - ОЗУ 9 и уменьшает вероятность искажения информации помехами в цепях связи датчиков с кодером, реализованным на счетчике 6, мультиплексоре 7, коммутаторах 2, 3 и 4, ИСКЛЮЧАЮЩЕМ ИЛИ 31.

Этап 4-Р выделяется для диагностики работоспособности общих и индивидуальных узлов устройства и отсутствия повреждений цепей связи датчиков блока 1 с кодером. На этапе 4-Р сигнал «1» на входы ИЛИ-НЕ 32 не подается, поэтому сигнал на его выходе равен «1», а коммутатор 3 остается в нерабочем состоянии. В рабочее состояние переводится коммутатор 2. Сигнал, который формируется коммутатором 2, определяется для каждого датчика в отдельности в зависимости от сигнала, ранее записанного в регистр - ОЗУ 9. На втором микротакте на вход разрешения (Р) регистра - ОЗУ 9 с выхода ИЛИ 13 подается рабочий сигнал, причем на указанном микротакте на вход управления (У) подается сигнал «0» с выхода ИЛИ 17, а на адресный вход (m+1)А подается сигнал "0" с выхода ИЛИ 18. В результате регистр - ОЗУ 9 оказывается в режиме считывания информации из ячеек, в которые ранее, на этапе 2-Р, была занесена информация. Считываемые из 9 сигналы подаются на второй (D) вход триггера, а на третьих микротактах переносятся в триггер 10 по сигналу «1» на третьем входе. Как было показано ранее, на этапе 2-Р в регистр - ОЗУ 9 записывается сигнал «1», если контакт опрашиваемого датчика замкнут. Для диагностики работоспособности элементов схемы и цепей связи датчика с кодером на этапе 4-Р для таких датчиков проверяется отсутствие короткого замыкания цепи связи датчика с кодером. В рассматриваемом случае сигнал «1» с первого выхода триггера 10 поступает на первый вход И-НЕ 30. Так как и на второй вход И-НЕ 30 подан сигнал «1», на выходе элемента образуется сигнал «0». Замыкается цепь: выход «U» источника питания - параллельные ветви из резистора 41 и перехода эмиттер-база транзистора 37 - резистор 42 - вход 3 коммутатора 2 - выход И-НЕ 30 - выход «0» источника питания. Как было указано ранее, резистор 41 фиксирует рабочую точку транзистора 37, а резистор 42 определяет рабочий ток транзистора 37. Ток во входной цепи 37 приводит к появлению тока в выходной цепи: выход «U» источника питания - переход эмиттер-коллектор 37 - стабилитрон 38 - резистор 43 - второй (общий) выход блока 1 - узел 1-1...1-n, соответствующий номеру опрашиваемого датчика, - стабилитрон 35 - диод 34 - информационный вход мультиплексора 7, соответствующий номеру опрашиваемого датчика, - выход «В» мультиплексора 7 - стабилитрон 53 коммутатора 4 - параллельные ветви из резистора 54 и перехода база-эмиттер транзистора 52 - выход «0» источника питания. Если из рассмотренной цепи не исключен стабилитрон 35 (цепь связи датчика с кодером не замкнута), уровень выходного рабочего сигнала коммутатора 2 оказывается меньше порогового уровня для рассмотренной цепи. В результате транзистор 52 коммутатора 4 остается в нерабочем состоянии, ток в выходной цепи 52 отсутствует, уровень сигнала на выходе коммутатора 4 равен «1». Так как на второй вход ИСЛЮЧАЮЩЕГО ИЛИ 31 в рассматриваемом режиме работы подан сигнал «1», элемент 31 выполняет функцию инвертора. В результате для рассмотренного случая сигнал на выходе 31 и информационном входе регистра - ОЗУ 9 равен «0». На четвертом микротакте на разрешающий (Р) вход регистра - ОЗУ 9 подан рабочий сигнал, на вход управления (У) подается сигнал «1» с выхода ИЛИ 17, так как на его вход подан сигнал «1» с выхода И 25, сигнал «1» подан также на адресный вход (m+1)А регистра - ОЗУ 9 с выхода ИЛИ 18. В результате в рассмотренном режиме работы в ячейку 9, соответствующую опрашиваемому датчику, заносится сигнал «0». Следует подчеркнуть, что номер ячейки, в которую повторно заносится информация от датчика, сдвинут на «n» относительно номера ячейки, в которую первоначально заносилась информация от данного датчика. В результате в рассматриваемом случае в указанную пару ячеек регистра - ОЗУ 9 оказывается записанной комбинация сигналов «10».

Если для рассматриваемого случая (первоначальной записи в регистр - ОЗУ сигнала «1») цепь связи опрашиваемого датчика с кодером окажется замкнутой, из рассмотренной цепи протекания выходного тока коммутатора 2 исключается стабилитрон 35. В результате рабочий сигнал коммутатора 2 превысит пороговый уровень для коммутатора 4; транзистор 52 коммутатора 4 будет переведен в рабочее состояние. На выходе коммутатора 4 образуется сигнал «0», который преобразуется в сигнал «1» на выходе 31. В результате в ячейки регистра - ОЗУ 9, выделенные для записи пары сигналов от одного датчика, будет записана комбинация сигналов «11», которая интерпретируется как неисправность (замыкание) цепи связи с датчиком или любая другая эквивалентная неисправность элементов устройства. Важно подчеркнуть, что при проведении диагностики работоспособности элементов устройства и цепей связи датчика с кодером задействовались цепи, которые на этапе 2-Р использовались для первоначальной записи в регистр - ОЗУ 9 сигнала, отображающего текущее состояние датчика, что максимально повышает степень контроля. Итак, если первоначально зафиксировано замкнутое состояние какого-либо датчика, в две ячейки регистра - ОЗУ 9 (выделенные для одного датчика) будет записана пара сигналов «10», если не обнаружена неисправность, и «11» - при обнаружении неисправности.

Рассмотрим работу устройства на этапе 4-Р для случая, когда первоначально зафиксировано разомкнутое состояние датчика, т.е. в соответствующую опрашиваемому датчику ячейку регистра - ОЗУ 9 был записан сигнал «0». В этом случае на этапе 4-Р триггер 10 (при считывании сигнала с соответствующей ячейки регистра - ОЗУ) оказывается в состоянии «0», И-НЕ 30 оказывается в нерабочем состоянии, а на два входа И-НЕ 29 подаются сигналы «1», на выходе элемента образуется сигнал «0». В этом случае, аналогично тому, как это было описано при переводе в рабочее состояние И-НЕ 30, сигналом «0» по второму входу коммутатора 2 переводится в рабочее состояние транзистор 36. Выходной сигнал транзистора 36 не ослабляется введением в выходную цепь стабилитрона 38. В результате создаются условия для диагностики отсутствия разрыва цепи связи датчика с кодером. Сформированный на выходе коммутатора 2 рабочий сигнал достаточен для перевода транзистора 52 коммутатора 4 в рабочее состояние, поэтому при исправных элементах схемы и цепи связи с опрашиваемым датчиком сигнал на выходе коммутатора 4 должен быть равным «0», а на выходе ИСКЛЮЧАЮЩЕГО ИЛИ 31 - равным «1». Как описано выше, данный сигнал заносится в выделенную для опрашиваемого датчика ячейку регистра - ОЗУ 9, причем номер ячейки сдвигается на «n» относительно ячейки, в которую ранее был записан сигнал, отображающий текущее состояние датчика. Таким образом, при фиксации разомкнутого состояния датчика и отсутствии разрыва цепи связи датчика с кодером в выделенные для опрашиваемого датчика две ячейки регистра 9 оказываются записанными сигналы «01». Если цепь связи датчика с кодером разорвана (или обнаружена эквивалентная неисправность элементов схемы), транзистор 52 коммутатора 4 не переводится в рабочее состояние, на его выходе образуется сигнал «1», а на выходе ИСКЛЮЧАЮЩЕГО ИЛИ 31 - сигнал «0», который записывается в соответствующую ячейку регистра - ОЗУ 9. Таким образом, при фиксации разомкнутого состояния датчика и обнаружении неисправности (разрыва) цепи связи датчика с кодером в выделенные для опрашиваемого датчика две ячейки регистра - ОЗУ 9 оказываются записанными сигналы «00». Данная ситуация идентифицируется приемником как неисправность, причем по полученным данным определяется номер датчика и тип неисправности.

Аналогично описанному проводится диагностика и повторная запись в регистр - ОЗУ 9 информации, полученной для всех датчиков, после чего работа устройства на этапе 4-Р завершается, устройство переходит на этап 5-Р.

Этап 5-Р предназначен для формирования и передачи во внешнее управляющее устройство сигнала «запрос 1» или «запрос 2», которым идентифицируется запись в регистр - ОЗУ информации, которая должна быть передана приемнику. Сигнал «запрос» поступает на выход устройства с выхода элемента И 75 или И 76. В ответ на сигнал «запрос 1» или «запрос 2» от внешнего устройства должен, соответственно, поступить сигнал «передача 1» или «передача 2». Элемент задержки 26 фиксирует, что устройство удерживается на этапе 5-Р более установленного времени, т.е. на его входы не поступает сигнал «передача 1» или «передача 2». В этом случае устройство не передает зафиксированные данные, так как на выходе 26 формируется сигнал «1», который через ИЛИ 19 поступает на первый (S) вход триггера 12. Как отмечалось выше, сигналом «1» от триггера 12 распределитель 27 возвращается в начальное состояние. На время от выдачи устройством сигнала «запрос» и до получения ответного сигнала «передача» сигналом «1» с выхода 5-Р распределителя 27 через ИЛИ 20 блокируется работа распределителя 28, а следовательно, и счетчика 6. Если в ответ на сигнал «запрос» от внешнего устройства поступает сигнал «передача 1» или «передача 2», сигнал «1» образуется на выходе ИЛИ 85, который через И 77, ИЛИ 88 подается на первый (С) вход распределителя 27. Устройство переходит на этап 6-Р.

Рассмотрим режим передачи данных для случая, когда на этапе 4-Р зафиксировано только одно «событие», т.е. нет необходимости в передаче данных о временной последовательности нескольких изменений сигналов от датчиков. В рассматриваемом режиме работы устройство (как рассмотрено ниже) формирует сигнал «запрос 1», в ответ на который от внешнего устройства должен поступить сигнал «передача 1». При этом сигнал «1» на входе «передача 2» отсутствует, сигнал «1» образуется на выходе НЕ 72 и на входе «X» коммутатора 62, через который проходит сигнал, поступивший на первый вход 62 с выхода И 79. Сигнал «1» на выходе И 79 образуется на этапах 6-Р и 7-Р (при подаче сигнала «1» на первый вход с выхода ИЛИ 15) синхронно с сигналом от формирователя 23, поступающим на второй вход И 79. В указанном режиме работы сигнал от И 79 управляет работой распределителя 27. Этапы 6-Р и 7-Р в рассмотренном режиме работы выделены для передачи данных, считываемых из регистра - ОЗУ 9. Данные сопровождаются управляющим сигналом «вывод данных», который формируется ИЛИ 15. На этапах 6-Р и 7-Р на управляющий (У) вход регистра - ОЗУ 9 подан сигнал «0», поэтому он переведен в режим считывания данных. На адресный вход (m+1)А регистра - ОЗУ 9 на этапе 6-Р подан сигнал «0», поэтому информация считывается из ячеек, в которые были занесены текущие значения сигналов от датчиков блока 1. Считываемые из регистра - ОЗУ 9 данные на втором микротакте переносятся в триггер 10, с первого (прямого) выхода которого информация подается на выход «данные 1» устройства. Данные сопровождаются сигналами «такты» с выхода формирователя импульсов 22.

После считывания сигналов состояния всех датчиков формируется очередной сигнал на выходе формирователя 23, которым счетчик 6 возвращается в начальное состояние, а распределитель 27 переводится на очередную позицию - 7-Р. Этап 7-Р выделен для вывода информации из ячеек регистра - ОЗУ 9, номера которых сдвинуты на «n» относительно номеров, из которых информация считывалась на этапе 6-Р. Как указывалось выше, в указанной зоне адресов хранится диагностическая информация. На второй вход ИЛИ 18 подан сигнал «1», который ретранслируется на адресный вход (m+1)А регистра - ОЗУ 9, определяя зону считывания информации. В остальном процедуры считывания данных на этапах 6-Р и 7-Р совпадают. После передачи всех диагностических сигналов формируется очередной сигнал на выходе формирователя 23, которым распределитель 27 (через И 79, коммутатор 62, ИЛИ 88) переводится в позицию 8-Р.

Сигнал «1» с выхода 8-Р распределителя 27 через ИЛИ 19 подается на первый (S) вход триггера 12. Сигнал «1» от триггера подается на R вход распределителя 27, приводя устройство в начальное состояние. Сигнал «вывод данных» снимается, завершается цикл ввода, кодирования, диагностики и передачи данных, устройство подготовлено для выполнения процедур очередного цикла работы.

Как видно, процедуры кодирования и передачи данных обеспечивают динамическую диагностику общих для всех датчиков и индивидуальных узлов, причем полученные диагностические данные вводятся в информационное сообщение устройства, что позволяет идентифицировать не только место, но и тип неисправности. При проведении процедур диагностики и рабочих процедур ввода и кодирования информации от датчиков используются одни и те же узлы и элементы, что повышает глубину диагностики.

Рассмотрим работу устройства при формировании данных, отображающих как сигналы от датчиков, так и временную последовательность их изменений.

При изменении состояния любого датчика сигнал «1» образуется на выходе компаратора 8, который на четвертом микротакте «4» распределителя 28 через И 78, ИЛИ 86 подается на тактовый (С) вход счетчика 57. Счетчик 57 подсчитывает число «событий». Одновременно сигнал «1» подается и на тактовый вход (С) распределителя 64, которым фиксируется: отсутствие хотя бы одного «события» (при этом сигнал «1» образуется на выходе 1 распределителя 64), только одно событие (при этом сигнал «1» образуется на выходе 2 распределителя 64), несколько «событий» (при этом сигнал «1» образуется на выходе 3 распределителя 64). После фиксации двух "событий" на вход разрешения (Р) 64 подается сигнал «0» от НЕ 71, распределитель 64 теряет чувствительность к тактовым сигналам и остается в принятом состоянии до поступления сигнала «1» на его R вход. В режиме передачи данных о временной последовательности «событий» переход распределителя 27 на позицию 6-Р задерживается на установленное время контроля.

Максимальное время контроля зависит от числа разрядов (q) счетчика 56, причем отсчет времени начинается от момента фиксации первого «события», когда появляется сигнал «0» на выходе 1 распределителя 64, появляется сигнал «1» на выходе НЕ 67 и деблокируется работа И 73. Выходные сигналы И 73 подаются на первый (С) вход счетчика 56 синхронно с сигналами «такты».

Рассмотрим динамические параметры устройства. Частота импульсов, поступающих на тактовый (С) вход счетчика 6, равна fг/6 (fг - частота сигналов генератора 5), соответствует скорости опроса датчиков. При последовательном опросе «n» датчиков частота поступления сигналов на вход счетчика 56 равна fг/6n, а максимальное время контроля временной последовательности изменений сигналов от датчиков (ТК) равно:

Частота fг/6n определяет минимальный временной сдвиг между двумя смежными «событиями», при котором фиксируется различное время изменений сигналов от датчиков. Важно подчеркнуть, что смежные «события» относятся к изменениям разных или одного и того же датчика. Поэтому установленное минимальное время - дискретность фиксации «событий», определяет и минимальную длительность сигнала от датчика, который фиксируется устройством. Например, для получения дискретности фиксации "событий" не больше 1 мс при n=32 частота сигналов генератора 5 должна быть не меньше 103·6·32 Гц (200 кГц). Число разрядов «q» счетчика 56, временная дискретность ТД и время контроля ТК связываются уравнением:

Для обеспечения ТК=10000 мс при ТД=1 мс необходимо, чтобы q=13. Кроме фиксации завершения установленного времени контроля "событий", счетчик 56 используется для определения временных сдвигов между "событиями", т.е. для формирования первой метки времени. Так как до момента фиксации первого «события» счетчик 56 удерживается в начальном состоянии, метка времени первого «события» условно принимается равной нулю.

Данные каждого «события» заносятся в регистр - ОЗУ 89 по сигналу от ИЛИ 86 (через И 78), поступающему на синхронизирующий (С) вход при фиксации любого «события» компаратором 8. Временной сдвиг «события» относительно первого (первая метка времени) определяется по числу импульсов, поступивших на вход счетчика 56 к моменту фиксации данного «события», и по установленному ТД. Код - состояние счетчика 56, подается на информационные входы (1...q) регистра - ОЗУ 89. Одновременно с занесением в регистр - ОЗУ 89 кода счетчика 56 в него также (по входам 1...m) заносится код с основных разрядов счетчика 6, которым определяется номер датчика. Сигнал, поступающий на шину «i» регистра - ОЗУ 89 с выхода коммутатора 4, определяет состояние датчика в момент фиксации «события». Таким образом, общее число информационных разрядов, характеризующих одно «событие», равно (m+q+1). По данному числу определяется разрядность ячеек памяти регистра - ОЗУ 89. Число ячеек памяти регистра - ОЗУ 89 выбирается с учетом установленного максимального числа «событий», которое определяется числом разрядов счетчика 57. Для примера, показанного на фиг.2, число разрядов счетчика 57 равно «s», а максимально возможное число событий - 2S-1. При достижении указанного числа «событий» чувствительность счетчика 57 к тактовым сигналам, поступающим на его первый (С) вход с выхода ИЛИ 86 (через И 78), блокируется сигналом «0» от НЕ 69, поданным на второй (Р) вход. Сигналы от счетчика 57 подаются на адресные шины регистра - ОЗУ 89.

Как указывалось, код счетчика 56 используется в качестве первой метки времени, по которой во внешнем устройстве может быть восстановлена временная последовательность «событий». Вторая метка времени, используемая для восстановления реального времени «событий», формируется счетчиком 58 и соответствует временному сдвигу между последним из зафиксированных событий и началом передачи информации в приемник. Для этого на тактовый (С) вход счетчика 58 подаются импульсы синхронно с их поступлением на вход счетчика 56. При фиксации любого «события» сигналом от И 78, поданным на R вход, счетчик 58 устанавливается в начальное состояние. Таким образом, после завершения времени контроля код счетчика 58 соответствует времени, прошедшему от момента фиксации последнего «события». Если передача данных не начинается до установки в счетчике 58 максимально допустимого кода, чувствительность счетчика к тактовым импульсам блокируется сигналом «0», поступающим на его второй (Р) вход от НЕ 70. Сочетание двух меток времени определяет временной сдвиг «события» относительно времени начала передачи информации в приемник. По времени передачи данных (ТП), а также времени, определяемому первой и второй метками времени (Т1М/Т2М), и абсолютному (астрономическому) времени фиксации информации во внешнем устройстве (ТА) можно определить реальное время «события» «х» (ТРХ):

где Т1МХ - время по первой относительной метке времени для «события» X.

Приведем пример расчета ТР7 («события» 7) для следующих исходных данных:

- ТА=12 часов 34 минуты 23 с 460 мс,

- зафиксированное число «событий» - 8,

- код первой метки времени, зафиксированный счетчиком 56 для седьмого «события», - 48710 (в десятичной системе), число разрядов кода первой метки времени (счетчика 56) - 16,

- код второй метки времени - 22810 при числе разрядов кода второй метки времени (счетчика 58) - 16,

- число датчиков - 32, т.е. m=5,

- частота сигналов генератора 5-200 кГц, дискретность фиксации «событий» ТД=1 мс.

Время ТП передачи в приемник данных по второй метке времени и информации от регистра 89 определяется общим числом тактов передачи, которое равно [16+8(16+5+1)]. Тогда ТП=6 [16+8(16+5+1)]/200 мс=6 мс.

Временной сдвиг Т1М7=487·1 мс, Т2М=228·1 мс. Тогда ТР7=12 часов 34 минуты 23 с 460 мс - (6+487+228) мс=12 часов 34 минуты 22 с 739 мс.

Следует отметить, что приведенные расчеты действительны при передаче данных приемнику в режиме, близком к реальному времени. При ретрансляции данных со скоростью, равной, например, 200 бит/с, для определения реального времени «события» необходимо учесть ТП=[16+8(16+5+1)]/0,2 мс=960 мс (приведенные в примерах расчеты не учитывают время передачи, кроме данных по «событию», других компонентов информационного сообщения, например стартовой комбинации, адресного поля, поля защиты).

Рассмотрим работу устройства при передаче «данных 2». Время фиксации «событий» ограничивается установленной (максимальной) емкостью счетчика 56 или установленным (максимальным) числом «событий», т.е. максимальной емкостью счетчика 57. С помощью ИЛИ 83 фиксируется ввод в счетчик 56 или 57 максимального числа импульсов. Сигнал «1» от ИЛИ 83 через И 74 (на второй вход которого подан сигнал «1» с выхода 5-Р распределителя 27) подается на один вход элементов И 75, И 76. Если к данному моменту зафиксировано одно «событие», сигнал «1» и выходной сигнал устройства «запрос 1» образуются на выходе И 75. В данном случае устройство реализует, как описано выше, процедуры передачи «данных 1». Если же регистр 64 зафиксировал не менее двух «событий», сигнал «1» и выходной сигнал «запрос 2» образуются на выходе И 76.

В ответ на сигнал «запрос 2» внешнее устройство подает на вход устройства сигнал «передача 2». Так как в рассматриваемом режиме работы сигнал «передача 1» отсутствует, на вход «X» коммутатора 62 подается сигнал «0» с выхода НЕ 72, а на вход «У» - сигнал «1» со входа НЕ 72. Передача сигналов от И 79 на выход коммутатора 62 заблокирована, а распределитель 27 не переводится из позиции 6-Р в позиции 7-Р и 8-Р по сигналам от формирователя 23. Позиция 6-Р используется для передачи во внешнее устройство кода второй метки времени, зафиксированной счетчиком 58. По сигналу «1» на выходе 6-Р распределителя 27, поданному на управляющий вход «X» коммутатора 61, на выходы коммутатора подаются сигналы с группы входов «DX», т.е. с выходов счетчика 58. Выходные сигналы коммутатора 61 по сигналу «1», поданному на управляющий (У) вход регистра 90 с выхода ИЛИ 84, записываются в регистр. Занесенный в регистр 90 параллельный код преобразуется в последовательный с помощью тактовых сигналов, поступающих на синхронизирующий (С) вход 90 с выхода 5 распределителя 28. Последовательный выходной код регистра 90 подается на выход «данные 2» устройства. Число тактов передачи кода второй метки времени должно соответствовать установленному числу разрядов (q) счетчика 58. Число тактов передачи эквивалентно коду на выходах 1...t счетчика 60, который переводится в рабочее состояние сигналом «1» на втором (Р) входе при поступлении на вход устройства сигнала «передача 2» и подсчитывает тактовые сигналы с выхода 5 распределителя 28. Завершение передачи кода второй метки времени определяется по кодовому состоянию счетчика 60. Требуемое кодовое состояние счетчика фиксируется дешифратором 80. Сигнал «1» с выхода дешифратора 80 через ИЛИ 82, коммутатор 62, ИЛИ 88 подается на первый (С) вход распределителя 27, переводя его в позицию 7-Р. Одновременно сигналом «1» по входу R счетчик 60 возвращается в начальное состояние. Позиция 7-Р распределителя 27 используется для передачи на выход «данные 2» информации, ранее записанной в регистр - ОЗУ 89. По сигналу «1», поданному на управляющий вход «У» коммутатора 61, на выходы коммутатора подаются сигналы с информационных выходов 1...(m+q+1) регистра - ОЗУ 89. Для считывания и передачи во внешнее устройство всех зафиксированных данных из регистра - ОЗУ 89 должны быть считаны данные с ячеек, число которых равно числу зафиксированных «событий». Число ранее зафиксированных событий сохраняется в счетчике 59. Считанный из регистра - ОЗУ 89 код включает данные, характеризующие одно событие. Указанный параллельный код заносится в регистр 90, который преобразует его в последовательный, поступающий на выход «данные 2» устройства. Число тактов передачи данных, характеризующих одно событие, равно числу разрядов выходного кода регистра - ОЗУ 89 - (m+g+1)=t, следовательно, число разрядов счетчика 60 должно быть не меньше «t». Число тактов передачи фиксируется дешифратором 81, который образует на выходе сигнал «1» при установке на выходе счетчика 60 требуемого кода. Сигнал от 81 через ИЛИ 86 подается на первый (С) вход счетчика 57, который к началу этапа 7-Р сигналом «1» по входу R (с выхода ИЛИ 87) был переведен в начальное состояние. Таким образом, выходной код счетчика 57 на этапе 7-Р соответствует числу циклов передачи данных, считанных из регистра - ОЗУ 89.

Сигнал от ИЛИ 86 подается также на синхронизирующий (С) вход регистра - ОЗУ 89, благодаря чему на выход регистра поступает код, характеризующий очередное «событие», причем номер «события» соответствует выходному коду счетчика 57. Как было описано, код от регистра - ОЗУ 89 через коммутатор 61 заносится в регистр 90 и преобразуется в последовательный код. Для определения момента завершения формирования «данных 2» код счетчика 57 сравнивается компаратором 63 с кодом, ранее занесенным в счетчик 59 и соответствующим числу зафиксированных «событий». Если коды счетчиков совпадают, на выходе 63 образуется сигнал «1», который подается на второй (D) вход триггера 65. По сигналу «1» на третьем (С) входе триггер 65 в указанном случае переводится в состояние «1». Сигнал от триггера 65 через ИЛИ 82 и коммутатор 62 подается на первый (С) вход распределителя 27. Устройство переводится на этап 8-Р и, как указывалось выше, завершается процесс передачи «данных 2».

Показано, что новые элементы предложенного устройства и связи между ними и элементами, введенными в устройство-прототип, позволяют обеспечить получение новых функциональных возможностей - углубленную диагностику работоспособности узлов, фиксацию кратковременных сигналов от датчиков и временной последовательности «событий» - изменений состояния датчиков. По информационным сообщениям от предложенного устройства во внешнем устройстве, соединенном с ним по телемеханическому каналу связи, восстанавливается реальное время любого «события», что обеспечивает использование предложенного устройства как регистратора нештатных (аварийных) ситуаций.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОДИРОВАНИЯ И ПЕРЕДАЧИ СИГНАЛОВ | 2004 |

|

RU2282246C2 |

| КОДОИМПУЛЬСНОЕ ПЕРЕДАЮЩЕЕ УСТРОЙСТВО С СОКРАЩЕНИЕМ ИЗБЫТОЧНОСТИ ИНФОРМАЦИИ | 2001 |

|

RU2234738C2 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

| Устройство для спорадической передачи телесигнализации | 1985 |

|

SU1260996A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| СИСТЕМА АДАПТИВНОГО УПРАВЛЕНИЯ ЭЛЕКТРОГИДРАВЛИЧЕСКИМ СЛЕДЯЩИМ ПРИВОДОМ | 2009 |

|

RU2430397C2 |

| Устройство для приема и обработки команд телеуправления | 1989 |

|

SU1667137A1 |

| Устройство стабилизации амплитуды видеосигнала | 1989 |

|

SU1748283A1 |

| Устройство для контроля правильности соединений электромонтажа | 1988 |

|

SU1553927A1 |

| Устройство для измерения расхода нефтепродуктов,сжиженных газов и газовых конденсатов | 1985 |

|

SU1281903A1 |

Устройство является частью многофункционального информационно-управляющего комплекса и предназначено для формирования информационного сообщения, содержащего не только данные о состоянии двухпозиционных объектов - исполнительных механизмов, охранной и пожарной сигнализации, но и временной последовательности их изменений. Технический результат - расширение функциональных возможностей. Устройство отличается высокой достоверностью информации благодаря совмещению процедур ввода и кодирования сигналов от датчика. Ввод и кодирование информации от датчиков проводится в два этапа - на первом этапе фиксируются и заносятся в регистры - ОЗУ текущие значения сигналов от датчиков, а на втором этапе процедуры ввода и кодирования сигналов совмещаются с диагностикой работоспособности общих и индивидуальных узлов устройства и цепей связи кодера с датчиками. Особенность предложенного устройства - фиксация кратковременных сигналов и временной последовательности их изменений, позволяет использовать его как регистратор аварийных (внештатных) процессов. Устройство позволяет применять телемеханические каналы связи. 3 ил.

Устройство формирования и передачи последовательности сигналов, которое содержит источник питания, блок датчиков сигналов, первый, второй и третий коммутаторы, преобразователь параллельного кода в последовательный, состоящий из мультиплексора и первого счетчика, генератор тактовых импульсов, первый распределитель импульсов, первый регистр - ОЗУ, компаратор последовательных кодов, первый, второй и третий триггеры, первый и второй формирователи импульсов, первый, второй, третий, четвертый, пятый, шестой, седьмой элементы ИЛИ, первый и второй элементы И, элемент задержки, первый и второй элементы И-НЕ, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, ИЛИ-НЕ, причем ненулевой («U») выход источника питания подключен к первым входам первого и второго коммутатора, вторым входам первого счетчика, первого распределителя, а нулевой («0») выход - к первому и четвертому входам первого триггера, первому входу второго триггера, ко второму входу второго коммутатора, объединенные вторые выходы узлов блока датчиков сигналов соединены с выходом первого и вторым выходом второго коммутаторов, а первые, индивидуальные выходы узлов блока датчиков сигналов подключены к информационным входам мультиплексора, у которого адресные входы соединены с адресными входами первого регистра - ОЗУ и соответствующими выходными разрядами (1...m) первого счетчика а выход - с первым выходом второго коммутатора и входом третьего коммутатора, у которого выход соединен с первым входом компаратора последовательных кодов, подключенного вторым входом к первому выходу первого триггера, который образует выход «данные 1» устройства, отличающееся тем, что в устройство включены второй распределитель импульсов, второй вход которого соединен с ненулевым выходом источника питания, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, ИЛИ-НЕ, второй, третий, четвертый, пятый и шестой счетчики, четвертый и пятый коммутаторы, компаратор параллельных кодов, третий распределитель импульсов, четвертый и пятый триггеры, второй регистр - ОЗУ, регистр - преобразователь параллельного кода в последовательный, первый и второй дешифраторы, третий, четвертый, пятый, шестой, седьмой восьмой и девятый элементы. И, восьмой, девятый десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый пятнадцатый и шестнадцатый элементы ИЛИ, первый, второй, третий, четвертый, пятый и шестой элементы НЕ, причем первый выход первого триггера подключен к первому входу второго элемента И-НЕ, выход которого соединен с третьим входом второго коммутатора, а второй вход - со вторыми входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первого элемента И-НЕ, подключенного выходом ко второму входу первого коммутатора, вторым входом второго элемента И, а также четвертым выходом первого распределителя, у которого также соединены: второй выход с третьим (С) входом третьего триггера, вторыми входами пятого элемента ИЛИ и элемента ИЛИ-НЕ, подключенного выходом к третьему входу второго коммутатора, первый выход - с первым входом элемента ИЛИ-НЕ и четвертым (R) входом третьего триггера, пятый выход - со вторым входом восьмого элемента ИЛИ и входом элемента задержки, подключенного выходом к первому входу седьмого элемента ИЛИ, шестой выход - соединен с первым, а седьмой выход - со вторым входом третьего элемента ИЛИ, подключенного выходом к выходу «вывод данных» устройства, и вторым входом шестого элемента ИЛИ, подключенного выходом к дополнительному адресному входу первого регистра - ОЗУ, восьмой выход - со вторым входом седьмого элемента ИЛИ, соединенного выходом - с первым (S) входом третьего триггера, у которого первый (прямой) выход соединен с третьим (R) входом первого распределителя, а второй (D) вход - со вторым (инверсным) выходом второго триггера, соединенного первым (прямым) выходом со вторым (D) входом второго триггера через первый вход четвертого элемента ИЛИ, у которого второй вход соединен с выходом компаратора, у второго триггера третий (С) вход соединен со вторыми входами первого и второго элементов ИЛИ, а четвертый (R) вход - с третьим (R) входом первого счетчика и выходом второго формирователя импульсов, соединенного входом с выходным разрядом (m+1) первого счетчика, у которого первый (С) вход соединен с шестым выходом второго распределителя, у которого также соединены: (С) вход - с выходом генератора тактовых импульсов, третий выход - с первым входом второго элемента ИЛИ и третьим (С) входом первого триггера, третий (R) вход - с выходом восьмого элемента ИЛИ, соединенного первым входом с выходами «такты» устройства и первого формирователя импульсов, подключенного входом к первому выходу первого счетчика, а второй выход - с первым входом первого элемента ИЛИ, у которого выход соединен со входом разрешения (Р) первого регистра - ОЗУ, у которого выход соединен со вторым (D) входом первого триггера, у которого второй (инверсный) выход соединен с первым входом первого элемента И-НЕ, информационный вход первого регистра - ОЗУ соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, подключенного первым входом к выходу третьего коммутатора, а управляющий (У) вход - с выходом пятого элемента ИЛИ, соединенного первым входом с первым входом шестого элемента ИЛИ и выходом второго элемента И, соединенного первым входом с выходом второго элемента ИЛИ, блок датчиков содержит для каждого датчика первый и второй диоды, первый стабилизатор, причем анод соответствующего первого диода и катод соответствующего второго диода объединены и являются первыми выходами блока датчиков сигнала, катод соответствующего первого диода соединен с одним выходом соответствующего датчика сигнала, анод соответствующего первого стабилитрона соединен с анодом соответствующего второго диода, вторые выходы датчиков сигнала, соединенные каждый с катодом соответствующего стабилитрона объединены и образуют второй, общий выход блока датчиков сигнала, первый коммутатор включает первый и второй транзисторы, первый, второй, третий, четвертый и пятый резисторы и второй стабилитрон, причем катоды первого и второго транзисторов и первые выводы первого и третьего резисторов соединены между собой, образуют первый вход коммутатора и подключены к ненулевому (U) выходу источника питания, вторые выходы первого и третьего резисторов соединены, соответственно, с базами первого и второго транзисторов и первыми выходами второго и четвертого резисторов, вторые выходы которых образуют, соответственно, второй и третий входы первого коммутатора, выход которого подключен к первому выходу пятого резистора, второй выход которого соединен с коллектором первого транзистора и анодом второго стабилитрона, соединенного катодом с коллектором второго транзистора, второй коммутатор включает третий и четвертый транзисторы, шестой, седьмой восьмой, девятый и десятый резисторы и третий диод, причем эмиттер третьего транзистора и первый выход шестого резистора подключены через первый вход коммутатора к ненулевому (U) выходу источника питания, база третьего транзистора и второй выход шестого резистора объединены и подключены к первому выходу седьмого резистора, второй выход которого является третьим входом второго коммутатора, второй вход которого соединен с нулевым выходом источника питания и объединенными эмиттером четвертого транзистора и первым выходом девятого резистора, второй выход которого соединен с базой четвертого транзистора, а через восьмой резистор с коллектором третьего транзистора и первым выходом десятого резистора, второй выход которого соединен с анодом третьего диода, подключенного катодом к первому выходу второго коммутатора, у которого второй выход соединен с коллектором четвертого транзистора, третий коммутатор включает пятый транзистор, третий стабилитрон, одиннадцатый и двенадцатый резисторы, причем первый выход двенадцатого резистора соединен с ненулевым выходом источника питания, второй выход двенадцатого резистора образует выход третьего коммутатора и соединен с коллектором пятого транзистора, у которого база соединена с первым выходом одиннадцатого резистора и анодом третьего стабилитрона, катод которого образует вход третьего коммутатора, а эмиттер пятого транзистора соединен со вторым выходом одиннадцатого резистора и нулевым выходом источника питания, причем у девятого элемента ИЛИ первый, второй, третий и четвертый входы соединены с соответствующими выходами первого распределителя, а выход соединен с первым входом первого элемента И, соединенного вторым входом с выходом второго формирователя импульсов, а выходом - с первым входом шестнадцатого элемента ИЛИ, выход третьего элемента ИЛИ соединен с первым, а выход второго формирователя импульсов - со вторым входом девятого элемента И, выходы (1...m) основных разрядов первого счетчика соединены с информационными входами (1...m) второго регистра - ОЗУ, информационные входы (m+1...m+q) которого соединена с выходами (1...q) второго счетчика, а информационный вход (m+q+1) - с выходом третьего коммутатора, у первого распределителя соединены: пятый выход - со вторыми входами четвертого и седьмого элементов И, шестой выход - с вторым входом пятнадцатого элемента ИЛИ, первым (X) управляющим входом четвертого коммутатора, первым входом двенадцатого элемента ИЛИ и вторым входом первого дешифратора, седьмой выход - с вторым (У) управляющим входом четвертого коммутатора, третьим, управляющим входом компаратора параллельных кодов, вторыми входами двенадцатого элемента ИЛИ и второго дешифратора, восьмой выход - с четвертыми (R) входами четвертого и пятого триггеров, третьими (R) входами второго и пятого счетчиков, третьего распределителя и первым входом пятнадцатого элемента ИЛИ, выход первого формирователя импульсов соединен со вторым входом третьего элемента И, пятый выход второго распределителя соединен с третьим (С) входом регистра - преобразователя параллельного кода в последовательный и первым (С) входом шестого счетчика, а четвертый выход второго распределителя соединен с первым входом восьмого элемента И, соединенного вторым входом с выходом компаратора последовательных кодов, а первый (С) вход первого распределителя соединен с выходом шестнадцатого элемента ИЛИ и третьим (R) входом шестого счетчика, выходы которого соединены с группой информационных входов первого и второго дешифраторов, а второй (Р) вход - с третьим (С) входом пятого триггера, входом шестого элемента НЕ, выходом «передача 2» внешнего устройства, вторым входом тринадцатого элемента ИЛИ, подключенного первым входом к выходу «передача 1» внешнего устройства, и вторым входом управления (У) пятого коммутатора, подключенного первым входом управления (X) к выходу шестого элемента НЕ, первым информационным входом к выходу девятого элемента И, вторым информационным входом к выходу десятого элемента ИЛИ, а выходом - ко второму входу шестнадцатого элемента ИЛИ, соединенного третьим входом с выходом седьмого элемента И, у которого первый вход соединен с выходом тринадцатого элемента ИЛИ, нулевой («0») выход источника питания соединен с первыми входами четвертого и пятого триггера, а ненулевой («U») выход источника питания - со вторым (Р) входом пятого счетчика, у которого первый (С) вход соединен с первым (С) входом третьего распределителя, выходом восьмого элемента И, третьим (R) входом четвертого счетчика и вторым входом четырнадцатого элемента ИЛИ, а выходы пятого счетчика соединены со второй группой информационных входов компаратора параллельных кодов, первая группа информационных входов которого соединена с адресными входами второго регистра - ОЗУ и выходами третьего счетчика, а выход - со вторым (D) входом четвертого триггера, у которого прямой выход соединен со вторым входом десятого элемента ИЛИ, подключенного первым входом к выходу первого дешифратора, а третий (С) вход четвертого триггера соединен с выходом второго дешифратора и первым входом четырнадцатого элемента ИЛИ, у которого выход соединен с первым (С) входом третьего счетчика и синхронизирующим (С) входом второго регистра - ОЗУ, у которого управляющий вход (W) соединен со вторым (инверсным) выходом пятого триггера, а группа информационных выходов - со второй группой (DY) информационных входов четвертого коммутатора, соединенного первой группой информационных входов с выходами четвертого счетчика, а группой информационных выходов - с группой информационных (D) входов регистра - преобразователя параллельного кода в последовательный, у которого вход управления (У) соединен с выходом двенадцатого элемента ИЛИ, а выход является выходом «данные 2» устройства, причем выход «запрос 1» устройства соединен с выходом пятого, а выход «запрос 2» устройства - с выходом шестого элемента И, первые входы пятого и шестого элементов И объединены и соединены с выходом четвертого элемента И, подключенного первым входом к выходу одиннадцатого элемента ИЛИ, второй вход пятого элемента И подключен ко второму, а второй вход шестого элемента И - к третьему выходу третьего распределителя, второму (D) входу пятого триггера и входу пятого элемента НЕ, соединенного выходом со вторым (Р) входом третьего распределителя, у которого первый выход соединен со входом первого элемента НЕ, подключенного выходом к первому входу третьего элемента И, соединенного выходом с первыми (С) входами второго и четвертого счетчиков, у которых вторые (Р) входы соединены, соответственно, с выходом второго и четвертого элементов НЕ, вход четвертого элемента НЕ соединен с выходом старшего разряда четвертого счетчика, а вход второго элемента НЕ - с выходом старшего разряда второго счетчика и первым входом одиннадцатого элемента ИЛИ, соединенного вторым входом с выходом старшего разряда третьего счетчика и входом третьего элемента НЕ, подключенного выходом ко второму (Р) входу третьего счетчика, у которого третий (R) вход соединен с выходом пятнадцатого элемента ИЛИ.

| Устройство для спорадической передачи телесигнализации | 1985 |

|

SU1260996A1 |

| RU 2132573 C1, 27.06.1999 | |||

| КОДОИМПУЛЬСНОЕ ПЕРЕДАЮЩЕЕ УСТРОЙСТВО С СОКРАЩЕНИЕМ ИЗБЫТОЧНОСТИ ИНФОРМАЦИИ | 2001 |

|

RU2234738C2 |

| US 5973629 A, 26.10.1994 | |||

| Плуг | 1980 |

|

SU974944A1 |

Авторы

Даты

2007-05-20—Публикация

2005-02-09—Подача