третий и четвертый элементы И, первые входы которых подключены соответственно к единичному и нулевому выходам второго триггера, а вторые входы третьего и четвертого элементов И объединены между собой и подключены к выходу второго элемента И, выход сумматора соединен с вторым входе блока быстрого преобразования Фурье, первый вход сумматора через второй функциональный преобразователь соединен с выходом первого блока формирования комплексно-сопряженных чисел, а второй вход сумматора подключен к выходу второго блока формирования комплексно-сопряженных чисел, первый вход которого соединен с первым входом первого блока формирования комплексно-сопряженных чисел, с управляющим входом четвертого кокмутатора и с нулевым выходом второго триггера блока управления, единичный вход которого соединен с входами Сброс первого и второго, регистров памяти, выход третьего элемента И блока управления подключен к управляющим входам третьего регистра памяти и третьего блока памяти, выход четвертого элемента И блока управления подключен к управляющим входам четвертого блока памяти и первого и второго регистров памяти, выходы которых соединены с вторыми входами соответственно первого и второго блоков формирования комплексно-сопряженных чисел, информационный вход первого регистра памяти подключен к выходу третьего регистра памяти, информационный вход которого объединен с информационным входом второго регистра памяти и соединен с выходом блока умножения, второй вход которого подключен к выходу четвертого ксадмутатора, первый и второй информационные входы которого соединены с выходами третьего и Четвертого блоков памяти соответственно, информационный вход четвертого блока памяти является вторым информационным входом генератора, вторым выходом которого является второй выход блока цифро-аналоговых преобразователей.

2. Генератор по п. 1, отличающийся тем, что каждый блок формирования комплексно-сопряженного числа содержит элемент НЕ и коммутатор ,, выход которого является выходом блока, первьам входом которого является вход элемента НЕ, выход которого соединен с первым информационным входсм коммутатора, второй информационный вход которого объединен с входом элемента НЕ, а управляш(ий вход коь««утатора является вторым ВХОДСЯ4 блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайного процесса | 1982 |

|

SU1020820A1 |

| Генератор случайного процесса | 1981 |

|

SU1015381A1 |

| Генератор случайного процесса | 1981 |

|

SU972505A1 |

| Генератор случайных процессов | 1984 |

|

SU1309021A1 |

| Генератор случайных процессов | 1981 |

|

SU985786A1 |

| Генератор нестационарного случайного импульсного процесса | 1981 |

|

SU1008739A1 |

| Генератор случайного процесса | 1982 |

|

SU1068936A1 |

| Генератор случайных чисел | 1983 |

|

SU1124294A1 |

| Генератор случайного процесса | 1982 |

|

SU1087991A1 |

| Стохастический преобразователь | 1981 |

|

SU1056191A1 |

1. ГЕНЕРАТОР СЛУЧАЙНОГО ПРОЦЕССА, содержащий три блока памяти, три коммутатора, блок умножения, блок быстрого преобразования Фурье, датчик случайных чисел, первый функциональный преобразователь, блок формирования интервалов времени, блок, цифро-аналоговых преобразователей и блок управления, содержащий генератор тактовых HMnyjjbcoB, регистр памяти, счетчик, схему сравнения, два элемента И и три триггера, единичные входы первых двух триггеров и счетный вход третьего триггера объединены между собой и подключены к первому выходу блока формирования интервалов времени, единичный выход третьего триггера соединен с управляюйшми входами первого, второго и третьего коммутаторов, выход генератора тактовых импульсов соединен с -первыми входами первого и второго элементов И и с входом блока формирования интервалов времени, выход регистра памяти блока управления соединен с первым входом схемы сравнения, второй вход которой подключен к информационному выходу счетчика, а выход cxeMfcj сравнения, соединен с вторым входом второго элемента И, выход которого соединен с входом Сброс счетчика и нулевым входом первого триггера, единичный выход которогр соединен с вторым входом вторрго элемента И, выход которого соединен с счетным входом счетчика, с-нулевым входом второго триггера, с входом датчика случайных чисел и с первым входом блока быстрого преобразования Фурье, выход которого подключен к информационному входу первого коммутатора, первый и второй выходы которого, соединены с информационными входами соответственно первого и второго блоков памяти, выходы е S которых подключены соответственно к первому и второму информационным (Л входам второго коммутатора, выход которого соединен с входом блока цифрос аналоговых преобразователей, первый выход которого является первым выходом генератора, первым информацион- 1 ным входом которого является информационный вход третьего блока памяти, выход датчика случайных чисел через первый функциональный преобразовась эо тель подключен к первому входу блока умножения, второй выход блока формирования интервалов времени соедих нен с информационным входом третьего :х: коммутатора, первый и второй выходы ел которого подключены к управляющим , входам соответственно первого и вто,рого блоков памяти, о т л и ч а ющ и и с я тем, что, с целью:расширения функциональных возможностей генератора за счет задания статисти.ческих характеристик процесса на втором выходе генератора, он содержит четвертый блок памяти, четвертый коммутатор, три регистра памяти, два блока формирования комплексно-сопряженных чисел, второй функциональный преобразователь и сумматор, а блок управления дополнительно .додержит

Изобретение относится к вычислительной технике и может быть использовано для имитации случайных процессов с заданныкм и программно управляемыми спектральными характеристиками в вычислительно-моделирующих комплексах для управления испытаниями изделий электронной и другой техники на механические, электрические и другие воздействия, а также при построении моделирующей аппаратуры для исследования и оптимизации структурно сложных систем.

Известны генераторы случайного процесса, содержащие один или несколько формирующих фильтров для придания случайному процессу требуемых спектральных свойств. Управление спектральной плотностью мощности случайного процесса на выходе таких генераторов выполняется изменением частотных характеристик формирующих фильтров С11.

Однако проектирование и изготовление формирующих фильтров с перестраиваемой в широком диапазоне частотной характеристикой представляет собой достаточно трудную техническую задачу.

Известно также устройство, использующее для формирования выходного случайного процесса множество импульсных потоков, содержащее в своей структуре множество генераторов импульсов, элементы И, элементы

ИЛИ и некоторые другие вспомогательные элементы. Процесс на выходе такого генератора представляет собой последовательность импульсных сигналов определенной формы, следующих через сутучайные интервалы времени, причем управляемой статистической характеристикрй выходного случайного процесса является закон распределения случайных временных интервалов СзТНедостатком устройства являются

ограниченные возможности его использования для генерирования случайного процесса с заданными спектральными характеристиками, так как определить

требуемую функцию распределения случайных временных интервалов по заданной спектральнойплотности мощности оказывается затруднительным как. изза сложности математических преобразований, так и из-за ограниченности классов воспроизводимых спектральных плотностей мощности.

Наиболее близким техническим решением к изобретению является устройство, содержащее три блока памяти, три коммутатора, блок быстрого преобразования Фурье, блок умножения, датчик случайных чисел, функциональный преобразователь, блок формирования интервалов времени, цифро-аналоговый преобразователь, блок управления и соответствующие связи. Устройство позволяет получать на своем выходе случайный процесс вибрационного типа с заданными спектральными характеристиками 31.

Недостатком известного устройства является невозможность одновременного формирования двух случайных процессов с заданными и в общем случае различными спектральными характеристиками (двухканальные генераторы широко используются в системах испытания изделий на. многомерные вибрационные воздействия и в других областях);

Цель изобретения - расширение функциональных возможностей за счёт одновременного формирования двух- случайных процессов с заданными спект.рал)Ными характеристиками.

Для достижения поставленной цели в генератор случайного процесса, содержащий три блока памяти, три коммутатора, блок умножения, блок быстрого преобразования Фурье, датчик случайных чисел, первый функциональный преобразователь, блок формирования интервалов времени, блок цифроаналоговых преобразователей и блок управления, содержащий генератор тактовых импульсов, регистр памяти, счетчик, схему сравнения, два элемента И и три триггера, единичные входы первых двух триггеров и счетный вход третьего.триггера объединены между собой и подключены к первому выходу блока формирования интервалов времени, единичный выход третьего триггера соединён с управляющими входами первого, второго и третьего коммутаторов, выход генератора тактовых импульсов соединен с первыми входами первого и второго элементов И и с входом блока формирования интервалов времени, выход регистра памяти блока управления соединен с первым входом cxeNtJ сравнения, второй вход которой подключен к информационному выходу счетчика, а выход схемы сравнения соединен с вторым входом второго злемента И, выход которого соединен с входом Сброс счетчика и с нулевым -входом первого триггера,

единичный выход которого соединен с вторым входом второго элемента И, выход которого соединен с счетным входом счетчика, с нулевым входом второго Триггера, с входом датчика случайных чисел и с первым входом блока быстрого преобразования Фурье, выход которого подключен к информа0ционному входу первого коммутатора, первый и второй выходы которого соединены с информационными входами соответственно первого и второго блоков памяти, выходы которых под5ключены соответственно .к первому и BTopcMwiy информационным входам второго коммутатора, выход которого со.единен с входом блока цифро-аналоговых преобразователей, первый выход

0 которого является первым выходом ге- . нератора, первым информационным входом которого является информационный вход третьего блока памяти, выход датчика случайных чисел через первый

5 функциональный преобразователь подключен к первсмиу входу блока умножения второй выход блока формирования интервалов времени соединен с инфор- . мационным входом третьего коммутато0ра, первый и второй выходы которого подключены к управляющим входам соответственно первого и второго блоков памяти, введены четвертый блок памяти, четвертый коммутатор, три регистра памяти, два блока формирова5ния комплексно-сопряженных чисел, второй функциональный преобразователь и сумматор, а блок управления дополнительно содержит третий и четвертый элементы И, первые входы ко0торых подключены соответственно к единичному и нулевому выходам второго триггера,.а вторые входы третьего и четвертого элементов И объединены между собой и подключены к выходу

5 второго элемента И, выход сумматора соединен с вторым входом блока быстрого преобразования Фурье, первый вход сумматора через второй функциональный преобразователь соединен с

0 выходом первого блока формирования

. комплексно-сопряженных чисел, а второй вход сумматора подключен к выходу второго е5лока формирования комплексно-сопряженных чисел, первый вход

5 которого соединён с первым входом первого блока формирования комплексносопряженных чисел, с управляющим входом четвертого коммутатора и с нулевым выходом второго триггера блока управления, единичный вход ко0торого соединен с входами Сброс первого и второго регистров памяти, выход третьего элемента И блока управления подключен к управляющим входам третьего регистра памяти и

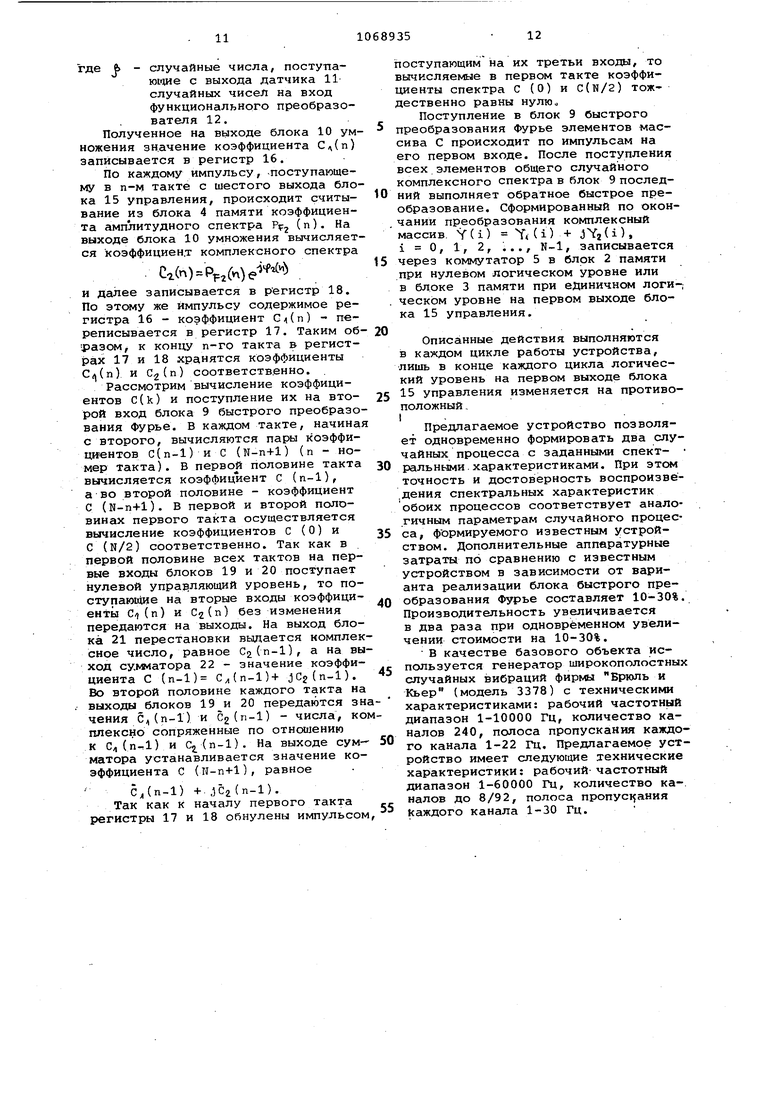

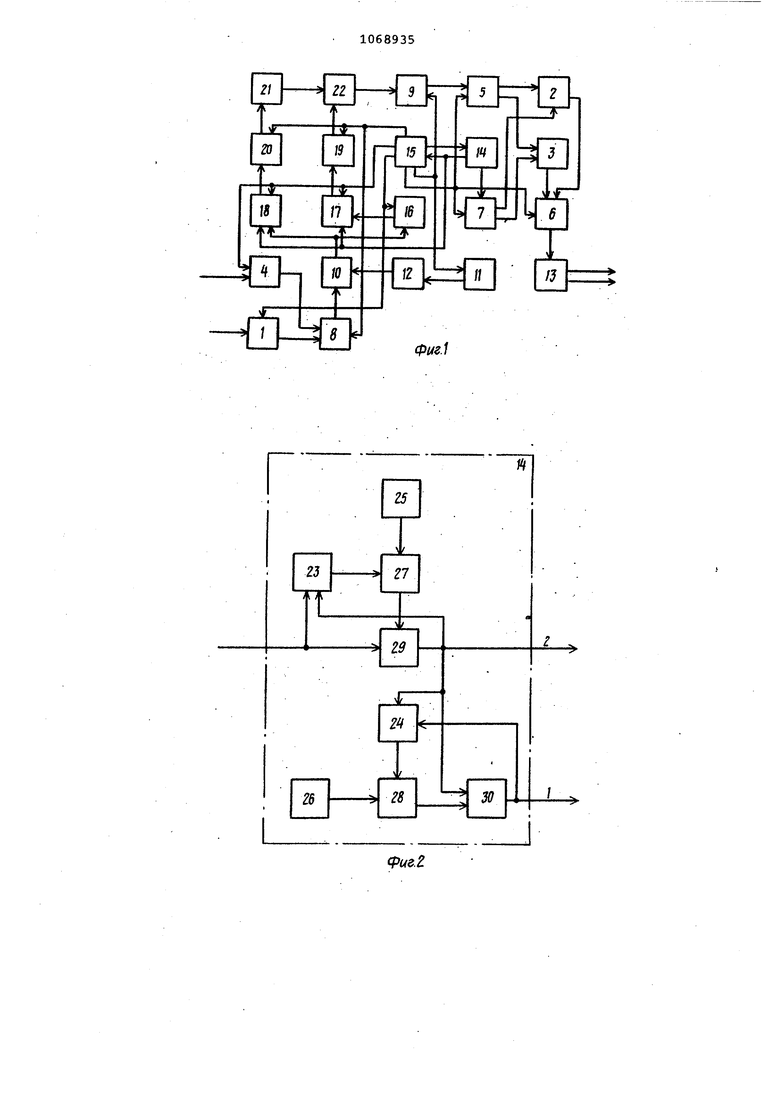

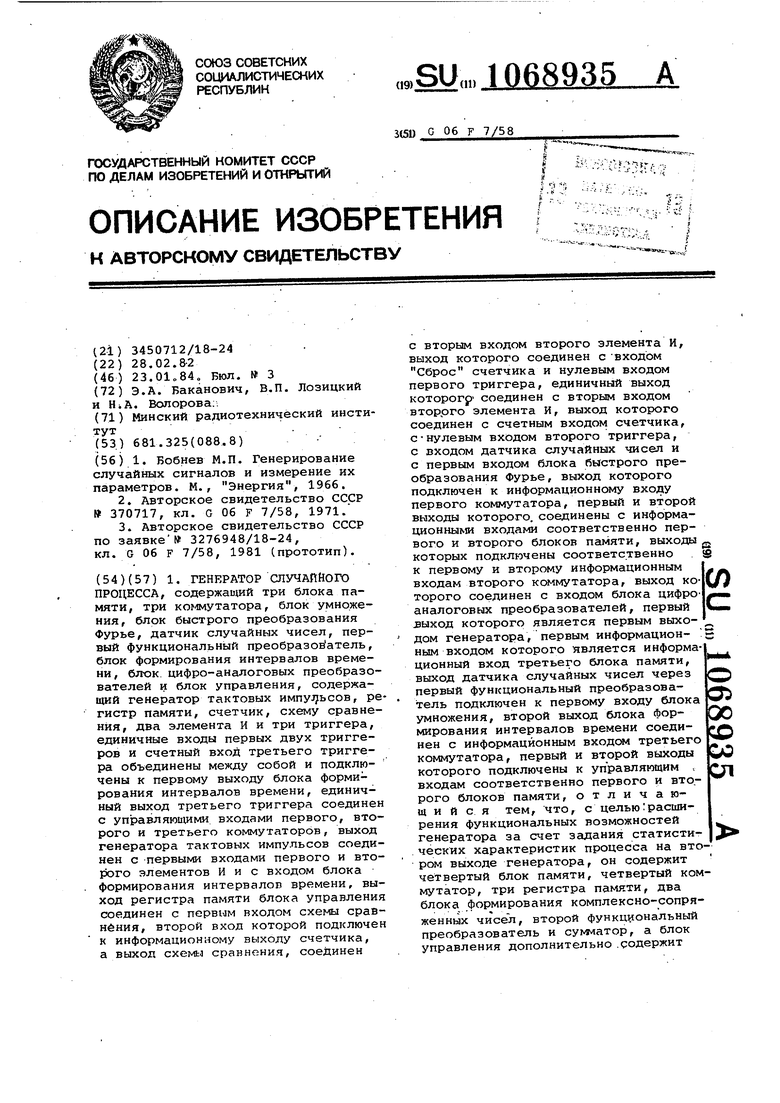

5 третьего блока памяти, выход четвер того элемента И блока управления подключен к управляющим входам четвертого блока памяти и первого и второго регистров памяти, выходы ко торых соединены с вторыми входами соответственно первого и второго бл ков формирования ксмплексно-сопрякенных чисел, информационный вход первого регистра памяти подключен к выходу третьего регистра памяти. информационный вход которого объединен с информационным.входом второго регистра памяти и соединен с выхо-.. дом блока умножения, второй вход которого подключен к выходу четверто го коммутатора, первый и второй информационные входы которого соединены с выходами третьего и четвёртого блоков памяти соответственно информационный вход четвертого блока памяти является вторым информационным входом генератора, вторым выходом ко торого является второй выход блока цифро-аналоговых преобразователей. Кроме того, каждый блок формирования комплексно-сопряженных чисел содержит элемент НЕ и коммутатор, вы ход которого является выходом блока первым входом которого является вход элемента НЕ, выход которого соедине с первым информационным входом коммутатора, второй информационный вход которого объединен с входом элемента НЕ, а управляющий вход кокмутатора является вторым входом блока. На фиг. 1 представлена структурная схема предлагаемого генератора; на фиг. 2 - пример схемной реализации блока формирования интервалов времени на фиг. 3 - схема блока Управления,- на фиг. 4 - пример реализации блока комплексно-сопряженных чисел; на фиг. 5 - временная диаграм ма, поясняющая работу блока управления. Устройство содержит блоки 1-4 памяти, коммутаторы 5-8, блок 9 быстрого преобразования Фурье, блок 10 умножения, датчик 11 случайных чисел функциональный преобразователь 12, блок 13 цифро-аналоговых преобразователей, блок 14 формирования интервалов времени, блок 15 управления, первый 16, втброй 17 и третий 18 регистры, блоки 19 и 20 формирования комплексно-сопряженных чисел, функциональный преобразователь 21 и сумматор 22. Рассмотрим функциональное назначение отдельных блоков устройства. БЛОК 1 памяти предназначен для приема с первого входа генератора и хранения соответствуюпдах коэффициентов амплитудного сйактра первого процесса. Последовательное считывание информации из блока 1 памяти ocy ществляется по импульсным сигнгшам, поступающим на его второй вход. Блоки 2 и 3 памяти идентичны .и предназначены для записи с первого входа и хранения комплексных чисел. Последовательное считывание информации из блоков 2 и 3 памяти осуществляется по импульсам, поступающим на их вторые входы. Четвертый блок 4 памяти предназначен для приема с второго входа генератора и хранения соответствующих им коэффициентов амплитудного спектра второго процесса. Последовательное считывание информации из блока 4 памяти осуществляется по импульсным сигналам на его втором входе. Коммутаторы 5 и 7 служат для коммутации информации, поступающей на второй вход, на первый (второй) выход при нулевом (единичном) сигнале на первом (управляющем) входе. Ком-, мутаторы 6 и 8 обеспечивают передачу на свой выход информации, поступающей на третий вход при нулевом сигнале на первом (управляющем) входе, или информации, поступающей на второй вход при единичном сигнале на первом входе. Блок 9 быстрого преобразования Фурье предназначен для выполнения по одному из известных алгоритмов Обратного быстрого преобразования Фурье над исходным массивок комплексных коэффициентов спектра, который поступает с второго входа. Запись во внутреннюю память блока 9 коэффициентов осуществляется по импульсам, поступгиощим на его первый вход. По окончании выполнения преобразования на выход блока 9 быстрого преобразования Фурье выдается результирующий комплексный массив. В качестве блока 9 может быть использовано любое известное устройство, выполняющее обратное быстрое преобразование Фурье.« Блок 10 умножения обеспечивает перемножение вещественных и комплексных чисел, поступающих соответственно на -второй и первый входы. Датчик 11 случайных чисел по каждому входному импульсу формирует равномерно распределенное целое двоичное число. функциональный преобразователь 12 предназначен для формирования на своем выходе комплексных величин . . ,2К7Гч Ф(К) cos(H) + jsi-n(-) ПО аргументу Кб О,Н-П., поступающему на его вход. Практически блок 12 может быть реализован в виде постоянного запоминающего устройства. Клок 13 цифро-аналоговых преобразователей обеспечивает представление входного дискретного комплексного

случайного процесса в аналоговой форме, причем сигналы на первом и втором выходах блока 13 являются аналоговым представлением соответственно действительной и мнимой частей входного комплексного числа. При практической реализации блок 13 представляет собой два отдельных цифро-аналоговых преобразователя.. На вход одного из них поступает действительная часть, а на вход другого - мнимая часть комплексного числ

Влок 14 формирования интервалов времени предназначен для формирования по входной последовательности импульсов с интервалом следования Ъ двух тактовых последовательностей регулярных импульсов на первом и вТорсяи выходах с интервалами следования соответственно NAt и At. Бло 14 формирования интерваловремени содержит счетчики 23 и 24 суммирующего типа, регистры 25 и 26, блоки 27 и 28 сравнения и элементы И 29 и 30. Счетчик 23, регистр 25, блок 27 сравнения и элемент И 29 обеспечивают формирование на втором выходе блока 14 регулярной последовательности импульсов с регулируемым интервалс 4 следования. По каждому импульсу, поступающему с входа блока 14 на счетный вход счетчика 23, его состояние увеличивается на единицу.. На второй вход элементаИ 29 с.выхода блока 27 сравнения поCTfynaeT высокий (разрешаю1Ш1й) логический уровень при совпадении двоичных кодов счетчика 23 и регистра 25 Установка счетчика 23 в нулевое состояние осуществляется каждым импуль,, поступающим с выхода элемента И 29 на вход сброса счетчика 23, поэтому на второй выход блока 1 формирования интервалов времеии поступает каждый т-й входной импульс. Изменяя содержимое регистра 25, можно управлять интервалом.

Вторая часть блока 14 (счетчик 2 регистр 26, блок 28 сравнения и элемент И 30) совершенно идентична первой И пропускает на первый выход блока 14 каждый N-й импульс, поступагощий с выхода элемента И 29 на счетный вход;счетчика 24 и первыйвход элемента И 30, причем в регистре 26 хранится двоичный код, равный N.

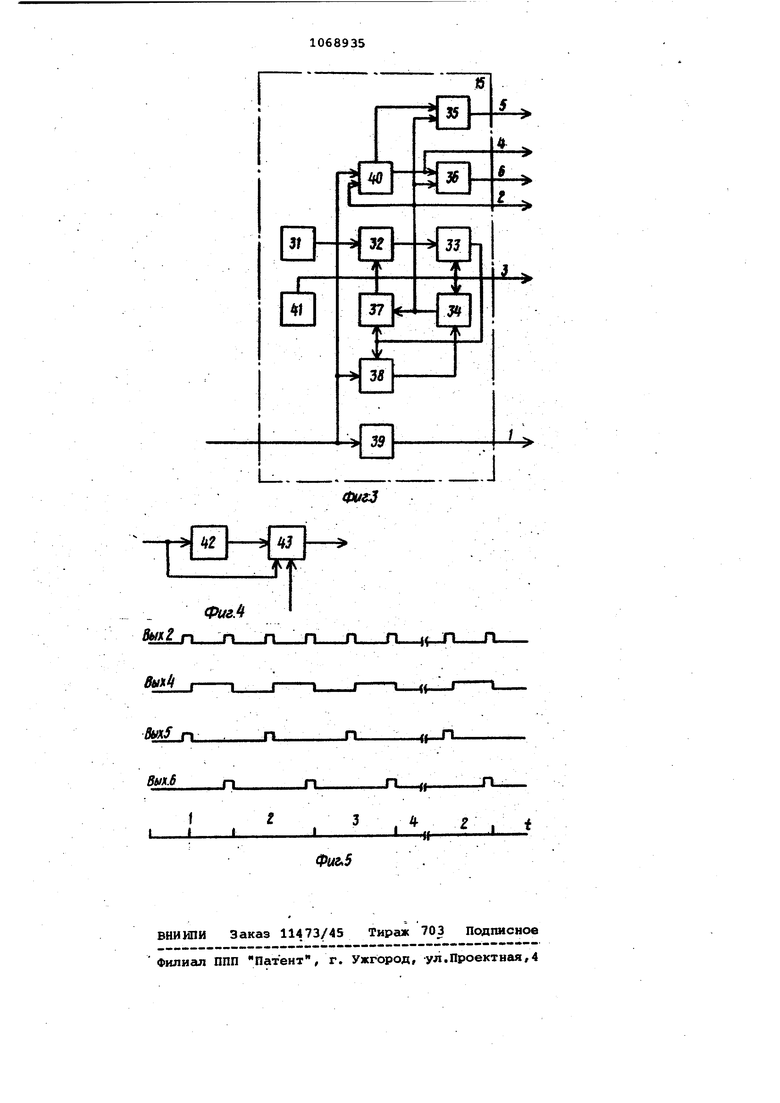

Блок 15 управления предназначен для управления работой отдельных блоков устройства и содержит регист 31, блок 32 сравнения, элементы И 33-36, счетчик 37, триггеры 38-40 и тактовый генератор 41.Выход регисра 31 соединен с первым входом блока 32 сравнения, второй вход которого Соединен с единичным выходом счеТчиКа 37, а выход блока 32 сравнения подключен к первому входу элемента И 33, второй вход которого соединен с вторым входом элемента И 34, выходом тактового генератора 41 и третьим выходом блока 15 управления, выход элемента И 33 подключен к нулевому входу триггера 38 и входу сброса счетчика 37, счетный вход которого соединен с выходом элемента И 34, вторыми входами элементов И 35 и 36, счетным входом триггера 40 и вторым выходом блока 15 управления,

вход которого соединен со счетным входом триггера 39, единичным входом триггера 38 и нулевым входом триггера 40, нулевой и единичный выходы которого подключены к первлм входам соответственно элементов И 35 и 36, вызсрды

которых являются соответственно пятым и шестым выходами блока 15 управления, первым выходом которого является единичный выход триггера 39, выход триггера 38 подключен к первому входу элемента И 34, а единичный выход триггера 40 является четвертым выходом блока 15 управления.

Так КсЖ триггер 39 работает в счетном режиме, то по каждому входному сигналу его состояние изменяется на противоположное. Тактовый генератор 41 формирует регулярную последовательность импульсов с интервалом следования t .

Регистр 31, блок 32 сравнения, элементы И 33 и 34, счетчик 37 и триггер 38 предназначены для формирования по запускающему и чпульсу на входе блока 15 управления группы из N импульсов на втором выходе блока 15 управления. Для этого в регистре 31 постоянно хранится двоичный код, равный (N-1). К моменту прихода очередного импульса на вход блока 15 управления счетчик 37 и триггер 38 находятся в нулевом состоянии. По заднему фронту этого импульса триггер 38 устанавливается в единичное состояние, разрешая тем caNttiM прохождение импульсов с выхо- да тактового генератора 41 на выход элемента И 34 и далее на счетный вход счетчика 37. По прохождении (N-1) импульсов через элемент И 34 в счетчике 37 устанавливается код (N-1), а на выходе блока 31 сравнения появляется высокий логический уровень, поэтому следую1иий тактовый импульс проходит также через элемент И 33 и устанавливает триггер 38 и счетчик 37 в нулевые состояния, запрещая тем самым прохождение следующих импульсов через элемент И 34.

Триггер 40, элементы И 35 и 36 Предназначены для разделения импульсов на втором выходе блока 15 управления на четные и нечетные. Так как по импульсу на входе блока 15 управ ления триггер устанавливается в нулевое состояние, то нечетные импуль сы передаются на пятый выход блока 15 управления, а четные - на шестой выход. Регистры 17 и 18 имеют вход сбро са (третий вход). Блоки 19 и 20 обеспечивают передачу комплексных чисел, поступающих на первый вход, на выход без измене ния при нулевом управляющем сигнале на втором входе и в комплексно-сопряженном виде при единичном сигнал на втором входе. Функциональный преобразователь 2 предназначен для перекрестной пере дачи на выход действительных и мнимых частей входных комплексных чисел, т.е.для выполнения преобразова ния X j(a + jb) -b + Ja, где X - комплексное число на выходе a+jb - комплексное число на входе. Сумматор 22 обеспечивает сложени комплексных чисел, поступающих на его первый и второй входы. Каждый блок формирования комплек сно-сопряженных чисел в простейшем частном случае может состоять из последовательно соединенных элемента НЕ 42 и коммутатора 43.. Сущность изобретения заключается в том, что при небольших дополнител ных аппаратурных затратах с помощью одного обратного быстрого преобразования Фурье одновременно формируются две реализации с различными за данными спектральными характеристиками, . одновременно вычисляются одна реализация первого случайного процесса и одна реализация второго случайного процесса. Случайный процесс на первом и втором выходах генератора представляет собой последовательность реали заций длительностью Т каждая. При этом Начало и.окончание реализаций на обоих выходах синхронны (совпада ют). Применение быстрого преобразования обуславливает протекание в устройстве на каждом цикле (т.е. в промежуток времени, равный длине одной реализации) двух процессов: происходит передача на выходы устройства реализаций случайных процессов кохорые вычислены в предыдущем цикле, и вычисляются реализации случайных процессов, которые передаются .на выходы устройства в следующем цикле. л . Рассмотрим первый процесс. Сформированные в предыдущем цикле значения У(1} и У(i) реализаций.первого и второго случайных процессов в виде действительных и мнимых частей комплексных чисел Y(1) хранятся в блоках 2 или 3 памяти в зависимости от значения управляющего сигнала на первом выходе блока 15 управления. При нулевом значении в текущем цикле этого управляющего сигнала значения Y (i) находятся в блоке 3 памяти, а при единичном - в блоке 2 памяти. При этом управляющий сигнал на первом выходе блока 15 управления изменяется на противоположный в конце каждой реализации (цикла). Последовательно считывание комплексных значений Y(i) осуществляется по импульсам, поступающим с второго выхода блока 14 формирования интервалов времени через коммутатор 7 на второй вход одного из блоков 2 или 3 памяти. Далее эти значения через коммутатор б поступают на вход цифроаналогового преобразователя 13, причем действительная часть А ( i) передается на первый выход преобразователя, а мнимая Уг(1) - на второй. В конце каждой реализации блок 14 формирования интервалов времени выдает на первый свой выход импульс конца реализации. Описанная процедура передачи на выходы устройства значений реализаций случайных процессов повторяется в каждом цикле с тем лиилз отличием, что с помощью управляющего сигнала на первом выходе блока 15 управления блоки 2 и 3 памяти меняются местами, т.е. изменяется коммутация их входов и выходов. Рассмотрим второй вычислительный процесс. Вначале осуществляется вычисление комплексного массива С за N/2 тактов (номера тактов обозначены на временной диаграмме цифрами 1, 2, 3, ..., N/2), В каждом такте на втором выходе блока 15 управления формируются два импульса, при этом первый из них передается на пятый выход блока 15 управления, а второй - на шестой выход. Логический уровень на четвертом выходе блока 15 управления изменяется на противоположный по каждому импульсу во втором выходе этого же блока, поэтому в первой половине каждого такта к второму входу блока 10 умножения подключается выход блока 1 памяти, а во второй половине выход блока 4 памяти. По -каждому импульсу, -поступающему с пятого выхода блока 15 управления в п-м такте, осуществляется считывание коэффициентов Рр (п) и передача на второй вход блока 10 умножения, на .первый вход которого поступают комплексные величины f,().(n )-coslifJbl sti Lfe-l где j - случайные числа, поступаю1Ще с выхода датчика 11 случайных чисел на вход функционального преобразователя 12. Полученное на выходе блока 10 ум ножения значение коэффициента С(п) записывается в регистр 16. По каждому импульсу, -поступающему в п-м такте с шестого выхода бло ка 15 управления, происходит считывание из блока 4 памяти коэффициента амплитудного спектра Р;: (п). На выходе блока 10 умножения вычисляет ся коэффициен.т комплексного спектра Сг(п) Рр,(п) : и далее записывается в регистр 18. По этому же импульсу содержимое регистра 16 - коэффициент G|(n) - переписывается в регистр 17. Таким об разом, к концу п-го такта в регистрах 17 и 18 хранятся коэффициенты С(п) и Cgln) соответственно. . Рассмотрим вычисление коэффициентов C(k) и поступление их на второй вход блока 9 быстрого преобразо вания Фурье. В каждом такте, начина с второго, вычисляются пары коэффициентов С(п-1) и с (N-n+1) (п - номер такта). В первой половине такта вычисляется коэффициент С (п-1), а во второй половине - коэффициент С (N-n+1). В первой и второй половинах первого такта осуществляется вычисление коэффициентов С (0) и С (N/2) соответственно. Так как в первой половине всех тактов на первые входы блоков 19 и 20 поступает нулевой управляющий уровень, то поступающие на вторые входы коэффициенты Ci(n) и С2(п) без изменения передаются на выходы. На выход блока 21 перестановки выдается комплек сное число, равное CgCn-l), а на вы ход сумматора 22 - значение коэффициента С (п-1) Си(п-1)+ jCgCn-l). Во второй половине каждого такта на выходы блоков 19 и 20 передаются зн чения С, (п-1) и Cgdi-l) - числа, ко пленено сопряженные по отношению к С;,() и С2(п-1). На выходе сумматора устанавливается значение коэффициента С (N-n+1), равное C(n-l) + JC2(n-l). Так как к началу первого такта регистры 17 и 18 обнулены импульсом поступающим на их третьи входы, то вычисляемые в первом такте коэффициенты спектра С (0) и c(N/2) тождественно равны нулюо Поступление в блок 9 быстрого преобразования Фурье элементов массива С происходит по импульсам на его первом входе. После поступления всех элементов общего случайного комплексного спектра в блок 9 последний выполняет обратное быстрое преобразование. Сформированный по окончании преобразования комплексный массив. Y(i) Y, (i) + jYzd), i О, 1, 2, ;.., N-1, записывается через коммутатор 5 в блок 2 памяти при нулевом логическом уровне или в блоке 3 памяти при единичном логи-, ческом уровне на первом выходе блока 15 управления. Описанные действия выполняются в каждом цикле работы устройства, лишь в конце каждого цикла логический уровень на первом выходе блока 15 управления изменяется на противоположный, I Предлагаемое устройство позволяет одновременно формировать два случайных процесса с заданными спект- ральньади.характеристиками. При этом точность и достоверность воспроизве.дения спектральных характеристик обоих процессов соответствует аналогичным параметрам случайного процесса, формируемого известным устройством. Дополнительные аппаратурные затраты по сравнению с известным устройством в зависимости от варианта реализации блока быстрого преобразования Фурье составляет 10-30%. Производительность увеличивается в два раза при одновременном увеличении стоимости на 10-30%. В качестве базового объекта используется генератор широкополостных случайных вибраций фирмы Брюль и Кьер (модель 3378) с техническими характеристиками: рабочий частотный диапазон 1-10000 Гц, количество каналов 240, полоса пропускания каждого канала 1-22 Гц. Предлагаемое устройство имеет следующие технические характеристики: рабочий частотный диапазон 1-60000 Гц, количество каналов до 8/92, полоса пропус1 ания Каждого канала 1-30 Гц.

5f

4f

ФигА

BvxS

Вык.6

n

ft

III

i:

36

33

И.. . «

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бобнев М.П | |||

| Генерирование случайных сигналов и измерение их параметров | |||

| М., Энергия, 1966 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-01-23—Публикация

1982-02-28—Подача